20071010105801!lecture07 FET Matching Networks

Diunggah oleh

Luis Alberto0 penilaian0% menganggap dokumen ini bermanfaat (0 suara)

4 tayangan3 halamanWe will look at how we can design matching networks to design a high gain amplifier using simultaneous conjugate matching. You make sure that you keep track of the work you do in your design notebooks. Much of the work we are doing will be helpful for your project.

Deskripsi Asli:

Judul Asli

20071010105801!Lecture07 FET Matching Networks

Hak Cipta

© © All Rights Reserved

Format Tersedia

DOC, PDF, TXT atau baca online dari Scribd

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniWe will look at how we can design matching networks to design a high gain amplifier using simultaneous conjugate matching. You make sure that you keep track of the work you do in your design notebooks. Much of the work we are doing will be helpful for your project.

Hak Cipta:

© All Rights Reserved

Format Tersedia

Unduh sebagai DOC, PDF, TXT atau baca online dari Scribd

0 penilaian0% menganggap dokumen ini bermanfaat (0 suara)

4 tayangan3 halaman20071010105801!lecture07 FET Matching Networks

Diunggah oleh

Luis AlbertoWe will look at how we can design matching networks to design a high gain amplifier using simultaneous conjugate matching. You make sure that you keep track of the work you do in your design notebooks. Much of the work we are doing will be helpful for your project.

Hak Cipta:

© All Rights Reserved

Format Tersedia

Unduh sebagai DOC, PDF, TXT atau baca online dari Scribd

Anda di halaman 1dari 3

ELEC 483-Microwave & RF Circuits & Systems

FET Matching Networs

We will look at how we can design matching networks to design a high gain amplifier using

simultaneous conjugate matching.

You make sure that you keep track of the work you do in your design notebooks. Much of the work we

are doing will be helpful for your project.

Part I: Simple matching network

In this part, you will create a simple matching network to match the input of your transistor, at your

design frequency, to a 5 ohm source.

!. "pen the #$% project elec483_2006_prj, and then open the schematic

SP_NF_GainMatchK.dsn. %imulate your transistor, ensuring that the %&#'& and %&"(

frequencies include your design frequency. In the data display window, select the S

!arameters" #rou$ %e&ay page, and put a marker on the %!! plot. )ote the *alue of %!! for

your transistor. &his is also +amma,in for your transistor, when the output is terminated in a 5

"hm load.

-. .sing the *alue of %!! for your transistor, add a two element /0section matching network

between the input of the transistor and the decoupling capacitor 1- so that the input reflection

coefficient 2i.e. %!!3 is as close to 4ero as possible at your design frequency. &hink about the

effect of your matching network on the bias conditions of the 56&. #dd a rectangular plot to the

data display window, and plot %!! in d7. You should be able to get %!! below 0- d7 at your

design frequency.

8. Make note of the matching network that you designed in your design log. &his may be helpful

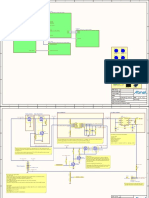

to you later on. #lso sketch the matching network below, and show the %!! below.

#nswers9

ELEC 483-Microwave & RF Circuits & Systems

FET Matching Networs

Part II: Gain and Matching Networks

In this simulation, you will design /1 matching networks at the input and output of the 56& at your

design frequency.

!. In the pre*ious session, we found that the transistor is potentially unstable at certain frequencies, and

so we stabili4ed the transistor. %ince with this resistor the transistor is unconditionally stable at your

frequency, we will design source and load matching networks to produce simultaneous conjugate

match at the input and output. .sing the procedure from last class, which used the NF, Gain, Stab.

Fact., Matchin page, 2or by looking up the results from the last class in your design notebook:3

determine the source and load impedances that result in a simultaneous conjugate match.

-. 1reate a matching network at the input that produces the necessary source impdance 2or

+amma,M%3 needed by your transistor for a simultaneous conjugate match. "ne way to do this is to

disconnect &6'M! from the transistor, and mo*e your &6'M- element beside it, lea*ing space

between the two for a matching network. &hen add the appropriate elements, and check that the %--

measured gi*es the *alue you want for +amma,M%.

8. 'epeat this procedure to design the output matching network that produces +amma,M/.

;. Insert the matching networks at the input and output of the 56&. 6nsure that you include the e<tra

stabili4ing resistor. 'econnect the &6'M! and &6'M- elements, and simulate. 6<amine your %0

parameters on the S !arameters" #rou$ %e&ay page. If designed perfectly the first time, you should

see %!! and %-- *ery close to the center of the %mith chart at your design frequency, and

equi*alently dipping quite low in magnitude on a d7 scale. %-! should reach a ma<imum at your

design frequency. If it does not, recheck your matching networks.

5. %ketch your matching networks here, and show the plots of your final %0parameters 2%!! and %-- on

a %mith chart, and the magnitudes of %!!, %--, %!-, and %-! in d7 on a rectangular plot3.

ELEC 483-Microwave & RF Circuits & Systems

FET Matching Networs

#nswers9

Anda mungkin juga menyukai

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeDari EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifePenilaian: 4 dari 5 bintang4/5 (5794)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreDari EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You ArePenilaian: 4 dari 5 bintang4/5 (1090)

- Never Split the Difference: Negotiating As If Your Life Depended On ItDari EverandNever Split the Difference: Negotiating As If Your Life Depended On ItPenilaian: 4.5 dari 5 bintang4.5/5 (838)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceDari EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RacePenilaian: 4 dari 5 bintang4/5 (895)

- Grit: The Power of Passion and PerseveranceDari EverandGrit: The Power of Passion and PerseverancePenilaian: 4 dari 5 bintang4/5 (588)

- Shoe Dog: A Memoir by the Creator of NikeDari EverandShoe Dog: A Memoir by the Creator of NikePenilaian: 4.5 dari 5 bintang4.5/5 (537)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersDari EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersPenilaian: 4.5 dari 5 bintang4.5/5 (344)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureDari EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FuturePenilaian: 4.5 dari 5 bintang4.5/5 (474)

- Her Body and Other Parties: StoriesDari EverandHer Body and Other Parties: StoriesPenilaian: 4 dari 5 bintang4/5 (821)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Dari EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Penilaian: 4.5 dari 5 bintang4.5/5 (121)

- The Emperor of All Maladies: A Biography of CancerDari EverandThe Emperor of All Maladies: A Biography of CancerPenilaian: 4.5 dari 5 bintang4.5/5 (271)

- The Little Book of Hygge: Danish Secrets to Happy LivingDari EverandThe Little Book of Hygge: Danish Secrets to Happy LivingPenilaian: 3.5 dari 5 bintang3.5/5 (400)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyDari EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyPenilaian: 3.5 dari 5 bintang3.5/5 (2259)

- The Yellow House: A Memoir (2019 National Book Award Winner)Dari EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Penilaian: 4 dari 5 bintang4/5 (98)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaDari EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaPenilaian: 4.5 dari 5 bintang4.5/5 (266)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryDari EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryPenilaian: 3.5 dari 5 bintang3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnDari EverandTeam of Rivals: The Political Genius of Abraham LincolnPenilaian: 4.5 dari 5 bintang4.5/5 (234)

- On Fire: The (Burning) Case for a Green New DealDari EverandOn Fire: The (Burning) Case for a Green New DealPenilaian: 4 dari 5 bintang4/5 (74)

- Examen de Inglés BásicoDokumen27 halamanExamen de Inglés BásicoLuis AlbertoBelum ada peringkat

- The Unwinding: An Inner History of the New AmericaDari EverandThe Unwinding: An Inner History of the New AmericaPenilaian: 4 dari 5 bintang4/5 (45)

- Rise of ISIS: A Threat We Can't IgnoreDari EverandRise of ISIS: A Threat We Can't IgnorePenilaian: 3.5 dari 5 bintang3.5/5 (137)

- CCTV Basics: Adept Designs PVT LTDDokumen41 halamanCCTV Basics: Adept Designs PVT LTDsyedriyazzz100% (4)

- Lab 1 To Lab 3Dokumen10 halamanLab 1 To Lab 3Harish Prakash0% (1)

- LoveDokumen1 halamanLoveLuis AlbertoBelum ada peringkat

- Ecuacion de OndaDokumen2 halamanEcuacion de OndaLuis AlbertoBelum ada peringkat

- Ecuacion de OndaDokumen2 halamanEcuacion de OndaLuis AlbertoBelum ada peringkat

- DFP - Diyfoa : F4U Corsair: Plans - Assembly Instructions F4U Corsair: Plans - Assembly InstructionsDokumen6 halamanDFP - Diyfoa : F4U Corsair: Plans - Assembly Instructions F4U Corsair: Plans - Assembly InstructionsLuis AlbertoBelum ada peringkat

- Modulation Power BandwidthDokumen7 halamanModulation Power BandwidthTestronic PartsBelum ada peringkat

- S Domain ElementsDokumen2 halamanS Domain ElementsLuis AlbertoBelum ada peringkat

- Transmission LinesDokumen32 halamanTransmission LinesLuis AlbertoBelum ada peringkat

- Transmisor TH7107Dokumen1 halamanTransmisor TH7107Luis AlbertoBelum ada peringkat

- Alphanumeric App NotesDokumen15 halamanAlphanumeric App NotesJose PerezBelum ada peringkat

- Inaoe LogoDokumen1 halamanInaoe LogoLuis AlbertoBelum ada peringkat

- RosarioDokumen2 halamanRosarioLuis AlbertoBelum ada peringkat

- Ejemplo de La Biblia en LatexDokumen5 halamanEjemplo de La Biblia en LatexLuis AlbertoBelum ada peringkat

- 01225681Dokumen3 halaman01225681Luis AlbertoBelum ada peringkat

- CH37BDokumen2 halamanCH37BLuis AlbertoBelum ada peringkat

- "Thru-Reflect-Line": An Improved Technique For Calibrating The Dual Six-Port Automatic Network AnalyzerDokumen7 halaman"Thru-Reflect-Line": An Improved Technique For Calibrating The Dual Six-Port Automatic Network Analyzercoasterfreak1029Belum ada peringkat

- Age of EmpiresDokumen21 halamanAge of EmpiresLuis AlbertoBelum ada peringkat

- Title PagesDokumen51 halamanTitle PagesLuis AlbertoBelum ada peringkat

- The Not So Short Introduction To LaTeXDokumen153 halamanThe Not So Short Introduction To LaTeXoetiker100% (3)

- VocabularyDokumen1 halamanVocabularyLuis AlbertoBelum ada peringkat

- SsopDokumen2 halamanSsopLuis AlbertoBelum ada peringkat

- Current Harmonic Analysis of Multi Pulse Diode Rectifiers With Phase Shifting TransformerDokumen5 halamanCurrent Harmonic Analysis of Multi Pulse Diode Rectifiers With Phase Shifting TransformerJakka VenkatBelum ada peringkat

- Tr-4211 NetApp Storage Performance PrimerDokumen42 halamanTr-4211 NetApp Storage Performance Primernetapp000444Belum ada peringkat

- Viper 12ADokumen21 halamanViper 12Aahmed hussainBelum ada peringkat

- Battery Charge MonitorDokumen3 halamanBattery Charge MonitorchakralabsBelum ada peringkat

- GPRS Session 4 Power Control Twn01Q4Dokumen18 halamanGPRS Session 4 Power Control Twn01Q4Nguyen LeBelum ada peringkat

- The Role of Memory in The ComputerDokumen6 halamanThe Role of Memory in The ComputerabcdBelum ada peringkat

- 10 Documentatie Regulator ESM-9950 (Engleza)Dokumen125 halaman10 Documentatie Regulator ESM-9950 (Engleza)emilBelum ada peringkat

- Plama Samsunh bn44Dokumen119 halamanPlama Samsunh bn44Julian Andres RozoBelum ada peringkat

- Components For Pneumatic Automation: Five ONEDokumen26 halamanComponents For Pneumatic Automation: Five ONEamBelum ada peringkat

- Samyung BNW 50Dokumen2 halamanSamyung BNW 50Aldrine Dela CruzBelum ada peringkat

- Tongyu Antenna Catalogue 2017 enDokumen207 halamanTongyu Antenna Catalogue 2017 enRaja Bilal LatifBelum ada peringkat

- Resolver-Based Motor Control Reference Design With A BLDC Motor and C2000™ MCUDokumen42 halamanResolver-Based Motor Control Reference Design With A BLDC Motor and C2000™ MCUStelian CrisanBelum ada peringkat

- NCP3488 MOSFET Driver With Dual Outputs For Synchronous Buck ConvertersDokumen7 halamanNCP3488 MOSFET Driver With Dual Outputs For Synchronous Buck ConvertersRoidysBelum ada peringkat

- 60LB5900UVDokumen43 halaman60LB5900UVfjeroBelum ada peringkat

- Chapter 1 NewDokumen28 halamanChapter 1 NewGemechu B. JiruBelum ada peringkat

- Engine Control Unit, ECU 100Dokumen8 halamanEngine Control Unit, ECU 100MasErn100% (1)

- Amp Design August 2005Dokumen51 halamanAmp Design August 2005Nguyễn Văn Hoà HoàBelum ada peringkat

- DX DiagDokumen36 halamanDX Diagm ikhsanBelum ada peringkat

- Daniel Gruss Slides Training PDFDokumen249 halamanDaniel Gruss Slides Training PDFMircea PetrescuBelum ada peringkat

- TV Troubleshooting Guide v1 1 PDFDokumen8 halamanTV Troubleshooting Guide v1 1 PDFPedro Alarcon100% (2)

- DADokumen40 halamanDAkrishneel sharmaBelum ada peringkat

- سلايدات م. سامر عبدالله صادق- تصميم المنطق الرقميDokumen287 halamanسلايدات م. سامر عبدالله صادق- تصميم المنطق الرقميAzzam SalehBelum ada peringkat

- OptimDokumen16 halamanOptimAverage Ayul EnjoyerBelum ada peringkat

- Pushpamalar Mukilan MFKE2008Dokumen135 halamanPushpamalar Mukilan MFKE2008honggiang13Belum ada peringkat

- Switching Regulator Applications: Absolute Maximum RatingsDokumen2 halamanSwitching Regulator Applications: Absolute Maximum RatingsValdir KoxinhaprBelum ada peringkat

- B.Tech - ECE Syllabus For Students Joined 2014 15 OnwardsDokumen188 halamanB.Tech - ECE Syllabus For Students Joined 2014 15 OnwardsKasi DuraiBelum ada peringkat

- SAMD21 Xplained Pro Design Documentation Release Rev2Dokumen16 halamanSAMD21 Xplained Pro Design Documentation Release Rev2Dimas Agung DwiparonaBelum ada peringkat

- ADUM5401Dokumen28 halamanADUM5401Muhammad Fakhrur RijalBelum ada peringkat