130nm CMOS Technology Design of Passive UHF RFID Tag in

Diunggah oleh

Duc DucDeskripsi Asli:

Judul Asli

Hak Cipta

Format Tersedia

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniHak Cipta:

Format Tersedia

130nm CMOS Technology Design of Passive UHF RFID Tag in

Diunggah oleh

Duc DucHak Cipta:

Format Tersedia

130nm CMOS Technology

Yang Hong, Chi Fat Chan, Jianping Guo, Yuen Sum Ng, Weiwei Shi, Lai Kan Leung, Ka Nang Leung,

Chiu Sing Choy and Kong Pang Pun

Department of Electronic Engineering,

The Chinese University of Hong Kong, Shatin N.T, Hong Kong

yhong@ee.cuhk.edu.hk; knleung@ee.cuhk.edu.hk

Abstract This paper presents a low-power, passive, UHF RFID

tag design compatible with EPC

TM

C1G2 protocol. In order to

reduce its cost, diode-connected NMOS in a standard CMOS

technology is used instead of Schottky diodes. With the help of

low-threshold-voltage, triple-well NMOS, a minimum input

power of -7.6dBm is achieved. A sub-1V, low temperature-

coefficient voltage reference using self-biased mutual

compensation is proposed without large resistors to save the

chip area. In addition, an energy-aware irregular clock

structure, together with clock gating, achieves low power

consumption in the baseband processor. The whole tag is

implemented in a 130nm CMOS technology and the total chip

area is 1200umx1220um.

I. INTRODUCTION

Passive UHF RFID distinguishes itself from others in the

near field item-level tagging applications, mainly due to its

high data rates, small antenna sizes and low costs. To lower

the tag cost to a few cents for wide applications, such as

supply chain management, chip area for tags is one of the

crucial considerations [1]. Apart from its cost, low power

consumption is also required for passive UHF RFID, not only

due to the passive working principles, but also for a longer

operating range in the order of several meters or even longer

[2]. As the RF signal power decreases rapidly with its

communication distance, the induced voltage across the

antenna is quite small, typically in the order of 200mV [2].

This means micro-power rectifier has to function properly

with such low input voltages. Moreover, the voltage reference

following the rectifier needs to be optimized for low voltage

operation to reduce the burden on the rectifier.

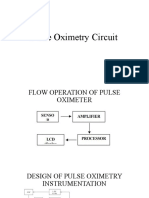

Fig. 1 shows the diagram of the proposed tag IC. The

rectifier, regulator, demodulator, modulator, clock generator

and the baseband processor are all integrated into the tag IC

and put onto the same chip. The rectifier, using low-threshold-

voltage, triple-well NMOS to reduce the required minimum

input voltage, will be proposed in Section II. The self-biased,

resistor-less bandgap voltage reference using mutual

compensation, which achieves sub-1V operation with low

temperature coefficient will be presented in Section III. The

clock generator together with ASK modulator and

demodulator will be introduced in Section IV. Section V will

discuss the design of the baseband processor using energy-

aware, irregular clock structure together with clock gating to

achieve good power saving. Finally, Section VI is the

conclusion of the design.

Fig.1 Passive UHF RFID tag diagram

II. RECTIFIER

The rectifier converts the input AC voltage into DC

voltage, which is further regulated by the voltage regulator to

provide power supply to the circuits in the tag. The single-

stage structure and the simplified circuit diagram for the

CMOS rectifier are shown in Fig. 2a and Fig. 2b,

respectively. Low threshold-voltage NMOSFET is chosen to

minimize the conduction loss of the rectifier. Compared with

the case using Schottky diodes, the utilized approach saves

the fabrication cost for extra masks the Schottky diode needs.

(a) (b)

Fig. 2 (a) single-stage structure (b) circuit of the proposed rectifier

A 16-stage rectifier is designed to generate an output

voltage of 1.3V from the worst-case of input peak-to-peak

Design of Passive UHF RFID Tag in

This work was supported by the Innovative Technology Commission

(GHS/020/06), Hong Kong.

1371 978-1-4244-2342-2/08/$25.00 2008 IEEE.

voltage of 180mV under the condition of 50- input

impedance. T The minimum input power entering the rectifier

is -7.6dBm, and the optimum area for the rectifier is 1200m

x 600m.

III. REGULATOR

Voltage regulator provides stable power supply to front-

end and other circuits. Moreover, the tag should function

properly when there is very little or even no RF power

available during backscattering [3]. A voltage regulator,

shown in Fig. 3, including voltage reference, bias current

generator, low dropout (LDO) convertor and power-on-rest

(POR) circuit (not displayed), is used in the tag design.

Fig. 3 Proposed LDO voltage regulator

A Bandgap voltage reference is used mainly due to its low

temperature coefficient (tempco) and high reliability in most

cases. Conventional bandgap voltage reference suffers low

voltage issue under sub-1V operation since the bandgap

voltage is around 1.25V. Although there are many new

structures proposed [4], it is not favorable to use bandgap

voltage reference in passive RFID tag design because the

very large resistor, up to tens of mega Ohm, is needed to

achieve ultra low quiescent current down to sub-1A, or even

tens of nano-ampere.

To achieve sub-1V operation with low tempco, a voltage

reference using self-biased mutual thermal compensation is

adopted without large resistors to save area and reduce

parasitic capacitance. The reference voltage is equal to [5].

+ =

L

W

C

I

V V

ox n

D

TH REF

2

(1)

With proper bias current I

D

, zero tempco can be achieved

by compensating the tempco of V

TH

and

n

. A self-biased

current generator is introduced to save power more

effectively. A startup circuit is included to initiate the circuit

after powering on. There are two feedback loops. One is

negative, coming from OP

1

and M

1

, while another is positive,

coming from OP

1

and M

1

M

4

. A large MOS capacitor M

C1

,

is used to slow down the speed to make the circuit stable.

Simulation results are shown in Fig. 4. The reference voltage

is 470mV at 27C with 25ppm/C tempco, while the tempco

of bias current is 550ppm/C. To get proper I

D

to lower the

tempco, a trimming strategy to resistor R

1

is introduced.

To save power and simplify the compensation of the LDO

converter, a single stage amplifier is adopted to drive the

power PMOSFET directly. The NMOSFET input transistors

work in sub-threshold region for low-voltage (sub-1V) and

low-power operation. A 1-nF MOS capacitor is used to store

sufficient charge to power up the tag when there is very little

or even no RF power available to the chip during

backscattering. The simulated load transient response of the

voltage regulator is shown in Fig. 5. The proposed regulator

can recover within 3 s with only 1mV voltage spike when

the loading current changes from 1A to 10A. Moreover, it

can also work well under 50A load transient change. To

save chip area, seven PMOS transistors with substrate

connected to the source terminal are used as a potential

divider to be the output feedback network.

The total quiescent current of the voltage regulator,

including trimming and POR circuits, is 0.73A at room

temperature when input voltage is 1.2V. The regulated output

voltage is 1.1V, which are the typical operational condition.

-20 0 20 40 60 80 100

0.4685

0.469

0.4695

0.47

0.4705

Temperature (degree)

R

e

f

e

r

e

n

c

e

V

o

l

t

a

g

e

V

R

E

F

(

V

)

-20 0 20 40 60 80 100

5.8

5.9

6

6.1

6.2

x 10

-8

I

b

i

a

s

(

A

)

VREF

Ibias

Fig. 4 Reference voltage and bias current vs. temperature

6 6.1 6.2 6.3 6.4 6.5 6.6 6.7

x 10

-4

1.07

1.08

1.09

1.1

1.11

Time (s)

V

O

U

T

(

V

)

6 6.1 6.2 6.3 6.4 6.5 6.6 6.7

x 10

-4

0

2

4

6

x 10

-5

Time (s)

I

O

U

T

(

A

)

Fig. 5 Load transient response of the voltage regulator

IV. CLOCK, ASK DEMODULATOR & MODULATOR

In analog domain, most of power consumed in the RFID

tag is by the oscillator [6]. To comply with the EPC C1G2

protocol, the clock frequency tolerance is required to be

within 4% under nominal temperature [7]. The largest

source of frequency variation comes from the variation in the

supply voltage since the incoming RF energy is weak and

1372

unstable. To strike a balance among power consumption,

frequency accuracy, and die area, a five-stage current-starved

ring oscillator is proposed, as shown in Fig. 6. The oscillator

consumes a maximum power of 500nW with frequency

variation being 0.6% when the supply voltage changes from

0.65V to 1.3V.

It is mentioned in [8] that 1.92MHz is the minimum

frequency required to decode the incoming PIE data correctly

according to the EPC C1G2 specification. To leave sufficient

margin, a frequency of 4MHz is selected.

Fig. 7 shows the ASK demodulator, which is composed of

an envelope detector and a voltage comparator. M

1

M

4

are

low-threshold transistors, while M

5

M

8

are normal ones.

The number of stages to generate V

env

and V

ref

is the same,

and the ideal values with no loading [2] are

) ( 5 . 2

low T in env

V RF V = (2)

) ( 5 . 2

nor T in ref

V RF V = (3)

VDD

Mb1

VDD

VSS

Mb

2

Ib

VDD

Vo Level

Converter

VSS

VSS

Fig. 6 Current starved ring oscillator

Fig. 7 Envelope detector

When input signal is applied to the RF

in

terminal, V

env

is

higher than V

ref

due to lower the threshold voltage of M

1

M

3

.In the absence of input signal, C

3

discharges through M

4

,

and C

6

discharges through M

8

. As diode-connected M

4

has a

lower threshold voltage, C

3

discharges faster than V

ref

. ASK

demodulation is completed after feeding V

env

and V

ref

to a

voltage comparator. The simulated output of the envelope

detector with RF

in

= 150mV

pk

and modulation index of 0.2at

900MHz is shown in Fig.8.

The modulator of the tag sends its replies to the RFID

reader by backscattering. This can be achieved by modulating

the input impedance of the tag when the RFID reader is

sending a continuous wave to it. In this work, ASK

modulation is chosen. Since high input impedance of the tag

reflects the continuous wave back to the reader while low

input impedance absorbs the wave, a switch is added at the

input of the tag IC. The difference of the two impedances is

given by

) // ( ) // (

tag ON SW tag OFF SW diff

Z Z Z Z Z

= (4)

Increase of the value of Z

diff

eases the detection of the

backscattering signal in the reader. For the maximum Z

diff

, the

optimal W/L aspect ratio of the switch is 42um/0.12um.

0 0.5 1 1.5 2 2.5

x 10

-5

-0.05

0

0.05

0.1

0.15

0.2

Time (s)

V

o

l

t

a

g

e

(

V

)

Venv

Vref

Fig. 8 Simulated output of the envelope detector

V. BASEBAND PROCESSOR

One of the constraints in the baseband processor design is

the limited power consumption under low supply voltage.

Another constraint is the weak wireless input from the RFID

reader. The input is prone to interference and data integrity is

a critical issue in the processor design [9]-[11]. Moreover, the

input is in a serial, PIE format [12]. Thus, the throughput of

the processor is limited.

The block diagram of the proposed baseband processor is

shown in Fig. 9. The data flow of the processor is based on

the input-verify-respond steps. Input PIE_LEN_COUNTER

is the extracted time value from the Demodulator. In the PIE

Decoding block, the preamble, frame and PIE data embedded

in the input is identified and decoded. When error is detected,

the whole circuit goes back to the ready state. In order to

increase the efficiency of the baseband processor, reception

and verification of the input data is implemented in a

pipelined manner.

To achieve good power saving, an energy-aware, irregular

clock is used in this design. As shown in Fig. 9, the

conventional command handler is partitioned into two parts.

One part, including the PIE Decoding block and the

Command Receiving block, is triggered by an irregular clock,

PIE_CLK. The remaining part, the Command Processing

block, is triggered by a regular clock, CMD_PROC_CLK. As

shown in Fig. 10, pulses with width of 20ns in the irregular

clock, PIE_CLK, are synchronized by the rising edges in the

1373

envelope of the RF signal. Because the energy supply is

abundant after the rising edge of the RF envelope, the clock

can easily trigger the PIE Decoding block and Command

Receiving block without any interruption in the power supply.

The regular clock, CMD_PROC_CLK, comes from the ring

oscillator outputs. Its frequency (62.5kHz ~ 500kHz) is equal

to the link frequency for the backscattering signal,

FM0_DATA.

To reduce dynamic power dissipation, Clock Gating

blocks (CK_G) are added into the design to stop the

propagation of the clocks when the blocks are in the idle

state. The structure of CK_G is shown in Fig. 11. Because all

the blocks are triggered at rising edge, CK_G can also avoid

the racing condition, which may cause failure of operation.

Table I summarizes the key performance of the baseband

processor. With the partition of the command handler, the

application of energy-aware, irregular clock and the use of

clock gating, the power consumption of the baseband

processor is only 1.1W. Efficiency of the baseband

processor is also increased under such low power

consumption by the pipelined architecture.

Fig. 9 Block diagram of baseband processor

Fig. 10 Timing steps with irregular clock

Fig. 11 Clock gating circuit (CK_G)

Table I Summary of Baseband Processor

Function Implemented Inventory (Query Command)

Area 215m 115m (Core & Buf.)

Leakage Power 700pW (EDA estimation)

Power Consumption 1.1W (EDA estimation)

VI. CONCLUSION

A low-voltage, low-power, cost-effective, passive UHF

RFID tag design has been proposed in this paper. It is

implemented in a 130nm CMOS technology and occupies an

area of 1200m 1220m. For the proposed rectifier, a

minimum input power of -7.6dBm is achieved by using

NMOS with low threshold voltage to reduce both cost and

input power. A low-tempco voltage reference using bias

mutual compensation is proposed for sub-1V operation

without using large resistors to save chip area. Energy-aware

irregular clock structure in the proposed baseband processor

together with clock gating helps to achieve good power

saving. All circuits have been designed in a 130nm CMOS

technology to satisfy EPC C1G2 protocol with emphasis on

reduction of both the power consumption and silicon area.

Simulations were done to verify all the proposed ideas.

REFERENCES

[1] M. Roberti, A 5-cent breakthrough, http://www.rfidjournal.com.

[2] T. Umeda, H. Yoshida, S. Sekine, Y. Fujita, T. Suzuki and S. Otaka,

A 950-MHz Rectifier Circuit for Sensor Network Tags With 10-m

Distance, IEEE J. Solid-State Circuits, vol. 41, pp. 35-41, Jan.2006.

[3] G. K.Baachandran and R. E.Barnett, A 110nA Voltage Regulator

System with Dynamic Bandwidth Boosting for RFID Systems, IEEE

J. Solid-State Circuits, vol. 41, pp. 2019-2028, Sep.2006.

[4] K. N. Leung and P. K. T. Mok, A sub-1V 15ppm/C CMOS bandgap

voltage reference without requiring low threshold voltage device,

IEEE J. Solid-State Circuits, vol.37, pp. 526-530, Apr. 2002.

[5] I. M.Filanovsky and A. Allam, Mutual Compensation of Mobility and

Threshold Voltage Temperature Effects with Application in CMOS

Circuits, IEEE Trans. Circuits Syst. I, vol.48, pp. 876-884, Jul. 2001.

[6] J. P. Curty, M. Declercq, C. Dehollain, N. Joehl Design and

Optimization of Passive UHF RFID Systems, Springer, 2007.

[7] EPC Radio-Frequency Identity Protocols Class-1 Generation-2 UHF

RFID Protocol for Communications at 860 MHz 960MHz,

http://www.epcglobalinc.org, 2005.

[8] Gen 2 Tag Clock Rate What You Need to Know,

http://www.impinj.com.

[9] Adam S.W. Man, Edward S. Zhang, H.T. Chan, Vincent K.N. Lau,

C.Y. Tsui and Howard C. Luong, Design and Implementation of a

Low-power Baseband-system for RFID Tag, in proc. ISCAS, pp.

1585-1588, 2007

[10] A. Ricci, M. Grisanti, I. De Munari, P. Ciapolini, Design of a Low-

Power Digital Core for Passive UHF RFID Transponder, in proc. 9th

EUROMICRO Conference on Digital System Design, pp. 561-568,

2006.

[11] Y. He, J. Hu, Q. Li, H. Min, Design of Low-power Baseband-

processor for RFID Tag, in proc. of the International Symposium on

Applications on Internet Workshops, pp. 60-63, Jan. 2006.

[12] EPCglobal Inc, EPC Radio-Frequency Identity Protocols: Class-1

Generation-2 UHF RFID Protocol for Communications at 860 MHz

960MHz Version 1.0.9, Jan. 2005.

1374

Anda mungkin juga menyukai

- 06616415Dokumen5 halaman06616415jitu_4Belum ada peringkat

- Power Harvester Design For Semi-Passive UHF RFID Tag Using A Tunable Impedance TransformationDokumen5 halamanPower Harvester Design For Semi-Passive UHF RFID Tag Using A Tunable Impedance TransformationM ABelum ada peringkat

- U-93 Application NOTE A New Integrated Circuit For Current Mode ControlDokumen9 halamanU-93 Application NOTE A New Integrated Circuit For Current Mode ControlpramodBelum ada peringkat

- AND8241/D A 5.0 V/2.0 A Standby Power Supply For INTEL Compliant ATX ApplicationsDokumen16 halamanAND8241/D A 5.0 V/2.0 A Standby Power Supply For INTEL Compliant ATX ApplicationsJonatan LunaBelum ada peringkat

- Application Note 91 October 2002: Note 1: This Method Has Been Tested With The LTC4401-1 and TheDokumen8 halamanApplication Note 91 October 2002: Note 1: This Method Has Been Tested With The LTC4401-1 and TheHahdBelum ada peringkat

- A Monolithic Dual Channel 0.5 To 20 GHZ LimiterDokumen4 halamanA Monolithic Dual Channel 0.5 To 20 GHZ Limiteragmnm1962Belum ada peringkat

- Op-Amps and Startup Circuits For CMOS Bandgap References With Near 1-V SupplyDokumen5 halamanOp-Amps and Startup Circuits For CMOS Bandgap References With Near 1-V Supplynivia25Belum ada peringkat

- Low Power High Speed I/O Interfaces in 0.18um CmosDokumen4 halamanLow Power High Speed I/O Interfaces in 0.18um Cmosayou_smartBelum ada peringkat

- Viper22a Equivalent PDFDokumen16 halamanViper22a Equivalent PDFXande Nane Silveira0% (1)

- Uc3842 Provides Low-Cost Current-Mode Control: Application NoteDokumen16 halamanUc3842 Provides Low-Cost Current-Mode Control: Application NoteLeonardo Ortiz100% (1)

- Waveform Generator Circuit Explain PDFDokumen37 halamanWaveform Generator Circuit Explain PDFMio2008Belum ada peringkat

- A 5.8-Ghz High Efficient, Low Power, Low Phase Noise Cmos Vco For Ieee 802.11ADokumen4 halamanA 5.8-Ghz High Efficient, Low Power, Low Phase Noise Cmos Vco For Ieee 802.11ARitika SinghBelum ada peringkat

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Dari EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Belum ada peringkat

- Motorola AN758Dokumen16 halamanMotorola AN758xavir111Belum ada peringkat

- SW - Buck - 1 Application Report: Topology: Non Synchronous Buck Converter Controller: Texas Instruments TPS40200Dokumen25 halamanSW - Buck - 1 Application Report: Topology: Non Synchronous Buck Converter Controller: Texas Instruments TPS40200Ion AvramBelum ada peringkat

- AN4102 (Uso 3S0680RF)Dokumen20 halamanAN4102 (Uso 3S0680RF)Cintya CardozoBelum ada peringkat

- A 900Mhz RF Energy Harvesting Module: Taris Thierry, Vigneras Valérie Fadel LudivineDokumen4 halamanA 900Mhz RF Energy Harvesting Module: Taris Thierry, Vigneras Valérie Fadel Ludivinekavirasu1990Belum ada peringkat

- Ultra-Low Power Phase-Locked LoopDokumen4 halamanUltra-Low Power Phase-Locked Loophawking1122Belum ada peringkat

- 20116052-Lica Term ProjectDokumen12 halaman20116052-Lica Term ProjectH052 Rajesh Komaravalli ECEBelum ada peringkat

- Ultra-Low: Power Silicon-on-Sapphire Energy-ScavengingDokumen4 halamanUltra-Low: Power Silicon-on-Sapphire Energy-ScavengingGurkaranjot SinghBelum ada peringkat

- A Low Power, and Low Signal 5-Bit 25msamples/s Pipelined ADC For Monolithic Active PixelsDokumen5 halamanA Low Power, and Low Signal 5-Bit 25msamples/s Pipelined ADC For Monolithic Active Pixelstajmjcet_123Belum ada peringkat

- 5.11 A 65nm Inverter-Based Low-Dropout Regulator With Rail-to-Rail Regulation and Over - 20dB PSR at 0.2V Lowest Supply VoltageDokumen3 halaman5.11 A 65nm Inverter-Based Low-Dropout Regulator With Rail-to-Rail Regulation and Over - 20dB PSR at 0.2V Lowest Supply Voltageeng_abdelghany1979Belum ada peringkat

- Design and Analysis of A Low Power Passive UHF RFID Transponder ICDokumen6 halamanDesign and Analysis of A Low Power Passive UHF RFID Transponder ICAli ErenBelum ada peringkat

- Class D Com FonteDokumen29 halamanClass D Com FontenicchioBelum ada peringkat

- A Complete Narrow-Band Power Line Communication Node For AMRDokumen6 halamanA Complete Narrow-Band Power Line Communication Node For AMRSudheer KakaniBelum ada peringkat

- 3-Phase PFC KolarDokumen7 halaman3-Phase PFC KolarJayant SalianBelum ada peringkat

- Iraudamp1 PDFDokumen22 halamanIraudamp1 PDFamijoski6051Belum ada peringkat

- A New Low Voltage, High PSRR, Cmos Bandgap Voltage ReferenceDokumen4 halamanA New Low Voltage, High PSRR, Cmos Bandgap Voltage ReferenceBodhayan PrasadBelum ada peringkat

- A Novel 1.5V DC Offset Cancellation CMOSDokumen4 halamanA Novel 1.5V DC Offset Cancellation CMOSJebreel SalemBelum ada peringkat

- Pulse Oximetry CircuitDokumen19 halamanPulse Oximetry Circuitنواف الجهنيBelum ada peringkat

- AND8099/D 5.0 V, 2.0 A Flyback Converter: Application NoteDokumen8 halamanAND8099/D 5.0 V, 2.0 A Flyback Converter: Application NoteIgor MairinckBelum ada peringkat

- AN-4102: Colour TV Receiver SMPSDokumen16 halamanAN-4102: Colour TV Receiver SMPSshri.bhairavkar6977Belum ada peringkat

- Low Voltage Smart Temperature Sensor Front End: Abstract-In This Brief, A Low Voltage Low Power CMOSDokumen5 halamanLow Voltage Smart Temperature Sensor Front End: Abstract-In This Brief, A Low Voltage Low Power CMOSBruno SilvaBelum ada peringkat

- Auto Shut OffDokumen5 halamanAuto Shut OffJuan Manuel Han MacBelum ada peringkat

- PWM Fan ControllerDokumen5 halamanPWM Fan ControlleranandBelum ada peringkat

- UC3842 Inside SchematicsDokumen17 halamanUC3842 Inside Schematicsp.c100% (1)

- 12AX7 6V6 Single Ended Class A Tube Amplifier Design and ConstructionDokumen11 halaman12AX7 6V6 Single Ended Class A Tube Amplifier Design and ConstructionOz Heat86% (7)

- Linear Amps For Mobile OperationDokumen10 halamanLinear Amps For Mobile OperationIan McNairBelum ada peringkat

- Design of A Low-Dropout Linear RegulatorDokumen4 halamanDesign of A Low-Dropout Linear RegulatorParindraBelum ada peringkat

- Application Note AN-4150: Design Guidelines For Flyback Converters Using FSQ-series Fairchild Power Switch (FPS™)Dokumen16 halamanApplication Note AN-4150: Design Guidelines For Flyback Converters Using FSQ-series Fairchild Power Switch (FPS™)Nagendra ChaitanyaBelum ada peringkat

- New 1600V BIMOSFET TransistorsDokumen10 halamanNew 1600V BIMOSFET TransistorsCristian BandilaBelum ada peringkat

- An 4134Dokumen14 halamanAn 4134shri.bhairavkar6977Belum ada peringkat

- Iraudamp 1Dokumen22 halamanIraudamp 1luizcpimentaBelum ada peringkat

- 8 ModulationDokumen8 halaman8 ModulationAhmadAkhbariBelum ada peringkat

- Design Guideline of AC-DC Converter Using FL6961 & FL6300A For 70W LED LightingDokumen13 halamanDesign Guideline of AC-DC Converter Using FL6961 & FL6300A For 70W LED Lightingshiva1luBelum ada peringkat

- A Fold-Back Current Limit Circuit With Load-Insensitive Quiescent Current For CMOS Low Dropout RegulatorDokumen4 halamanA Fold-Back Current Limit Circuit With Load-Insensitive Quiescent Current For CMOS Low Dropout Regulatorhjtseng1974Belum ada peringkat

- Aerosemi: Features ApplicationsDokumen9 halamanAerosemi: Features Applicationsttnaing100% (1)

- A 6-b 1-GS/s 30-mW ADC in 90-nm CMOS Technology: Yuan-Ching Lien and Jri Lee National Taiwan University, Taipei, TaiwanDokumen4 halamanA 6-b 1-GS/s 30-mW ADC in 90-nm CMOS Technology: Yuan-Ching Lien and Jri Lee National Taiwan University, Taipei, TaiwanSunil PandeyBelum ada peringkat

- 2008 ICECS - Design On Mixed-Voltage IO Buffers With Slew-Rate Control in Low-Voltage CMOS ProcessDokumen4 halaman2008 ICECS - Design On Mixed-Voltage IO Buffers With Slew-Rate Control in Low-Voltage CMOS ProcessKeerthiBelum ada peringkat

- AN738 Design of A Small, Efficient, Isolated Flyback Converter For 24-V Input Systems With Si9121Dokumen9 halamanAN738 Design of A Small, Efficient, Isolated Flyback Converter For 24-V Input Systems With Si9121Swati DevBelum ada peringkat

- Ecler Pam2000 Pam2600 Power Amplifier Service ManualDokumen107 halamanEcler Pam2000 Pam2600 Power Amplifier Service Manuallluissb92% (12)

- Ieee Delangen 1998Dokumen15 halamanIeee Delangen 1998kurabyqldBelum ada peringkat

- Ultra Low Power Digitally Controlled Buck ConvDokumen9 halamanUltra Low Power Digitally Controlled Buck Convrmsharma1970Belum ada peringkat

- Amplitude Modulation of The AD9850Dokumen2 halamanAmplitude Modulation of The AD9850maruja4Belum ada peringkat

- IEEE - A 1.8V 1MSps Rail-To-Rail 10-Bit SAR ADC in 0.18um CMOS PDFDokumen3 halamanIEEE - A 1.8V 1MSps Rail-To-Rail 10-Bit SAR ADC in 0.18um CMOS PDFQuoc Thang TranBelum ada peringkat

- AV02-2211EN AN - 5442 MGA-17516 07apr2011,0 PDFDokumen24 halamanAV02-2211EN AN - 5442 MGA-17516 07apr2011,0 PDFAnh Bien NguyenBelum ada peringkat

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Dari EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Penilaian: 2.5 dari 5 bintang2.5/5 (3)

- Analog Circuit Design Volume Three: Design Note CollectionDari EverandAnalog Circuit Design Volume Three: Design Note CollectionPenilaian: 3 dari 5 bintang3/5 (2)

- Validating Direct Memory Access Interfaces With Conformance CheckingDokumen8 halamanValidating Direct Memory Access Interfaces With Conformance CheckingDuc DucBelum ada peringkat

- Configuring A Processor For Low-Power IoT Applications PDFDokumen8 halamanConfiguring A Processor For Low-Power IoT Applications PDFDuc DucBelum ada peringkat

- 0907 TsirlineDokumen8 halaman0907 TsirlineDuc DucBelum ada peringkat

- CMOS High Performance Programmable DMA Controller Features: Data Sheet FN2967.4 October 2, 2015Dokumen26 halamanCMOS High Performance Programmable DMA Controller Features: Data Sheet FN2967.4 October 2, 2015Duc DucBelum ada peringkat

- DMADokumen5 halamanDMAPrabir K DasBelum ada peringkat

- Direct - Memory - Access - V1 - 60 - Datasheet PDFDokumen23 halamanDirect - Memory - Access - V1 - 60 - Datasheet PDFDuc DucBelum ada peringkat

- (Ebook - PDF - Electronics) Antenna Circuit Design For RFID Applications (Lee 2003) PDFDokumen50 halaman(Ebook - PDF - Electronics) Antenna Circuit Design For RFID Applications (Lee 2003) PDFmoomoerBelum ada peringkat

- 10 1 1 77 123Dokumen13 halaman10 1 1 77 123Duc DucBelum ada peringkat

- Austriamicrosystems ATA1004Dokumen4 halamanAustriamicrosystems ATA1004Duc DucBelum ada peringkat

- A 20-Gb/s 1: 2 demultiplexer in 0.18-Μm Cmos: Zhang Changchun , Wang Zhigong , Shi Si , and Li WeiDokumen5 halamanA 20-Gb/s 1: 2 demultiplexer in 0.18-Μm Cmos: Zhang Changchun , Wang Zhigong , Shi Si , and Li WeiDuc DucBelum ada peringkat

- An Efficient Layout Style For ThreeDokumen12 halamanAn Efficient Layout Style For Threejhchon2000Belum ada peringkat

- Austriamicrosystems ATA1004Dokumen4 halamanAustriamicrosystems ATA1004Duc DucBelum ada peringkat

- CML PaperDokumen6 halamanCML PaperAhmed El SaidBelum ada peringkat

- Antenna CoilDokumen4 halamanAntenna CoilDuc DucBelum ada peringkat

- An 313Dokumen8 halamanAn 313gurupalmurBelum ada peringkat

- An 313Dokumen8 halamanAn 313gurupalmurBelum ada peringkat

- A High Density MIM Capacitor in A Standard CMOS Process: Christian Rye IversenDokumen4 halamanA High Density MIM Capacitor in A Standard CMOS Process: Christian Rye IversenDuc DucBelum ada peringkat

- A Highly Efficient Power Management System For Charging Mobile Phones Using RF Energy HarvestingDokumen10 halamanA Highly Efficient Power Management System For Charging Mobile Phones Using RF Energy HarvestingijitcsBelum ada peringkat

- RF Modeling of An MOS Varactor and MIM Capacitor in 0.18 - M CMOS TechnologyDokumen5 halamanRF Modeling of An MOS Varactor and MIM Capacitor in 0.18 - M CMOS TechnologyDuc DucBelum ada peringkat

- 2Dokumen11 halaman2Duc DucBelum ada peringkat

- (Ebook - PDF - Electronics) Antenna Circuit Design For RFID Applications (Lee 2003) PDFDokumen50 halaman(Ebook - PDF - Electronics) Antenna Circuit Design For RFID Applications (Lee 2003) PDFmoomoerBelum ada peringkat

- Antenna CoilDokumen4 halamanAntenna CoilDuc DucBelum ada peringkat

- A Unified Model For Injection-Locked Frequency DividersDokumen13 halamanA Unified Model For Injection-Locked Frequency DividersDuc DucBelum ada peringkat

- Integration of A Passive-Type UHF RFID Tag Using Ferroelectric Memory TechnologyDokumen6 halamanIntegration of A Passive-Type UHF RFID Tag Using Ferroelectric Memory TechnologyDuc DucBelum ada peringkat

- 0907 TsirlineDokumen8 halaman0907 TsirlineDuc DucBelum ada peringkat

- Integration of A Passive-Type UHF RFID Tag Using Ferroelectric Memory TechnologyDokumen6 halamanIntegration of A Passive-Type UHF RFID Tag Using Ferroelectric Memory TechnologyDuc DucBelum ada peringkat

- (Ebook - PDF - Electronics) Antenna Circuit Design For RFID Applications (Lee 2003) PDFDokumen50 halaman(Ebook - PDF - Electronics) Antenna Circuit Design For RFID Applications (Lee 2003) PDFmoomoerBelum ada peringkat

- A Unified Model For Injection-Locked Frequency DividersDokumen13 halamanA Unified Model For Injection-Locked Frequency DividersDuc DucBelum ada peringkat

- Near-Field Loop Antenna For The UHF RFID Reader: Peng Yang, Yan Li, Li-Jun Jiang, and Feng YangDokumen5 halamanNear-Field Loop Antenna For The UHF RFID Reader: Peng Yang, Yan Li, Li-Jun Jiang, and Feng YangDuc DucBelum ada peringkat

- 220 JBT Info TestreportsDokumen5 halaman220 JBT Info TestreportsC.H. WEEBelum ada peringkat

- Lab Session: 3: Demonstrate The Behavior of A Silicon Diode in Half Wave RectifierDokumen7 halamanLab Session: 3: Demonstrate The Behavior of A Silicon Diode in Half Wave RectifierFatima AmjadBelum ada peringkat

- Philips 109b7Dokumen90 halamanPhilips 109b7Charly HirschBelum ada peringkat

- Max17126b PDFDokumen34 halamanMax17126b PDFedvanps100% (2)

- CBTP 1Dokumen41 halamanCBTP 1yeabBelum ada peringkat

- Harmonic and FlickerDokumen56 halamanHarmonic and Flickerzombie138Belum ada peringkat

- C79 C57 DDD 01Dokumen3 halamanC79 C57 DDD 01tenisonBelum ada peringkat

- New Generation Three-Phase RectifierDokumen164 halamanNew Generation Three-Phase Rectifierqfcjagu865Belum ada peringkat

- Paperless e Cash Management System by Using An I Button TechnologyDokumen35 halamanPaperless e Cash Management System by Using An I Button TechnologyAmali JayawardhanaBelum ada peringkat

- Telecom Energy BrochureDokumen18 halamanTelecom Energy BrochureahmedBelum ada peringkat

- Power Electronics Application in DC Motor Drives - Case Study - ss03595 - Sarwan Shah PDFDokumen6 halamanPower Electronics Application in DC Motor Drives - Case Study - ss03595 - Sarwan Shah PDFMehdi Raza KhorasaniBelum ada peringkat

- Experiment 3Dokumen3 halamanExperiment 3Abdulmalek AkashaBelum ada peringkat

- 2001-36T Three Phase PWM Boost-Buck Rectifiers With Power Regenerating CapabilityDokumen10 halaman2001-36T Three Phase PWM Boost-Buck Rectifiers With Power Regenerating CapabilitypadarwitoBelum ada peringkat

- Samsung 633nw Ls16cmy SCH PDFDokumen10 halamanSamsung 633nw Ls16cmy SCH PDFeugenio bravataBelum ada peringkat

- Dimension Dwg135NXB3Dokumen36 halamanDimension Dwg135NXB3Anonymous hRePlgdOFrBelum ada peringkat

- Level 2 QuestionDokumen22 halamanLevel 2 QuestionFuaz SukaryaBelum ada peringkat

- Operating Manual: Combo Series CC/CV Based Welding MachineDokumen36 halamanOperating Manual: Combo Series CC/CV Based Welding MachinePascu AurelBelum ada peringkat

- EEE TitleDokumen7 halamanEEE Titlebvkarthik2711Belum ada peringkat

- Operating Instructions: OPTISWITCH 5100 C, 5150 C With Transistor OutputDokumen32 halamanOperating Instructions: OPTISWITCH 5100 C, 5150 C With Transistor OutputNishanth KallingentavidaBelum ada peringkat

- Wear Testing RigDokumen6 halamanWear Testing Rigibson045001256Belum ada peringkat

- EB 01 - 01 Introduccion A La Electronica - (ESPAÑOL)Dokumen40 halamanEB 01 - 01 Introduccion A La Electronica - (ESPAÑOL)IppolitoCaravaggioBelum ada peringkat

- Catalogue-200mA X-Ray MachineDokumen1 halamanCatalogue-200mA X-Ray Machineshoaib tariqBelum ada peringkat

- FR151 - FR157: FeaturesDokumen3 halamanFR151 - FR157: FeatureselsubberBelum ada peringkat

- EEMODS Paper Full.R1Dokumen10 halamanEEMODS Paper Full.R1DungBelum ada peringkat

- KBPC25005/W - KBPC2510/W: 25A Bridge RectifierDokumen2 halamanKBPC25005/W - KBPC2510/W: 25A Bridge RectifierEnzo CeballosBelum ada peringkat

- AEM For Series SE and SEHDokumen30 halamanAEM For Series SE and SEHdimBelum ada peringkat

- 15EC35 - Electronic Instrumentation - Module 4Dokumen33 halaman15EC35 - Electronic Instrumentation - Module 4Anish AnniBelum ada peringkat

- Power System: DPS 2000C-48-3Dokumen2 halamanPower System: DPS 2000C-48-3samBelum ada peringkat

- Single Phase RectifiersDokumen11 halamanSingle Phase RectifiersMiguel MartinezBelum ada peringkat

- IEC Systems Manual - SCRDokumen102 halamanIEC Systems Manual - SCRgabriel100% (3)