EES11 - Power Management

Diunggah oleh

asdsdDeskripsi Asli:

Hak Cipta

Format Tersedia

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniHak Cipta:

Format Tersedia

EES11 - Power Management

Diunggah oleh

asdsdHak Cipta:

Format Tersedia

Embedded Electronic Systems

d

r

a

N

o

l

t

e

,

G

e

s

i

n

e

M

a

r

w

e

d

e

l

,

2

0

0

3

G

r

a

p

h

i

c

s

:

A

l

e

x

a

n

d

Power Issues

Battery Management

Processing units

Need for efficiency (power +energy):

Why worry about

Power is considered as the most important constraint in

embedded systems

[in: L. Eggermont (ed): Embedded Systems Roadmap 2002, STW]

Why worry about

energy and power?

Energy consumption by IT is the key concern of

green computing initiatives

(embedded computing leading the way)

http://www.esa.int/images/earth,4.jpg

Low Power vs. Low Energy Consumption

Minimizing the power consumption is important for

the design of the power supply

the design of voltage regulators

the dimensioning of interconnect

short term cooling

Minimizing the energy consumption is important due to

restricted availability of energy (mobile systems)

limited battery capacities (only slowly improving)

very high costs of energy (solar panels, in space) y g gy ( p , p )

cooling

high costs

limited space

dependability

long lifetimes, low temperatures

Power Consumption in CMOS Digital Logic

Dynamic power consumption

charging and discharging capacitors g g g g p

Short circuit currents

short circuit path between supply rails during

switching

Leakage

leaking diodes and transistors

problem even when in standby!

Power Consumption in CMOS Digital logic

Dynamic power

consumption

Power due to

short-circuit

Power due to

P = AC V

2

f + A I

sw

V f + I

leak

V

where

consumption

short circuit

current during

transition

leakage current

A =activity factor (probability of 0 1 transition)

C =total chip capacitance

V =total voltage swing, usually near the power supply voltage

f =clock frequency

I

sw

=short circuit current when logic level changes

I

leak

=leakage current in diodes and transistors

Dynamic Power Consumption

V Supply voltage

Trend: has been dropping

with each successive fab

C Total capacitance

seen by the gates outputs

Function of wire lengths,

transistor sizes

f ACV

2

A - Activity of gates

How often on average do

wires switch?

f clock frequency

Trend: increasing ...

transistor sizes, ...

Reducing Dynamic Power

1) Reducing V has quadratic effect; Limits?

2) Lower C - shrink structures, shorten wires

3) Reduce switching activity - Turn off unused parts or

use design techniques to minimize number of transitions

Short-circuit Power Consumption

f AVI

short

t

Finite slope of the input signal

causes a direct current path

between V

DD

and GND for a

short period of time during

switching when both the

NMOS and PMOS transistors

Vin Vout

C

L

I

short

short

are conducting

Reducing Short-circuit

1) Lower the supply voltage V

2) Slope engineering match the rise/fall time of the input and output signals

Leakage Power

leak

VI

Sub-threshold current grows exponentiallywith

increases in temperature and decreases in Vt

Sub-threshold

current

How can we reduce

power consumption?

Dynamic power consumption

Reduce the rate of charge/discharge of highly loaded nodes

Reduce spurious switching (glitches)

Reduce switching in idle states (clock gating)

Decrease frequency

Decrease voltage (and frequency)

Static power Consumption

Smaller area (!)

Reduce device leakage through power gating

Reduce device leakage through body biasing Reduce device leakage through body biasing

Use higher-threshold transistors when possible

Power performance tradeoffs!

Why not simply lower V?

Total P can be minimized by lower V

lower V are a natural result of smaller feature sizes

But transistor speeds decrease dramatically as V is

reduced to close to threshold voltage

performance goals may not be met

t

d

=CV / k(V-V

t

)

o

where o is between 1-2

Why not lower this threshold voltage?

makes noise margin and I

leak

worse!

Need to do smarter voltage scaling!

Approaches to Energy Efficiency

P = o C V

2

f

Continuous

Event-Driven

Latency is Important

Only Throughput is

Important

Reduce V

(Burst throughput)

Increase h/w and

algorithmic concurrency

Make f low or 0

Shutdown when

inactive

e.g., Speech Coding

Video Compression

e.g., X Display Server

algorithmic concurrency

Disk I/O Reduce oC

Energy efficient s/w

Communication

System partitioning

inactive

Efficient Circuits & Layouts

Speed vs. Voltage

7.0

3.0

5.0

Normalized

Delay

1.0 1.5 2.0 2.5 3.0

Supply Voltage, V

1.0

Reducing the Supply Voltage: an Architectural

Approach

Operate at reduced voltage at lower speed

Use architecture optimization to compensate for slower

operation operation

e.g. concurrency, pipelining via compiler techniques

Architecture bottlenecks limit voltage reduction

degradation of speed-up

interconnect overheads

Similar idea for memory: slower and parallel Similar idea for memory: slower and parallel

Trade-off AREA for lower POWER

Fundamentals of dynamic voltage scaling (DVS)

Power consumption of CMOS

circuits (ignoring leakage):

with

2

f V C P o

V

Delay for CMOS circuits:

frequency clock :

voltage supply :

e capacitanc load :

activity switching :

with

f

V

C

f V C P

dd

L

dd L

o

o =

( )

) than (

voltage threshhold :

with

2

dd t

t

t dd

dd

L

V V

V

V V

V

C k

<

= t

frequency clock : f

Decreasing V

dd

reduces P quadratically,

while the run-time of algorithms is only linearly increased

E=P x t decreases linearly

(ignoring the effects of the memory system and V

t

)

Voltage scaling: Example

V

dd

[Courtesy, Yasuura, 2000]

T

frame

T

frame

Fixed Supply Variable Supply

Varying the Supply Voltage

Active Idle

E

fixed

= 1/2 CV

dd

2

Active

E

var

= 1/2 C(V

dd

/2)

2

= 1/4E

fixed

0.6

0.8

1.0

Normalized

Power

Fixed Supply

0 0.2 0.4 0.6 0.8 1.0

0

0.2

0.4

Normalized Workload

Power

Variable Supply

from [Gutnik96]

(VLSI Symposium)

Low-power Software

Wireless industry Constantly evolving standards

Systems have to be flexible and adaptable

Significant portion of system functionality is implemented as

software running on a programmable processor

Software drives the underlying hardware

Hence, it can significantly impact system power consumption

Significant energy savings can be obtained by clever Significant energy savings can be obtained by clever

software design.

Low-power Software Strategies

Code running on CPU

Code optimizations for lowpower Code optimizations for low power

Code accessing memory objects

SW optimizations for memory

Data flowing on the buses

I/O coding for low power

CPU

Cache

Compiler controlled power management

Memory

Dynamic Power Optimization

Two main steps:

Workload allocation to processing elements: task mapping and

scheduling scheduling

After workload allocation, resource of processing elements

should be adapted to the required performance to minimize

energy consumption

shut-down voltage scaling

Shut-Down

When the system is idle the processor can be placed into a

lowpower state low-power state

reactivity power level

-core clock gating (waked-up by timer interrupt)

- core power gating (waked-up by on-chip peripherals)

no need for context restore

need for context restore

-chip power gating (waked-up by external, on board

interrupts)

need for context restore

Shutdown for Energy Saving

Blocked

Off

Active

On

Subsystems may have small duty factors

CPU, disk, wireless interface are often idle

H ge difference bet een on&offpo er

Off On

T

block

T

active

ideal improvement = 1 + T

block

/T

active

Huge difference between on & off power

Some Low-Power CPUs: StrongARM400mW (active)/ 50 mW(idle) / 0.16 mW(sleep)

2.5 Hard Disk: 1.35W (idle spinning) / 0.4W (standby) / 0.2W (sleep) / 4.7W (start-up)

Example: SA-1100 CPU

RUN

400 mW

RUN

IDLE

CPU stopped when not in

use

Monitoring for interrupts

RUN

10 s 10 s

90 s

160 ms

SLEEP

Shutdown on-chip activity

IDLE SLEEP

50 mW 0.16 mW

90 s

When is DPM useful?

Blocked Active

P

tr

T

tr

If T

tr

=0, P

tr

=0 then DPM policy is trivial

Stop a component when it is not needed

Blocked

Off

Active

On

P

tr

T

tr

If, as is usual, T

tr

!=0, P

tr

!=0

shutdown only when idleness is going to be long enough to

make it worthwhile

Complex decision if the time spent in state is not deterministic

Breakeven Point

Breakeven point: minimum idle time that would make it

worthwhile to shutdown

DPM worthwhile when T

BE

<Average T

idle

Problems in Shutdown

Cost of restarting: latency vs. power trade-off

increase in latency (response time)

e.g. time to save restore CPU state, spin up disk e g t e to sa e esto e C U state, sp up ds

increase in power consumption

e.g. higher start-up current in disks

When to Shutdown

Optimal vs. Idle Time Threshold vs. Predictive

When to Wakeup

Optimal vs. On-demand vs. Predictive

Cross-over point for shutdown to be effective

Frequency/Voltage Scaling

DFVS:

Adapting frequency/voltage to the workload Adapting frequency/voltage to the workload

Frequency must be scaled with voltage to keep circuit

functionality

Dynamic power goes with the square of Vdd and

linearly with clock speed

Scaling V and F by a factor of s ->power scales as s

3

f V C P

dd eff

= o

2

Shutdown vs. Variable Voltage

Example: task with 100ms deadline, requires 50ms CPU

time at full speed

When Voltage Reduction is Better

time at full speed

normal system gives 50ms computation, 50ms idle/stopped

time

half speed/voltage system gives 100ms computation, 0ms

idle

same number of CPU cycles but 1/4 energy reduction

T1 T2 T1 T2

S

p

e

e

d

Time

Idle

Same work,

lower energy

Task

Task

Problem with Voltage Reduction

Voltage gets dictated by the tightest (critical) timing constraint

not a problem if latency not important

throughput canalways be improvedby pipelining throughput can always be improved by pipelining,

parallelism etc.

but, real systems have bursty throughput and latency

critical tasks

Solution: dynamically vary the voltage! y y y g

Barriers to Future Voltage Scaling

Voltage scaling requires threshold voltage V

t

to be scaled as well (15%

per generation)

this increases sub-threshold leakage current

impact on power consumption and circuit robustness

scaling V and V

t

poses serious challenges to special circuits such as

domino logic, sense amplifiers

Leakage power

total leakage current goes up 7.5x per generation

leakage power power by 5x

soonwill become a significant portionof total soon will become a significant portion of total

active power remains constant for constant die size

leakage power, and therefore total power, can be substantially

reduced by cooling

Essential to control die temperature

power density (W/cm

2

): 0.6 micron chips surpassed a hot plate!

Energy Use scaling while it

reduces the energy

Scaling vs. Shutdown

Region of

scaling

Region of

shutdown

E

min

*

reduces the energy

If more time is

allowed, scale

down to the

minimum energy

point and

subsequently use

shutdown

time

Power

time

allowed time

Execution time =t*

Power

time

allowed time

Execution time =t*

Power

time

allowed time

Execution time

t*

time

Energy in Radio

Tx: Sender R R i Tx: Sender Rx: Receiver

Channel

Incoming

information

Outgoing

information

Tx

elec

E

Rx

elec

E

RF

E

Transmit

electronics

Receive

electronics

Power

amplifier

Wireless communication subsystem consists of three

components with substantially different characteristics

Their relative importance depends on the transmission

power of the radio

electronics electronics amplifier

Tx Electronics Rx Electronics

txElec start tx

P E P + =

rxElec start rx

P E P + =

Path Loss

P

rcvd

= P

1m

d

n

Communication Energy Model

P =o + | P

t

E = C V

2

+

Digital Processing

Protocol

MAC

Link

Radio

Tx

Protocol

MAC

Link

Radio

Rx

Power Amp Efficiency

P

amp

o

amp

+ |

amp

P

out

E

bit

= C

bit

V

DD

+

V

DD

I

leak

(V

DD

,V

TH

) T

bit

(V

DD

,V

TH

)

C

bit

I

leak

T

bit

V

DD

V

TH

E

start

n

P

1m

P

out

P

rxElec

P

txElec

Switched capacitance per bit

Leakage current

Processing time per bit

Supply Voltage

Transistor Threshold Voltage

Startup (turn-on) energy

Path loss exponent

Attenuation over one meter

Output power from power amp

Receiver static power

Transmitter static power

Min et. al., Mobicom 2002 (Poster)

Energy Consumption of Transmitting a Packet

| | | |

overhead bit s electronic transmit packet

E H L T P P E + + + =

Power consumed by the power amplifier, depends on the required

performance and the wireless channel (distance, fading, etc.)

P

transmit

Power consumed by the electronic circuitry for filtering,

upconverting, modulation, frequency synthesis, etc.

P

electronics

Energy consumption that is independent of the packet size and

E

h d

gy p p p

modulation scheme (startup cost, fixed encoded header, etc.)

E

overhead

Time to transmit one bit (depends on modulation and symbol rate R

s

) T

bit

Size of packet payload L

Size of packet header H

Energy Consumption of Transmitting a Bit

E H

E

(

Minimize header

size

Minimize

overhead

: Optimize

modulation

Independent of

bit

E

| |

L

E

L

H

T P P

L

E

overhead

bit s electronic transmit

packet

+

(

+ + = 1

p

modulation Modulation

Scaling

Energy per Bit

( ) J E

bit

Region of modulation scaling

P

transmit

4-QAM

9 mW

P 15mW P

electronics

15 mW

R

s

1 Mbaud

Beyond Energy Efficiency: Battery-aware Design

Theoretical capacity of battery is decided by the amount of the active

material in the cell

batteries often modeled as buckets of constant energy

e.g. halving the power by halving the clock frequency is assumed

to double the computation time while maintaining constant

computation per battery life

In reality, delivered or nominal capacity depends on how the battery is

discharged

di h t (l d t) discharge rate (load current)

discharge profile and duty cycle

operating voltage and power level drained

Problem Formulation

Due to battery properties, the ways

at which the batteries are

T

time

Total Service, S

U discharged have impact on the

actual lifetime

Static Approach: Fix U(t), find the

optimal U that maximize S

}

=

=

T

t

APP

dt t U S

0

) (

T

Dynamic Approach: Heuristic

approach to find optimal U(t)

Power and energy are related to each other

}

= dt P E

P

}

P

E E'

t

In many cases, faster execution also means less energy, but

the opposite may be true if power has to be increased to allow

faster execution.

Battery Characteristics

Important characteristics:

energy density (Wh/liter) and specific energy (Wh/kg)

power density (W/liter) and specific power (W/kg) power density (W/liter) and specific power (W/kg)

open-circuit voltage, operating voltage

cut-off voltage (at which considered discharged)

shelf life (leakage)

cycle life

The above are decided by system chemistry

advances in materials and packaging have resulted in advances in materials and packaging have resulted in

significant changes in older systems

carbon-zinc, alkaline manganese, NiCd, lead-acid

new systems

primary and secondary (rechargeable) Li

secondary zinc-air, Ni-metal hydride

Modeling the Battery Behavior

Theoretical capacity of battery is decided by the amount of the

active material in the cell

batteries often modeled as buckets of constant energy batteries often modeled as buckets of constant energy

e.g. halving the power by halving the clock frequency is

assumed to double the computation time while maintaining

constant computation per battery life

In reality, delivered or nominal capacity depends on how the

battery is discharged

di h t (l d t) discharge rate (load current)

discharge profile and duty cycle

operating voltage and power level drained

Battery Model: Physical Picture

Battery Capacity

100

Current in C rating:

load current normalized to batterys capacity

e.g. a discharge current of 1C for a capacity of 500 mAh is 500 mA

Battery Capacity vs. Discharge Current

Amount of energy delivered is decreased as the current (rate

at which power is drawn) is increased

ratedas ampere hours or watt hours when discharged rated as ampere hours or watt hours when discharged

at a specific rate to a specific cut-off voltage

primary cells rated at a current which is 1/100th of the

capacity in ampere hours (C/100)

secondary cells are rated at C/20 or C/10

At high currents, the diffusion process that moves new active

material fromelectrolytes to the electrode cannot keep up material from electrolytes to the electrode cannot keep up

concentration of active material at cathode drops to

zero, and cell voltage goes down below cut-off

even though active material in cell is not exhausted!

Battery Capacity vs. Discharge Current

Peukerts Formula

Peukerts Law expresses the capacity of a battery

in terms of it discharge.

C

P

= I

k

t

C

P

is the capacity according to Peukert (A.h).

I discharge current.

k Peukert constant .

t time of discharge.

Ragone Plots (log-log plot)

Specific Power

W/kg

Specific Energy

Wh/kg

Alternate Equivalent View of the Battery

Manufacturers often give battery efficiency (%) vs. discharge rate

(or discharge current ratio)

discharge rate =I

ave

/I

rated

dsc a ge a e

ave

/

rated

Battery cannot respond to instantaneous changes in current so, a

time constant t used to calculate I

ave

Given actual energy drawn by the circuit, one can use the battery

efficiency to calculate the actual depletion in the stored energy in

the battery the battery

Example:

battery efficiency is 60% and its rated capacity is 100 mAh @ 1V

computed average DC-DC current of 300 mA would drain the

battery in 12 min, while at 100% efficiency it would last 1 hr

Modeling Battery Efficiency

rated

ave

I

I

I

R =

cycle

bat

T

N

t

=

=

bat

N

system ave

cycle I I ) (

1

= cycle

system

bat

ave

y

N

0

) (

cycle bat ave bat bat

T V I E ) 1 ( q =

from [Simunic01]

Capacity & Variable Discharge Current

Constant vs. Pulsed

Capacity can be extended by draining power in short discharge

periods separated by rest periods periods separated by rest periods

also works with constant background current

Battery relaxes and partially recovers the active material lost

during the current impulse

longer the rest period, the better is the recovery

longer rest period needed as the discharge depth becomes greater

battery voltage also goes back up

Benefits of Pulsed Discharge

Higher specific power for a given specific energy

impulses of several times the limiting current value

can be obtained by choosing short pulses and long can be obtained by choosing short pulses and long

rest periods

Higher specific energy for a given specific power

ideally, want specific energy =theoretical capacity

depends on pulse and rest periods

Exploiting Pulse Discharge

Gain in battery life if system shutdown is done taking into

account the pulse discharge

Examples:

protocols in case of radios where power during

transmission is a lot higher than during receive and

idle periods

shutdown of CPUs and variable speed CPUs

shutdown of disks

Rate Capacity Effect

Capacity depends on the discharge rate

Higher discharge rate reduces the actual capacity

Summary of Battery

Non-Idealities

Higher discharge rate reduces the actual capacity

Relaxation Effect

When discharge current is either cutoff or reduced, the batterys

capacity is recovered

2.66

2.68

2.7

2.72

V

)

8 5 mA

0 100 200 300 400 500 600

time (sec)

2.56

2.58

2.6

2.62

2.64

V

o

l

t

a

g

e

(

V

8.5 mA

1.9 mA

Battery Modeling

Predict battery lifetime given a load profile

Many battery models Many battery models

Model electrochemical processes in the battery

Solve system of PDEs, e.g. Berkeleys DUALFOIL

Accurate but long simulation times and large number of

parameters (e.g. >50 with DUALFOIL)

Not easy to use in an optimization tool

Abstract representation of batteries

E.g. Markov chain

No physics or chemistrybasedjustification No physics or chemistry based justification

Not easy to use in an optimization tool

Analytical models

Capture key factors of battery performance

E.g model by Rakhmatov & Vrudhula @ U. Arizona

Lithium Battery Charging

Example of Rechargeable Battery management

Example of Rechargeable Battery management

Example of Non-Rechargeable Battery management

Battery Charging Method

Trickle Charging -dT/dt cutoff

-V cutoff Time controlled charging

Alternatives to Batteries?

Small batteries are the only choice for consumer products

up to 20W

But

heavy

expensive

expire without warning

require replacement (disposal problem) or recharging

(time problem)

Are there alternatives?

YES, we can

harvest the energy!!!!

How to Select and Use Power

Supplies and dc/dc Converters for

Your Applications

Introduction to Power Supplies and dc/dc

Converters

Available/Raw Power Sources

AC or DC (frequency) AC or DC (frequency)

Un-regulated (changes with load, prime source, etc.)

Voltage (different level, polarity, isolation)

Non-protected (against over load, fault, temp., etc.)

Load Demand

Different AC or DC (frequency) Different AC or DC (frequency)

Regulated (against load, prime source, etc.)

Voltage (different level, polarity, isolation)

Protected (against over load, fault, temp., etc.)

Desired power out

Introduction to Power Supplies and dc/dc

Converters

Power & Electronic

Circuits

Raw power in

(V, I, P, F)

To loads:

Electronic ckts

Motor

Computer

E i t

Battery

Fuel Cell

AC Outlet

Solar

Power Supply

Equipment

Control

Power Supplies and dc/dc Converters

Types & Technologies

AC-DC Power Supply (or AC Adapter)

Change ac power into regulated dc power, e.g., a typical AC Adapter takes 120

V ac input and converter it to regulated 5 Vdc.

DC-DC Converters

Change dc at one voltage potential to a dc at a different voltage potential

DC-AC Power Supply (for example, UPS, 12Vdc-

120Vac adapter) p )

AC-AC Power Supply/Regulator (for example, line

regulator)

Linear Regulators

+ Simple, inexpensive

+ Electrically quiet pure DC output + Electrically quiet pure DC output

- Vout < Vin

- Poor Efficiency

e.g., if Vin = 6V, Vout = 3V, Efficiency = %?

- Can be physically large

Switching Regulators

Also known as DC-DC Converters or

Switchmode Regulators

+ Wide range of input voltages

+ Multiple output voltages possible

+ High Efficiency (sometimes >90%!)

+ Compact

Complex more expensive - Complex, more expensive

- Electrically noisy (not pure DC)

Switching Regulators

A few types

Buck (step-down)

B ( ) Boost (step-up)

Flyback (supports multiple outputs; transformer needed)

Buck-boost (step-up or down)

SEPIC, Zeta, Cuk (specialized buck-boost)

Forward (requires transformer) Forward (requires transformer)

Charge Pump (no inductor)

Switching Regulators

Buck Converter

C ti d Di ti M d Continuos mode Discontinuos Mode

D = Duty Cycle

Switching Regulators

Boost Converter

C ti d Di ti M d Continuos mode Discontinuos Mode

D = Duty Cycle

Switching Regulators

Buck Boost Converter

C ti d Di ti M d

D = Duty Cycle

Continuos mode Discontinuos Mode

A.K.A. charge pump or flying capacitor

I d t l (l t)

Switching Regulators

Switched Capacitor

Inductorless (low cost)

Work well for loads up to ~100mA

Produce output voltage equal to Vin or 2 x Vin

Output noisy and poorly regulated,

but OK for certain applications

AC-DC Power Supplies

Circuit Selection and Design

Using Linear Regulators

Step-down

Xfmer

Regulator

120 V

AC

For low power (some watts or below) applications.

Low efficiency, large size and weight

(bulky step-down line transformer)

Low cost

AC-DC Power Supplies

Circuit Selection and Design

Using Switching-Mode

High efficiency

Small size and light weight

For high power (density) applications

Selecting the Right dc/dc Converter

The Need for dc/dc Converters

E.g., a single AA alkaline battery produces 1.5 V when fully charged and its voltage

drops to as low as 0.9 V when becoming depleted.

Dc/dc Converter Types

Buck

Boost

Buck-Boost

Dc/dc Converter Technologies

Linear Regulators

Switching Regulators

Charge Pumps

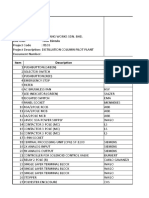

Selecting the Right dc/dc Converter

Dc/dc converter technology comparison

Parameter

Linear Switching

Charge pump Parameter

regulator regulator

Charge pump

Efficiency Low High Medium

EMI Noise Low High Medium

Output current Low to medium Low to High Low

Boost (step-up) No Yes Yes

Buck (step-

down)

Yes Yes Yes

Solution size small Large Medium

Selecting the Right dc/dc Converter

(example mobile phone)

VBAT = 3.7 V nom, Vcircuit= 1.2 V

Load Current = 600 mA

Power delivered to load = 600 mA * 1.2 V = 720 mW

Power converted to heat =

720 W * ((3 7/1 2) 1) 1 500 W

Linear regulators:

Inexpensive

small footprint

720 mW * ((3.7/1.2)-1) = 1,500 mW

Total power consumed =

720 mW + 1,500 mW = 2,200 mW

32% goes to work, 68% goes to heating user hand and ear

when using a Linear Regulator for a mobile device

VBAT = 3.7 V nom; Vcircuit = 1.2 V

Load Current = 600 mA

small footprint

low part count

low noise

high ripple rejection

Switching regulators:

Converter efficiency = 90%

Power delivered to load = 600 mA * 1.2 V = 720 mW

Power converted to heat =720 mW * ((1/0.9)-1)=80 mW

Total power consumed = 720 mW + 80 mW = 800 mW

90% goes to work, 10% goes to heating user hand and ear

When using a Switch-mode regulator for a mobile device.

a bigger footprint

higher part count,

more cost

prone to conducted and

radiated EMI.

Specs, Performance and Protection

Voltage ripple (+-50 mV, or 5%)

Isolation (e.g., 1,500 V ac for 1 min.) Isolation (e.g., 1,500 V ac for 1 min.)

Load regulation (e.g., 3%)

Dynamic response (transients, wake-up time, etc.)

Short circuit protection

OC protection (Overcharge)

OV protection (Overvoltage)

OT protection (Overtemperature)

Power Losses and Thermal Design

For example, a 7815 linear regulator with input voltage of 20 V and

output current of 1 A.

The power loss is (20-15)Vx(1 A)=5 W.

From the chip to the ambient, AT

i

can be calculated according to the

thermal circuit using Ohms law (R=V/I), where R is the thermal

resistance, V is the temperature and I is the power dissipation.

case ambient

Thcase ambient

d

T T

R

P

=

Where:

T

case

is case Temp.

T

ambient

is ambient Temp.

dissipation

out

dissipation in out out

op

P

P

P P P P

q

= =

ambient

p

P

dissipation

is power loss

P

in

is input power

P

out

is output power

q

op

is efficiency under

given operating conditions

Power Losses and Thermal Design

A more detailed thermal circuit

W : Device power loss

Tj : Junction temperature of device

Tc : Device case temperature

Tf : Temperature of heatsink

Ta : Ambient temperature

Rth(j-c) : Thermal resistance between junction and case,

specified in datasheet

Rth(c-f) : Contact thermal resistance between case and

h t i k ifi d i d t h t heatsink, specified in datasheet

Rth(f-a) : Thermal resistance between heatsink and

ambient air, specified by the heatsink manufacturer

Power Losses and Thermal Design

Tj=WRth(j-c)+Tc

Tc=W{Rth(c-f) + Rth(f-a)}+Ta

Tj WRth(j c)+Tc

Examples

Device : 7815 (Linear regulator)

Vin=20V, Vo=15V, Io=1A

W: (20 15)1=5 watts W : (20-15)1=5 watts

Rth(j-c) : 5 C/W

Rth(c-f) : 0.5 C/W, Greased surface

Rth(f-a) :20 C/W

Ta=25 C

An assortment of 78XX series

Tc=5(0.5 + 20)+25=127.5 C

Tj=51+127.5=132.5 C

ATj=82.5-25=107.5C

An assortment of heatsinks

Anda mungkin juga menyukai

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryDari EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryPenilaian: 3.5 dari 5 bintang3.5/5 (231)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Dari EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Penilaian: 4.5 dari 5 bintang4.5/5 (119)

- Never Split the Difference: Negotiating As If Your Life Depended On ItDari EverandNever Split the Difference: Negotiating As If Your Life Depended On ItPenilaian: 4.5 dari 5 bintang4.5/5 (838)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaDari EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaPenilaian: 4.5 dari 5 bintang4.5/5 (265)

- The Little Book of Hygge: Danish Secrets to Happy LivingDari EverandThe Little Book of Hygge: Danish Secrets to Happy LivingPenilaian: 3.5 dari 5 bintang3.5/5 (399)

- Grit: The Power of Passion and PerseveranceDari EverandGrit: The Power of Passion and PerseverancePenilaian: 4 dari 5 bintang4/5 (587)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyDari EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyPenilaian: 3.5 dari 5 bintang3.5/5 (2219)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeDari EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifePenilaian: 4 dari 5 bintang4/5 (5794)

- Team of Rivals: The Political Genius of Abraham LincolnDari EverandTeam of Rivals: The Political Genius of Abraham LincolnPenilaian: 4.5 dari 5 bintang4.5/5 (234)

- Rise of ISIS: A Threat We Can't IgnoreDari EverandRise of ISIS: A Threat We Can't IgnorePenilaian: 3.5 dari 5 bintang3.5/5 (137)

- Shoe Dog: A Memoir by the Creator of NikeDari EverandShoe Dog: A Memoir by the Creator of NikePenilaian: 4.5 dari 5 bintang4.5/5 (537)

- The Emperor of All Maladies: A Biography of CancerDari EverandThe Emperor of All Maladies: A Biography of CancerPenilaian: 4.5 dari 5 bintang4.5/5 (271)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreDari EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You ArePenilaian: 4 dari 5 bintang4/5 (1090)

- Her Body and Other Parties: StoriesDari EverandHer Body and Other Parties: StoriesPenilaian: 4 dari 5 bintang4/5 (821)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersDari EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersPenilaian: 4.5 dari 5 bintang4.5/5 (344)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceDari EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RacePenilaian: 4 dari 5 bintang4/5 (890)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureDari EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FuturePenilaian: 4.5 dari 5 bintang4.5/5 (474)

- The Unwinding: An Inner History of the New AmericaDari EverandThe Unwinding: An Inner History of the New AmericaPenilaian: 4 dari 5 bintang4/5 (45)

- The Yellow House: A Memoir (2019 National Book Award Winner)Dari EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Penilaian: 4 dari 5 bintang4/5 (98)

- On Fire: The (Burning) Case for a Green New DealDari EverandOn Fire: The (Burning) Case for a Green New DealPenilaian: 4 dari 5 bintang4/5 (73)

- Service Manual: PMA-510AEDokumen38 halamanService Manual: PMA-510AEpapkin hagopian100% (1)

- BOM Electrical ComponentsDokumen3 halamanBOM Electrical Componentslinkin_slayerBelum ada peringkat

- 76 - 8271423M - B FGTM-MDokumen32 halaman76 - 8271423M - B FGTM-MHamza_yakan967Belum ada peringkat

- Smart Water ManagementDokumen21 halamanSmart Water ManagementPaushal Pradeep ABelum ada peringkat

- Couplers and Hybrid Rings P y G: .Donelli@disi - Unitn.it .Donelli@disi - Unitn.itDokumen75 halamanCouplers and Hybrid Rings P y G: .Donelli@disi - Unitn.it .Donelli@disi - Unitn.itasdsdBelum ada peringkat

- 2014 - WebRTC Enabled Multimedia Conferencing and Collaboration Solution PDFDokumen6 halaman2014 - WebRTC Enabled Multimedia Conferencing and Collaboration Solution PDFasdsdBelum ada peringkat

- Microwave Microwave Microwave Devices Devices Devices Power Power Power Splitters Splitters Splitters///combiners Combiners CombinersDokumen31 halamanMicrowave Microwave Microwave Devices Devices Devices Power Power Power Splitters Splitters Splitters///combiners Combiners CombinersasdsdBelum ada peringkat

- 2014 - Finite State Machine Based Flow Analysis For WebRTC Applications PDFDokumen6 halaman2014 - Finite State Machine Based Flow Analysis For WebRTC Applications PDFasdsdBelum ada peringkat

- Frequency Domain Analysis of Microwave DevicesDokumen41 halamanFrequency Domain Analysis of Microwave DevicesasdsdBelum ada peringkat

- Filters 2Dokumen36 halamanFilters 2asdsdBelum ada peringkat

- Rectangular Waveguides Rectangular Waveguides Rectangular Waveguides G G G G G GDokumen51 halamanRectangular Waveguides Rectangular Waveguides Rectangular Waveguides G G G G G GasdsdBelum ada peringkat

- SL3Dokumen35 halamanSL3asdsdBelum ada peringkat

- SL3Dokumen35 halamanSL3asdsdBelum ada peringkat

- SL5Dokumen14 halamanSL5asdsdBelum ada peringkat

- Filters 3Dokumen18 halamanFilters 3asdsdBelum ada peringkat

- SL1Dokumen10 halamanSL1asdsdBelum ada peringkat

- Rectangular Waveguides Rectangular Waveguides Rectangular Waveguides G G G G G GDokumen51 halamanRectangular Waveguides Rectangular Waveguides Rectangular Waveguides G G G G G GasdsdBelum ada peringkat

- Filters 2Dokumen36 halamanFilters 2asdsdBelum ada peringkat

- Filters 3Dokumen18 halamanFilters 3asdsdBelum ada peringkat

- Filters 1Dokumen30 halamanFilters 1asdsdBelum ada peringkat

- CS1m Part3 2013 2014Dokumen75 halamanCS1m Part3 2013 2014asdsdBelum ada peringkat

- SL1Dokumen10 halamanSL1asdsdBelum ada peringkat

- Ees04 CDokumen47 halamanEes04 CasdsdBelum ada peringkat

- Ees06 MSP430 GpioDokumen20 halamanEes06 MSP430 GpioasdsdBelum ada peringkat

- EEE194 RF Microwave FiltersDokumen13 halamanEEE194 RF Microwave FiltersNico PutterBelum ada peringkat

- CS1m Part4 2013 2014Dokumen60 halamanCS1m Part4 2013 2014asdsdBelum ada peringkat

- Exercises: CDMA: XerciseDokumen4 halamanExercises: CDMA: XerciseasdsdBelum ada peringkat

- MSP430 Microcontroller Architecture GuideDokumen128 halamanMSP430 Microcontroller Architecture GuideasdsdBelum ada peringkat

- EES13 - Energy Harvesting - WSNDokumen90 halamanEES13 - Energy Harvesting - WSNasdsdBelum ada peringkat

- OPTIC FIBERS: FUNDAMENTALDokumen69 halamanOPTIC FIBERS: FUNDAMENTALasdsdBelum ada peringkat

- EES12 - Energy HarvestingDokumen48 halamanEES12 - Energy HarvestingasdsdBelum ada peringkat

- Thermal Noise in Telecommunication SystemsDokumen55 halamanThermal Noise in Telecommunication SystemsasdsdBelum ada peringkat

- CS1m Part1 2013 2014Dokumen22 halamanCS1m Part1 2013 2014asdsdBelum ada peringkat

- AREVA HVDC DC Protection Scheme Lecture NotesDokumen59 halamanAREVA HVDC DC Protection Scheme Lecture Noteshareshacharya33860% (1)

- SKBIF / LCD Monitor-NGC - Troubleshooting Guide: LAST UPDATED: 12/11/2018Dokumen9 halamanSKBIF / LCD Monitor-NGC - Troubleshooting Guide: LAST UPDATED: 12/11/2018dhanysiregarBelum ada peringkat

- Small Form-Factor Pluggable Transceiver - Wikipedia PDFDokumen8 halamanSmall Form-Factor Pluggable Transceiver - Wikipedia PDFsorin-itBelum ada peringkat

- Custom Detail Page Format ElementsDokumen5 halamanCustom Detail Page Format ElementsBhavneet SinghBelum ada peringkat

- Rele Siemens 7SJ601Dokumen18 halamanRele Siemens 7SJ601luisBelum ada peringkat

- ExamplesDokumen10 halamanExamplesjojojojoBelum ada peringkat

- Cache PerformanceDokumen41 halamanCache PerformanceDebashis DasBelum ada peringkat

- Hxhm8x3www1616065t0at06 PDFDokumen1 halamanHxhm8x3www1616065t0at06 PDFОльга ПестряковаBelum ada peringkat

- ZED-F9P ProductSummary (UBX-17005151)Dokumen2 halamanZED-F9P ProductSummary (UBX-17005151)mar_barudjBelum ada peringkat

- Bab 4: Dasar-dasar Elektronika ReviewDokumen46 halamanBab 4: Dasar-dasar Elektronika ReviewYhola YosevinBelum ada peringkat

- X5-400M Matlab BSP ManualDokumen71 halamanX5-400M Matlab BSP Manualmidlopez83Belum ada peringkat

- FIT393M ManualDokumen15 halamanFIT393M ManualSaikrishna Guntha0% (2)

- CR-IR 357 Service Manual: Control SheetDokumen108 halamanCR-IR 357 Service Manual: Control SheetEduardo Saul MendozaBelum ada peringkat

- 110V LdoDokumen20 halaman110V LdoJohn MelchizedekBelum ada peringkat

- User Manual Logitech x620Dokumen10 halamanUser Manual Logitech x620Husăsan VladBelum ada peringkat

- How a pnp Transistor OperatesDokumen5 halamanHow a pnp Transistor OperatesmohanBelum ada peringkat

- ATA 44 - Cabin Systems (Mike Tooley)Dokumen16 halamanATA 44 - Cabin Systems (Mike Tooley)Jagbir SinghBelum ada peringkat

- Introduction To Semiconductor DiodesDokumen7 halamanIntroduction To Semiconductor DiodesAndy CentenaBelum ada peringkat

- A429 Users ManualDokumen244 halamanA429 Users ManualbaburaokodavatiBelum ada peringkat

- MV AC Drive Topology Analysis 1143643595Dokumen49 halamanMV AC Drive Topology Analysis 1143643595Edith Yesenia Bustamante VelardeBelum ada peringkat

- Chap12 Spread Spectrum SignalsDokumen87 halamanChap12 Spread Spectrum SignalsFadi AkilBelum ada peringkat

- Ubiquiti Education Wi-Fi Best Practices (38Dokumen42 halamanUbiquiti Education Wi-Fi Best Practices (38Andrew DiazBelum ada peringkat

- Control System Lab Manual 18EEL66Dokumen70 halamanControl System Lab Manual 18EEL66ADARSH SHINDE100% (1)

- ManualDokumen385 halamanManualSayak BoseBelum ada peringkat