VHDL

Diunggah oleh

Daniel CadenaJudul Asli

Hak Cipta

Format Tersedia

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniHak Cipta:

Format Tersedia

VHDL

Diunggah oleh

Daniel CadenaHak Cipta:

Format Tersedia

C

C

a

a

p

p

t

t

u

u

l

l

o

o

1

1

L

L

e

e

n

n

g

g

u

u

a

a

j

j

e

e

s

s

d

d

e

e

D

D

e

e

s

s

c

c

i

i

p

p

c

c

i

i

n

n

d

d

e

e

H

H

a

a

r

r

d

d

w

w

a

a

r

r

e

e

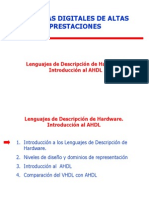

1.0 INTRODUCCION

Resulta muy difcil disear un sistema digital sin tener conocimiento y comprensin de

los bloques bsicos tales como compuertas lgicas y Flip Flops. Muchos sistemas

digitales han sido diseados utilizando ecuaciones Booleanas. Se han desarrollado

muchas tcnicas para optimizar esta tcnica, incluyendo la minimizacin de ecuaciones

para lograr un uso efectivo de los componentes.

La tcnica de diseo con ecuaciones booleanas requiere que se conozcan las

ecuaciones para: la entrada de cada Flip Flop, entrada de datos y Bloque de

compuertas. Esto ha hecho que las ecuaciones booleanas sean poco prcticas en

diseos complejos que contienen miles de compuertas y Flip Flops ya que seran

necesarias un gran nmero de ellas.

Existen varios niveles de descripcin que van desde un nivel de silicio hasta la

descripcin de sistemas complejos. Estos niveles pueden ser analizados en trminos

de su estructura y funcionamiento.

1.0.0 DESCRIPCIN FUNCIONAL

A travs de la descripcin funcional de un sistema, se busca representar el

comportamiento del mismo mediante modelos matemticos o algortmicos. El ms

bajo nivel dentro de este dominio lo constituyen descripciones con base en ecuaciones

que modelan cada uno de los elementos (transistores, diodos, resistencias, etc.) que

conforman el sistema.

Subiendo de nivel se encuentran las ecuaciones booleanas, lenguaje de transferencia de

registros (RTL), mquinas de estado, etc. Buscando siempre que las descripciones se

puedan realizar de la forma ms natural posible. Dentro de esta categora se

encuentran los lenguajes de descripcin o especificacin de Hardware (HDLs), que

bsicamente permiten descripciones a nivel algortmico (funcional) y a nivel de

estructura (nivel de transferencia de registros).

1.0.0.0 NIVEL ALGORTMICO

En este nivel se modela el comportamiento, como una funcin entradasalida, sin

tener en cuenta cmo puede llegar a ser su realizacin fsica, o cual ser la tecnologa

en la cual se implemente. La descripcin del sistema a este nivel toma la forma de

algoritmos, usualmente expresados en un lenguaje con las construcciones, tipos de

datos, operadores, y facilidades de un lenguaje de programacin de alto nivel.

Lenguajes de descripcin funcional incluyen a VHDL, Verilog, subconjuntos de

lenguajes convencionales de programacin, como C, y lenguajes de varios

fabricantes, como Altera (AHDL), y Xilinx (SML).

Las ventajas que se ganan al adoptar este nivel de descripcin del sistema son:

Su utilidad como medio de especificacin o definicin del sistema a ser desarrollado.

La rapidez con la que puede ser concebido el sistema, al no tener que especificarse los

detalles de cmo ser su realizacin.

La velocidad con la que la descripcin del sistema puede ser depurada, al ser posible la

simulacin directa de la descripcin funcional realizada.

Este ltimo punto es de gran importancia en la concepcin de sistemas complejos, en

los que a menudo es difcil o imposible, contemplar todas las posibilidades de la

relacin entradasalida del sistema.

1.0.0.0 NIVEL DE TRANSFERENCIAS ENTRE REGISTROS (RTL)

En este nivel se define la arquitectura para la realizacin del sistema, en trminos de

las distintas unidades funcionales a ser utilizadas, de los registros o bloques de

almacenamiento requeridos, y de los buses de datos o medios de interconexin entre

las unidades funcionales y entre stas y los registros. En la definicin de la

arquitectura de un sistema digital moderno es usual observar una separacin clara

entre la seccin de datos de la arquitectura, con capacidad de transformacin y

almacenamiento de datos, y la seccin de control sobre la misma. Esto permite

separar el diseo de la seccin de datos, que es usualmente de arquitectura sencilla

pero con unidades funcionales complejas y grandes bloques de almacenamiento, del

diseo de la seccin de control, que usualmente demanda un pequeo nmero de

componentes, pero es de una alta complejidad algortmica.

La descripcin del sistema a nivel de arquitectura toma usualmente la forma de

sentencias concurrentes, que describen la secuencia de operaciones del sistema y el

flujo de datos de un sitio a otro en el mismo. Este tipo de descripcin es soportada

por lenguajes como VHDL.

1.0.0 DESCRIPCIN ESTRUCTURAL

Una descripcin a nivel estructural de un sistema, define la arquitectura del mismo a

nivel de subcomponentes y sus interconexiones. Este tipo de descripciones es

usualmente de tipo jerrquico, donde la descripcin de los subcomponentes es a la vez

basada en otra que utiliza elementos (componentes) de ms bajo nivel.

Los elementos de ms bajo nivel son normalmente compuertas lgicas y flipflops,

incluso componentes como transistores y resistencias. Esto ocasiona que las

descripciones estructurales puedan tener un carcter lgico o circuital.

Este tipo de descripciones es normalmente respaldado por una herramienta CAD de

diseo digital a travs de editores esquemticos (editores grficos) que facilitan la

interconexin de los componentes disponibles en libreras. Estas descripciones

normalmente incluyen caractersticas fsicas del comportamiento de los elementos,

tales como retardos de operacin, con los cuales se logran simulaciones funcionales

prximas al desempeo real que se obtendr con la implementacin fsica.

1.0.0.0 NIVEL LGICO

Este nivel es comnmente utilizado en los mtodos tradicionales de diseo, donde los

componentes empleados corresponden a bloques funcionales disponibles

comercialmente y para los cuales se encuentran diversidad de herramientas para

diseo, simulacin e implementacin.

Los lenguajes de descripcin a este nivel incluyen los editores esquemticos, lenguajes

primitivos como AHPL, lenguajes de intercambio de informacin de componentes e

interconexiones (Netlist) como EDIF, adems de los subconjuntos respectivos de

VHDL, Verilog y otros.

1.0.0.0 NIVEL ELCTRICO O DE CIRCUITO

Identifica la realizacin en trminos de dispositivos electrnicos bsicos, tales como

interruptores, transistores, resistencias y condensadores, segn la tecnologa

seleccionada. En la mayora de los casos, en descripciones con componentes o celdas

de tipo estndar, o con dispositivos de lgica programable, la correspondencia entre

celdas funcionales bsicas del sistema (compuertas y celdas de almacenamiento) y el

nivel elctrico es fija, y determinada por la familia lgica, dispositivo, o tecnologa

electrnica utilizada. Sin embargo, en estos casos es necesario tener en cuenta algunas

consideraciones elctricas importantes del diseo, tales como los niveles de fanin y

fanout (manejos de corriente) de los componentes, tiempos de inercia, retardo, ajuste

y mantenimiento en compuertas y celdas de almacenamiento, y niveles de consumo de

potencia.

La descripcin elctrica de un sistema se puede hacer por diagramas esquemticos, o

por listas de componentes y conexiones elctricas, como en el formato usado por el

simulador elctrico SPICE.

1.0.0 DESCRIPCIN FSICA

El tipo de descripcin fsica adecuada para la realizacin de un sistema depende de la

tecnologa utilizada y el nivel de detalle requerido. La descripcin fsica puede darse a

nivel de bastidor, de tarjeta, de configuracin de dispositivo lgico programable, o de

geometras de circuito integrado. Los problemas abordados en el diseo fsico del

sistema son de particin, colocacin, y enrutamiento de las unidades bsicas.

Las consideraciones principales para el diseo fsico incluyen:

El nmero de unidades bsicas, dispositivos, o geometras requeridas en la realizacin

del sistema, as como el nmero de interconexiones entre stas.

El espacio fsico o la cantidad de recursos disponibles en cada unidad de fabricacin

usada

Las facilidades de enrutamiento e interconexin existentes en las unidades de

fabricacin.

Las reglas de diseo que es necesario obedecer, propias de la tecnologa (tal como

nmero, dimensiones, y espaciamientos mnimos, etc).

El nivel de descripcin fsica genera un mayor volumen de informacin en la

especificacin de un sistema, e invariablemente requiere el uso de herramientas de

diseo asistido por computador. Los lenguajes usados en la descripcin fsica

incluyen el formato CIF (Caltech Intermediate Format) para la descripcin de

geometras en circuitos integrados sobre medidas (fullcustom) y semicustom, varios

formatos de asignacin de recursos y dispositivos en lgica programable, y diagramas

fsicos de colocacin e interconexin de dispositivos, como en diagramas de circuito

impreso.

1.0 METODOLOGIA DE DISEO

1.0.0 INTRODUCCIN

Con el advenimiento de mltiples tecnologas de implementacin y herramientas de

diseo orientadas al manejo y desarrollo de los procesos de diseo de sistemas

digitales, es claro que una metodologa estructurada semi-estandarizada, colabora en la

solucin de varios de los problemas presentados en el abordaje, desarrollo y

mantenimiento de los sistemas trabajados, problemas tales como: el manejo de la

complejidad propia del sistema a desarrollar, la cantidad de informacin generada y el

aprovechamiento al mximo de los beneficios que se puedan obtener de las diferentes

tecnologas de implementacin accequibles y de el potencial brindado por las

herramientas de diseo que se dispongan.

Una metodologa de diseo estructurado de sistemas digitales comparte ideas de

programacin estructurada, y es similar a sta en los pasos que toma :

La concepcin y el desarrollo de un sistema digital se realiza de una manera

descendente (topdown), partiendo desde su especificacin funcional hasta llegar

a su realizacin fsica en la tecnologa seleccionada.

La especificacin funcional del sistema a disear y de cada uno de sus subsistemas

permite la verificacin y depuracin de stos desde las primeras etapas de

desarrollo. Esto hace que se eviten errores de especificacin o diseo, que pueden

llegar a ser costosos si se detectan nicamente en las ltimas etapas del proceso de

diseo.

El uso de una jerarqua de niveles de diseo en el mtodo descendente permite

particionar el sistema a disear en una serie de subsistemas ms simples que el

original, que en principio pueden ser especificados y desarrolados

independientemente por distintos grupos de trabajo.

El uso de estructuras regulares de diseo, como son los bloques RAM, ROM, y de

dispositivos lgicos programables (PICs) en general, permite el uso y la rplica de

unidades bsicas de diseo (como celdas de almacenamiento, compuertas AND u

OR, o bloques lgicos generales) muchas veces y con patrones de inteconexin

absolutamente regulares y eficientes. Se debe recordar aqu que los problemas de

interconexin y comunicaciones en un sistema digital complejo, como lo es un

circuito integrado VLSI, son grandes, y en muchos casos superiores a los de

diseo y realizacin de las distintas unidades funcionales utilizadas.

La reutilizacin de diseos, hecha posible por medio de su definicin y

almacenamiento en libreras de diseo, as como el uso de diseos genricos

parametrizables, son elementos importantes en el desarrollo de nuevos sistemas

digitales. La reutilizacin de diseos permite aumentar la confiabilidad de un

nuevo diseo, al presentar componentes depurados y as reducir la posibilidad de

errores y a la vez reducir el tiempo y costo de desarrollo del nuevo diseo.

A continuacin se presenta una metodologa general "Top-Down" estructurada para el

desarrollo de diseos de tipo digital, con la cual se aborda de una manera coherente las

etapas en el proceso de diseo y se pueda acoplar a mltiples tcnicas o tecnologas de

implementacin.

Las fases de la metodologa se deducen de los procesos obvios de diseo, buscando se

tomen en cuenta la mayor cantidad de consideraciones en el desarrollo, para as

incrementar la garanta de la obtencin de un producto con un desempeo funcional

correcto.

Actualmente se cuenta con una gran variedad de tecnologas de implementacin,

empezando por aquellos dispositivos de funciones estndar o funcin fija

(compuertas, registros, contadores, multiplexores, decodificadores, sumadores, etc),

dispositivos lgicos programables (PALs, PLAs, PLDs, FPGAs, PLSs, ROMs),

microprocesadores y microcontroladores, hasta la posibilidad de implementacin de

diseos en circuitos integrados de aplicacin especfica (ASIC) no programables, es

decir aquellos diseos en los que se aborda el desarrollo de circuitos integrados para su

fabricacin y en los cuales se pueden integrar mltiples funciones con una

complejidad considerable.

Esta gama de potenciales tecnologas de implementacin, obliga a un diseador a

evaluar las ventajas existentes entre un tipo de implementacin y otra. Aunque

algunos tipos de aplicacin o mdulos de la misma se prestan de manera directa a ser

implementados con una tecnologa en particular, la implementacin de los otros ser

definida prcticamente por los deseos, conocimientos o criterios del diseador, basado

posiblemente en su experiencia previa o restricciones del medio. Para facilitar este

tipo de evaluacin se debe adoptar una metodologa que gue al diseador en su

decisin, facilite el desarrollo al mximo de un diseo de manera independiente a la

tecnologa, utilice las facilidades brindadas por los recursos disponibles y genere una

documentacin manejable con informacin til, para hacer que el diseo obtenido

pueda ser abordado nuevamente (retomado, actualizado, mejorado, etc) de forma

eficaz.

1.0.0 FASES PARA LA IMPLEMENTACIN DE UNA APLICACIN

1.0.0.0 FASE DE DISEO

Es la primera fase del desarrollo lgico. Aqu se tienen en cuenta los aspectos

involucrados en el diseo terico, desde la definicin de las funciones necesarias a

partir de las especificaciones, hasta lograr una implementacin de la solucin a nivel

digital.

Esta fase conlleva la realizacin de las siguientes etapas:

1. Planteamiento del problema. Consiste en dar una clara y completa descripcin

funcional del problema a ser solucionado, usando criterios que permitan visualizar las

necesidades del requerimiento en cuanto a: restricciones de potencia y velocidad,

condiciones para interfazarse hacia el exterior del sistema (cantidad y tipo de seales),

etc. Dada la complejidad del diseo a abordar y con base en los criterios anteriores se

puede realizar una modularizacin inicial que permita descomponer el problema en

mltiples problemas de menor complejidad, generando un diagrama en bloques con

una notacin clara que no permita ambigedad entre las diferentes seales que

conforman el sistema.

En esta etapa por consiguiente se genera la documentacin que contiene los

requerimientos del diseo y un diagrama en bloques que describe las seales e

interfaces a utilizar.

2. Descripcin. Del anterior diagrama en bloques, el diseador deriva una

descripcin funcional detallada. Esta puede tomar varias formas dependiendo de la

aplicacin y de las preferencias del diseador. Comnmente, esta expresin se hace

mediante el uso de tablas de operacin funcional (tablas de verdad o tablas de estado)

o mediante el uso de diagramas de tiempo o esquemticos. En esta etapa debe

seleccionarse el tipo de implementacin con el que se realizar cada mdulo con

respecto a Hardware y Software. Se realizar una implementacin HW normalmente

en mdulos con funciones de mediana o baja complejidad o con altos volmenes de

produccin. Las implementaciones SW utilizando una plataforma PC o similar, se

utilizan normalmente para la implementacin de funciones complejas y de baja

produccin, adems de permitir una interfaz de manejo ms natural y amable al

usuario. Caben dentro de la categora SW, implementaciones de mdulos con base en

microcontroladores y similares.

La descripcin de los diferentes mdulos HW puede hacerse de diversas maneras,

entre las cuales estn: ecuaciones Booleanas, tablas de verdad, diagramas de tiempo

tabulados, tablas de estado, un lenguaje de alto nivel, diagramas esquemticos,

diagramas de estado, etc. Estos pueden ser manejados por el diseador en forma

individual o en combinaciones de ellos. Una vez realizada esta especificacin inicial

del sistema, el diseador debe obtener una descripcin que se preste a la

implementacin del mismo, es decir una descripcin optimizada a nivel de

componentes (ecuaciones Boolenas, planos, etc.) lista para poder abordar la

implementacin fsica de la misma.

1.0.0.0 FASE DE SIMULACIN

La simulacin es una parte integral en el proceso de diseo. Consiste en aplicar

niveles a las entradas y probar las respuestas en las salidas, para asegurar que el diseo

lgico de entrada opere correctamente. Es muy importante entonces contar con

herramientas software que permitan evaluar la correcta funcionalidad de las

descripciones realizadas.

En este paso se generan los vectores de diseo los cuales pueden ser derivados

directamente de las tablas de verdad, de los diagramas de tiempo o de la forma

escogida para describir el sistema. Esto debe ser elaborado manualmente si no se

dispone de un mdulo de simulacin.

El conjunto de vectores de diseo y los resultados de la simulacin deben formar

parte de la documentacin.

1.0.0.0

PARTICIN

En esta etapa debe seleccionarse el tipo de implementacin con el que se realizar

cada mdulo con respecto a Hardware y Software. Se realizar una implementacin

HW normalmente en mdulos con funciones de mediana o baja complejidad o con

altos volmenes de produccin. Las implementaciones SW utilizando una plataforma

PC o similar, se utilizan normalmente para la implementacin de funciones complejas

y de baja produccin, adems de permitir una interfaz de manejo ms natural y amable

al usuario. Caben dentro de la categora SW, implementaciones de mdulos con base

en microcontroladores y similares.

1.0.0.0 FASE DE IMPLEMENTACIN

El diseador debe inicialmente seleccionar el tipo de tecnologa para la

implementacin de cada mdulo. Los mdulos descritos en forma esquemtica son

directamente implementables con circuitos integrados de funcin fija, aunque

dependiendo de las herramientas disponibles, este tipo de descripcin puede ser

sintetizado en una tecnologa de implementacin diferente como un PLD, un FPGA u

otro tipo de ASIC. Las descripciones obtenidas con ecuaciones boolenas pueden ser

implementadas en forma discreta (compuertas) aunque normalmente ser ms ptima

la utilizacin de algn elemento programable. Dependiendo de factores como

cantidad de productos a obtener, complejidad del mismo, restricciones

fsicas/ elctricas, es posible que sea vlida la realizacin de un ASIC en el cual se

pueda incorporar todo el sistema o un parte importante del mismo. El tipo de

descripcin no necesariamente debe comprometer el tipo de implementacin, as,

descripciones tipo hardware pueden ser desarrolladas en soluciones software y

viceversa.

Para ls mdulos hardware, una vez seleccionada la tecnologa se debe realizar el

proceso de sntesis, el cual consiste en traducir la descripcin hasta ahora lograda al

formato o lenguaje necesario para su posterior implementacin fsica. Con las

concecuentes etapas de simulacin, optimizacin y resimulacin, para asegurar un

diseo funcionalmente correcto. Para los mdulos Software es necesario seleccionar

previamente una arquitectura con un protocolo de comunicacin preestablecido con el

hardware del sistema. La sntesis de los mdulos software son equivalentes a la

compilacin de las descripciones, obtenindose como resultado un archivo en el

lenguaje de mquina del sistema microprocesado seleccionado. Es de vital

importancia poseer facilidades de simulacin previa implementacin real de estos

mdulos.

Una vez obtenida la implementacin fsica del sistema (prototipo) se debe validar su

correcta operacin, esta fase es equivalente a la de simulacin en donde los vectores o

estmulos de entrada sern aplicados directamente sobre las entradas del circuito real y

se debe obtener una respuesta elctrica (funcional) equivalente a la obtenida en

simulacin.

Se proceder entonces a la integracin de los diferentes mdulos, para validar su

funcionamiento de manera global.

Un aspecto importante en esta metodologa de diseo, es que cubre el diseo de un

sistema completo involucrando mdulos hardware y software. El objetivo final es el

de obtener previa implementacin fsica de los mdulos que los constituyen, una

simulacin funcional completa del sistema. El soporte de esta metodologa esta ligado

a las facilidades que se dispongan para realizar sntesis de las descripciones realizadas

(Codescripcin y cosntesis) y a las tcnicas de validacin concurrentes de los mismos

(Cosimulacin y coverificacin).

1.0.0.0 DOCUMENTO

Finalmente, despus de terminado el proceso de diseo e implementacin de un

sistema, se debe recopilar la documentacin que genera cada etapa. Esto es de gran

importancia para la determinacin de posibles errores y problemas, adems de

permitir la abstraccin de las funciones que desempea el diseo y mejorar la

mantenibilidad del mismo. Adems, esta documentacin permite su utilizacin como

gua de la aplicacin prctica de la metodologa, o como base para desarrollos

similares, ya que se trata de sistemas que pueden generalmente acomodarse fcilmente

a otras aplicaciones.

En la siguiente grfica se resume un proceso estructurado de diseo para diferentes

tecnologas de implementacin.

1.0 HERRAMIENTAS CAD

Debido al aumento de la complejidad de los sistemas digitales, se crearon herramientas

software para proporcionar ayuda al diseador, dichas herramientas reciben el nombre

genrico CAD (Computer Aided Design) y se clasifican segn su funcin en:

Modelado

Captura Esquemtica

HDL

Sntesis

Sntesis de alto nivel

Sntesis lgica

Simulacin

Funcional

A nivel de transistor

Ubicacin e interconexin (Place and Route)

Reglas de Diseo (Design Rule Check)

Extraccin del circuito (LVS)

Test.

Generacin de vectores de test

Cobertura de fallos.

1.0.0 HERRAMIENTAS DE MODELADO

Las herramientas de modelado permiten realizar descripciones del sistema con

diferentes niveles de abstraccin, estas herramientas estn divididas en dos grupos:

1.0.0.0 CAPTURA ESQUEMTICA

Permite seleccionar componentes de una determinada librera e interconectarlos de

una forma grfica.

Los diseos basados en captura esquemtica aumentan las capacidades de las

ecuaciones booleanas ya que permiten utilizar adems de las compuertas lgicas

bsicas otros elementos ms complejos (Decodificadores, contadores, etc) . Estos

elementos pueden estar formados por compuertas, Flip Flops y otros circuitos,

permitiendo generar diseos jerrquicos que incorporan un gran nmero de

ecuaciones booleanas con menos esfuerzo que el que se requiere con las ecuaciones

booleanas. Muchas personas prefieren la entrada esquemtica ya que esta muestra ms

claramente las relaciones entre los diferentes bloques de diseo.

En este tipo de descripcin, el sistema se especifica como una red de elementos

interconectados. La especificacin informal de un sistema es dada en la forma del

comportamiento esperado del sistema (Que debe hacer el sistema ante una serie de

eventos). En el diseo tradicional esta descripcin es trasladada a un sistema de

ecuaciones booleanas, en este punto se inicia el proceso de captura esquemtica.

Algunos diseadores con mayor experiencia pueden realizar la transicin de la

especificacin formal a la captura esquemtica.

DESCRIPCION

INFORMAL

ECUACIONES

BOOLEANAS

CAPTURA

ESQUEMATICA.

SINTESIS

1.0.0.0 LENGUAJES DE DESCRIPCION DE HARDWARE

El principal inconveniente del mtodo tradicional es la transicin manual de la

especificacin formal del sistema a un set de ecuaciones lgicas. Este paso puede

eliminarse completamente utilizando Lenguajes de Descripcin de Hardware (HDL).

Por ejemplo, la mayora de las herramientas HDL permiten el uso de mquinas de

estado para sistemas secuenciales y tablas de verdad para sistemas combinatorios.

Tales descripciones pueden convertirse automticamente a un cdigo HDL y

posteriormente implementarse por las herramientas CAD.

DESCRIPCION

INFORMAL

ESPECIFICACION

EN HDL

SINTESIS

Los mtodos de diseo descritos anteriormente parecen ser suficientes. Sin

embargo muchos de ellos se utilizan en pequeas partes del proceso. Para realizar un

diseo se debera cambiar de una descripcin de diseo a otra o de una herramienta a

otra. Lo cual lleva a buscar compatibilidad entre las herramientas y a dominar nuevos

ambientes de diseo.

1.0.0 HERRAMIENTAS DE SINTESIS

La sntesis lgica es el proceso mediante el cual se pasa de una descripcin de alto

nivel (HDL) a una descripcin a nivel de compuertas para una tecnologa dada.

Adems de permitir la transformacin de:

Ecuaciones booleanas en compuertas

Una descripcin de mquinas de estado a compuertas y flip flops

Minimizacin de:

Nmero de compuertas

Retardo de propagacin

Area y/ o consumo.

Las principales ventajas de la sntesis son: Reduccin del ciclo de diseo,

independencia del diseo frente a la experiencia del diseador, adems de modelar el

sistema de una forma independiente de la tecnologa y posteriormente sintetizarlo.

1.0 VHDL

VHDL es la sigla de : V Very High Speed Integrated Circuit (Circuitos Integrados

de alta velocidad) y HDL Significa Hardware Descrption Language (Lenguaje de

Descripcin de Hardware). Este nombre ha sido dado por el departamento de

Defensa de los Estados Unidos, los cuales fueron los primeros en utilizar los

beneficios del lenguaje. Bajo su patrocinio el VHDL ha sido desarrollado e

introducido en los aplicaciones de diseo electrnico.

Los primeros simuladores aparecieron a principios de los 90s y hasta 1994 se

pudo disponer de una versin para PC y los diseadores de PLD y FPGA

comenzaron a utilizarlo en grandes diseos.

Note que la palabra Sntesis no fue mencionada como razn para la creacin del

VHDL, el VHDL inicialmente fue diseado como una herramienta de simulacin,

modelaje y documentacin. La sntesis fue implementada por algunos investigadores

que lo vean como una forma de automatizar el proceso de diseo.

Sin una plataforma comn de diseo, un proyecto dividido en varios equipos de

trabajo requerira un trabajo adicional para coordinarse de tal forma que todas las

partes se integren entre s. Cuando se utiliza en lenguaje universal los equipos de

trabajo pueden compartir fcilmente sus trabajos

1.0.0 ESTANDARIZACIN.

A pesar del hecho que el VHDL estuvo ligado fuertemente al Departamento de

defensa de los Estados Unidos, se utiliz rpidamente en diseos no militares. Gracias

a la estandarizacin y divulgacin realizada a travs de la IEEE (Institute of Electrical

and Electronic Engineering). El primer standard de VHDL aparece en 1993.

Respondiendo a las necesidades de los diseadores, varios grupos de expertos han

puesto sus esfuerzos para hacer un lenguaje ms universal. Estos esfuerzos dieron

como frutos algunos estndares que hacen parte del principal 1076 (IEEE VHDL

STANDARD) :

El Standard 1076 contiene la definicin del lenguaje. Tiene dos versiones la 1076-87 y

la 1076-93 relacionadas con su ao de publicacin. A pesar de que la versin 1076-93

se puede conseguir fcilmente algunas herramientas de trabajo estn limitadas a la

versin 1076-87:

1076.1 : Extensin anloga Ha sido propuesta para la especificacin de sistemas

anlogos y mixtos.

1076.2 : Utilidades Matemticas.

1076.3 : Destinado a realizar sntesis en VHDL.

1076.4 : VITAL (VHDL Initiative Toward ASIC Libraries) Estandarizacin de

circuitos integrados de aplicacin especfica.

1076.5 : Librera VHDL

1164 : Extiende el lenguaje VHDL co. lgica multi-valor necesaria para describir

sistemas en tiempo real.

1029 : VHDL Waveform and Vector Exchange Specification define los formatos de

datos para pruebas y verificacin de tiempos.

1.0.0 VENTAJAS AL UTILIZAR VHDL

Permite diseos modulares y jerrquicos. Soporta diferentes metodologas de diseo.

Soporta varias tcnicas de modelado digital:

Descripcin algortmica

Ecuaciones booleanas

Mquinas de Estados Finitos

Soporta temporizacin:

Sncrona

Asncrona

Es un lenguaje concurrente, aunque permite definir dominios en los que las acciones

se suceden en un orden secuencial.

Permite simular el diseo y generar formas de onda

Soporta diferentes tipos de descripcin

Comportamental

RTL

Lgico

A partir de un modelo en VHDL se puede sintetizar Hardwarea nivel de puertas con

herramientas de sntesis.

Es el lenguaje de Descripcin de hardware ms utilizado.

Los sistemas se pueden especificar de forma estructural o comportamental a

diferentes niveles de detalle.

1.0 UNIDADES BASICAS EN VHDL

Todo sistema debe tener una forma de comunicacin desde y hacia el entorno donde

el opera. Esta funcin de comunicacin recibe el nombre de interfaz, si no existiera

esta interfaz, el sistema podra no tener uso alguno. (Imagine un computador tpico

con sus perifricos: Mouse, Keyboard y monitor estos elementos constituyen la

interfaz del computador y son de suma importancia).

En VHDL la interfaz esta descrita por su entidad (Entity), la cual constituye la

unidad bsica de diseo de cualquier sistema y realiza una abstraccin Hardware del

mismo. As como es imposible tener un sistema sin interfaz no se puede concebir un

sistema VHDL sin una entidad.

Para lograr el funcionamiento deseado, los datos de entrada deben sufrir alguna

transformacin dentro del sistema. Esta transformacin y salida de datos son

realizadas por la parte interna del sistema la cual recibe el nombre de arquitectura

(Architecture).

Algunos sistemas pueden presentar caractersticas adicionales al utilizar elementos

externos. Un ejemplo de dichos elementos puede ser una tarjeta que acelera las

operaciones grficas en un computador. Tales tarjetas adicionales pueden ser

consideradas parte del sistema pero para mayor claridad las consideraremos como un

tercer componente del sistema y lo denominaremos Paquetes (Package).

1.0.0 UNIDAD PRINCIPAL DE DISEO: ENTITY

Ya que al iniciar cualquier diseo lo primero que se hace es realizar un estudio de su

entorno (Conexin con otros sistemas), la entidad, la cual describe la interfaz entre el

sistema y su ambiente debe ser la principal unidad de cualquier especificacin.

No existe una especificacin en VHDL de cualquier sistema si no se declara la

entidad. Ms an cualquier especificacin de entidad es automticamente visible desde

las dems unidades de diseo asociadas con esta entidad. Por lo tanto el nombre del

sistema debe ser el mismo nombre de la entidad. (Todo diseo en VHDL comienza

con la declaracin de una entidad).

La entidad suministra la interfaz del sistema y esta compuesta por dos partes:

Parmetros del sistema: que son vistos desde el exterior, como por ejemplo el

ancho del bus de un microprocesador, la mxima frecuencia de operacin, etc.

Conexiones: Las cuales transfieren datos desde y hacia el sistema.

Ejemplo:

entity Eight_bit_register i s

LENGTH = 8

fmax = 50MHz Parmetros

D_IN eight_bit Input

D_OUT eight_bit Output Conexiones

CLK One bit Input

end entity Eight_bit_register;

Los elementos de la interfaz (Parmetros y conexiones) tienen sus propias

declaraciones dentro de la entidad:

Todos los parmetros son declarados como genricos y son pasados al cuerpo del

sistema.

Las conexiones pueden transmitir datos desde y hacia el sistema y reciben el nombre

de puertos (ports) y forman la segunda parte de la entidad.

Ejemplo:

entity Eight_bit_register is

generic(

LENGTH = 8

fmax = 50MHz Parmetros

);

port(

D_IN eight_bit Input

D_OUT eight_bit Output Conexiones

CLK One bit Input

);

end entity Eight_bit_register;

1.0.0 ARQUITECTURA

En VHDL la arquitectura est encargada de realizar operaciones con los datos, cada

entidad debe tener por lo menos una arquitectura.

Ejemplo:

entity cain is

....

end entity cain

architecture abel of cain is

.....

end architecture abel

Todo sistema puede ser especificado en trminos de su funcionalidad (Behavoir) o en

trminos de su estructura, las cuales requieren diferentes clases de informacin sobre

el sistema. Para un mejor entendimiento de la diferencia entre descripcin funcional y

estructural debemos realizar las siguientes preguntas:

Que funcin realiza (Funcional)

Como est compuesto (Estructural)

La descripcin funcional especifica el comportamiento que se espera del sistema ante

una determinada entrada.

La descripcin estructural especifica que elementos se utilizan y como estn

conectados para lograr el comportamiento deseado. En otras palabras describe la

estructura interna del sistema.

Los diseos estructurales son ms fciles de sintetizar que los funcionales ya que el

primero se refiere a componentes fsicos. Sin embargo son ms difciles de crear ya

que requieren cierta experiencia por parte de los diseadores para ser ms efectivos.

Ya que diferentes tipos de arquitecturas pueden realizar la misma funcin, un sistema

(entity) puede ser especificado con diferentes arquitecturas. Sin embargo lo contrario

no es cierto, ya que la arquitectura no debe tener diferentes interfaces. Y no puede ser

asignada a diferentes entidades.

Dependiendo del tipo de sentencias utilizadas se puede modelar una arquitectura

de las siguientes formas:

Algortmica: Define la funcionalidad del componente mediante un algoritmo

compuesto por un conjunto de instrucciones que se ejecutan secuencialmente.

Ejemplo:

architecture Algoritmico of Cain is

begin

process (a, b, ctrl)

begin

if (ctrl = 0) then

z <= a;

else

z <= b;

end if;

end process;

end Algortmico;

Flujo de Datos: Modela la arquitectura como un flujo de datos entre distintos

mdulos encargados de implementar funciones u operadores.

Ejemplo:

architecture FlujoDatos of Cain i s

signal ctrl_n, n1, n2 : bit;

begin

ctrl_n <= not (ctrl) after 1 ns;

n1 <= ctrl_n and a after 2 ns;

n2 <= ctrl and b after 2 ns;

z <= (n1 or n2) after 2 ns;

end FlujoDatos;

Estructural: Define la arquitectura como un conjunto de componentes

interconectados.

Ejemplo:

architecture Estructural of Cain i s

signal ctrl_n, n1, n2 : bit;

component INV

port( y : in bit;

z: out bit);

end component;

component AND2;

port( x: in bit;

y : in bit;

z : out bit);

end component;

component OR2

port( x : in bit;

y : in bit;

z : out bit);

end component;

begin

U0 : INV port map (ctrl, ctrl_n);

U1: AND2 port map (ctrl_n, b, n1);

U2 : AND2 port map (ctrl, b, n2);

U3 : OR2 port map (n1, n2, z);

end Estructural;

1.0.0 CONFIGURACION

Como vimos anteriormente se pueden asignar varias arquitecturas a una entidad. Al

momento de simular el modelo se debe especificar cual de las arquitecturas se va a

utilizar. La configuracin es la construccin VHDL encargada de seleccionar la

arquitectura que se quiere utilizar para una entidad concreta. Ms adelante se tratara

con detalle este tema.

1.0.0 EL CONCEPTO DE PAQUETE (PACKAGE).

Que hacemos normalmente cuando nos encontramos ante un concepto o una palabra

desconocida. Lo ms probable es consultar a otra persona o buscar en un diccionario.

Si se planea usar un diccionario, se puede decir que se va a utilizar una unidad de

librera (un libro). Ms an si nos encontramos lejos de una tienda de libros la tienda

puede enviarnos el libro por correo en un paquete. Se utilizarn packages (fuentes

externas de descripcin) cuando se utilicen sentencias que no estn incluidas dentro

del lenguaje Standard.

Una situacin similar a la expuesta anteriormente puede presentarse con las

descripciones en VHDL; eventualmente se pueden necesitar funciones que no se

encuentran en las libreras Standard del VHDL. Los packages nos permiten hacer la

definicin de estas funciones no soportadas por el standard.

La nica restriccin en el uso de packages, es que es necesario que sean declarados

antes de ser usados, usualmente estn al inicio de una entidad. Existen dos clusulas

que utilizaremos para la declaracin: library y use.

Por ejemplo supongamos que vamos a utilizar el concepto Save_To que se

encuentra definido en el package Cain de la librera NewConceptLib.

Lo primero que debemos hacer es declarar la librera que vamos a utilizar, esto lo

hacemos utilizando la clusula Library. A continuacin debemos indicar que

componente de la librera usaremos, esto se realiza con la clusula Use. La sentencia

Use realiza la siguiente funcin Useel conceptoSave_Toel cual est definidoen el package

Cain almacenadoen la librera NewConceptLib.

1.0.0.0 PACKAGES PREDETERMINADOS.

El VHDL es un ambiente de diseo robusto y tiene varios packages predefinidos. Los

packages definidos por la IEEE son:

STANDARD : Contiene todas las declaraciones bsicas y definiciones del lenguaje y

se incluye por defecto en todas las especificaciones, por lo tanto el uso de Library u

Use no es necesario.

TEXTIO: Contiene declaraciones de operaciones bsicas de lectura y escritura sobre

texto. Estas operaciones no son sintetizables y se utilizan para simulacin y

modelamiento nicamente. Para utilizar este package se debe incluir antes de la

declaracin de la entidad:

library Std;

use Std.TextIO.all;

STD_LOGIC_1164: Extensiones al VHDL standard, definidos por el standard IEEE

1164: Valores Lgicos mltiples, funciones de resolucin y operadores extendidos. La

declaracin de la entidad debe precederse por:

library IEEE;

use IEEE.Std_Logic_1164.all;

Adems de los packages de la IEEE cada vendedor de la herramienta adiciona sus

propios packages, en estos casos normalmente la librera lleva el nombre del

vondedor.

CUESTIONARIO

La entidad proporciona el nombre del sistema y sus conexiones nicamente

Las especificaciones estructurales pueden ser jerrquicas.

Un objeto declarado en un package puede utilizarse si est localizado en el mismo

directorio de la entidad.

Las nicas unidades de diseo son las entidades (entity) y las arquitecturas

(architecture)

Las entradas del sistema reciben el nombre de generics y las salidas el de ports

Una entidad puede ser asignada a mltiples arquitecturas.

Todo sistema debe tener una interfaz

Para utilizar un package standard la entidad debe estar precedida por las clusulas

library y use.

Todo sistema especificado en VHDL est compuesto de una entidad y una

arquitectura.

La entidad es lo ms importante para un sistema VHDL

Una arquitectura se especifica con base en una entidad.

Una arquitectura puede ser asignada a varias entidades.

La sntesis de una descripcin funcional es ms fcil que la de una comportamental.

1.0 EL CONCEPTO DE SEAL

Uno de los fenmenos ms importantes en el mundo es el proceso de comunicacin.

Nosotros compartimos mucha informacin con otras personas; La comunicacin

siempre involucra la transmisin de informacin desde el mensajero hasta el receptor,

y existen varias formas de realizarla, pero todas tienen algo en comn: Las seales.

La comunicacin no se limita a los seres vivos, las mquinas tambin se pueden

comunicar. Por ejemplo un sensor puede informar a un circuito el estado en cada

momento de una determinada variable fsica. Las seales cumplen un papel muy

importante en la operacin de los dispositivos electrnicos ya que no se pude concebir

un sistema electrnico que no enve o reciba alguna seal. Ya que el VHDL fue

diseado para describir la operacin de un sistema electrnico, las seales juegan un

papel muy importante en la descripcin de la comunicacin entre circuitos o bloques.

Fsicamente una seal es un flujo de electrones que estn regidos por las leyes de la

fsica. Sin embargo al utilizar el VHDL no debemos preocuparnos por estas leyes ya

que la sntesis lgica se encarga de tener en cuenta dichas leyes al crear la conexin

fsica. Todo lo que se necesita hacer es especificar la funcionalidad y comportamiento

del circuito.

Los diseos electrnicos estn basados en componentes y las lneas de seal

comunican los componentes entre s. Estas lneas de seal pueden implementarse

como una conexin o mltiples conexiones.

Una conexin simple puede representarse por una seal la cual puede tomar un valor

binario. Un ejemplo de tal conexin es la seal de reloj utilizada para sincronizar todos

los eventos del sistema.

Algunos diseadores incluyen seales de mltiples lneas, llamadas buses o vectores,

las cuales transmiten informacin como combinacin de valores binarios.

1.0.0 SEALES BIT Y BIT_VECTOR.

Seal simple y Vector son palabras que describen muy bien los diferentes tipos de

seales en los circuitos electrnicos. Ya que se necesita una especificacin formal de

las seales, consideraremos dos tipos de seales, los cuales pueden ser usados para

especificar cualquier seal.

Los tipos de seales permitidos por VHDL, son llamados bit (para seales simples) y

bit_vector (para buses). En ambos casos cada lnea de la seal puede tomar los

valores lgicos 0 o 1. En el caso de los buses es necesario definir su ancho

(Nmero de lneas que lo conforman).

1.0.0 ANCHO DEL BUS Y ORDEN DE LOS BITS.

Cuando se trabaja con seales de un bit es muy fcil hacer la declaracin, solamente se

utiliza el prefijo bit. Sin embargo, describir un bus es ms complejo. Primero se debe

escribir la Clusula bit_vector indicando que trabajaremos con vectores. A

continuacin se debe especificar el ancho del bus y el orden de los bits. Por ejemplo

supongamos que tenemos un bus de 8 bits: el sptimo bit es el ms significativo y el

bit 0 el menos significativo, para realizar la descripcin de este bus debemos escribir:

bit_vector (7 downto 0).

Pero si deseamos que el bit 0 sea el ms significativo y el 7 el menos significativo

debemos escribir: (0 to 7).

En conclusin el formato para definir un bus en VHDL es:

bit_vector (MSB to/downto LSB).

Donde MSB y LSB son nmeros enteros y representan respectivamente los bit ms y

menos significativos del bus, se utilizar to cuando MSB sea menor que LSB y

downto cuando MSB sea mayor que LSB.

1.0.0 SEALES EXTERNAS E INTERNAS

Las seales pueden clasificarse de dos formas:

Externas: Son seales que conectan al sistema con su entorno.

Internas: Las cuales no son visibles desde el exterior y estn contenidas

completamente dentro el sistema y forman parte de su estructura interna.

Recuerde que existe una distincin similar entre la entidad (entity) y la arquitectura

(architecture). En efecto las seales externas son declaradas en la entidad y las internas

son declaradas exclusivamente en la arquitectura.

Las seales que conectan a un sistema con su entorno reciben el nombre de puerto

(port) y son definidas en la seccin port de la entidad., la cual define la interfaz de la

entidad.

1.0.0 DECLARACIN DE SEALES EXTERNAS.

Toda seal debe tener un nico nombre y un nico tipo, adems las seccin port debe

informar la direccin del flujo de informacin los tipos bsicos soportados por VHDL

son denominados modos (modes) y son: input, output e inout (bidireccional). El

tipo de seal debe indicarse explcitamente (de lo contrario implcitamente se adopta

como de entrada: mode in). En VHDL esto se realiza al definir el modo de cada seal

de la interfaz. Por lo tanto la sintaxis de un puerto es la siguiente:

port_name : mode port_type

A pesar del hecho que VHDL soporta cinco tipos de seales:

IN : El puerto recibe datos nicamente, y solo permite lectura.

OUT : El puerto enva datos y slo permite escritura.

INOUT : El puerto es bi-direccional y permite la lectura y escritura.

BUFFER : Similar a inout pero restringido a escritura.

LINKAGE : Tambin un puerto bidireccional pero con reglas de restriccin.

Es recomendable utilizar solo los tres primeros ya que los dems no son soportados

por todas las herramientas de diseo.

Ejemplo de declaracin:

port ( RESULT : inout bit_vector (0 to 7);

z : in bit;

EXT : out bit_vector (4 downto 0));

1.0.0 DECLARACIN DE SEALES INTERNAS.

La entidad describe la interfaz del sistema con el mundo exterior y la arquitectura todo

lo que reside en el interior del sistema. Las seales internas no son la excepcin, y para

distinguirlas de otros objetos en el cdigo de VHDL se debe utilizar la clusula signal

en cada declaracin.

Las seales internas no requieren declaracin de modo (in, out, inout).

1.0.0 VISIBILIDAD DE LAS SEALES

La visibilidad de cada seal est dada por el sitio en donde se declara.

Una seal declarada en un package se puede ver en todas las unidades de diseo que

utilicen este package;

Una seal declarada como puerto en una entidad es visible en todas las arquitecturas

asignadas a la entidad.

Una seal declarada en una arquitectura es visible solo dentro de la arquitectura.

Una seal declarada en un bloque localizado dentro de una arquitectura es visible solo

dentro de este bloque.

Estas reglas resultan de la jerarqua del diseo: Si alguna seal es declarada en un nivel

de jerarqua, puede ser visible en los niveles inferiores de jerarqua.

1.0 ESPECIFICACION DE LA INTERFAZ

El nombre de una entidad, llamado formalmente identificador, se utiliza

principalmente para propsitos de documentacin. Por lo tanto debe escogerse un

nombre que describa su funcin ya que el VHDL no es case sensitive (no es sensible a

maysculas ni minsculas) Es preferible que el nombre se escriba en forma mixta por

ejemplo: Contador_Binario.

Cada identificador en VHDL incluyendo el nombre de la entidad debe seguir las

siguientes reglas:

Debe ajustarse en una sola lnea.

Debe comenzar con una letra.

Debe estar compuesto nicamente por letras nmeros y underscores.

No debe iniciar o terminar con underscores o tener dos underscores seguidos.

No se permiten espacios

No se diferencia entre caracteres en mayscula o minscula.

No se pueden utilizar palabras reservadas.

La entidad se termina con la clusula end y es recomendable utilizar despus entity y

el nombre de la entidad:

end entity Nombre_de_la_Entidad

1.0.0 COMENTARIOS EN VHDL:

No existe un buen diseo sin documentacin, los comentarios dentro del cdigo

facilitan su posterior lectura ya sea por su creador o por otros usuarios del cdigo. Los

comentarios en VHDL comienzan con dos signos menos y terminan con un final de

lnea (Enter). Ellos pueden localizarse en cualquier parte pero no deben empezar entre

una palabra reservada o de un identificador.

--Este es un ejemplo de comentario

1.0.0 SIGNIFICADO DE PUERTO.

Un puerto est definido como: Canal de comunicacin dinmica entre un bloque y su

entorno.

1.0.0 QU ES UN GENRICO.

Un genrico es un canal esttico de informacin que debe comunicarse a un bloque

desde su entorno. En otras palabras, los genricos proporcionan valores constantes

para diferentes parmetros. Esto significa que las declaraciones genricas deben ser

colocadas dentro de la entidad del sistema, el cual provee comunicacin entre un

sistema y su entorno. Los genricos son usados para describir valores constantes. Por

ejemplo ellos pueden controlar el tamao de un modelo, en particular el ancho de los

buses y el tamao de los mdulos parametrizados tales como sumadores o

comparadores de n bits. Tambin pueden utilizarse para parmetros de tiempo.

Ejemplo:

entity Mi_Proyecto is

generic(BusWidth : Integer := 4);

MaxDelay : time := 20ms;

port (..

DataBus : inout bit_vector (BusWidth 1 downto 0);

....

);

end entity Mi_Proyecto;

Los genricos son declarados en las entidades dentro de la clusula generic, la cual se

localiza antes de port, la clusula generic est formada por el comando generic y una

lista encerrada en parntesis, dicha lista esta separada por punto y coma.

Cada declaracin generic consta de:

Un nombre seguido por una coma.

El tipo de genrico.

Opcional: El valor del genrico es precedido por el smbolo :=.

Opcional: Un comentario que indica cual es la funcin del genrico.

Los genricos se utilizan cuando se necesita un valor esttico. En efecto, es

recomendado utilizar genricos cuando se trabaja con grandes diseos ya que facilitan

los cambios.

1.0 TIPOS DE DATOS.

Todo tipo de informacin almacenada dentro de un computador o de otro sistema

digital es almacenada en forma de bits o vectores de bits. Sin embargo, a menudo no

es conveniente utilizar esta forma, ya que los diferentes tipos de datos utilizan

diferentes nmero de bits, por lo que resulta ms prctico utilizar nmeros

hexadecimales.

Similarmente, muchas estructuras de datos ms complejas pueden representarse por

arreglos y parmetros fsicos. VHDL soporta este tipo de estructuras y parmetros

1.0.0 NO LGICOS

Escalares:

El tipo escalar es nombre genrico que agrupa todos los tipos cuyos objetos tienen

un valor nico en cualquier instante de tiempo. Los escalares no tienen elementos o

estructura interna. VHDL tiene predefinidos algunos tipos de escalares, sin embargo

se pueden especificar otros tipos. Los tipos de datos definidos por el usuario se

declaran como sub-tipos de un tipo de dato declarado con anterioridad, ya sea uno

standard o uno definido por el usuario.

Los tipos de datos predefinidos en VHDL son :

BOOLEAN, Declarado como:

type BOOLEAN is (false, true);

En VHDL los valores True/ False no son equivalentes a los niveles lgicos 1/ 0. Por lo

tanto no debe asumirse que TRUE es lo mimo que 1 y viceversa. Los tipos bit y

BOOLEAN son completamente diferentes en VHDL.

CHARACTER, Declarado como:

type CHARACTER i s (null, soh, ..., a, b, c, ...);

El set de valores especificado en el tipo CHARACTER cubre todos los caracteres

definidos por el set ISO 8859-1 (Conocido como Latin-1). En general incluye

caracteres semi grficos y caracteres nacionales del occidente de Europa.

INTEGER, Declarado como:

type INTEGER i s range 2147483647 to 2147483647 (2 31).

El rango de los valores enteros depende de la implementacin pero debe estar

incluido dentro del rango especificado arriba. En el proceso de sntesis los enteros

estn limitados a un subset de un grupo (por ejemplo 0 a 15 0 0 a 99) con el fin de

reducir el nmero de elementos almacenados.

REAL, Declarado como:

type REAL is range 1.0E308 to 1.0E38

El tipo real es llamado aveces tipo de punto flotante (floating point), es especeficado

con un rango que es dependiente de la aplicacin. Sin embargo el rango especificado

debe ser el mnimo que debe ser cubierto por todas las aplicaciones. Tambin se debe

garantizar un mximo de seis dgitos decimales de precisin.

BIT, Declarado como:

type BIT i s (0, 1);

El tipo bit es numerado que define dos valores lgicos standard: 0 y 1. Este es el

nico tipo que puede ser usado para operaciones lgicas y a diferencia de diseos

basados en compuertas no puede asumirse que los valores lgicos son equivalentes a

los tipos booleanos.

1.0.0 TIPOS DEFINIDOS POR EL USUARIO:

Los diseadores a menudo requieren codificar alguna informacin del sistema para

obtener una mayor eficiencia o entendimiento. Un ejemplo tpico es una maquina de

estados (FSM) que representa un diseo secuencial.

Para propsitos de sntesis, cada estado de una mquina de estados es codificada con

variables de estado (flip flops) los cuales almacenan informacin del estado actual. Sin

embargo a nivel de especificacin es ms conveniente asignar un nico nombre a cada

estado y referirse a este estado por su nombre. Todos los nombres de los estados son

listados en la declaracin de un nuevo tipo de enumeracin.

Ejemplo:

type FSMStates is(S0, S1, S2, S3);

1.0.0 TIPOS FSICOS

Los tipos fsicos son nicos en VHDL porque ellos no-solo especifican los valores de

los objetos, sino tambin las unidades en las que los valores son expresados. Esto

permite definir las cantidades fsicas con precisin. El VHDL standard solo define el

tipo fsico tiempo, pero se pueden definir los que se requieran.

Por ejemplo:

type time i s range 2147483647 to 2147483647 (2 31)

units

fs;

ps = 1000 fs;

ns = 1000 ps;

us = 1000 ns;

ms = 1000 us;

sec = 1000 ms;

min = 60 sec;

hr = 60 min;

end units;

Existen dos tipos de unidades en la declaracin de tipos fsicos: La unidad primaria y

la unidad secundaria que se define en trminos de la unidad primaria. Note que el

rango especificado en el encabezado de la declaracin se refiere nicamente a la

unidad primaria. A pesar de su utilidad los tipos fsicos no son sintetizables.

1.0.0 ARREGLOS PREDEFINIDOS

Los arreglos son tipos de datos complejos, con una estructura regular y estan

formados por elementos del mismo tipo. El nmero de elementos de un arreglo est

determinado por su rango, dicho rango puede ser ilimitado o limitado; el rango

ilimitado se define como:

range <>

Existen dos arreglos predefinidos en VHDL: bit_vector (con elementos tipo BIT) y

string (con elementos tipo CHARACTER) ambos estn declarados con un rango

ilimitado. Sin embargo difieren en la declaracin de su lmite inferior: el primer

elemento de un bit_vector tiene un ndice 0 mientras que el del tipo string comienza

con 1.

Ejemplo

signal DataBus : bit_vector (7 downto 0):

DataBus = ...

DataBus(7)= .. ;

Note que un elemento del arreglo se especifica con comillas sencillas, mientras que

dos o ms elementos requieren comillas dobles para su declaracin.

1.0.0 ARREGLOS DEFINIDOS POR EL USUARIO

Debido a que los arreglos predefinidos tienen una dimensin, algunas veces reciben el

nombre de vectores. Sin embargo, se pueden declarar arreglos con un nmero

arbitrario de dimensiones. Una aplicacin tpica de los arreglos es una memoria, la cual

puede considerarse como un arreglo de bits de dos dimensiones. En una memoria real

los bits estn ordenados en palabras. Por ejemplo una memoria de 1K x 3 bits puede

describirse de la siguiente forma:

signal Mem1k4 : array (0 to 1023) of bit_vector (3 downto 0);

1.0.0 RECORDS

Los records al igual que los arreglos son tipos de datos complejos. Pero difieren de

ellos en que un record puede contener elementos de diferentes tipos. Al referirse a un

elemento de un record se debe seguir la siguiente expresin:

record_name.element_name

Estos nombres se escriben sin parntesis. La funcin principal de un record es agrupar

diferentes parmetros de objetos simples, cada uno de estos objetos es referenciado

por un nombre, lo cual hace que el cdigo sea ms compacto y leible.

Ejemplo:

type InsCain i s record

Processor : String;

DataMem : Integer;

ProgMem : Bit_Vector (7 downto 0);

end record;

signal intel, amd, motorola : InsCain;

...

intel.Processor : pentium

intel.DataMem : 1024

amd.processorv : k62

amd.DataMem : 2048

1.0.0 SUBTIPOS

El uso de subtipos permite restringir el rango de un tipo de dato escalar. La sintaxis

para la declaracin del subtipo es la siguiente:

subtype_declaration ::= subtype identifier i s subtype_indication ;

subtype_indication ::= [ resolution_function_name ] type_mark [ constraint ]

type_mark ::= type_name | subtype_name

constraint ::= range_constraint | index_constraint

Existen dos casos de aplicacin de los subtipos: Un subtipo puede restringir los

valores de un tipo de dato escalar a un rango especfico. Por Ejemplo:

subtype pin_count is integer range 0 to 400;

subtype digits is character range '0' to '9';

Un subtipo puede restringir cualquier arreglo ilimitado, indicando los ndices de

los lmites. Por ejemplo:

subtype id is string(1 to 20);

subtype word is bit_vector(31 downto 0);

Existen dos subtipos predefinidos en VHDL:

subtype natural is integer range 0 to highest_integer

subtype positive is integer range 1 to highest_integer

1.0.0 TIPOS DE ACCESO

Los tipos de acceso se utilizan cuando se conoce el tamao de los datos a almacenar,.

En algunas aplicaciones este tamao puede ser desconocido, o dependiente de la

ejecucin, por esta razn, VHDL proporciona apuntadores para crear estructuras de

datos dinmicas, estos apuntadores reciben el nombre de tipos de acceso. Su sintaxis

es la siguiente:

type identificador i s access tipo_datos;

1.0.0 TIPOS DE ARCHIVO

Un objeto tipo archivo se utiliza para el almacenamiento de datos de un determinado

tipo. Para poder realizar operaciones con archivos es necesario hacer su declaracin, la

cual debe indicar el tipo de datos a almacenar. La sintaxis es la siguiente:

type identificador i s file of tipo_objetos;

La biblioteca STD se define el paquete textioque proporciona el tipo archivo de texto

y las rutinas de lectura y escritura para trabajar con este tipo de archivos.

Concretamente se definen los siguientes tipos:

type line is access string;

type text i s file of string;

1.0 EXPRESIONES Y OPERADORES

En todos los sistemas las seales de entrada deben transformarse de alguna forma

para obtener las seales de salida deseadas. Este proceso puede visualizarse como:

Salidas transformacin de entradas.

Las transformaciones son realizadas por las expresiones: Frmulas que consisten en

operadores con un apropiado nmero de parmetros. En efecto cualquier

especificacin de un sistema funcional puede verse como un grupo de expresiones

sobre las entradas asignadas a las salidas.

El elemento bsico de cada expresin es el operador. Cada operador es asignado para

un determinado tipo de datos y requiere uno o varios parmetros, los cuales son

objetos sobre los cuales puede realizarse la operacin.

1.0.0 OPERADORES LGICOS

Ya que las seales en los sistemas digitales son seales lgicas, los operadores ms

utilizados en VHDL son los operadores lgicos. Los operadores lgicos realizan

operaciones entre dos parmetros tales como and, or, nand, nor, xor, xnor. El

operador not acta sobre un parmetro. Los operadores lgicos estn definidos para

los tipos de datos: bit y bit_vector, lo cual significa que los parmetros deben ser de

estos tipos. El resultado es del mismo tipo que el parmetro.

En el caso de bit_vector la operacin lgica se realiza sobre bits independientes.

Dependiendo del orden de los bits.

1.0.0 OPERADORES NUMRICOS:

Este nombre agrupa a los operadores que realizan operaciones sobre parmetros

numricos. Y cubre las operaciones suma, resta, multiplicacin, divisin, mdulo,

residuo, exponencial y valor absoluto.

Estos operadores pueden aplicarse sobre parmetros de tipo entero y real, pero se

necesita que ambos parmetros sean del mismo tipo. La nica excepcin a esta regla

es el exponencial ya que requiere que el argumento sea de tipo entero.

Adems de los tipos enteros y reales tambin se puede utilizar los datos tipo time con

los operadores numricos. En este caso, las reglas no son tan estrictas: La suma y resta

requiere que ambos parmetros sean de tipo time, pero un dato de tipo time puede

multiplicarse o dividirse por nmeros enteros o reales y el resultado es de tipo time.

1.0.0.0 SUMA

Smbolo:

+

Descripcin:

Suma dos valores numricos del mismo tipo y da como resultado un valor del mismo

tipo de los parmetros. Aplicable a datos tipo entero, real, tiempo, enteros y reales

universales (#%$&#%). Los valores universales pueden sumarse a su contraparte ms

general (Enteros universales con enteros y Reales universales con reales)

1.0.0.0 RESTA

Smbolo:

-

Descripcin:

Resta un valor numrico de otro del mismo tipo y da como resultado un valor del

mismo tipo de los dos parmetros. Aplicable a datos tipo entero, real, tiempo, enteros

y reales universales (#%$&#%). Los valores universales pueden a su contraparte ms

general (Enteros universales con enteros y Reales universales con reales)

1.0.0.0 MULTIPLICACIN

Smbolo:

*

Descripcin:

Multiplica dos valores numricos y el resultado es del mismo tipo de los parmetros

1.0.0.0 DIVISIN:

Smbolo:

/

Descripcin:

Divide dos valores numricos y da como resultado un nmero del mismo tipo.

1.0.0.0 MDULO

Smbolo:

mod

Descripcin:

Proporciona el residuo de una divisin entera.

Ejemplo:

6 mod 4 --Da como resultado 2

7 mod 3 --Da como resultado 1

1.0.0.0 RESIDUO

Simbolo:

rem

Descripcin:

Proporciona el residuo de una divisin entera. Esta definido para operandos de tipo

entero nicamente.

Ejemplo:

8 rem 3 --Da como resultado 2

9 rem 4 --Da como resultado 1

1.0.0.0 POTENCIA

Smbolo:

**

Descripcin:

Este operando requiere que el segundo operando sea de tipo entero y es equivalente a

una multiplicacin sucesiva del primer operando un nmero de veces que viene

determinado por el segundo operando.

Ejemplo:

A**2 --Es equivalente a A*A

A**4 --Es equivalente a A*A*A*A

1.0.0.0 VALOR ABSOLUTO

Simbolo:

abs

Descripcin:

abs es un operador unitario, es decir que slo requiere un operando, y est definido

para cualquier tipo numrico (Entero, real o tiempo) El resultado es del mismo tipo

pero siempre es positivo.

1.0.0 OPERADORES RELACIONALES

Siempre que sea necesario comparar dos objetos se deben utilizar los operadores

relacionales. Ellos cubren todos los tipos de comparaciones:

Igual =

Diferente / =

Menor que <

Menor que o igual a<=

mayor que >

Mayor que o igual a >=

Los objetos comparados deben ser del mismo tipo y pueden ser: Boolean, bit,

character, integer, real, time, string o bit_vector. Sin embargo, el resultado siempre es

booleano.

Cuando se comparan dos vectores no es necesario que sean de la misma longitud. Al

operando de menor longitud se le adicionan ceros hasta que queden del mismo

tamao y ambos se justifican a la izquierda.

1.0.0 OPERADORES DE CORRIMIENTO

Como su nombre lo indica estos operadores realizan operaciones de corrimiento

sobre arreglos de una dimensin. Estos operadores estn restringidos a los arreglos

cuyos elementos sean de tipo bit o boolean.

Los operadores de corrimiento requieren dos operandos. El izquierdo representa un

arreglo y el de la derecha es un entero que indica el nmero de posiciones que debe

correrse el arreglo. Si el signo del operador de la derecha es negativo el corrimiento se

realizar en sentido contrario al indicado.

Los operadores de corrimiento son los siguientes:

1.0.0 OPERADOR DE CONCATENACIN

La concatenacin es una forma muy conveniente para crear nuevos valores de arreglos

de cualquier tipo. Esta operacin est definida para arreglos de una dimensin.

La concatenacin une dos operandos usando el operador &. El resultado es un arreglo

cuya longitud es la suma de las longitudes de los operadores.

Ejemplo:

CAI & N --Da como resultado CAIN

1.0.0 ATRIBUTOS

Un atributo es una caracterstica que se puede asociar a cualquier elemento de un

modelo VHDL como puede ser un tipo de datos, un objeto, una entidad o un

procedimiento. No se de be confundir el atributo de un objeto con su valor, ya que en

un momento dado cada objeto tiene un nico valor mientras que puede tener muchos

atributos asociados. La sintaxis para un atributo es la siguiente:

identificador_elementoidentificador_atributo

1.0.0.0 ATRIBUTOS DE RANGOS DE VECTORES

Aleft(n) Valor izquierdo del ndice de A

Aright(n) Valor derecho del ndice de A

Alow(n) Valor mnimo del ndice de A

Ahigh(n) Valor mximo del ndice de A

Aascending(n) Verdadero si el rango del ndice n de A es ascendente

Arange(n) Rango del ndice n de A

Areverse_range(n) Rango del ndice n de A invertido

Alength(n) Nmero de valores del rango n de A

1.0.0.0 ATRIBUTOS DE TIPOS DE DATOS

Tbase Tipo base de T

Tleft Valor ms a la izquierda de T

Tright Valor ms a la derecha de T

Tlow Valor mnimo de T

Thigh Valor mximo de T

Tascending Verdadero si T tiene rango ascendente

Timage(x) Representacin textual del valor x de tipo T

Tvalue(x) Valor expresado por la cadena de caracteres

Tpos(x) Posicin ocupada por x en T

Tval(x) Valor de la posicin x en T

Tsucc(x) Valor de la posicin siguiente a x en T

Tpred(x) Valor de la posicin anterior a x en T

Tleftof(x) Valor de la posicin derecha a x en T

Trightof(x) Valor de la posicin izquierda a x en T

1.0.0.0 ATRIBUTOS DE SEALES

1.0.0.0 ATRIBUTOS DEFINIDOS POR EL USUARIO

Adems de los atributos predefinidos, VHDL permite definir atributos que se pueden

asociar a cualquier elemento. La sintaxis para la declaracin de atributos es la siguiente:

attribute identificador : tipo_datos;

Y la sintaxis para la especificacin del atributo es

attribute identificador of id_elemento : clase_elemento is expresin;

El identificador determina el elemento especfico al que se le aplica el atributo, y la

clase determina su naturaleza (Por ejemplo, indica si se trata de una seal, un

procedimiento o una entidad).

La sintaxis para utilizar un atributo definido por el usuario es la siguiente:

Identificador_elementoidentificador_atributo

Ejemplo:

signal Reloj : std_logic;

attribute NumeroPin : natural;

attribute NumeroPin of Reloj : signal i s 5;

1.0.0 ASIGNACIN DE EXPRESIONES A SEALES

El objetivo principal de todo sistema electrnico es generar una respuesta determinada

ante una entrada especfica. Eventualmente, los resultados de las operaciones deben

ser asignados a las salidas. El mecanismo de asignacin es muy simple: La seal

destino aparece a la izquierda seguida por el smbolo <= y finalmente la expresin a

asignar. El resultado de la expresin ser pasado a la seal destino. Para recordar

mejor la asignacin, la flecha determina el flujo de informacin.

Ejemplos:

X <=Y <=Z; --Esta expresin asigna el valor de la comparacin (Y <= Z) a

la seal booleana X.

A <=B or C; --Esta expresin asigna el valor de la operacin lgica B or C a

la seal A.

K <=1; --Este tipo de asignacin se realiza para los tipos bit o

character unicamente

M <=01010 --Este tipo de asignacin se aplica a arreglos.

1.0.0.0 REATARDO EN LAS ASIGNACIONES

Nada ocurre instantneamente en el mundo real, Los eventos en un sistema ocurren

despus de un determinado tiempo. Este comportamiento se modela en VHDL con la

clusula after que puede incluirse en cualquier expresin de asignacin.

La clusula after especifica la cantidad de tiempo que hay que esperar para realizar la

asignacin.

Cuando la respuesta de un sistema es retardada, puede surgir una pregunta interesante:

Hasta que velocidad de cambio de la entrada, puede responder la salida?. La respuesta

es: no importa. Si un LED es encendido y apagado en un intervalo de tiempo muy

corto, el LED no cambiar de estado y permanecer apagado. Este comportamiento

del LED es llamado inercia y en VHDL se modela con el retardoinercial (inertial delay).

La clusula after asume automticamente el retardo inercial. El comportamiento

caracterstico de este modelo es que dos cambios subsecuentes de la entrada se

ignorarn si la diferencia de tiempo entre ellos es menor que el retardo inercial. Este es

un punto muy importante ya que todo sistema electrnico responde a una

determinada velocidad, si no se tuviera en cuenta este comportamiento todas las

especificaciones podran funcionar a una frecuencia infinita y como sabemos esto

fsicamente no es posible.

Retardo de transporte:

El retardo inercial es el retardo electrnico ms comn, pero no el nico.

Consideremos por ejemplo una lnea de transmisin que transporta pulsos. A

diferencia de una compuerta un lnea de transmisin puede propagar cualquier tipo de

pulso sin importar su duracin, pero se debe tener en cuenta el tiempo que la seal

necesita para viajar a travs de ella.

Retardo inercial vs Retardo de transporte.

Estos dos retardos son suficientes para describir cualquier sistema fsico en VHDL.

Las principales diferencias entre ellos son las siguientes:

El retardo inercial esta por defecto en las descripciones de VHDL y no necesita

declaraciones adicionales, Mientras que si se desea utilizar un retardo de

transporte se debe utilizar la clusula transport.

El retardo inercial no ve a los pulsos que tengan una duracin menor que el

retardo especificado. Los retardos de transporte propagan todas las seales sin

importar su duracin.

Los retardos inerciales y de transporte se especifican utilizando la clusula after,

seguido por el valor del retardo.

Ambos modelos de retardo pueden aplicarse a seales de cualquier tipo.

1.0.0 DECLARACIN DE CONSTANTES

Las constantes juegan un papel similar a los genricos: ellas soportan informacin

esttica que puede ser utilizada dentro del modelo. Sin embargo, a diferencia de los

genricos que se declaran en las entidades, las constantes son declaradas en las

arquitecturas.

Para declarar una constante se necesitan los siguientes elementos:

La clusula constant.

El nombre de la constante

Dos puntos

Tipo de constante.

Valor de la constante despus del smbolo :=

Un punto y coma finalizando la expresin.

constant identifier_list : subtype_indication [ := expression ] ;

Si existen dos o ms constantes del mismo tipo y tienen el mismo valor pueden

declararse al mismo tiempo.

Las constantes se utilizan para trabajar con nombres legibles dentro del cdigo,

adems se puede realizar cualquier cambio rpidamente ya que al cambiar el valor

asignado a una constante, se cambian automticamente todos los sitios en los que se

utiliza.

Las constantes se utilizan de la misma forma que los genricos, especficamente para:

Especificar el tamao de objetos complejos (arreglos, buses).

Control de ciclos.

Definicin de parmetros de timing: Delays, setup times, hold times, switching times,

etc.

1.0.0 CONSTANTES VS GENRICOS

La principal diferencia entre los genricos y las constantes es que los primeros se

utilizan dinmicamente mientras que las constantes son estticas. Esto significa que se

puede cambiar el valor de un genrico sin cambiar el cdigo. Sin embargo, las

constantes no pueden cambiarse sin modificar el cdigo. Esto es importante

especialmente en el caso de utilizar el cdigo como componente de una especificacin

de alto nivel. Cada vez que se utilice dicho componente, se le pueden asignar nuevos

valores si ellos estn especificados por genricos.

Los cambios realizados en los genricos afectan a las arquitecturas que los utilizan,

mientras que el cambio en una constante slo afecta la arquitectura en la que es

declarada.

1.0 DESCRIPCION DE LA ARQUITECTURA

Qu significa el comportamiento del sistema?. El principal propsito de cualquier

sistema o dispositivo electrnico es transformar los datos de entrada a resultados en

las salidas. Este tipo de actividad se conoce como comportamiento o funcionalidad

del sistema y la especificacin del sistema describe la transformacin de los datos de

entrada a resultados en las salidas.

La descripcin de una arquitectura se compone de un conjunto de sentencias

concurrentes que se ejecutan de forma asncrona entre s y se comunican mediante

seales.

1.0.0 PROCESOS

Un proceso es una sentencia concurrente; En el interior de un proceso las sentencias

se ejecutan en orden secuencial, marcado por las sentencias de control de flujo de

programa tpicas de un lenguaje imperativo. La ejecucin se hace en tiempo cero.

Un proceso puede estar activo o en suspenso. Ya que el VHDL representa sistemas

reales se debe dar una explicacin adicional sobre el concepto terminacin del proceso.

Consideremos la operacin de un sistema tpico: Se debe ejecutar un proceso y

despus detenerse para siempre? o Se deben repetir el proceso en un lazo infinito?.

La segunda opcin es ms cercana a la realidad. El proceso asegura que despus de

ejecutar la ltima operacin inmediatamente se inicia la ejecucin de la primera y

como resultado de esto un proceso nunca termina.

La sintaxis para la declaracin de un proceso es la siguiente:

En donde las variables A y B se conocen con el nombre de lista de sensibilidad, una

vez que el proceso ejecuta la ltima sentencia, este entra en un estado de suspensin,

hasta que suceda un evento (cambio de seal) en alguna de las variables de la lista de

sensibilidad.

Los dispositivos electrnicos normalmente operan en un ciclo infinito una vez

activados, ellos ejecutan sus operaciones y una vez las han finalizado entran en un

estado de espera, y reanudan su operacin hasta que se presenten las condiciones

especficas de su activacin.

Estas condiciones de activacin en VHDL son descritas por la clusula wait. Y se

utiliza para los siguientes propsitos:

Paradas incondicionales, suspencin de la ejecucin de un proceso.

Lista las condiciones para reanudar un proceso.

Ya que en la prctica existen diferentes formas de activar un proceso. VHDL

proporciona tres formas de utilizar la clusula while:

1. Esperar a que se cumpla en tiempo: Suspende la ejecucin de un proceso por un

determinado perodo de tiempo. El tiempo puede especificarse explcitamente o como

una expresin.

Ejemplo:

wait for 10 ns;

wait for frecuancia/2;

2. Esperar a que se cumpla una condicin booleana: Suspende la ejecucin de un

proceso hasta que una determinada expresin booleana se torne verdadera.

Ejemplo:

wait until CLK = 1;

waint until RST and (LOAD or CLK);

3. Esperar a que una determinada seal cambie de valor: Suspende el proceso hasta

que se detecta un evento en cualquiera de las seales listadas, es decir, el proceso se

reanuda hasta que alguna seal de la lista de sensibilidad cambia

Ejemplo:

wait on CLK;

wait on LOAD, RST;

Adems de estas condiciones se puede hacer una combinacin de ellas para obtener