Tda 7313

Diunggah oleh

ClaudiuMaxmiucHak Cipta

Format Tersedia

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniHak Cipta:

Format Tersedia

Tda 7313

Diunggah oleh

ClaudiuMaxmiucHak Cipta:

Format Tersedia

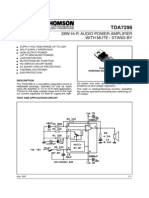

TDA7313

DIGITAL CONTROLLED STEREO AUDIO PROCESSOR

WITH LOUDNESS

INPUT MULTIPLEXER:

- 3 STEREOINPUTS

- SELECTABLEINPUT GAINFOR OPTIMAL

ADAPTIONTO DIFFERENT SOURCES

INPUT AND OUTPUT FOR EXTERNAL

EQUALIZER OR NOISE REDUCTION SYS-

TEM

LOUDNESS FUNCTION

VOLUMECONTROL IN 1.25dB STEPS

TREBLEAND BASSCONTROL

FOURSPEAKERATTENUATORS:

- 4 INDEPENDENT SPEAKERSCONTROL

IN1.25dB STEPS FOR BALANCEAND

FADERFACILITIES

- INDEPENDENT MUTE FUNCTION

ALL FUNCTIONS PROGRAMMABLE VIA SE-

RIAL I

2

C BUS

DESCRIPTION

The TDA7313 is a volume, tone (bass and treble)

balance (Left/Right) and fader (front/rear) processor

for quality audio applications in car radio and Hi-Fi

systems.

Selectable input gain and external loudness function

are provided. Control is accomplished by serial I

2

C

busmicroprocessor interface.

TheACsignal settingis obtainedby resistor networks

andswitches combinedwith operationalamplifiers.

Thanks to the used BIPOLAR/CMOS Tecnology,

LowDistortion, LowNoise and LowDCstepping are

obtained.

November 1999

DIP28 SO28

ORDERING NUMBERS:

TDA7313 TDA7313D

PIN CONNECTION (Topview)

1/14

THERMAL DATA

Symbol Description SO28 DIP28 Unit

R

th j-pins

Thermal Resistance Junction-pins max 85 65 C/W

QUICK REFERENCE DATA

Symbol Parameter Min. Typ. Max. Unit

V

S

Supply Voltage 6 9 10 V

V

CL

Max. input signal handling 2 Vrms

THD Total Harmonic Distortion V = 1Vrms f = 1KHz 0.01 0.1 %

S/N Signal to Noise Ratio 106 dB

S

C

Channel Separation f = 1KHz 103 dB

Volume Control 1.25dB step -78.75 0 dB

Bass and Treble Control 2db step -14 +14 dB

Fader and Balance Control 1.25dB step -38.75 0 dB

Input Gain 3.75dB step 0 11.25 dB

Mute Attenuation 100 dB

ABSOLUTE MAXIMUM RATINGS

Symbol Parameter Value Unit

V

S

Operating Supply Voltage 10.2 V

T

amb

Operating Ambient Temperature -40 to 85 C

T

stg

Storage Temperature Range -55 to +150 C

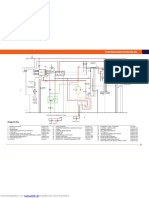

TEST CIRCUIT

TDA7313

2/14

L

1

1

5

L

1

L

2

1

4

L

2

L

3

1

3

L

3

I

N

P

U

T

S

E

L

E

C

T

O

R

+

G

A

I

N

C

1

C

2

C

3

L

E

F

T

I

N

P

U

T

S

3

x

2

.

2

F

S

U

P

P

L

Y

R

3

9

R

3

R

2

1

0

R

2

R

1

1

1

R

1

C

4

C

5

C

6

3

x

2

.

2

F

R

I

G

H

T

I

N

P

U

T

S

2

3

1

V

C

C

A

G

N

D

C

R

E

F

C

9

2

.

2

F

O

U

T

(

L

)

I

N

(

L

)

1

7

1

6

V

O

L

+

L

O

U

D

L

O

U

D

(

L

)

1

2

1

0

0

n

F

C

1

4

B

A

S

S

1

9

5

.

6

K

R

2

B

O

U

T

(

L

)

1

8

B

I

N

(

L

)

1

0

0

n

F

C

1

5

R

B

T

R

E

B

L

E

C

1

7

2

.

7

n

F

T

R

E

B

L

E

(

L

)

4

M

U

T

E

D

9

4

A

U

1

8

0

S

E

R

I

A

L

B

U

S

D

E

C

O

D

E

R

+

L

A

T

C

H

E

S

S

P

K

R

A

T

T

2

5

V

O

L

+

L

O

U

D

B

A

S

S

T

R

E

B

L

E

O

U

T

(

R

)

I

N

(

R

)

C

8

2

.

2

F

7

6

1

0

0

n

F

C

1

2

1

0

0

n

F

C

1

3

5

.

6

K

R

1

B

O

U

T

(

R

)

B

I

N

(

R

)

2

1

2

0

R

B

2

.

7

n

F

C

1

6

T

R

E

B

L

E

(

R

)

M

U

T

E

S

P

K

R

A

T

T

2

8

2

7

2

6

2

2

S

C

L

S

D

A

D

I

G

G

N

D

B

U

S

O

U

T

R

I

G

H

T

R

E

A

R

O

U

T

L

E

F

T

F

R

O

N

T

5

2

2

F

C

7

8

L

O

U

D

(

R

)

C

1

1

1

0

0

n

F

1

0

0

n

F

C

1

0

M

U

T

E

S

P

K

R

A

T

T

O

U

T

L

E

F

T

R

E

A

R

2

3

M

U

T

E

S

P

K

R

A

T

T

O

U

T

R

I

G

H

T

F

R

O

N

T

2

4

BLOCK DIAGRAM

TDA7313

3/14

ELECTRICAL CHARACTERISTICS (refer to the test circuit Tamb = 25C, VS = 9V, RL = 10K,

RG = 600, all controls flat (G = 0), f = 1KHz unless otherwise specified)

Symbol Parameter Test Condition Min. Typ. Max. Unit

SUPPLY

V

S

Supply Voltage 6 9 10 V

IS Supply Current 8 11 mA

SVR Ripple Rejection 60 80 dB

INPUT SELECTORS

R

II

Input Resistance Input 1, 2, 3 35 50 70 K

V

CL

Clipping Level 2 2.5 Vrms

SIN Input Separation (2) 80 100 dB

R

L

Output Load resistance pin 7, 17 2 K

G

INmin

Min. Input Gain -1 0 1 dB

G

INmax

Max. Input Gain 11.25 dB

G

STEP

Step Resolution 3.75 dB

e

IN

Input Noise G = 11.25dB 2 V

V

DC

DC Steps adjacent gain steps 4 20 mV

G = 18.75 to Mute 4 mV

VOLUMECONTROL

R

IV

Input Resistance 20 33 50 k

C

RANGE

Control Range 70 75 80 dB

A

VMIN

Min. Attenuation -1 0 1 dB

AVMAX Max. Attenuation 70 75 80 dB

A

STEP

Step Resolution 0.5 1.25 1.75 dB

E

A

Attenuation Set Error Av = 0 to -20dB

Av = -20 to -60dB

-1.25

-3

0 1.25

2

dB

dB

E

T

Tracking Error 2 dB

V

DC

DC Steps adjacent attenuation steps

From 0dB to Av max

0

0.5

3

7.5

mV

mV

SPEAKERATTENUATORS

C

range

Control Range 35 37.5 40 dB

S

STEP

Step Resolution 0.5 1.25 1.75 dB

E

A

Attenuation set error 1.5 dB

A

MUTE

Output Mute Attenuation 80 100 dB

VDC DC Steps adjacent att. steps

from 0 to mute

0

1

3

10

mV

mV

BASS CONTROL (1)

Gb Control Range Max. Boost/cut +12 +14 +16 dB

B

STEP

Step Resolution 1 2 3 dB

RB Internal Feedback Resistance 34 44 58 K

TREBLE CONTROL (1)

Gt Control Range Max. Boost/cut +13 +14 +15 dB

T

STEP

Step Resolution 1 2 3 dB

TDA7313

4/14

ELECTRICAL CHARACTERISTICS (continued)

Symbol Parameter Test Condition Min. Typ. Max. Unit

AUDIO OUTPUTS

V

OCL

Clipping Level d = 0.3% 2 2.5 Vrms

R

L

Output Load Resistance 2 K

C

L

Output Load Capacitance 10 nF

R

OUT

Output resistance 30 75 120

V

OUT

DC Voltage Level 4.2 4.5 4.8 V

GENERAL

e

NO

Output Noise BW = 20-20KHz, flat

output muted

all gains = 0dB

2.5

5 15

V

V

A curve all gains = 0dB 3 V

S/N Signal to Noise Ratio all gains = 0dB; VO = 1Vrms 106 dB

d Distortion A

V

= 0, V

IN

= 1Vrms

A

V

= -20dB V

IN

= 1Vrms

V

IN

= 0.3Vrms

0.01

0.09

0.04

0.1

0.3

%

%

%

Sc Channel Separation left/right 80 103 dB

Total Tracking error A

V

= 0 to -20dB

-20 to -60 dB

0

0

1

2

dB

dB

BUS INPUTS

V

IL

Input Low Voltage 1 V

V

IH

Input High Voltage 3 V

I

IN

Input Current -5 +5 A

V

O

Output Voltage SDA

Acknowledge

I

O

= 1.6mA 0.4 V

Notes:

(1) Bass and Trebleresponse see attached diagram(fig.16). The center frequency and quality of the resonance behaviour can be choosen by

the external circuitry. A standard first order bass response can be realized by a standard feedback network

(2) The selected input is groundedthru the 2.2F capacitor.

Figure 2: Loudnessvs. Frequency (CLOUD =

100nF) vs. Volume Attenuation

Figure 1: Loudness vs. Volume Attenuation

TDA7313

5/14

Figure 6: Distortion & Noise vs. Frequency

Figure 7: Distortion & Noise vs. Frequency

Figure 8: Distortion vs. Load Resistance

Figure 4: Noise vs. Volume/Gain Settings

Figure 5: Signal to Noise Ratio vs. Volume

Setting

Figure 3: Loudness vs. External Capacitors

TDA7313

6/14

Figure 12: Output Clipping Level vs. Supply

Voltage

Figure 14: Supply Current vs. Temperature Figure 13: Quiescent Current vs. Supply Voltage

Figure 10: Input Separation(L1 L2, L3, L4) vs.

Frequency

Figure 9: Channel Separation(L R) vs.

Frequency

Figure 11: Supply Voltage Rejection vs.

Frequency

TDA7313

7/14

I

2

C BUS INTERFACE

Data transmission from microprocessor to the

TDA7313 and viceversa takes place thru the 2

wires I

2

C BUS interface, consisting of the two

lines SDA and SCL (pull-up resistors to positive

supply voltage must be connected).

Data Validity

As shown in fig. 17, the data on the SDA line

must be stable during the high period of the clock.

The HIGH and LOW state of the data line can

only change when the clock signal on the SCL

line is LOW.

Start and Stop Conditions

As shown in fig.18 a start condition is a HIGH to

LOW transition of the SDA line while SCL is

HIGH. The stop condition is a LOW to HIGH tran-

sition of the SDA line while SCL is HIGH.

Byte Format

Every byte transferred on the SDA line must con-

tain 8 bits. Each byte must be followed by an ac-

knowledge bit. The MSB is transferred first.

Acknowledge

The master (P) puts a resistive HIGH level on the

SDA line during the acknowledge clock pulse (see

fig. 19). The peripheral (audioprocessor) that ac-

knowledges has to pull-down (LOW) the SDA line

during the acknowledge clock pulse, so that the

SDAline is stable LOWduringthis clock pulse.

The audioprocessor which has been addressed

has to generate an acknowledge after the recep-

tion of each byte, otherwise the SDA line remains

at the HIGH level during the ninth clock pulse

time. In this case the master transmitter can gen-

erate the STOP information in order to abort the

transfer.

Transmissionwithout Acknowledge

Avoiding to detect the acknowledge of the audio-

processor, the P can use a simplier transmis-

sion: simply it waits one clock without checking

the slave acknowledging, and sends the new

data.

This approach of course is less protected from

misworking and decreases the noise immunity.

Figure 17: Data Validity on the I

2

CBUS

Figure 16: Typical Tone Response (with the ext.

components indicated in the test

circuit)

Figure 15: Bass Resistance vs. Temperature

TDA7313

8/14

SOFTWARE SPECIFICATION

Interface Protocol

The interface protocol comprises:

A start condition (s)

A chip address byte, containing the TDA7313

address (the 8th bit of the byte must be 0). The

TDA7313 must always acknowledge at the end

of each transmitted byte.

A sequenceof data (N-bytes + acknowledge)

A stop condition (P)

TDA7313 ADDRESS

MSB first byte LSB MSB LSB MSB LSB

S 1 0 0 0 1 0 0 0 ACK DATA ACK DATA ACK P

Data Transferred (N-bytes + Acknowledge)

ACK = Acknowledge

S = Start

P = Stop

MAX CLOCK SPEED100kbits/s

SOFTWARE SPECIFICATION

Chip address

1

MSB

0 0 0 1 0 0 0

LSB

DATA BYTES

MSB LSB FUNCTION

0

1

1

1

1

0

0

0

0

1

1

0

0

1

1

1

B2

0

1

0

1

0

1

1

B1

B1

B1

B1

B1

G1

0

1

B0

B0

B0

B0

B0

G0

C3

C3

A2

A2

A2

A2

A2

S2

C2

C2

A1

A1

A1

A1

A1

S1

C1

C1

A0

A0

A0

A0

A0

S0

C0

C0

Volume control

Speaker ATT LR

Speaker ATT RR

Speaker ATT LF

Speaker ATT RF

Audio switch

Bass control

Treble control

Ax = 1.25dB steps; Bx = 10dB steps; Cx = 2dB steps; Gx = 3.75dB steps

Figure 18: Timing Diagramof I

2

CBUS

Figure 19: Acknowledgeon the I

2

CBUS

TDA7313

9/14

SOFTWARE SPECIFICATION (continued)

DATA BYTES(detailed description)

Volume

MSB LSB FUNCTION

0 0 B2 B1 B0 A2 A1 A0 Volume 1.25dB steps

0

0

0

0

1

1

1

1

0

0

1

1

0

0

1

1

0

1

0

1

0

1

0

1

0

-1.25

-2.5

-3.75

-5

-6.25

-7.5

-8.75

0 0 B2 B1 B0 A2 A1 A0 Volume 10dB steps

0

0

0

0

1

1

1

1

0

0

1

1

0

0

1

1

0

1

0

1

0

1

0

1

0

-10

-20

-30

-40

-50

-60

-70

For example a volume of -45dBis given by:

0 0 1 0 0 1 0 0

Speaker Attenuators

MSB LSB FUNCTION

1

1

1

1

0

0

1

1

0

1

0

1

B1

B1

B1

B1

B0

B0

B0

B0

A2

A2

A2

A2

A1

A1

A1

A1

A0

A0

A0

A0

Speaker LF

Speaker RF

Speaker LR

Speaker RR

0

0

0

0

1

1

1

1

0

0

1

1

0

0

1

1

0

1

0

1

0

1

0

1

0

-1.25

-2.5

-3.75

-5

-6.25

-7.5

-8.75

0

0

1

1

0

1

0

1

0

-10

-20

-30

1 1 1 1 1 Mute

For example attenuationof 25dB on speaker RF is given by:

1 0 1 1 0 1 0 0

TDA7313

10/14

Audio Switch

MSB LSB FUNCTION

0 1 0 G1 G0 S2 S1 S0 Audio Switch

0

1

0

0

1

1

0

1

0

1

Stereo 1

Stereo 2

Stereo 3

Stereo 4 (*)

LOUDNESS ON

LOUDNESS OFF

0

0

1

1

0

1

0

1

+11.25dB

+7.5dB

+3.75dB

0dB

For example to select the stereo 2 input with a gain of +7.5dBLOUDNESS ON the 8bit string is:

0 1 0 0 1 0 0 1

(*) Stereo 4 is connected internally, but not available on pins.

Bass andTreble

0

0

1

1

1

1

0

1

C3

C3

C2

C2

C1

C1

C0

C0

Bass

Treble

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

0

0

0

0

1

1

1

1

1

1

1

1

0

0

0

0

0

0

1

1

0

0

1

1

1

1

0

0

1

1

0

0

0

1

0

1

0

1

0

1

1

0

1

0

1

0

1

0

-14

-12

-10

-8

-6

-4

-2

0

0

2

4

6

8

10

12

14

C3 = Sign

For example Bass at -10dBis obtained by the following 8 bit string:

0 1 1 0 0 0 1 0

Purchase of I

2

C Components of STMicroelectronics, conveys a license under the Philips I

2

C Patent

Rights to use these components in an I

2

C system, provided that the system conforms to the I

2

C

Standard Specifications as defined by Philips.

TDA7313

11/14

SO28

DIM.

mm inch

MIN. TYP. MAX. MIN. TYP. MAX.

A 2.65 0.104

a1 0.1 0.3 0.004 0.012

b 0.35 0.49 0.014 0.019

b1 0.23 0.32 0.009 0.013

C 0.5 0.020

c1 45 (typ.)

D 17.7 18.1 0.697 0.713

E 10 10.65 0.394 0.419

e 1.27 0.050

e3 16.51 0.65

F 7.4 7.6 0.291 0.299

L 0.4 1.27 0.016 0.050

S 8 (max.)

OUTLINE AND

MECHANICAL DATA

TDA7313

12/14

DIM.

mm inch

MIN. TYP. MAX. MIN. TYP. MAX.

a1 0.63 0.025

b 0.45 0.018

b1 0.23 0.31 0.009 0.012

b2 1.27 0.050

D 37.34 1.470

E 15.2 16.68 0.598 0.657

e 2.54 0.100

e3 33.02 1.300

F 14.1 0.555

I 4.445 0.175

L 3.3 0.130

DIP28

OUTLINE AND

MECHANICAL DATA

TDA7313

13/14

Information furnished i s believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences

of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is

granted by implication or otherwise under any patent or patent rights of STMicroelectroni cs. Specification mentioned in this publication are

subject to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products

are not authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics.

The ST l ogo is a registeredtrademark of STMicroelectronics

1999 STMicroelectronics Printed in Italy All Rights Reserved

STMicroelectronics GROUP OF COMPANIES

Australia - Brazil - China - Finland - France - Germany - Hong Kong - India - Italy- Japan - Malaysia - Malta - Morocco -

Singapore - Spain - Sweden - Switzerland - United Kingdom - U.S.A.

http://www.st.com

TDA7313

14/14

Anda mungkin juga menyukai

- Nano SP SP+ - Maintenance and Fault FindingDokumen38 halamanNano SP SP+ - Maintenance and Fault FindingClaudiuMaxmiuc100% (1)

- Ad7730 7730LDokumen52 halamanAd7730 7730LDa Q ShaBelum ada peringkat

- TDA7440D: Tone Control Digitally Controlled Audio ProcessorDokumen17 halamanTDA7440D: Tone Control Digitally Controlled Audio ProcessorJimmy R. Calderon GualeBelum ada peringkat

- Tda 7439Dokumen17 halamanTda 7439Arwana ChipmunksBelum ada peringkat

- Tda 7438Dokumen18 halamanTda 7438sontuyet82Belum ada peringkat

- Tda 7440Dokumen17 halamanTda 7440Albert ThomasBelum ada peringkat

- Tda 7313Dokumen15 halamanTda 7313jordachadiBelum ada peringkat

- Tda 7313Dokumen14 halamanTda 7313Ariel NavarreteBelum ada peringkat

- TDA7442Dokumen16 halamanTDA7442gaston30-3@Belum ada peringkat

- Tda7317 EcualizadorDokumen13 halamanTda7317 EcualizadorRafael AlcazarBelum ada peringkat

- TDA7442 TDA7442D: Tone Control and Surround Digitally Controlled Audio ProcessorDokumen17 halamanTDA7442 TDA7442D: Tone Control and Surround Digitally Controlled Audio ProcessormochuraBelum ada peringkat

- 4-Ch Output Stereo Audio Processor With 4 Stereo Inputs and Tone/Volume ControlDokumen13 halaman4-Ch Output Stereo Audio Processor With 4 Stereo Inputs and Tone/Volume ControlRaúl García LópezBelum ada peringkat

- Hoja de Datos Del TDA 7439Dokumen20 halamanHoja de Datos Del TDA 7439_el_patriarca_Belum ada peringkat

- Tda 7449Dokumen18 halamanTda 7449Ariel NavarreteBelum ada peringkat

- Tda 7340GDokumen27 halamanTda 7340GAndrei PetriciBelum ada peringkat

- Tda 7442Dokumen17 halamanTda 7442Ariel NavarreteBelum ada peringkat

- Tda 7468DDokumen22 halamanTda 7468DJohn Keneth Vasquez100% (1)

- Tda 7339Dokumen12 halamanTda 7339Giovanni Carrillo VillegasBelum ada peringkat

- 3 V To 5 V Single Supply, 200 KSPS 8-Channel, 12-Bit Sampling ADC AD7858/AD7858LDokumen36 halaman3 V To 5 V Single Supply, 200 KSPS 8-Channel, 12-Bit Sampling ADC AD7858/AD7858Ljnax101Belum ada peringkat

- Datasheet AN5829S - Sound Multiplex Decoder IC For The U.S. Televisions - Panasonic SemiconductorDokumen17 halamanDatasheet AN5829S - Sound Multiplex Decoder IC For The U.S. Televisions - Panasonic Semiconductorfernandog251186Belum ada peringkat

- That1510p PDFDokumen6 halamanThat1510p PDFJefferson Gutama ValladaresBelum ada peringkat

- Ta 0104 ADokumen18 halamanTa 0104 AJump DownBelum ada peringkat

- Tda 7318Dokumen14 halamanTda 7318Ariel NavarreteBelum ada peringkat

- Integrado An5829sDokumen20 halamanIntegrado An5829sangelr203619219Belum ada peringkat

- An7316 Idjo3Dokumen5 halamanAn7316 Idjo3Andy Luis Morales GuerraBelum ada peringkat

- 60 W Hi-Fi Dual Audio Driver: DescriptionDokumen12 halaman60 W Hi-Fi Dual Audio Driver: DescriptionLenin BabuBelum ada peringkat

- Njw1197a eDokumen15 halamanNjw1197a eSava Beljan-SavijaBelum ada peringkat

- 3 V To 5 V Single Supply, 200 KSPS 8-Channel, 12-Bit Sampling ADC AD7858/AD7858LDokumen32 halaman3 V To 5 V Single Supply, 200 KSPS 8-Channel, 12-Bit Sampling ADC AD7858/AD7858LJodelCamarinBelum ada peringkat

- LM1894 Dynamic Noise Reduction System DNR: General DescriptionDokumen10 halamanLM1894 Dynamic Noise Reduction System DNR: General DescriptionKoszegi AttilaBelum ada peringkat

- Lm6172 Op Amp DobleDokumen19 halamanLm6172 Op Amp DobleGREKO_ONEBelum ada peringkat

- SR510 MDokumen73 halamanSR510 McampuspointBelum ada peringkat

- ssm2165 B PDFDokumen12 halamanssm2165 B PDFenzo_60Belum ada peringkat

- Tda 7250Dokumen11 halamanTda 7250Mazariegôs JJBelum ada peringkat

- Tda 7250Dokumen12 halamanTda 7250killer_jj100% (1)

- WM9701A Low Power AC'97 Multimedia Audio Codec: Description FeaturesDokumen0 halamanWM9701A Low Power AC'97 Multimedia Audio Codec: Description FeaturesJorBS57Belum ada peringkat

- Datasheet 2Dokumen10 halamanDatasheet 2miguel angel jaramilloBelum ada peringkat

- VIF/SIF/Y/C/Deflection Implemented in A Single Chip: For NTSC Color Television SetsDokumen35 halamanVIF/SIF/Y/C/Deflection Implemented in A Single Chip: For NTSC Color Television SetsLeonel MartinezBelum ada peringkat

- LV1035MDokumen3 halamanLV1035Msudhakar.mrBelum ada peringkat

- Microstepping DMOS Driver With Translator: Description Features and BenefitsDokumen18 halamanMicrostepping DMOS Driver With Translator: Description Features and BenefitsSaid BoubkerBelum ada peringkat

- LM4811 Dual 105mW Headphone Amplifier With Digital Volume Control and Shutdown ModeDokumen20 halamanLM4811 Dual 105mW Headphone Amplifier With Digital Volume Control and Shutdown ModeBuga BuniciBelum ada peringkat

- AD8319Dokumen20 halamanAD8319agmnm1962Belum ada peringkat

- Programmable Quad Bipolar Operational Amplifier: LM146 LM246 LM346Dokumen6 halamanProgrammable Quad Bipolar Operational Amplifier: LM146 LM246 LM346Alejandro Borrego DominguezBelum ada peringkat

- Features Descriptio: Ltc1566-1 Low Noise 2.3Mhz Continuous Time Lowpass FilterDokumen8 halamanFeatures Descriptio: Ltc1566-1 Low Noise 2.3Mhz Continuous Time Lowpass Filtergiapy0000Belum ada peringkat

- THAT 4301 DatasheetDokumen12 halamanTHAT 4301 DatasheetSaverioCorBelum ada peringkat

- DatasheetDokumen10 halamanDatasheetJose SalgueroBelum ada peringkat

- 28W Hi-Fi Audio Power Amplifier With Mute / Stand-By: DescriptionDokumen11 halaman28W Hi-Fi Audio Power Amplifier With Mute / Stand-By: DescriptionbaczonifBelum ada peringkat

- Ssm2120 2 ExpanderDokumen12 halamanSsm2120 2 ExpandershirtquittersBelum ada peringkat

- Tda 7497Dokumen8 halamanTda 7497Madein ChinaBelum ada peringkat

- Opa 134 DatasheetDokumen19 halamanOpa 134 DatasheetNikos SpirouBelum ada peringkat

- Datasheet TDA2052Dokumen14 halamanDatasheet TDA2052FrancoilBelum ada peringkat

- La 1140Dokumen15 halamanLa 1140Mariano KokoBelum ada peringkat

- TLO74CNDokumen12 halamanTLO74CNEverson CorreaBelum ada peringkat

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Dari EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Belum ada peringkat

- Audio IC Projects: A Collection of Useful Circuits Based on Readily Available ChipsDari EverandAudio IC Projects: A Collection of Useful Circuits Based on Readily Available ChipsBelum ada peringkat

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Dari EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Penilaian: 2.5 dari 5 bintang2.5/5 (3)

- Wire and Cable Markers: Self-Laminating Labels, Manual MarkingDokumen1 halamanWire and Cable Markers: Self-Laminating Labels, Manual MarkingClaudiuMaxmiucBelum ada peringkat

- Operating and Maintenance Manual: (Serial No. 17774216D Onwards)Dokumen28 halamanOperating and Maintenance Manual: (Serial No. 17774216D Onwards)ClaudiuMaxmiucBelum ada peringkat

- DAM-E3039F User's Manual H (V6.13)Dokumen18 halamanDAM-E3039F User's Manual H (V6.13)ClaudiuMaxmiucBelum ada peringkat

- Elektrischer Schaltplan: Manualslib - deDokumen1 halamanElektrischer Schaltplan: Manualslib - deClaudiuMaxmiucBelum ada peringkat

- Exploded Diagram: The SystemDokumen15 halamanExploded Diagram: The SystemClaudiuMaxmiucBelum ada peringkat

- Process Indicators: Programmable Process Indicator TC67UDokumen1 halamanProcess Indicators: Programmable Process Indicator TC67UClaudiuMaxmiucBelum ada peringkat

- Cbls Datasheet PDFDokumen2 halamanCbls Datasheet PDFClaudiuMaxmiucBelum ada peringkat

- Ax MS PDFDokumen2 halamanAx MS PDFClaudiuMaxmiucBelum ada peringkat

- Axor CD180 PDFDokumen10 halamanAxor CD180 PDFClaudiuMaxmiucBelum ada peringkat

- Utc Ta7343apDokumen5 halamanUtc Ta7343apClaudiuMaxmiucBelum ada peringkat

- EST3 To EST4 Forward Migration SINGLEDokumen1 halamanEST3 To EST4 Forward Migration SINGLEDhaval ChitaraBelum ada peringkat

- Whirlpool Awo D 53105 Service PDFDokumen29 halamanWhirlpool Awo D 53105 Service PDFbogdan80Belum ada peringkat

- PC 670Dokumen195 halamanPC 670Ian DorringtonBelum ada peringkat

- Introduction With The WiMAX Equipments AlvarionDokumen38 halamanIntroduction With The WiMAX Equipments AlvarionSubir Chandra Mazumdar50% (2)

- Input and Output DevicesDokumen6 halamanInput and Output DevicesLakshmiRengarajanBelum ada peringkat

- MIMO PresentationDokumen15 halamanMIMO PresentationAnonymous OPfgsRdpt9Belum ada peringkat

- Question Paper JEDokumen11 halamanQuestion Paper JECSE SWRBelum ada peringkat

- Omnidirectional AntennaDokumen11 halamanOmnidirectional AntennaAnonymous gUjimJKBelum ada peringkat

- 579-183 (24 Point IO Card Installation Guide)Dokumen28 halaman579-183 (24 Point IO Card Installation Guide)ishaqBelum ada peringkat

- Silicon Chip-1995 09Dokumen108 halamanSilicon Chip-1995 09Jorge AgarieBelum ada peringkat

- Engine Control PDFDokumen53 halamanEngine Control PDFRamon CasillasBelum ada peringkat

- B Side: N7Tw - Power.Pcb 1LG4B10Y04300Dokumen2 halamanB Side: N7Tw - Power.Pcb 1LG4B10Y04300Dario EzequielBelum ada peringkat

- ASUS Z97-ADokumen6 halamanASUS Z97-ASAMUEL CENTENOBelum ada peringkat

- Emerson Vs APCDokumen6 halamanEmerson Vs APCsfekhan1978Belum ada peringkat

- CAN Doku EMR2 Engl PDFDokumen28 halamanCAN Doku EMR2 Engl PDFAnonymous RcxX0FcBelum ada peringkat

- PrecommissioningSwitchgear GeneralDokumen2 halamanPrecommissioningSwitchgear Generalhari banggaBelum ada peringkat

- 03 - Lecture - Performance AnalysisDokumen26 halaman03 - Lecture - Performance AnalysisAhmedBelum ada peringkat

- VNA Hfst3 CapacitorDokumen8 halamanVNA Hfst3 CapacitorAhmedBelum ada peringkat

- CBLM Set Up Welding Equipment NC 2 OCT. 2022Dokumen43 halamanCBLM Set Up Welding Equipment NC 2 OCT. 2022Mark KimhitaBelum ada peringkat

- 062N PDFDokumen7 halaman062N PDFhectorsevillaBelum ada peringkat

- Interview Questions & Answers: Ans: 101 ASCII Value of "A" Is 1000001, Which When Converted Into Octal Gives 101Dokumen16 halamanInterview Questions & Answers: Ans: 101 ASCII Value of "A" Is 1000001, Which When Converted Into Octal Gives 101Shakeel ScetBelum ada peringkat

- Eeprom 29c040Dokumen13 halamanEeprom 29c040api-3710567Belum ada peringkat

- Wicomm T QPSKDokumen13 halamanWicomm T QPSKvithyaBelum ada peringkat

- Diagrama Electrico 777GDokumen27 halamanDiagrama Electrico 777GSamuel Tirado Canihuante100% (1)

- 13 02 01 03C UTC Product-Catalog Ventilclima ENDokumen30 halaman13 02 01 03C UTC Product-Catalog Ventilclima ENDaniel MartinsBelum ada peringkat

- 12 Volt 12.0 Amp. HRS.: Rechargeable Sealed Lead-Acid BatteryDokumen2 halaman12 Volt 12.0 Amp. HRS.: Rechargeable Sealed Lead-Acid BatteryJuan EsBelum ada peringkat

- ARGtek ARG-1210 QIGDokumen18 halamanARGtek ARG-1210 QIGPriyo SanyotoBelum ada peringkat

- 1 General Information: Nettime Timestamp of The Position and Trigger TimeDokumen51 halaman1 General Information: Nettime Timestamp of The Position and Trigger TimeСтив АааBelum ada peringkat

- Fulltext01 4Dokumen83 halamanFulltext01 4survivalofthepolyBelum ada peringkat

- YT-2500 Smart PositionerDokumen43 halamanYT-2500 Smart Positionermsalem73Belum ada peringkat