5KVA Inverter Boost H-Bridge

Diunggah oleh

Thèm KhátDeskripsi Asli:

Hak Cipta

Format Tersedia

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniHak Cipta:

Format Tersedia

5KVA Inverter Boost H-Bridge

Diunggah oleh

Thèm KhátHak Cipta:

Format Tersedia

Bajopas Vol.

2 Number 1 June, 2009

6

Bayero J ournal of Pure and Applied Sciences, 2(1): 6 - 13

Received: November, 2008

Accepted: February, 2009

5KVA POWER INVERTER DESIGN AND SIMULATION BASED ON BOOST

CONVERTER AND H-BRIDGE INVERTER TOPOLOGY

*Musa, A. and G.S.M. Galadanci

Department of Physics, Bayero University, PMB 3011, Kano

*Correspondence author

ABSTRACT

Five (5) kVA power inverter was designed and simulated base on two topologies; Boost converter

and Half-bridge inverter topology. A 555 timer I C was used as the control at fixed frequencies of 25

kHz and 50 Hz for the two stages. The results of the simulation were obtained. The graphs for both

stages were plotted and the results show a significant increase in the voltage and duty cycle. The

wave form of the output gives a square wave form.

Keywords: Power inverter, Simulation, Topology, Converter

I NTRODUCTION

The World demand for electrical energy is constantly

increasing and conventional energy resources are

diminishing and even threatened to be depleted. With

the increasing popularity of alternative power sources,

such as solar and wind, the need for static inverters to

convert dc energy stored in batteries to conventional

ac form has increased substantially. This conversion

can either be achieved by transistors or by SCRs

(silicon controlled rectifiers). For lower and medium

power outputs, transistorised inverters are suitable but

for high power outputs, SCRs should be used.

Transistor inverters are useful in wide variety of

applications. They provide power to the complicated

electronic systems of orbiting satellites and cool

astronaut suits

(http;//Guru/PEInverters/introduction/pdf/inv.pdf,

2006).

However, MOSFETs (Metal Oxide

Semiconductor Field Effect Transistor) and IGBTs

(Insulated Gate Bipolar Transistor) are good

candidates for the switches in dc to ac conventional

techniques. With the development electronic devices

and circuits, newer equipment often have converters

that allow the user to change the voltage and

frequency applied to the equipment .Power electronics

also provides the industries with effective methods to

save energy and improve performance (Sen, 2002).

Power electronic devices can be divided in to

two categories: Single component and hybrid

component. The single component is composed of one

solid-state device, and hybrid component is a

combination of several single components

manufactured as a single block. The single devices are

loosely divided into three type :(1) the two layer

devices such as diode , (2) the three layer devices

such as transistor , and (3) the four layer devices such

as the Thyristor . The hybrid components include

wider range of devices such as the Insulated Gate

Bipolar Transistor (IGBT), Static Insulated Transistor

(SIT), and Darlington Transistor (DT). Solid state

devices are main building components of any

converter. Their function is mainly to mimic the

mechanical switches by connecting and disconnecting

electrical loads, but at very high speed. When the

mechanical switch is open (off), the current through

the switch is zero and the voltage across its terminal is

equal to the source voltage. When the switch is closed

(on), its terminal voltage is zero and its current is

determined by load impedance (Mukund, 2006).

Design Stage for fly Boost Converter and Power

Inverter

Boost converter design

Based on the dc-dc converter topology; Boost

converter circuit design is shown with duty cycle (D),

output input gain with pulse width modulation to drive

the converter at 25 kHz shown in Figure 1.0

Figure 1.0: Boost converter schematic diagram

PWM &

V

i

Bajopas Vol. 2 Number 1 June, 2009

7

The output to the input voltage gain of the inverter is given by (Simon and Oliva, 2005).

2.0

and 2.1

where , is the duty cycle of switching converter that is

2.2

where switched off time for the transistor

switched on time for the transistor and

which is define by the following relation

2.3 a

or 2.3 b

However, with 555-timer ICs an inexpensive regulated SMPS is constructed, feedback and pulse width

modulation were shown in Figure 2.0. If the desired inverter frequency and the voltage are known, the power

consumed by the switching on and off of the converter can be estimated by the following equation

(http://supertex.com/pdf/app.note/AN-36.pdf, 2008).

2.4

GND

DI S

OUT RST

VCC

THR

CON

TRI

2

0

0

3

5

0

6

7

Fig. 2 DC-DC Converter

0

1

0

Battery

Cin

CT

RD

RC

RFB

555

ZFB

L

Qsw

D

Cout

0

4

Vout

Determine operating frequency, Duty cycle, and I nductor

Neglecting switch resistance, inductor losses, and other parasitic, the relationship between these

parameters can be approximated by the following

2.5

Selection of a converter frequency is very important,

since many applications require certain frequencies for

EMI reasons. Higher switching frequencies allow the

use of smaller inductors but lead to high switching

losses. Conversely, lower frequencies can reduce

switching losses but require large inductors. Converter

in the range of 20 kHz-100 kHz are generally suitable.

Duty cycle is calculated as follows.

2.6

The equation above yield duty cycles greater than 100%. For the inductor rating, peak inductor current can be

approximated using the following equation

2.7

Select Q

sw

and D

For switching transistor Q

sw

, the most important

parameters are break down voltage, on resistance,

peak current, and power dissipation. For the diode,

the important parameters are reverse break down

voltage, peak repetitive current, and average forward

current and reverse recovery time. Since peak inductor

current also flows through the switch and the diode, it

may be used to rate these components as well.

2.8

Maximum average current will occur at minimum input voltage

2.9

Figure 2.0 DC-DC Boost converter

Bajopas Vol. 2 Number 1 June, 2009

8

Average power dissipation in the switch can be estimated from the following equation.

3.0

Where R

sw

= switch on resistance

Select C

in

and C

out

Input capacitance C

in

functions as an input bypass

capacitor to reduce the effective source impedance

and also EMI by restricting high frequency current

paths to short loops.. For the best performance C

in

impedance should be less than 1.

3.1

Where

Output capacitance C

out

stores high voltage energy

and also reduces EMI by restricting high frequency

current paths to stop short loops. The value of C

out

must largely dependent on the desired ripple voltage

on V

out

. Generally, ripple (as a fraction of output

voltage) of about 10% is adequate.

3.2

Where I

out

= output current to the inverter,

Ripple = and , both C

in

and C

out

should be high frequency

types

Select Timing Components ,

Timing components , determine

nominal converter frequency and maximum duty cycle.

Selection of these components is an iterative process.

The ratio sets the maximum possible duty

cycle, while , together determine

nominal output frequency. Maximum duty cycle can

also be calculated using the following equation.

3.3

The ratio must be greater than for proper operation of the 555 timer. If less, timing capacitor

voltage will be unable to discharge to and output of the 555 will remain low. Nominal converter

frequency can be calculated using the following equation.

3.4

Select Feedback components

Output voltage is determine by the zener voltage plus an amount of bias voltage needed to vary duty cycle of

the timing

3.5

The amount bias will vary depending on load and input voltage. The extreme limits of bias voltage are given in

equations 3.6 and 3.7.

3.6

3.7

and

If is too low, it will prevent timing capacitor voltage from rising to as required for nominal

operation of the 555, resulting in switch staying on and the current rising to destructive levels. To prevent

this from occurring, the ratio of must always be greater than two.

3.8

Bajopas Vol. 2 Number 1 June, 2009

9

Power Inverter stage design

However, in this part H-bridge inverter topology was

adopted. The half bridge inverter in the simplest form

is shown is Figure 3.0 H-bridge inverter topology has

lower number of switches and simple

control.(http://Guru/PEInverter/Half-

bridge/pdf/inv.pdf, 2006). The duration of the dead

band should be large enough to allow the switch that

is turned off to close before the other switch, to start

conducting. The advantage of H-bridge inverter

topology has lower number of switches and simple

control (Emadi and Stoyan, 1992). The differential

equation for the current from 0 = t

to 2 T t =

governing the current and voltage flows of half-bridge

inverter may be written as

( )

( )

s

V t Ri

dt

t di

L = + 3.9

Its general solution is of the form

( )

t s

Ae

R

V

t i

+ = 4.0

Where , the time constant for R-L load, is

R

L

= , Applying the initial condition, that is

( )

max min

0 I I i = = when 0 = t , we get

max

I

R

Vs

A = .

Hence, the expression for the current in the circuit during 0 = t and 2 T t = is

( ) ( )

t t

e I e

R

Vs

t i

=

max

1 4.1

The current attains its maximum value at 2 T t = and is obtained from (4.1) as

( )

2

max

2

max

1

T

e I e

R

V

I

T s

=

Rearranging the term we get

2

2

max

1

1

T

T

e

e

R

Vs

I 4.2

Hence the current in the circuit during 0 = t and 2 T t = is

( ) ( )

t

T

T

s t s

e

e

e

R

V

e

R

V

t i

=

2

2

1

1

1 4.3

Figure 3.0 (i) Half-bridge inverter with dual supply, and (ii) single supply

MATERI ALS AND METHODS

Two methods were employed for the inverter designed

and simulation; the computer simulation with NI

Multisim 10. Software and the circuit analysis using

the above equations. The design topology which was

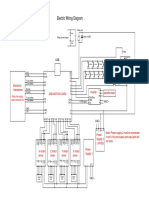

adopted is shown in Fig.4 with two stages; boost

converter and half-bridge inverter, and their controls.

Bajopas Vol. 2 Number 1 June, 2009

10

Figure 4.0 DC-AC Inverter circuit design

RESULTS:

Based on the simulation and the equations above the results were plotted using origin 50 with the following

graphs:

0.0 0.2 0.4 0.6 0.8 1.0

0

2

4

6

8

10

Buck Converter

Boost Converter

Buck-Boost Converter

V

out

/V

in

Duty cycle(%)

Figure 5.0 Graph of commonly converters compared analytically with equation 2.0 which shows the boost

converter has high gain.

0.88 0.89 0.90 0.91 0.92 0.93 0.94

8

10

12

14

16

18

Boost Converter

V

out

/V

in

Duty Cycle

Figure 6.0 Graph of the gain to the duty cycle from the simulation result

1 2 3 4 5 6 7 8 9 10

0.0

0.2

0.4

0.6

0.8

1.0

B

D

(

d

u

t

y

c

y

c

le

)

R

C

/R

D

ratio

Figure 7.0 Graph of maximum duty cycle with ratio of timing resistors

Feedbac

DC-DC (Boost

Converter

Control

(555-timer IC)

DC-AC (H-Bridge

l )

Control

(555-timer IC)

1

st

Stage 2

nd

Stage

Bajopas Vol. 2 Number 1 June, 2009

11

However, the nominal converter frequency was

chosen to be 25 kHz which gave an inductor of 500H

and inductor peak current I

L(pk)

using equations (2.6)

and (2.7) with design power level of 700mW.

Maximum duty is 70% at 6.0volt correspond to R

C

/R

D

ratio of 3.4 with equation 10; the R

C

value was 40.5k

which indicated R

D

is 11.9k. For maximum regulation,

R

FB

should be greater than 81.0k since R

C

was

40.5k then R

FB

is slightly greater than 81.0k which

approximately 90.0k

0 20 40 60 80 100 120 140 160 180

0

10

20

30

40

50

60

70

R

C

/R

D

=3

R

C

/R

D

=4

R

C

/R

D

=5

R

C

/R

D

=6

R

C

/R

D

=7

R

C

/R

D

=8

R

C

/R

D

=9

R

C

/R

D

=10

F

r

e

q

e

n

c

y

(

k

H

z

)

R

C

kohms

Figure 8.0 Graph of nominal Converter frequency for C

T

= 1nF

2 3 4 5 6

20

40

60

80

100

120

140

160

180

200

R

C

/R

D

=3

R

C

/R

D

=4

R

C

/R

D

=5

R

C

/R

D

=6

R

C

/R

D

=7

R

C

/R

D

=8

R

C

/R

D

=9

R

C

/R

D

=10

V

B

IA

S

(

v

o

l

t

)

R

FB

/R

C

Figure 9.0 Graph of Bias voltages plot from equation (3.7)

However, for maximum regulation R

FB

are slightly greater than two as equation (3.8). Since R

C

is 41.0k

than R

FB

must be greater than 82 k but 90.0 k was selected.

Figure 10.0 Converter output voltage from the simulation

Figure 11.0 Output wave form for the two AND-gate

Bajopas Vol. 2 Number 1 June, 2009

12

Figure 12.0 Inverter output voltage from the simulation

Table 1.0 Requirement for Comparison

12k

90k

41k

7uF

GND

DI S

OUT RST

VCC

THR

CON

TRI

500uH

2

0

0

3

5

1nF

0

6

7

02BZ2.2

VN10LF

4.7uF

Fig. 2 DC-DC Converter

0

1

6-12v Cin

CT

RD

RC

RFB

555

ZFB

L

Qsw

D

Cout

Vout BAV21

XSC1

A B

Ext Trig

+

+

_

_ + _

0

0

8

U1

LM555CM

GND

1

DI S 7

OUT 3 RST 4

VCC

8

THR 6

CON 5

TRI 2

R1

24k

C2

330nF

R2

10k

R3

42k

Key=A

50%

1

0 0

U3A

74HC113D_4V

1J 3

~1Q 6

1CLK 1

1K 2

1Q 5

~1PR

4

U4

3554AM

6

5

7

2

1

2

R4

10k

R5

100k

Key=A

50%

6

7

0

0

5

8

U2A

7408N U2C

7408N

10

11

9

U5A

MCT6

2

1

8

7

U5B

MCT6

4

3

5

6

R6

7k

R7

7k

3

12

0

13

14

0

XSC1

A B

Ext Trig

+

+

_

_ + _

15

16

17

18

0

0

T1

TS_POWER_25_TO_1

12k

90k

41k

7uF

GND

DI S

OUT RST

VCC

THR

CON

TRI

500uH

1nF

02BZ2.2

VN10LF

4.7uF

6-12v Cin

CT

RD

RC

RFB

555

ZFB

L

Qsw

D

Cout

Vout BAV21

0

22

0

27

26

0

25

24

0

0

23

0

20

4

Q3

IRFP250

Q2

IRFP250

XMM1

U7

LM7812CT

LI NE VREG

COMMON

VOLTAGE

0

28

21 19

S/ no. Parameter Required Achieved

1 V

out

(converter) 48.0 V 100V

2 V

out

(inverter) 220V 220V

3 P

out

(converter) 700mW 0.15W

4 P

out

(inverter) 5kVA 2.09kVA

5 Converter wave form Modulated Modulated

6 Inverter wave form Modified Sine wave Square wave with

distortion

7 I

out

(inverter) 22.7 A 9.53A

8 I

Lpk

330mA 185.32mA

9 Inverter Freq. 50Hz 48.6Hz

10 Converter Freq. 25kHz 24.6kHz

Figure 14. DC-DC/DC-AC power Inverter stage

TS25T1 power

Transformer

Figure. 13 DC-DC converter stages with the nominal calculated values

Bajopas Vol. 2 Number 1 June, 2009

13

SUMMARY, DI SCUSSI ON AND CONCLUSI ON

The selection of the above topology simulated and

worked with the nominal calculated values. It also

shows that from table 1.0 the frequencies for both

converter and inverter were close to the required

values together with the wave forms.

In conclusion, the circuits when simulated

performed much better than the expected result due

to calculation assumptions and approximations. It

shows that the duty cycle of the converter change

completely as seen from the Fig. 6 when compared

with general topologies in Fig.5. It is also shown from

Fig. 11 output voltage high than expected.

REFERENCES

http://Guru/PEInverters/introduction/pdf/inv.pdf 24th

February, 2006

PC Sen. (2002), Power Electronics. Tata McGraw-Hill

publishing company limited, New Delhi, India,

726p

Mukund R. Patel (2006). Wind and Solar Power

System: Design, Analysis, and Operation (2

nd

edition). CRC press, Taylor & Francis, U.S.A

221-224pp

Simon ANG and Alejandro Oliva (2005). Power

Switching Converters, (2

nd

edition) CRC

press, Taylor & Francis, 32-38pp

http://supertex.com/pdf/app-note/AN-36.pdf 23th

January, 2008.

http://Guru/PEInverte rs/Half-bridge/pdf/inv.pdf

24th February, 2006

Ali Emadi Abdolhosein Nasiri and Stoyan B Bekiarou

(1992). Uninterruptable Power Supplies& Active

Filter.53p

Anda mungkin juga menyukai

- 19MO504-IE 2 MarksDokumen40 halaman19MO504-IE 2 MarksSaranya. M SNSBelum ada peringkat

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Dari EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Belum ada peringkat

- DC Transformers 77Dokumen15 halamanDC Transformers 77Keshavamurthy MurthyBelum ada peringkat

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Dari EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Penilaian: 2.5 dari 5 bintang2.5/5 (3)

- Buck Converter Design DemystifiedDokumen6 halamanBuck Converter Design DemystifiedEric MorissetBelum ada peringkat

- Influence of System Parameters Using Fuse Protection of Regenerative DC DrivesDari EverandInfluence of System Parameters Using Fuse Protection of Regenerative DC DrivesBelum ada peringkat

- 689-Article Text-2322-1-10-20160621Dokumen7 halaman689-Article Text-2322-1-10-20160621AfifNasirBelum ada peringkat

- Single PhasingDokumen41 halamanSingle PhasingdiljithBelum ada peringkat

- Introduction to Power System ProtectionDari EverandIntroduction to Power System ProtectionPenilaian: 5 dari 5 bintang5/5 (1)

- Lesson 8 Hard and Soft Switching of Power SemiconductorsDokumen12 halamanLesson 8 Hard and Soft Switching of Power SemiconductorsChacko MathewBelum ada peringkat

- Practical Switching Power Supply DesignDari EverandPractical Switching Power Supply DesignPenilaian: 2 dari 5 bintang2/5 (1)

- Analysis of Buck Converter and Simulating It For Different Switching Frequencies and Different Power DevicesDokumen6 halamanAnalysis of Buck Converter and Simulating It For Different Switching Frequencies and Different Power DevicesPrema Vinod PatilBelum ada peringkat

- 200 - EE8552, EE6503 Power Electronics - Question Bank 3Dokumen119 halaman200 - EE8552, EE6503 Power Electronics - Question Bank 3NiteshNarukaBelum ada peringkat

- Power Supply Projects: A Collection of Innovative and Practical Design ProjectsDari EverandPower Supply Projects: A Collection of Innovative and Practical Design ProjectsPenilaian: 3 dari 5 bintang3/5 (2)

- Project ReportDokumen8 halamanProject Reportسید کاظمی100% (1)

- Soft Switched High Step-Up DC-DC Converter For Automotive ApplicationDokumen4 halamanSoft Switched High Step-Up DC-DC Converter For Automotive Applicationkarthi.r.tBelum ada peringkat

- Implementation of Full-Bridge Current-Fed Resonant Boost Converter Using PIC MicrocontrollerDokumen6 halamanImplementation of Full-Bridge Current-Fed Resonant Boost Converter Using PIC MicrocontrollerAlonso CoradoBelum ada peringkat

- Boost ConvertersDokumen4 halamanBoost ConvertersSyed Mohammad FarooqueBelum ada peringkat

- 20977-Article Text-63774-1-10-20180626Dokumen8 halaman20977-Article Text-63774-1-10-20180626gürcan EserBelum ada peringkat

- Resonant Converter Power Supply For Arc Welding ApplicationDokumen5 halamanResonant Converter Power Supply For Arc Welding Applicationshado2010Belum ada peringkat

- ReportDokumen15 halamanReportGavaine MattisonBelum ada peringkat

- Boost Detailed Design PDFDokumen22 halamanBoost Detailed Design PDFshivaBelum ada peringkat

- EE6503-Power ElectronicsDokumen41 halamanEE6503-Power Electronicscwizard60Belum ada peringkat

- High-Power Density Design of A Soft-Switching High-Power Bidirectional DC-DC ConverterDokumen9 halamanHigh-Power Density Design of A Soft-Switching High-Power Bidirectional DC-DC Convertermurthy237Belum ada peringkat

- Power Electronics Lab Simulation Project ReportDokumen5 halamanPower Electronics Lab Simulation Project ReportMaha RaufBelum ada peringkat

- EE51POWER ELECTORNICS EzDokumen20 halamanEE51POWER ELECTORNICS EzAnonymous m8oCtJBBelum ada peringkat

- 1000w Inverter PURE SINE WAVE Schematic DiagramDokumen153 halaman1000w Inverter PURE SINE WAVE Schematic Diagramjeevapillay100% (4)

- Switched Mode Power SupplyDokumen153 halamanSwitched Mode Power SupplyIvan222244Belum ada peringkat

- Two-Level and Three-Level Converter Comparison in Wind Power ApplicationDokumen11 halamanTwo-Level and Three-Level Converter Comparison in Wind Power ApplicationIkram RidhoBelum ada peringkat

- Pulse Density ModulationDokumen4 halamanPulse Density ModulationrhusheinBelum ada peringkat

- Design and Implementation of ZCS BUCK CONVERTERDokumen51 halamanDesign and Implementation of ZCS BUCK CONVERTERAriful Haque100% (1)

- PLC Based Load Sharing On Slide ShareDokumen28 halamanPLC Based Load Sharing On Slide ShareHemu Bhai PatelBelum ada peringkat

- 2 Marks and 3 MarksDokumen14 halaman2 Marks and 3 Marksnani2012Belum ada peringkat

- 고전압비와 낮은 전압 스트레스를 가진 단일 스위치와 전압 체배 회로를 이용한 새로운 비절연형 DC-DC 컨버터Dokumen5 halaman고전압비와 낮은 전압 스트레스를 가진 단일 스위치와 전압 체배 회로를 이용한 새로운 비절연형 DC-DC 컨버터Armandinho CaveroBelum ada peringkat

- WMCDokumen65 halamanWMCbhagathnagarBelum ada peringkat

- DC To Ac Converter by Using 555 Timer ICDokumen6 halamanDC To Ac Converter by Using 555 Timer ICAlfred Adukobirre AdukobillaBelum ada peringkat

- Fast Charger 2Dokumen10 halamanFast Charger 2gcarliBelum ada peringkat

- Design and Implementation of Multiple Output Switch Mode Power SupplyDokumen6 halamanDesign and Implementation of Multiple Output Switch Mode Power SupplyseventhsensegroupBelum ada peringkat

- Design of A Low-Dropout Linear RegulatorDokumen4 halamanDesign of A Low-Dropout Linear RegulatorParindraBelum ada peringkat

- A Novel ZCS-PWM Flyback Converter With A Simple ZCS-PWM Commutation CellDokumen9 halamanA Novel ZCS-PWM Flyback Converter With A Simple ZCS-PWM Commutation CellSHIVIKA BISARIABelum ada peringkat

- Performance of A Current-Fed Soft Switched Full-Bridge Boost Double Stage Converter Using ZVS PWMDokumen8 halamanPerformance of A Current-Fed Soft Switched Full-Bridge Boost Double Stage Converter Using ZVS PWMiajerBelum ada peringkat

- Design and Analysis of A Transformer-Less Single-Phase Grid-Tie Photovoltaic Inverter Using Boost Converter With Immittance Conversion TopologyDokumen8 halamanDesign and Analysis of A Transformer-Less Single-Phase Grid-Tie Photovoltaic Inverter Using Boost Converter With Immittance Conversion Topologyangel monroyBelum ada peringkat

- Making Inverter Welder - IRFDokumen18 halamanMaking Inverter Welder - IRFShaun Dwyer Van Heerden0% (1)

- Design and Simulation of Triggering Circ PDFDokumen4 halamanDesign and Simulation of Triggering Circ PDFYimy GarciaBelum ada peringkat

- Self-Oscillating Resonant AC/DC Converter Topology For Input Power-Factor CorrectionDokumen11 halamanSelf-Oscillating Resonant AC/DC Converter Topology For Input Power-Factor CorrectionJie99Belum ada peringkat

- Unit I: The Controlling Parameter Is Gate-Emitter VoltageDokumen10 halamanUnit I: The Controlling Parameter Is Gate-Emitter VoltageRaj TilakBelum ada peringkat

- Single Phase AC To AC Conversion Without Frequency RestrictionsDokumen4 halamanSingle Phase AC To AC Conversion Without Frequency RestrictionsTaniyaBelum ada peringkat

- Simulation and Prototype Implementation of Phase Shift Full Bridge DC DC ConverterDokumen4 halamanSimulation and Prototype Implementation of Phase Shift Full Bridge DC DC ConverterjimmyBelum ada peringkat

- LV DESGIN FOR TRAINING Manual FinalDokumen8 halamanLV DESGIN FOR TRAINING Manual FinalBehailu MulugetaBelum ada peringkat

- Power-Electronics Ktuonline - in PDFDokumen68 halamanPower-Electronics Ktuonline - in PDFchippyviswanBelum ada peringkat

- Zeta Converter PDFDokumen7 halamanZeta Converter PDFSreeram PanigrahiBelum ada peringkat

- Switched Inductor Z-Source Matrix Converter Operation and AnalysisDokumen9 halamanSwitched Inductor Z-Source Matrix Converter Operation and AnalysisA'Platinum EngBelum ada peringkat

- Speedam 2008 FINAL Mag IntDokumen9 halamanSpeedam 2008 FINAL Mag IntbiswajitntpcBelum ada peringkat

- Ulta Stepup DC To DC Conveter With Reduced Switch StressDokumen21 halamanUlta Stepup DC To DC Conveter With Reduced Switch StressDRISHYABelum ada peringkat

- M Group: EE1301-Power ElectronicsDokumen14 halamanM Group: EE1301-Power Electronicsscribdm100% (5)

- Ac Link Buck Boost ConverterDokumen6 halamanAc Link Buck Boost ConverterrigowBelum ada peringkat

- Buck RegulatorDokumen6 halamanBuck RegulatorBhukya Reethvik RathodBelum ada peringkat

- Tube Packaging: Verpackt in StangenprofilDokumen1 halamanTube Packaging: Verpackt in StangenprofilThèm KhátBelum ada peringkat

- Frequency Offset and Symbol Timing Recovery inDokumen12 halamanFrequency Offset and Symbol Timing Recovery inThèm KhátBelum ada peringkat

- Without Interlocking: 12-PoligDokumen1 halamanWithout Interlocking: 12-PoligThèm KhátBelum ada peringkat

- Wire Guide 12-Contacts: 1,27 DRC Drahtführung 12-PolDokumen1 halamanWire Guide 12-Contacts: 1,27 DRC Drahtführung 12-PolThèm KhátBelum ada peringkat

- Application Book: Telecommunications Applications With The Tms320C5X DspsDokumen317 halamanApplication Book: Telecommunications Applications With The Tms320C5X DspsyjmagicBelum ada peringkat

- Ieee Isie 2015 ChoqueuseDokumen6 halamanIeee Isie 2015 ChoqueuseThèm KhátBelum ada peringkat

- Patel - Spacecraft Power SystemsDokumen734 halamanPatel - Spacecraft Power SystemsThèm Khát100% (1)

- I: What It Is, What It Isn't, and How To Use It: by Chris GlaserDokumen7 halamanI: What It Is, What It Isn't, and How To Use It: by Chris Glaserychig1232669Belum ada peringkat

- Tracking and Kalman Filtering Made EasyDokumen480 halamanTracking and Kalman Filtering Made EasyKiran Ali100% (5)

- TEXTBOOK-Introduction To Random Signals and Applied Kalman Filtering With MatlabDokumen248 halamanTEXTBOOK-Introduction To Random Signals and Applied Kalman Filtering With MatlabCường Sống Thiện0% (1)

- DS PANDA48Cell-24b 40mm EU EN B&B 201309 v02.40Dokumen2 halamanDS PANDA48Cell-24b 40mm EU EN B&B 201309 v02.40Thèm KhátBelum ada peringkat

- Lap Trinh FPGADokumen31 halamanLap Trinh FPGAThèm KhátBelum ada peringkat

- Power Inverter Hard Ware DesignDokumen39 halamanPower Inverter Hard Ware Designapi-369580189% (9)

- Opj 2013071916290665Dokumen5 halamanOpj 2013071916290665Thèm KhátBelum ada peringkat

- Thesis BergveldDokumen328 halamanThesis Bergveldcdevelop10Belum ada peringkat

- Thunder Click WebDokumen2 halamanThunder Click WebThèm Khát100% (2)

- Telecom Data QueryDokumen21 halamanTelecom Data QueryHassan Mody TotaBelum ada peringkat

- Fuzzy Logic Based Control of Variable Wind Energy System: Trisha Bora Prateekee Chatterjee Saradindu GhoshDokumen5 halamanFuzzy Logic Based Control of Variable Wind Energy System: Trisha Bora Prateekee Chatterjee Saradindu GhoshIam AnonymousBelum ada peringkat

- Power Supply 17IPS19-5 Philips VES2.2E LA PDFDokumen4 halamanPower Supply 17IPS19-5 Philips VES2.2E LA PDFJejeBelum ada peringkat

- Physics Investigatory ProjectDokumen11 halamanPhysics Investigatory ProjectNo BodyBelum ada peringkat

- Exp 2Dokumen4 halamanExp 2Mustafa MhmoodBelum ada peringkat

- Nitech - CT's PDFDokumen3 halamanNitech - CT's PDFJesse WilliamsBelum ada peringkat

- Analysis of Cascaded H-Bridge Multilevel Inverter With Phase Shifted PWM On Induction MotorDokumen12 halamanAnalysis of Cascaded H-Bridge Multilevel Inverter With Phase Shifted PWM On Induction MotoremyimranBelum ada peringkat

- ST Products and Solutions For Solar Energy PDFDokumen33 halamanST Products and Solutions For Solar Energy PDFrfm61Belum ada peringkat

- Three Phase Controlled RectifiersDokumen111 halamanThree Phase Controlled RectifiersDeepthiBelum ada peringkat

- للDokumen4 halamanللerfan roshandelBelum ada peringkat

- Lecture 3Dokumen65 halamanLecture 3Rami ZakoutBelum ada peringkat

- Bidirectional Battery Charger Circuit Using BuckBoost ConverterDokumen6 halamanBidirectional Battery Charger Circuit Using BuckBoost ConverterRakesh SandarativjuBelum ada peringkat

- Theory of Switched Mode Power SupplyDokumen21 halamanTheory of Switched Mode Power Supplyseahate100% (1)

- We en Web in Ar Sic Mosfet 1638931895460Dokumen29 halamanWe en Web in Ar Sic Mosfet 1638931895460Алексей ЯмаBelum ada peringkat

- Chapter1-3 - Three Phase TransformerDokumen29 halamanChapter1-3 - Three Phase TransformerPraveen Nayak BhukyaBelum ada peringkat

- Manual UPS BORRI PDFDokumen218 halamanManual UPS BORRI PDFzzofoneaka100% (6)

- Omega Pet 429Dokumen1 halamanOmega Pet 429urjashah3Belum ada peringkat

- Voltage Across The PN JunctionDokumen2 halamanVoltage Across The PN JunctionEmil RudzainiBelum ada peringkat

- Design of State Feedback Controller For Positive Output Elementary Super-Lift DC-DC Luo Converter ForDokumen18 halamanDesign of State Feedback Controller For Positive Output Elementary Super-Lift DC-DC Luo Converter ForGabriel AlvesBelum ada peringkat

- Electric Wiring Diagram PDFDokumen1 halamanElectric Wiring Diagram PDFWilliams Ayala100% (2)

- LCL Filter DesignDokumen11 halamanLCL Filter DesignQawl TayebBelum ada peringkat

- BTech EE SchemeDokumen3 halamanBTech EE SchemeNikhil SinghBelum ada peringkat

- 62nd ECTC Advance ProgramDokumen32 halaman62nd ECTC Advance Programmuh9904Belum ada peringkat

- Mounting Instr ATV71Dokumen108 halamanMounting Instr ATV71leonardo proBelum ada peringkat

- Low Cost Digital Signal Generation For Driving Space Vector PWM InverterDokumen12 halamanLow Cost Digital Signal Generation For Driving Space Vector PWM InverterJunaid AhmadBelum ada peringkat

- Multilevel Inverter Topologies - 12th May BIKRAM DASDokumen50 halamanMultilevel Inverter Topologies - 12th May BIKRAM DASprasad2303Belum ada peringkat

- 1 Half-Wave Rectifier With R LoadDokumen18 halaman1 Half-Wave Rectifier With R LoadKARMUGHILLAAN MANIMARAN STUDENTBelum ada peringkat

- P2110 DatasheetDokumen12 halamanP2110 DatasheetR Bonifacio DaitanBelum ada peringkat

- A Wireless Power Transfer System With Inverse Coupled Current Doubler Rectifier For High-Output Current ApplicationsDokumen10 halamanA Wireless Power Transfer System With Inverse Coupled Current Doubler Rectifier For High-Output Current Applicationsmeenujataj469481Belum ada peringkat

- MOSFET Power Losses Calculation Using The Data-Sheet ParametersDokumen23 halamanMOSFET Power Losses Calculation Using The Data-Sheet ParametersElvis Yu0% (1)

- INCOSE Systems Engineering Handbook: A Guide for System Life Cycle Processes and ActivitiesDari EverandINCOSE Systems Engineering Handbook: A Guide for System Life Cycle Processes and ActivitiesPenilaian: 5 dari 5 bintang5/5 (1)

- Electronics All-in-One For Dummies, 3rd EditionDari EverandElectronics All-in-One For Dummies, 3rd EditionPenilaian: 5 dari 5 bintang5/5 (2)

- Digital Filmmaking: The Ultimate Guide to Web Video Production for Beginners and Non-Professionals, Learn Useful Tips and Advice on How You Can Create, Film and Edit Your VideosDari EverandDigital Filmmaking: The Ultimate Guide to Web Video Production for Beginners and Non-Professionals, Learn Useful Tips and Advice on How You Can Create, Film and Edit Your VideosPenilaian: 5 dari 5 bintang5/5 (1)

- Hacking Electronics: An Illustrated DIY Guide for Makers and HobbyistsDari EverandHacking Electronics: An Illustrated DIY Guide for Makers and HobbyistsPenilaian: 3.5 dari 5 bintang3.5/5 (2)

- Practical Electrical Wiring: Residential, Farm, Commercial, and IndustrialDari EverandPractical Electrical Wiring: Residential, Farm, Commercial, and IndustrialPenilaian: 3.5 dari 5 bintang3.5/5 (3)

- Analog Design and Simulation Using OrCAD Capture and PSpiceDari EverandAnalog Design and Simulation Using OrCAD Capture and PSpiceBelum ada peringkat

- Programming the Raspberry Pi, Third Edition: Getting Started with PythonDari EverandProgramming the Raspberry Pi, Third Edition: Getting Started with PythonPenilaian: 5 dari 5 bintang5/5 (2)

- Electrical Engineering 101: Everything You Should Have Learned in School...but Probably Didn'tDari EverandElectrical Engineering 101: Everything You Should Have Learned in School...but Probably Didn'tPenilaian: 4.5 dari 5 bintang4.5/5 (27)

- Teach Yourself Electricity and Electronics, 6th EditionDari EverandTeach Yourself Electricity and Electronics, 6th EditionPenilaian: 3.5 dari 5 bintang3.5/5 (15)

- Heat Transfer Engineering: Fundamentals and TechniquesDari EverandHeat Transfer Engineering: Fundamentals and TechniquesPenilaian: 4 dari 5 bintang4/5 (1)

- Conquering the Electron: The Geniuses, Visionaries, Egomaniacs, and Scoundrels Who Built Our Electronic AgeDari EverandConquering the Electron: The Geniuses, Visionaries, Egomaniacs, and Scoundrels Who Built Our Electronic AgePenilaian: 4.5 dari 5 bintang4.5/5 (10)

- 2022 Adobe® Premiere Pro Guide For Filmmakers and YouTubersDari Everand2022 Adobe® Premiere Pro Guide For Filmmakers and YouTubersPenilaian: 5 dari 5 bintang5/5 (1)

- Build Your Own Electronics WorkshopDari EverandBuild Your Own Electronics WorkshopPenilaian: 3.5 dari 5 bintang3.5/5 (3)

- The Innovators: How a Group of Hackers, Geniuses, and Geeks Created the Digital RevolutionDari EverandThe Innovators: How a Group of Hackers, Geniuses, and Geeks Created the Digital RevolutionPenilaian: 4.5 dari 5 bintang4.5/5 (543)

- Upcycled Technology: Clever Projects You Can Do With Your Discarded Tech (Tech gift)Dari EverandUpcycled Technology: Clever Projects You Can Do With Your Discarded Tech (Tech gift)Penilaian: 4.5 dari 5 bintang4.5/5 (2)

- The Phone Fix: The Brain-Focused Guide to Building Healthy Digital Habits and Breaking Bad OnesDari EverandThe Phone Fix: The Brain-Focused Guide to Building Healthy Digital Habits and Breaking Bad OnesPenilaian: 5 dari 5 bintang5/5 (1)

- Current Interruption Transients CalculationDari EverandCurrent Interruption Transients CalculationPenilaian: 4 dari 5 bintang4/5 (1)