Operating System Concepts: Govindarajan

Diunggah oleh

Shashidhar Narayana KrishnamurthyDeskripsi Asli:

Judul Asli

Hak Cipta

Format Tersedia

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniHak Cipta:

Format Tersedia

Operating System Concepts: Govindarajan

Diunggah oleh

Shashidhar Narayana KrishnamurthyHak Cipta:

Format Tersedia

Operating System Concepts

Govindarajan

Overview

Introduction

The Kernel

Process Management

Scheduling

Memory Management

System Calls

Interrupts

Virtual FileSystem

Virtual Machines

Introduction

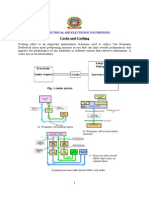

X! "rchitecture

an x86 CPU with registers, execution unit, and memory

management

Memory

Disk

Dispay

!ther "esources

#$!% "!M

Cock, etc&

Introduction

'pp( 'pp) 'pp*

Introduction

" program that acts as an intermediary #etween a user

o$ a computer and the computer hardware%

Operating system goals

+xecute user programs

Contros execution o, programs to prevent errors and improper use

o, the computer

Make the computer system convenient to use

Use the computer hardware optimay

Manages a resources

Decides -etween con,icting re.uests ,or e,,icient and ,air resource

use

/erne 0 %ystem programs

Introduction

The Kernel

Process Management

Process

1undamenta a-straction in Unix

' program in execution

$ncudes

Program counter

%tack

Data and text section

"esources

'ddress space

!ne or more execution threads

Process in Memory

Process &esctriptor

Process Management

Process Creation

,ork23

C!4 pages

Process descriptor 2dup5task5struct233

%et 6'%/5U7$76+""UP6$#8+

get5pid23

exec23

v,ork23

cone23

Process Creation

Process States

Scheduling

Scheduler

Divides the ,inite resource o, CPU time -etween runna-e

processes

#asis o, mutitasking operating systems

Co9operative

Pre9emptive

Utii:e processor time optimay

Decide what process to run next -ased on a poicy

$;! -ound

CPU -ound

Process priority 29)< to 0(=3

Scheduling

Scheduling

CP' scheduling decisions may ta(e place when a

process

%witches ,rom running to waiting state

%witches ,rom running to ready state

%witches ,rom waiting to ready

6erminates

Process Management

Time)sharing

Prioriti:ed credit9-ased > process with most credits is schedued next

Credit su-tracted when timer interrupt occurs

4hen credit ? <, another process chosen

4hen a processes have credit ? <, recrediting occurs

#ased on ,actors incuding priority and history

*eal)time

%o,t rea9time

Posix&(- compiant > two casses

1C1% and ""

@ighest priority process aways runs ,irst

Scheduling

Scheduling

Memory Management

Program must -e -rought 2,rom disk3 into memory and paced

within a process ,or it to -e run

Main memory and registers are ony storage CPU can access

directy

"egister access in one CPU cock 2or ess3

Main memory can take many cyces

Cache sits -etween main memory and CPU registers

Protection o, memory re.uired to ensure correct operation

Memory Management

Memory Management

'ddress -inding o, instructions and data to memory addresses

can happen at three di,,erent stages

Compile timeA $, memory ocation known a priori, a#solute code can

-e generatedB must recompie code i, starting ocation changes

+oad timeA Must generate relocata#le code i, memory ocation is not

known at compie time

,-ecution timeA #inding deayed unti run time i, the process can -e

moved during its execution ,rom one memory segment to another&

7eed hardware support ,or address maps 2e&g&, -ase and imit

registers3

Memory Management

'ddress -inding o, instructions and data to memory addresses

can happen at three di,,erent stages

Compile timeA $, memory ocation known a priori, a#solute code can

-e generatedB must recompie code i, starting ocation changes

+oad timeA Must generate relocata#le code i, memory ocation is not

known at compie time

,-ecution timeA #inding deayed unti run time i, the process can -e

moved during its execution ,rom one memory segment to another&

7eed hardware support ,or address maps 2e&g&, -ase and imit

registers3

Memory Management

Memory Management

6he concept o, a ogica address space that is -ound to a

separate physical address space is centra to proper memory

management

+ogical address > generated -y the CPUB aso re,erred to as virtual

address

Physical address > address seen -y the memory unit

8ogica and physica addresses are the same in compie9time and

oad9time address9-inding schemes

ogica 2virtua3 and physica addresses di,,er in execution9time

address9-inding scheme

Memory Management 'nit

.ardware device that maps virtual to physical

address

In MM' scheme/ the value in the relocation register

is added to every address generated #y a user

process at the time it is sent to memory

The user program deals with logical addresses0 it

never sees the real physical addresses

Memory Management

" process can #e swapped temporarily out o$ memory to a #ac(ing store/

and then #rought #ac( into memory $or continued e-ecution

1ac(ing store 2 $ast dis( large enough to accommodate copies o$ all

memory images $or all users0 must provide direct access to these memory

images

*oll out/ roll in 2 swapping variant used $or priority)#ased scheduling

algorithms0 lower)priority process is swapped out so higher)priority process

can #e loaded and e-ecuted

Ma3or part o$ swap time is trans$er time0 total trans$er time is directly

proportional to the amount o$ memory swapped

Modi$ied versions o$ swapping are $ound on many systems 4i%e%/ '5IX/ +inu-/

and 6indows

System maintains a ready 7ueue o$ ready)to)run processes which have

memory images on dis(

Swapping

Memory Management

Main memory usuay into two partitionsA

"esident operating system, usuay hed in ow memory with interrupt

vector

User processes then hed in high memory

"eocation registers used to protect user processes ,rom each

other, and ,rom changing operating9system code and data

#ase register contains vaue o, smaest physica address

8imit register contains range o, ogica addresses > each ogica

address must -e ess than the imit register

MMU maps ogica address dynamically

Contiguous "llocation

Mutipe9partition aocation

@oe > -ock o, avaia-e memoryB hoes o, various si:e are

scattered throughout memory

4hen a process arrives, it is aocated memory ,rom a hoe arge

enough to accommodate it

!perating system maintains in,ormation a-outA

aocated partitions

,ree partitions 2hoe3

!%

process C

process 8

process )

!%

process C

process )

!%

process C

process )

!%

process C

process =

process )

process =

process

(<

&ynamic Storage "llocation

First)$itA 'ocate the first hoe that is -ig enough

1est)$itA 'ocate the smallest hoe that is -ig enoughB

must search entire ist, uness ordered -y si:e

Produces the smaest e,tover hoe

6orst)$itA 'ocate the largest hoeB must aso search

entire ist

Produces the argest e,tover hoe

Paging

8ogica address space o, a process can -e

noncontiguousB process is aocated physica memory

whenever the atter is avaia-e

Divide physica memory into ,ixed9si:ed -ocks caed

$rames 2si:e is power o, ), -etween C() -ytes and

8,(=) -ytes3

Divide ogica memory into -ocks o, same si:e caed

pages

/eep track o, a ,ree ,rames

6o run a program o, si:e n pages, need to ,ind n ,ree

,rames and oad program

%et up a page ta-e to transate ogica to physica

addresses

System Calls

Programming inter,ace to the services provided -y the !%

6ypicay written in a high9eve anguage 2C or C003

Mosty accessed -y programs via a high9eve "pplication

Program Inter$ace 4"PI8 rather than direct system ca use

6hree most common 'P$s are 4in*) 'P$ ,or 4indows,

P!%$D 'P$ ,or P!%$D9-ased systems 2incuding virtuay a

versions o, U7$D, 8inux, and Mac !% D3, and Eava 'P$ ,or

the Eava virtua machine 2EFM3

4hy use 'P$s rather than system casG

System Calls

System Calls

6ypicay, a num-er associated with each system ca

%ystem9ca inter,ace maintains a ta-e indexed according to

these num-ers

6he system ca inter,ace invokes intended system ca in !%

kerne and returns status o, the system ca and any return

vaues

6he caer need know nothing a-out how the system ca is

impemented

Eust needs to o-ey 'P$ and understand what !% wi do as a

resut ca

Most detais o, !% inter,ace hidden ,rom programmer -y 'P$

Managed -y run9time support i-rary 2set o, ,unctions -uit into

i-raries incuded with compier3

"PI 2 System Call 2 OS

System Call ,-ample

Types o$ Syscalls

Process contro

1ie management

Device management

$n,ormation maintenance

Communications

Virtual File System

Firtua 1ie %ystems 2F1%3 provide an o-ject9oriented way o,

impementing ,ie systems&

F1% aows the same system ca inter,ace 2the 'P$3 to -e

used ,or di,,erent types o, ,ie systems&

6he 'P$ is to the F1% inter,ace, rather than any speci,ic type

o, ,ie system&

Virtual File System

VFS O#3ects

%uper-ock

"epresents speci,ic mounted ,ie system

read5inode23, sync5,s23

$node o-ject

%peci,ic ,ie

create23, ink23

dentry o-ject

%peci,ic directory entry

d5compare23, d5deete23

,ie o-ject

!pen ,ie as associated with a process

read23 and write23

Interrupts

$nterrupt trans,ers contro to the interrupt service routine

generay, through the interrupt vector, which contains the

addresses o, a the service routines&

$nterrupt architecture must save the address o, the

interrupted instruction&

$ncoming interrupts are disabled whie another interrupt is

-eing processed to prevent a lost interrupt&

' trap is a so,tware9generated interrupt caused either -y an

error or a user re.uest&

'n operating system is interrupt driven&

Interrupt .andling

6he operating system preserves the state o, the CPU -y

storing registers and the program counter&

Determines which type o, interrupt has occurredA

polling

vectored interrupt system

%eparate segments o, code determine what action shoud -e

taken ,or each type o, interrupt

Interrupt Timeline

Interrupts

Interrupts

(ernel9s interrupt handling data structures are set up #y

the device drivers

System 1IOS sets up the Interrupt topology

PCI set up code writes the pin num#er o$ the interrupt

controller into the PCI con$iguration header $or each

device

PCI devices may share interrupts

Interrupt .andling

Interrupt Controllers

XT PIC

6wo 89-it controers

Fery ,ew avaia-e ,ree ines

"PIC

'dvanced programma-e $nterrupt Controer

8'P$C

$!'P$C

Provides ))H usa-e $"I vectors ,rom an $;! 'P$C

8'P$Cs manage a externa interrupts ,or the processor that it is part

o,

$;! 'P$Cs contain a redirection ta-e to route $nterrupts to 8'P$Cs

Virtual Machines

Virtual Machines

:uestions;

Product &iagrams 2 VMware Server

Product &iagrams 2 VMware Server

+%D %erver

Product Diagrams > FMware $n,rastructure *

+%D %erver

Product Diagrams > FMware $n,rastructure *

Anda mungkin juga menyukai

- Unit I Overview & Instructions: Cs6303-Computer ArchitectureDokumen16 halamanUnit I Overview & Instructions: Cs6303-Computer Architecturetamizhanps100% (1)

- OS Viva Expected QuestionsDokumen7 halamanOS Viva Expected Questionsaamer_shahbaazBelum ada peringkat

- Input-Output Operations.: J.Tiberghien - Computer Systems - Printed: 29/09/2014Dokumen10 halamanInput-Output Operations.: J.Tiberghien - Computer Systems - Printed: 29/09/2014Thota Indra MohanBelum ada peringkat

- The Evaluation of Operating SystemDokumen6 halamanThe Evaluation of Operating Systemksai.mbBelum ada peringkat

- 08 - The Processor - Students VersionDokumen9 halaman08 - The Processor - Students Versionfghf1Belum ada peringkat

- Operating System Viva Questions: 1. Explain The Concept of Reentrancy?Dokumen7 halamanOperating System Viva Questions: 1. Explain The Concept of Reentrancy?Sreeraj JayarajBelum ada peringkat

- Process & Kernel 2Dokumen20 halamanProcess & Kernel 2deepak_shankyBelum ada peringkat

- Linux 56 AssignmentDokumen32 halamanLinux 56 Assignmentr_k_sBelum ada peringkat

- System Unit & Input/ Output Devices & Secondary StorageDokumen20 halamanSystem Unit & Input/ Output Devices & Secondary StorageSaya Munir100% (1)

- Computers in Control SystemsDokumen9 halamanComputers in Control SystemsAgrippa MungaziBelum ada peringkat

- Basic Operating System Concepts: A ReviewDokumen53 halamanBasic Operating System Concepts: A ReviewPradnya JoshiBelum ada peringkat

- 1 - Computer ArchitectureDokumen3 halaman1 - Computer Architectureozy.almondry2021Belum ada peringkat

- Operating System QuestionsDokumen4 halamanOperating System QuestionsAnonymous V7P5fNQIBelum ada peringkat

- Memory Management: Concept of Memory HierarchyDokumen10 halamanMemory Management: Concept of Memory HierarchyEdo LeeBelum ada peringkat

- Operating System ReportDokumen14 halamanOperating System Reportrajesh__rajesh100% (3)

- Lec2 Lec3 Cpuvirt FullDokumen67 halamanLec2 Lec3 Cpuvirt FullamulyaBelum ada peringkat

- CS2253 Computer Organization and Architecture Lecture NotesDokumen181 halamanCS2253 Computer Organization and Architecture Lecture NotesRoselene RebeccaBelum ada peringkat

- Aplus Practical Exam CramDokumen42 halamanAplus Practical Exam CramUzziel Mendez100% (1)

- The Basic Structure and Functional Units of a Computer SystemDokumen180 halamanThe Basic Structure and Functional Units of a Computer SystemAltafAhmed2706Belum ada peringkat

- Basic Computer Organization: Unit - 1Dokumen9 halamanBasic Computer Organization: Unit - 1theresa.painterBelum ada peringkat

- Operating System ComponentsDokumen59 halamanOperating System ComponentsJikku VarUgheseBelum ada peringkat

- Session 9Dokumen26 halamanSession 9theresa.painterBelum ada peringkat

- Chapter 4 The Components of The System UnitDokumen8 halamanChapter 4 The Components of The System Unitpiash246Belum ada peringkat

- Answers to Sample Paper and QuestionsDokumen29 halamanAnswers to Sample Paper and QuestionsPradeep KumarBelum ada peringkat

- Memory ManagementDokumen63 halamanMemory ManagementTheSpeedDealBelum ada peringkat

- MS Syllabus 2009Dokumen47 halamanMS Syllabus 2009Anubhav KhareBelum ada peringkat

- Basic Hardware IssuesDokumen18 halamanBasic Hardware IssuesRakesh PatilBelum ada peringkat

- KernelDokumen9 halamanKernelvikasrampal99Belum ada peringkat

- Purpose and Function of The CPUDokumen16 halamanPurpose and Function of The CPUsophiegcseBelum ada peringkat

- Operating SystemsDokumen22 halamanOperating Systemsakj1992Belum ada peringkat

- ELECTRICAL AND ELECTRONIC ENGINEERING Cache CachingDokumen15 halamanELECTRICAL AND ELECTRONIC ENGINEERING Cache CachingEnock OmariBelum ada peringkat

- Evolution of OSDokumen67 halamanEvolution of OSErjohn BulosBelum ada peringkat

- OS Introduction - 40 Character TitleDokumen41 halamanOS Introduction - 40 Character Titlesatya1401Belum ada peringkat

- Department of Information TechnologyDokumen25 halamanDepartment of Information Technologymyilvahanan85Belum ada peringkat

- Operating SystemDokumen174 halamanOperating SystemHarshini BabyBelum ada peringkat

- Module 3 (Ddco)Dokumen35 halamanModule 3 (Ddco)manasashivanna7991Belum ada peringkat

- Computer Architecture: Computer Architecture Refers To Those Attributes of A System Visible To ADokumen6 halamanComputer Architecture: Computer Architecture Refers To Those Attributes of A System Visible To AKobinaBelum ada peringkat

- Memory Hir and Io SystemDokumen26 halamanMemory Hir and Io SystemArjun M BetageriBelum ada peringkat

- GCSE Computer Science: Geraint D. Jones Mark D. ThomasDokumen72 halamanGCSE Computer Science: Geraint D. Jones Mark D. ThomasMohit ChanganiBelum ada peringkat

- Computer Fundamentals NotesDokumen40 halamanComputer Fundamentals NotesRatish KakkadBelum ada peringkat

- Module 3 (Ddco)Dokumen28 halamanModule 3 (Ddco)manasashivanna7991Belum ada peringkat

- Gcse Computer Science Final VersionDokumen72 halamanGcse Computer Science Final VersionZalifah AswanaBelum ada peringkat

- Main Memory ManagementDokumen7 halamanMain Memory ManagementpoojajadhavBelum ada peringkat

- Chapter 8Dokumen36 halamanChapter 8JackYuan JinFengBelum ada peringkat

- Process Description and ControlDokumen53 halamanProcess Description and ControlAhmed HeshamBelum ada peringkat

- What Is Paging? Why Paging Is Used?: Resource Allocator and ManagerDokumen8 halamanWhat Is Paging? Why Paging Is Used?: Resource Allocator and ManagerCatherine OliverBelum ada peringkat

- HardwareDokumen17 halamanHardwareSLADIFYBelum ada peringkat

- Operating System Concepts 9th Edition Study GuideDokumen19 halamanOperating System Concepts 9th Edition Study Guidehotfudge2116100% (2)

- Memory and Operating System: ObjectivesDokumen9 halamanMemory and Operating System: ObjectivessignalcontrolspjBelum ada peringkat

- Advanced Performance Tuning..Dokumen135 halamanAdvanced Performance Tuning..Satish MadhanaBelum ada peringkat

- Architecture: SAP R/3 Workload AnalysisDokumen5 halamanArchitecture: SAP R/3 Workload AnalysispapusahaBelum ada peringkat

- A NotesDokumen5 halamanA NotesNirav MehtaBelum ada peringkat

- AnywayDokumen116 halamanAnywayAnonymous nzfEotriWKBelum ada peringkat

- Overview of Computers and Programming: Understanding Components and LanguagesDokumen27 halamanOverview of Computers and Programming: Understanding Components and Languagessyam_5491983Belum ada peringkat

- Architecture and OrganizationDokumen4 halamanArchitecture and OrganizationNickBelum ada peringkat

- SAP R/3 Architecture OverviewDokumen66 halamanSAP R/3 Architecture OverviewSandyChinnaBelum ada peringkat

- Operating Systems Interview Questions You'll Most Likely Be Asked: Job Interview Questions SeriesDari EverandOperating Systems Interview Questions You'll Most Likely Be Asked: Job Interview Questions SeriesBelum ada peringkat

- Preliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960Dari EverandPreliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960Belum ada peringkat

- 20 Windows Tools Every SysAdmin Should KnowDari Everand20 Windows Tools Every SysAdmin Should KnowPenilaian: 5 dari 5 bintang5/5 (2)

- Unit 1 MCQDokumen12 halamanUnit 1 MCQNikhil BhaleraoBelum ada peringkat

- Protocolo Interface TARGADokumen5 halamanProtocolo Interface TARGAMarcos QuequeBelum ada peringkat

- Dell Studio XPS™ 435T/9000 Service Manual: Notes, Cautions, and WarningsDokumen41 halamanDell Studio XPS™ 435T/9000 Service Manual: Notes, Cautions, and WarningsaairrBelum ada peringkat

- Smallest in The Industry, With Top-Class Performance and FunctionsDokumen4 halamanSmallest in The Industry, With Top-Class Performance and FunctionsSergio Eu CaBelum ada peringkat

- AMT - CPU Product Price List - Jan'2020 (06012020)Dokumen1 halamanAMT - CPU Product Price List - Jan'2020 (06012020)Hasnan IbrahimBelum ada peringkat

- Intel Atom, Core and Pentium SRP with Motherboards and Memory SRPDokumen2 halamanIntel Atom, Core and Pentium SRP with Motherboards and Memory SRPWaylan BasungitBelum ada peringkat

- Computer Software and Its TypesDokumen12 halamanComputer Software and Its TypesHaroon Zafar50% (2)

- EEL3801 Lab Manual PDFDokumen29 halamanEEL3801 Lab Manual PDFMLW BDBelum ada peringkat

- Midterm Exam - Attempt ReviewDokumen2 halamanMidterm Exam - Attempt ReviewTon LazaroBelum ada peringkat

- Ics3U UNIT#1 Lesson#5 Operating SystemDokumen19 halamanIcs3U UNIT#1 Lesson#5 Operating SystemNidhi VyasBelum ada peringkat

- Sample Questions For Paper 1Dokumen13 halamanSample Questions For Paper 1Dexter MacBelum ada peringkat

- Logos of Top Multinational Companies Through the YearsDokumen19 halamanLogos of Top Multinational Companies Through the Yearsasif2400Belum ada peringkat

- TCS Notes Unit 1Dokumen30 halamanTCS Notes Unit 1Utkarsh SinghBelum ada peringkat

- Berger A.s.embedded Systems Design - An Introduction To Processes Tools and Techniques.2002Dokumen210 halamanBerger A.s.embedded Systems Design - An Introduction To Processes Tools and Techniques.2002ayush charde 786Belum ada peringkat

- OpenocdDokumen221 halamanOpenocdJim JimBelum ada peringkat

- English for Informatics 1: Identifying Network TopologiesDokumen8 halamanEnglish for Informatics 1: Identifying Network TopologiesAgungBelum ada peringkat

- CofaDokumen286 halamanCofamhommad saifBelum ada peringkat

- DUI0646C Cortex m7 DgugDokumen315 halamanDUI0646C Cortex m7 Dgugserdar.karamanBelum ada peringkat

- Computer Shopper August 2005 PDF eBook-iNTENSiTYDokumen160 halamanComputer Shopper August 2005 PDF eBook-iNTENSiTYvoodoower100% (3)

- Virtual To Physical Address TranslationDokumen36 halamanVirtual To Physical Address TranslationNagender GoudBelum ada peringkat

- MP2100 Maitenance Manual 6439726 01 4307920 01Dokumen57 halamanMP2100 Maitenance Manual 6439726 01 4307920 01ahmed nourBelum ada peringkat

- How To Develop Embedded Software Using The QEMU Machine EmulatorDokumen107 halamanHow To Develop Embedded Software Using The QEMU Machine Emulatorvikas upadhyayBelum ada peringkat

- Computer Basic NotesDokumen7 halamanComputer Basic NotesmarjBelum ada peringkat

- 107 97 HardwarePTDRLPFBUSBDokumen2 halaman107 97 HardwarePTDRLPFBUSBVoicu StaneseBelum ada peringkat

- Raspberry PiDokumen15 halamanRaspberry PiAjayChandrakarBelum ada peringkat

- How To Interface A SD CARD To An Arduino BoardDokumen4 halamanHow To Interface A SD CARD To An Arduino BoardgdgthrtBelum ada peringkat

- CJ1W-SPU01-V2: High-Speed Collection of System DataDokumen13 halamanCJ1W-SPU01-V2: High-Speed Collection of System Datamax_6744Belum ada peringkat

- FAS2040 Install and Setup DiagDokumen2 halamanFAS2040 Install and Setup Diagj5unBelum ada peringkat

- EPson SC P5k - SMDokumen490 halamanEPson SC P5k - SMA100% (1)