Thi Nghiem Ky Thuat So - DE1

Diunggah oleh

Dương Tấn QuốcJudul Asli

Hak Cipta

Format Tersedia

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniHak Cipta:

Format Tersedia

Thi Nghiem Ky Thuat So - DE1

Diunggah oleh

Dương Tấn QuốcHak Cipta:

Format Tersedia

TN KTS-Altera DE1 B mn in T - HBK Tp HCM

Kit th nghim K thut s

Altera DE1

Trang 1

TN KTS-Altera DE1 B mn in T - HBK Tp HCM

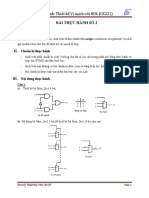

CC BC TH NGHIM K THUT S TRN KIT ALTERA DE1

Nhp file thit k dng m Verilog

Bin dch

M phng chc nng

No

Thit k ng?

Yes

Gn chn

Phn tch v m phng thi gian

No

t yu cu thi gian?

Yes

Np kit v th mch

Hnh 1: Cc bc thc hin

Trang 2

TN KTS-Altera DE2 B mn in T - HBK Tp HCM

Bc 1. Chy chng trnh Quartus II:

Hnh 2: Mn hnh chnh Quartus II.

Trang 3

TN KTS-Altera DE1 B mn in T - HBK Tp HCM

Bc 2. To project mi:

1. Chn File > New Project Wizard:

Hnh 3: File menu.

2. Chn th mc lm vic, t tn cho project ri nhn Next:

Hnh 4: To 1 project mi.

Trang 4

TN KTS-Altera DE1 B mn in T - HBK Tp HCM

Nhn Yes.

Hnh 5: Quartus II to th mc mi cho project.

3. Khng cn phi chn thm file no, nhn NEXT:

Hnh 6: Thm file thit k c sn.

4.

Chn chip Cyclone II EP2C20F484C7N, nhn NEXT.

Hnh 7: Chn chip FPGA.

Trang 5

TN KTS-Altera DE1 B mn in T - HBK Tp HCM

5. Khng cn chn EDA TOOL no, nhn Next:

Hnh 8: Chn EDA tools.

6. Bng tm tt cc thng s ci t cho project nh hnh 9. Nhn Finish

Hnh 9: Tm tt cc thng s ci t cho project.

Trang 6

TN KTS-Altera DE1 B mn in T - HBK Tp HCM

Chng trnh s quay tr v mn hnh chnh:

Hnh 10: Mn hnh Quartus II cho project mi c to.

Trang 7

TN KTS-Altera DE2 B mn in T - HBK Tp HCM

Bc 3. Nhp file thit k dng m Verilog:

3.1. Chn File > New, chn Verilog HDL File, ri nhn OK.

Hnh 13: Chn Verilog HDL file.

Trang 8

TN KTS-Altera DE2 B mn in T - HBK Tp HCM

3.2. To file thit k mi: chn File > Save As, chn Save as type = Verilog HDL

File. t tn cho file. Chn Add file to current project. Nhn Save

Hnh 14: t tn file.

3.3 Nhp chng trnh dng m Verilog vo khung Text Editor.

Lu file: File > Save, hoc nhn Ctrl-S.

Hnh 15: Mn hnh Quartus II sau khi to file.

Trang 9

TN KTS-Altera DE1 B mn in T - HBK Tp HCM

C th ty chn cc tnh nng ca Text Editor bng cch chn: Tools > Options > Text

Editor.

Hnh 16: Cc ty chn cho Text Editor.

C th dng template nhp chng trnh: Edit > Insert Template > Verilog HDL

3.4. a file thit k vo project: chn Assignments > Settings, chn Files hoc chn

Project > Add/Remove Files in Project

Nu dng Quartus II Text Editor v chn Add file to current project nh

trong phn 3.2 th file thit k s c np thng vo project.

Hnh 17: Ty chn cc thng s cho project.

Trang 10

TN KTS-Altera DE1 B mn in T - HBK Tp HCM

Nu cha c th phi np nh sau:

1. Copy file thit k vo th mc lm vic.

2. Nhn nt ... chn file

Hnh 18: Chn file

3. Chn file cn thit ri nhn Open. Sau nhn Add, OK.

Bc 4. Bin dch chng trnh thit k:

4.1 Chn Processing > Start Compilation, hoc nhn nt .

Ch bin dch chng trnh cho n khi bo Successful (hoc unsuccessful) ri nhn OK

Hnh 19: Mn hnh sau khi bin dch thnh cng.

Trang 11

TN KTS-Altera DE1 B mn in T - HBK Tp HCM

4.2 Khi bin dch xong chng trnh s t ng hin th Compilation Report. Report ny

cng c th c m bng cch chn Processing > Compilation Report hoc nhn

nt .

Hnh 20: Kt qu bin dch.

Thng bo li:

Hnh 25: Thng bo bin dch c li.

Hnh 26: Ni dung li.

Hnh 27: Xc nh v tr li

Trang 12

TN KTS-Altera DE1 B mn in T - HBK Tp HCM

Bc 5. Gn chn ca project cho kit Altera DE 1:

5.1 Chn Assignments > Import Assignments. Chn file DE1_pin_assignments.csv Nhn OK.

Hnh 24. Mn hnh Import Assignments

5.2 Chn Assignments > Assignment Editor. Chn Category = Pin.

Double-click vo vt sng highlight mu xanh dng ct To. Ri gn cc chn vo, ra

tng ng.

Hnh 25. Drop-down menu hin th tn cc ng vo, ra.

Lu file thit k.

Hnh 27. Hon tt vic gn chn

Bc 6. M phng mch thit k:

1. Chn File > New - Chn Vector Waveform File - Nhn OK.

2. Mn hnh Waveform Editor nh Hnh 32.

Lu vector waveform file (.vwf)

Chn thi gian thc hin m phng t 0 n 200 ns bng cch chn Edit > End Time ri

nhp 200 ns.

Chn View > Fit in Window

13

TN KTS-Altera DE1 B mn in T - HBK Tp HCM

Hnh 33. Mn hnh Waveform Editor

3. Chn Edit > Insert Node or Bus.

Hnh 34. Hp thoi Insert Node or Bus.

Nhn nt Node Finder.

Hnh 35. Chn nodes a vo Waveform Editor.

Chn Filter = Pins: all ri nhn nt List.

Chn nt >> ri nhn OK.

Nhn OK trong ca s hnh 34.

4. Chn cc gi tr logic ca cc ng vo th. Lu vector waveform file.

14

TN KTS-Altera DE1 B mn in T - HBK Tp HCM

Hnh 37. Chn cc gi tr logic ca cc ng vo th

6.1 Thc hin m phng: (Functional Simulation)

Chn Assignments > Settings chn Simulation mode = Functional ri nhn OK.

Hnh 38. Chn Simulation mode = Functional.

Chn Processing > Generate Functional Simulation Netlist.

Bt u thc hin m phng bng cch chn Processing > Start Simulation, hoc nhn nt .

Hnh 39. Kt qu m phng.

15

TN KTS-Altera DE1 B mn in T - HBK Tp HCM

Bc 7. Lp trnh cho FPGA trn kit Altera DE1:

Trn kit DE2 t SW19 = RUN (JTAG mode)

Kt ni USB cp t my tnh vi USB-Blaster trn kit DE1.

Cp ngun cho kit.

Chn Tools > Programmer. Chn Mode = JTAG. Chn Hardware = USB-Blaster theo nh

Hnh 42.

Chn Check box Program/Configure.

Hnh 41. Mn hnh programing.

Hnh 42. Mn hnh chn hardware.

Nhn nt Start bt u np project vo kit DE1.

Bc 8. Th project va thit k:

Tin hnh th project va c np trn kit DE1.

Nu mun thay i thit k trc ht phi tt mn hnh Programmer ri thc hin project mi t bc

2.

16

TN KTS-Altera DE1 B mn in T - HBK Tp HCM

Bi th nghim 1

Switches, Lights, Multiplexers

1. Th nghim 1.1:

Thc hin mch th nghim c ng vo l 10 cng tc SW 90 , v ng ra l 10 n LED mu LEDR 90 dng c trng

thi ca cc ng vo.

// Chung trnh Verilog n gin cho bi TN 1.1:

module tn1_1 (SW, LEDR);

input [9:0] SW;

// toggle switches

output [9:0] LEDR;

// red LEDs

assign LEDR = SW;

endmodule

Cc bc cn thc hin:

1.

2.

To project mi.

Vit chng trnh Verilog cho bi TN

3.

4.

Gn chn & bin dch project.

Np project vo kit TN. Th mch.

2. Th nghim 1.2:

Cho mch multiplexer 2 sang 1 nh hnh 2 vi ng vo chn knh s. Nu s = 0 ng ra m s bng ng vo x, v nu s

= 1 th ng ra m = y.

x

m

s

y

a) S mch

s

s

0

1

x

y

x

y

b) Bng s tht

0

1

c) K hiu

Hnh 2. Mch multiplexer 2 sang 1.

Mch c th m t dng m Verilog nh sau:

assign m = ( s & x) (s & y);

Dng 4 b multiplexer 2 sang 1 nh hnh 2 thc hin mch multiplexer 2 sang 1 - 4 bit nh hnh 3a. Mch c 2 ng

vo nh phn 4 bit X v Y, v ng ra 4 bit M. Nu s = 0 th M = X , cn s = 1 th M = Y.

17

TN KTS-Altera DE1 B mn in T - HBK Tp HCM

x3

y3

X3

Y3

m3

m2

s

4

x0

y0

m0

a) s mch

b) k hiu

Hnh 3. Mch multiplexer 2 sang 1, 4 bit.

Cc bc cn thc hin:

1. To project mi.

2. Vit chng trnh Verilog vi:

s = SW9 v ni vi LEDR9

X = SW3-0 v ni vi LEDR3-0

Y = SW7-4 v ni vi LEDR7-4

M = LEDG3-0

3. Gn chn

4. Bin dch project.

5. Np project vo kit TN.

6. Th mch bng cch thay i cc cng tc SW ri theo di cc n LED xanh, .

3. Th nghim 1.3:

Dng 3 b multiplexer 2 sang 1 nh hnh 2 thc hin mch multiplexer 4 sang 1 nh hnh 4a.

Mch c 4 ng vo u, v, w v x; 1 ng ra m; 2 ng vo chn knh s1 s0

s1

s0

u

v

w

x

0

1

a) s mch

18

TN KTS-Altera DE1 B mn in T - HBK Tp HCM

s1 s0

0

0

1

1

u

v

w

x

0

1

0

1

s1

s0

u

x

v

00

01

10

11

b) bng s tht

c) k hiu

Hnh 4. Mch multiplexer 4 sang 1

Tng t dng 2 mch multiplexer 4 1 nh hnh 4a thc hin mch multiplexer 4 1 - 2 bit nh

hnh 5

s1

s0

U

2

2

V

W

X

2

2

00

01

10

11

Hnh 5. Mch multiplexer 4 sang 1 - 2 bit

Cc bc cn thc hin:

1. To project mi.

2. Vit chng trnh Verilog vi:

s 1 s 0 = SW9-8 v ni vi LEDR9-8

U-X = SW7-0 v ni vi LEDR7-0

M = LEDG1-0

3. Gn chn

4. Bin dch project.

5. Np project vo kit TN.

6. Th mch bng cch thay i cc cng tc SW ri theo di cc n LED xanh, .

19

TN KTS-Altera DE1 B mn in T - HBK Tp HCM

4. Th nghim 1.4:

Thc hin b gii m c 2 ng vo c1 c0 v 7 ng ra t 0 n 6 dng hin th cc k t trn b hin th 7 on

nh hnh 6.

Bng 1 lit k cc k t cn hin th (gm H,E,L v k t O) tng ng vi cc ng vo c1 c0 .

Cc ng ra tch cc mc logic 0.

0

5

c1

c0

7-segment

decoder

1

2

Hnh 6. B gii m 7 on

c1 c0

K t

00

01

10

11

H

E

L

O

Bng 1. Bng m ch

Cc bc cn thc hin:

1. To project mi.

2. Vit chng trnh Verilog vi:

o Cc ng vo c1 c0 ni vi cc cng tc SW1-0

o Cc ng ra 0 6 ni vi HEX00, HEX01..HEX06

3. Gn chn

4. Bin dch project.

5. Np project vo kit TN.

6. Th mch bng cch thay i cc cng tc SW10 ri quan st b hin th 7 on.

20

TN KTS-Altera DE1 B mn in T - HBK Tp HCM

5. Th nghim 1.5:

Thc hin mch in hin th ch xoay nh hnh 7 hot ng theo bng 2.

Cc cng tc SW 70 dng to k t v SW 98 dng chn k t hin th.

SW 9

SW 8

SW 7 6

SW 5 4

SW 3 2

SW 1 0

0

00

01

10

11

7-segment

decoder

2

3

Hnh 7. Mch c th chn & hin th 1 trong 4 k t.

SW9 SW8

Hin th

00

01

10

11

H

E

L

O

Bng 2. Hin th ch xoay HELLO.

module part5 (SW, HEX0);

input [9:0] SW;

// toggle switches

output [0:6] HEX0;

// 7-seg displays

wire [1:0] M;

mux 2bit 4to1 M0 (SW[9:8], SW[7:6], SW[5:4], SW[3:2], SW[1:0], M);

char 7seg H0 (M, HEX0);

endmodule

// implements a 2-bit wide 4-to-1 multiplexer

module mux 2bit 4to1 (S, U, V, W, X, M);

input [1:0] S, U, V, W, X;

output [1:0] M;

. . . code not shown

endmodule

// implements a 7-segment decoder for H, E, L and O

module char 7seg (C, Display);

input [1:0] C;

// input code

output [0:6] Display; // output 7-seg code

. . . code not shown

endmodule

Hnh 8. Chng trnh gi cho mch in hnh 7.

21

TN KTS-Altera DE1 B mn in T - HBK Tp HCM

Bi th nghim 2

Numbers & Displays

y l bi th nghim thit k mch t hp thc hin b bin i s nh phn sang s thp phn v mch

cng hai s BCD.

1. Th nghim 2.1:

Dng cc n 7 on HEX1 v HEX0 hin th cc s thp phn t 0 n 9. Gi tr hin th thay i c

bng cc cng tc SW74 v SW 30 tng ng.

1.

2.

3.

4.

Cc bc cn thc hin:

To project mi.

Vit chng trnh Verilog cho bi TN

Gn chn & bin dch project.

Np project vo kit TN. Th mch bng cch thay i cc cng tc v quan st cc n hin th.

2. Th nghim 2.2:

Thc hin 1 phn ca mch chuyn i s nh phn 4 bit V = v 3 v2 v1 v0 thnh s thp phn D = d1 d0 n h hnh

1, b ng 1. Mch bao gm mch so snh ( kim tra V > 9), mch multiplexer v mch A (cha cn thc hin

mch B v b gii m 7 on). Mch s c ng vo V 4 bit, ng ra M 4 bit v ng ra z.

Binary value

Decimal digits

0000

0001

0010

...

0

0

0

...

0

1

2

...

1001

1010

1011

1100

1101

1110

1111

0

1

1

1

1

1

1

9

0

1

2

3

4

5

Bng 1. Bng gi tr chuyn i nh phn thp phn.

Cc bc cn thc hin:

1. To project mi. Vit chng trnh

2.

3.

4.

5.

Bin dch project v thc hin m phng

Vit thm on chng trnh cho mch B v mch gii m 7 on. Dng cc cng tc SW30

nhp s nh phn V v cc n 7 on HEX1, HEX0 hin th s thp phn d 1 d0

Bin dch li ri np project vo kit TN.

Th mch: thay i gi tr V v quan st cc n hin th.

22

TN KTS-Altera DE1 B mn in T - HBK Tp HCM

d1

z

Comparator

Circuit B

4

v3

m3

1

2

d0

v2

m2

0

1

0

7-segment

decoder

4

v1

v0

m1

m0

2

3

Circuit A

Hnh 1. Mch chuyn i nh phn-thp phn.

3. Th nghim 2.3:

Cho mch cng ton phn (FA) nh hnh 2a vi cc ng vo a, b, and ci , cc ng ra s v co .

c o s = a + b + ci .

Dng 4 mch cng FA nh trn thc hin mch cng 4 bit nh hnh 2d.

23

TN KTS-Altera DE1 B mn in T - HBK Tp HCM

ci

s

ci

a

b

a) Mch cng FA

b a ci

co s

0

0

0

0

1

1

1

1

0

0

0

1

0

1

1

1

0

0

1

1

0

0

1

1

0

1

0

1

0

1

0

1

0

1

1

0

1

0

0

1

c) Bng s tht

co

co

FA

b) K hiu

b3 a3 c

3

b2 a2 c

2

FA

FA

FA

s2

c out s 3

b1 a1 c

1

b 0 a 0 c in

FA

s1

s0

d) Mch cng 4 bit

Hnh 2. Mch cng.

Cc bc cn thc hin:

1. To project mi v vit chng trnh Verilog cho mch cng:

Ni cc ng vo A, B v cin vi cc cng tc tng ng SW74 , SW 30 v SW8 v vi

cc n LED mu LEDR

Ni cc ng ra c out v S vi cc n LED mu xanh LEDG

2.

3.

Gn chn, bin dch v np project vo kit TN

Th mch bng cch thay i cc gi tr khc nhau ca A, B v c in, quan st cc n hin th.

4. Th nghim 2.4:

Thc hin mch cng 2 s BCD. Ng vo ca mch l 2 s A, B v ng vo cho s nh c in . Ng ra l s BCD

tng S1 S0 v s nh c out.

Cc bc cn thc hin:

1. To project mi cho mch cng s BCD. Phi thc hin mch cng 2 s 4 bit A, B (th nghim 2.3)

v 1 mch chuyn i 5 bit tng s3s2s1s0co thnh 2 s BCD S1 S0 (th nghim 2.2)

2. Vit chng trnh Verilog:

Ni cc ng vo A, B v cin vi cc cng tc tng ng SW74 , SW 30 v SW8 v vi cc

n LED mu LEDR70

Ni cc ng ra c out v S vi cc n LED mu xanh LEDG40

Dng cc n 7 on HEX3, HEX2 hin th gi tr ca 2 s A v B v HEX1, HEX0 hin

th kt qu S1 S0 .

3.

4.

Gn chn, bin dch v np project vo kit TN

Th mch bng cch thay i cc gi tr khc nhau ca A, B v c in, quan st cc n hin th.

5. Th nghim 2.5:

Thit k mch t hp chuyn i 1 s nh phn 6 bit thnh s thp phn di dng 2 s BCD. Dng cc cng tc

SW 50 nhp s nh phn v cc n 7 on HEX1 v HEX0 hin th s thp phn.

24

TN KTS-Altera DE1 B mn in T - HBK Tp HCM

Bi th nghim 3

Latches, Flip-flops, Registers

1. Th nghim 3.1:

Hnh 1 m t mch RS latch dng cng logic.

C 2 cch dng Verilog m t mch ny: dng cng logic (hnh 2a) v dng cng thc logic (hnh 2b).

R

R_g

Qa (Q)

Clk

Qb

S_g

Hnh 1. Mch RS latch dng cng logic.

// A gated RS latch

module part1 (Clk, R, S, Q);

input Clk, R, S;

output Q;

wire R_g, S_g, Qa, Qb /* synthesis keep */ ;

and (R_g, R, Clk);

and (S_g, S, Clk);

nor (Qa, R_g, Qb);

nor (Qb, S_g, Qa);

assign Q = Qa;

endmodule

Hnh 2a. Dng cng logic m t mch RS latch.

// A gated RS latch

module part1 (Clk, R, S, Q);

input Clk, R, S;

output Q;

wire R_g, S_g, Qa, Qb /* synthesis keep */ ;

assign R_g = R & Clk;

assign S_g = S & Clk;

assign Qa = (R_g Qb);

assign Qb = (S_g Qa);

assign Q = Qa;

endmodule

Hnh 2b. Dng cng thc logic m t mch RS latch.

25

TN KTS-Altera DE1 B mn in T - HBK Tp HCM

C 2 cch thc hn: dng 1 LUT 4 ng vo (hnh 3a) v dng 4 LUT 2 ng vo (hnh 3b).

R

Qa (Q)

Clk

4-LUT

(a) RS latch ch dng 1 bng tham chiu 4 ng vo.

R_g

Qa (Q)

4-LUT

4-LUT

Clk

S_g

4-LUT

4-LUT

Qb

(b) RS latch dng 4 bng tham chiu 2 ng vo.

Hnh 3. Cc cch thc hin mch RS latch

Cc bc cn thc hin:

1.

2.

3.

4.

To project RS latch

Vit chng trnh Verilog theo hai cch 2a v 2b.

Bin dch. Dng tin ch RTL Viewer so snh vi s mch hnh 1. Dng tin ch Technology

Viewer so snh vi s mch hnh 3b.

To Vector Waveform File (.vwf) cho cc ng vo/ra. To dng sng cho cc ng vo R v S ri

dng tin ch Quartus II Simulator quan st cc dng sng R_g, S_g, Qa v Qb

26

TN KTS-Altera DE1 B mn in T - HBK Tp HCM

2. Th nghim 3.2:

Cho mch D latch dng cng nh hnh 4.

D

S_g

Qa (Q)

Clk

Qb

R_g

Hnh 4. Mch D latch dng cng logic.

Cc bc cn thc hin:

1.

2.

3.

4.

5.

6.

To project mi vi chng trnh Verilog dng 2b cho mch D latch.

Bin dch chng trnh. Dng tin ch Technology Viewer kho st mch.

M phng kim tra hot ng ca mch.

Dng cng tc SW0 cho ng vo D, v SW1 cho ng vo Clk. Ni ng ra Q n LEDR 0 .

Bin dch chng trnh li v np project vo kit TN.

Th mch bng cch thay i cc ng vo D, Clk v quan st ng ra Q.

27

TN KTS-Altera DE1 B mn in T - HBK Tp HCM

3. Th nghim 3.3:

Cho mch master-slave D flip-flop hnh 5.

Master

D

Clock

Slave

Qm

Clk Q

Clk Q

Qs

Q

Q

Hnh 5. Mch master-slave D flip-flop.

Cc bc cn thc hin:

1.

2.

3.

4.

5.

To project mi dng 2 D flip-flop ca th nghim 3.2.

Dng cng tc SW 0 cho ng vo D, v SW 1 cho ng vo Clk. Ni ng ra Q n LEDR 0 .

Bin dch chng trnh.

Dng tin ch Technology Viewer kho st mch. M phng kim tra hot ng ca mch.

Th mch bng cch thay i cc ng vo D, Clk v quan st ng ra Q.

4. Th nghim 3.4:

Cho mch in hnh 6 vi D latch, D flip- flop kck cnh ln v D flip- flop kck cnh xung.

28

TN KTS-Altera DE1 B mn in T - HBK Tp HCM

D

Clock

Qa

Clk Q

Qa

Qb

Qb

Qc

Qc

(a) S mch

Clock

D

Qa

Qb

Qc

(b) Gin d thi gian

Hnh 6. S mch v dng sng ca th nghim 3.4.

Cc bc cn thc hin:

1.

2.

3.

4.

5.

To project mi.

Vit chng trnh da trn on chng trnh gi nh hnh 7.

Bin dch chng trnh.

Dng tin ch Technology Viewer kho st mch.

M phng kim tra hot ng ca mch. So snh hot ng ca cc phn t trong mch.

module D_latch (D, Clk, Q);

input D, Clk;

output reg Q;

always @ (D, Clk)

if (Clk)

Q = D;

endmodule

Hnh 7. Chng trnh gi cho D latch.

29

TN KTS-Altera DE1 B mn in T - HBK Tp HCM

Bi th nghim 4

Counters

1. Th nghim 4.1:

Cho mch m ng b 4 bit dng 4 T flip-flops nh hnh 1.

Enable

Clock

Q

Q

Clear

Hnh 1. B m 4 bit.

Cc bc cn thc hin:

1. To project mi thc hin b m 16 bit dng 4 mch m nh hnh 1. Bin dch chng trnh. Ghi nhn

s phn t logic (LEs) c dng? Tn s hot ng ti a (Fmax) ca mch m l bao nhiu?

2. M phng hot ng ca mch.

3. Gn thm nt nhn KEY0 lm ng vo Clock, cc cng tc SW 1, SW0 lm ng vo Enable, Reset v cc

n 7 on HEX3-0 hin th gi tr thp lc phn ca ng ra mch m.

4. Bin dch li v np project vo kit TN.

5. Th hot ng ca mch bng cch thay i cc cng tc v quan st cc n 7 on.

6. Thc hin mch m 4 bit ri dng tin ch RTL Viewer quan st mch v so snh vi mch in hnh 1.

2. Th nghim 4.2:

Thc hin li th nghim 4.1 dng m Verilog sau:

Q <= Q + 1;

Bin dch chng trnh.

So snh s phn t logic (LEs) c dng, tn s hot ng ti a (Fmax) ca mch m.

Dng RTL Viewer kho st v nhn xt nhng khc bit so vi th nghim 4.1.

30

TN KTS-Altera DE2 B mn in T - HBK Tp HCM

3. Th nghim 4.3:

Dng module c sn trong th vin LPM (Library of Parameterized Modules) thc hin mch m 16 bit.

Thay i LPM cho ph hp, nh Enable, Reset.

4. Th nghim 4.4:

Thc hin mch ng h m giy t 0 n 9s hin th trn n 7 on HEX 0.

Phi thc hin 1 mch m to thi gian 1s t xung clock 50 MHz c sn trn kit TN.

5. Th nghim 4.5:

Thc hin mch hin th ch HELLO ln 4 n 7 on HEX 3 0, dch t phi sang tri vi thi khong 1s

theo mu nh bng 1.

Clock cycle

0

1

2

3

4

5

6

7

8

...

Displayed pattern

H

E

L

L

O

H

E

L

L

O

H

E

L

L

O

H

E

L

L

O

H

and so on

Bng 1. n ch chy HELLO.

31

Anda mungkin juga menyukai

- Lab2 - Continuous AssignmentDokumen6 halamanLab2 - Continuous AssignmentĐông HưngBelum ada peringkat

- đếm lên 0 9 và ngược lạiDokumen18 halamanđếm lên 0 9 và ngược lạiBảo Kỳ NguyễnBelum ada peringkat

- Lab 3 OverviewDokumen9 halamanLab 3 OverviewquynhthomBelum ada peringkat

- Lab3 - Procedural Assignment - Counter, TimerDokumen8 halamanLab3 - Procedural Assignment - Counter, TimerĐông HưngBelum ada peringkat

- TN DSP-2015-01-18-SinhVienDokumen94 halamanTN DSP-2015-01-18-SinhVienNhật DuyBelum ada peringkat

- Bao Cao TKHTSDokumen55 halamanBao Cao TKHTSdinvd777Belum ada peringkat

- Thiết kế IC đồng hồ sốDokumen56 halamanThiết kế IC đồng hồ sốHà GiangBelum ada peringkat

- Huong Dan Su Dung QuartusDokumen52 halamanHuong Dan Su Dung QuartusthothaiBelum ada peringkat

- THIẾT KẾ THIẾT BỊ THỰC HÀNH VI XỬ LÝ DLAB8051Dokumen8 halamanTHIẾT KẾ THIẾT BỊ THỰC HÀNH VI XỬ LÝ DLAB8051phamvanha0804Belum ada peringkat

- Lab1 - Huong Dan Thiet Ke Verilog Tren Quartus IIDokumen16 halamanLab1 - Huong Dan Thiet Ke Verilog Tren Quartus IITrí Nguyễn HữuBelum ada peringkat

- B1 GIỚI THIỆU KIT DSP - MATLABDokumen22 halamanB1 GIỚI THIỆU KIT DSP - MATLABluong trinh ducBelum ada peringkat

- Quartus II TutorialDokumen32 halamanQuartus II TutorialThuận Lê VănBelum ada peringkat

- New Project TutorialDokumen32 halamanNew Project TutorialThuận Lê VănBelum ada peringkat

- Lab1 ADokumen9 halamanLab1 ALương Quốc ToảnBelum ada peringkat

- Prelab 1Dokumen4 halamanPrelab 1DuyBelum ada peringkat

- Huong Dan Thiet Ke Mach So Dung VivadoDokumen26 halamanHuong Dan Thiet Ke Mach So Dung VivadoHùng Sơn Trương100% (2)

- Bao Cao Thuc Hanh Vi Dieu KhienDokumen19 halamanBao Cao Thuc Hanh Vi Dieu KhienĐạt Nguyễn HữuBelum ada peringkat

- Thực hành Kỹ thuật vi xử lý- PHẦN 1Dokumen53 halamanThực hành Kỹ thuật vi xử lý- PHẦN 1Văn Minh VũBelum ada peringkat

- Huong Dan Hoc Revit MEP 2013Dokumen229 halamanHuong Dan Hoc Revit MEP 2013Tuan Nguyen100% (1)

- Chapter 3Dokumen45 halamanChapter 3Lâm Phú VinhBelum ada peringkat

- Huong Dan Su Dung Phan Mem Reads51Dokumen4 halamanHuong Dan Su Dung Phan Mem Reads51ducanhbkbkBelum ada peringkat

- Hướng dẫn sử dụng Quartus II để thiết kế mạchDokumen12 halamanHướng dẫn sử dụng Quartus II để thiết kế mạchstylesboy89Belum ada peringkat

- Lab 2 - 6 - 7Dokumen26 halamanLab 2 - 6 - 7Quang HưngBelum ada peringkat

- Lab 1Dokumen8 halamanLab 1Hoàng ThắngBelum ada peringkat

- Thiết kế chế tạo mạch đo và hiển thị cường độ từ trường trên LCDDokumen29 halamanThiết kế chế tạo mạch đo và hiển thị cường độ từ trường trên LCDThanhha NguyenBelum ada peringkat

- TNVDK01 - Input-Output-7SegmentLED - 29.09.2021Dokumen6 halamanTNVDK01 - Input-Output-7SegmentLED - 29.09.2021Tam PhamBelum ada peringkat

- Bao Cao Thuc Tap Tot Nghiep SPKTDokumen21 halamanBao Cao Thuc Tap Tot Nghiep SPKTTruong Trong TinBelum ada peringkat

- TNKTS Lab4Dokumen14 halamanTNKTS Lab4Lyo KraqBelum ada peringkat

- TNKTS - LAB3 đã chuyển đổiDokumen14 halamanTNKTS - LAB3 đã chuyển đổiNam Phong Mai NguyễnBelum ada peringkat

- Code VerilogDokumen28 halamanCode VerilogHuỳnh Thanh DưBelum ada peringkat

- LAB0 HomeDokumen9 halamanLAB0 Homebảo long Phạm hoàngBelum ada peringkat

- Huong Dan Su Dung Quartus II de Thiet Ke MachDokumen5 halamanHuong Dan Su Dung Quartus II de Thiet Ke MachHue BuiBelum ada peringkat

- Thuc Hanh Ky Thuat Truyen So LieuDokumen27 halamanThuc Hanh Ky Thuat Truyen So LieuphuongltbkBelum ada peringkat

- Đồ án Vẽ mạch và thiết kế mạch in hiển thị LED 7Dokumen19 halamanĐồ án Vẽ mạch và thiết kế mạch in hiển thị LED 7leduythangepuBelum ada peringkat

- (713612) Lê Bảo Ngọc-20182390-Báo - cáo - thực - tập - cơ - bản - kì - 20211Dokumen28 halaman(713612) Lê Bảo Ngọc-20182390-Báo - cáo - thực - tập - cơ - bản - kì - 20211Bảo Ngọc LêBelum ada peringkat

- In 2 Mặt - 9 BảnDokumen37 halamanIn 2 Mặt - 9 BảndothanhdattvqBelum ada peringkat

- Tai Lieu Huong Dan Thuc Hanh Lap Trinh Ghep Noi May TinhDokumen29 halamanTai Lieu Huong Dan Thuc Hanh Lap Trinh Ghep Noi May TinhĐức TạBelum ada peringkat

- Báo Cáo TH C Hành Thông Tin QuangDokumen17 halamanBáo Cáo TH C Hành Thông Tin QuangPhong Lê ThanhBelum ada peringkat

- Thiet Ke He Thong Hvac Voi Revit Mep UpdateDokumen38 halamanThiet Ke He Thong Hvac Voi Revit Mep Updatent_long76Belum ada peringkat

- Thiet Ke He Thong Hvac Voi Revit MepDokumen38 halamanThiet Ke He Thong Hvac Voi Revit MepTrungHiếuLêBelum ada peringkat

- Ulysse-Quick Light PDFDokumen59 halamanUlysse-Quick Light PDFDương Tấn Quốc100% (1)

- LedimmPro Vs LedimmDokumen1 halamanLedimmPro Vs LedimmDương Tấn QuốcBelum ada peringkat

- LedimmPro Vs LedimmDokumen1 halamanLedimmPro Vs LedimmDương Tấn QuốcBelum ada peringkat

- 6th Central Pay Commission Salary CalculatorDokumen15 halaman6th Central Pay Commission Salary Calculatorrakhonde100% (436)