Lecture 8 - Gate-Level Delay Estimation

Diunggah oleh

Bala Krishna0 penilaian0% menganggap dokumen ini bermanfaat (0 suara)

15 tayangan40 halamankjjdfngjnlfsnlnvlk

Judul Asli

Lecture08 Delay

Hak Cipta

© © All Rights Reserved

Format Tersedia

PDF, TXT atau baca online dari Scribd

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen Inikjjdfngjnlfsnlnvlk

Hak Cipta:

© All Rights Reserved

Format Tersedia

Unduh sebagai PDF, TXT atau baca online dari Scribd

0 penilaian0% menganggap dokumen ini bermanfaat (0 suara)

15 tayangan40 halamanLecture 8 - Gate-Level Delay Estimation

Diunggah oleh

Bala Krishnakjjdfngjnlfsnlnvlk

Hak Cipta:

© All Rights Reserved

Format Tersedia

Unduh sebagai PDF, TXT atau baca online dari Scribd

Anda di halaman 1dari 40

Lecture 8 ECE 425

Lecture 8 -- Gate-level Delay Estimation

Lecture 8 ECE 425

Outline

Estimating delay of single gates and multi-gate circuits

Lecture 8 ECE 425

Talking About Delays

Three common measurements of gate performance:

Delay time (t

d

or t

pd

) -- Delay between when the input

signal to a gate reaches the 50% point and when the

output signal reaches the 50% point.

Rise time (t

r

) -- time it takes for a signal to go from 10% to

90% of its output range

Fall time (t

f

) -- time it takes for a signal to go from 90% to

10% of its output range

Lecture 8 ECE 425

Pictorial View

Lecture 8 ECE 425

Why do we care?

Its pretty obvious why we care about gate delay, in that

we like circuits to go fast

Rise/fall times matter for a number of reasons

Theyre a component of total gate delay

While the inputs to a gate are rising or falling, a

conductive path exists between power and ground

Power dissipation

Can potentially harm the chip if too much current

flows

For signals that have high inductance, overly short

rise/fall times can lead to di/dt-induced swings

Mostly relevant on chip I/O pins

Lecture 8 ECE 425

Estimating Delay

Gate delays are determined by how quickly the driving

gate can charge/discharge its load capacitance

Lecture 8 ECE 425

Estimating Delay

Gate delay may vary depending on which inputs are

changing -- generally use the worst case

Lecture 8 ECE 425

General Approach

Divide circuit into DC-connected components, solve for

each component

Lecture 8 ECE 425

Fall Time Analysis

During the fall time one or more nMOS transistors

discharge the energy stored in the output capacitance

Lecture 8 ECE 425

Fall Time Analysis

During the fall time, the nMOS transistor starts in the

saturated region and passes into the linear region

Lecture 8 ECE 425

Fall Time Analysis

Divide fall time into two components: t

f,sat

and t

f,linear

In saturation, current through the transistor is constant

Lecture 8 ECE 425

Fall Time

This becomes

Define t

1

, t

2

such that V

o

(t

1

) = 0.9V

dd

and V

o

(t2) = V

dd

- V

t

.

Then,

And t

f, sat

is:

Lecture 8 ECE 425

Fall Time

In the linear region, current through the transistor

depends on V

o

And t

f, linear

becomes

Lecture 8 ECE 425

Fall Time

Integrating, we get t

f, linear

=

And

For many processes, V

t

~= 0.2V

dd

, allowing us to

approximate

Lecture 8 ECE 425

Rise Time

Redoing the same analysis for the pMOS transistor in pull-

up gives

Note that beta for pMOS tends to be about 1/2 beta for

nMOS given equivalent size devices, so typically want

pMOS about twice as wide as nMOS to get equivalent

rise and fall times

Lecture 8 ECE 425

Gate Delay Estimation

Somewhat more complicated -- depends on rise and fall

times of the input signals.

Assuming (unrealistically) that the input rises or falls in

zero time, then the gate delay can be approximated as

half of the rise or fall time for the gate, and averaged to

Since gates are generally driven by other gates, we need

a better approximation for real circuits

Could just simulate the design, but that wouldnt give

much insight

Simulation is good for verifying that something works

the way you want but not for designing it to do so

Lecture 8 ECE 425

Circuit Delay Estimation

1. Divide circuit into DC-connected blocks as we talked

about at the start of lecture.

2. Compute a simple delay model for each block

3. Add the delays for each block to get overall delay.

In CMOS, a DC-connected block (stage) will be either:

1. A single logic gate

2. A transmission-gate network and the gates driving it

In the simple case, a block switches in response to a single

signal changing at one of its inputs, called the trigger

signal

Lecture 8 ECE 425

Making the System Tractable

As weve seen, solving even simple transistor networks

analytically requires solving differential equations that

change at region boundaries

For example, the rise and fall time derivations we

presented really only apply for inverters, and

computing them for larger gates is more complex

Now think about doing that for a 100-transistor

network, much less anything bigger

Solution: linearize the transistor equations by replacing

each transistor with an equivalent resistor, R

eff

Lecture 8 ECE 425

Computing R

eff

R

eff

for a transistor depends on what region its operating

in

Example: R

eff

= dV

ds

/dI

ds

= infinity in saturation

In linear region,

During switching, a transistor travels through different

regions of operation

We want a single R

eff

that approximates the behavior of a

transistor during the entire rise/fall time

R

eff

will be different depending on whether the

transistor is transmitting a zero or a one.

Lecture 8 ECE 425

Case One -- nMOS Transistor, Logic 0

nMOS transistor, discharging capacitor to ground

Lecture 8 ECE 425

nMOS Transistor, Logic 0

Want to model as a single network with R

eff

, C

Choose R

eff

so that both circuits have the same fall time

Lecture 8 ECE 425

nMOS Transistor, Logic 1

Back to the I-V curve

Lecture 8 ECE 425

nMOS Transistor, Logic 1

Problem: V

O

never makes it to 0.9 V

dd

in this case,

assuming V

t

= 0.2V

dd

, so cant try to match the full rise

time

If we try to match the time it takes to hit 0.5V

dd

, we get

Note that this is about 3x larger than the discharging

case. Why does this make sense?

Lecture 8 ECE 425

pMOS Transistors

Lecture 8 ECE 425

Estimating Stage Delay

Need to decide whether each transistor is off, transmitting

a logic 0, or transmitting a logic 1.

Then, can replace the stage with an RC network

Lecture 8 ECE 425

Estimating Stage Delay

This is still too complex -- solving these networks exactly

requires solving several simultaneous differential

equations.

Simplify further by reducing to an equivalent single-RC

network with time constant

Lecture 8 ECE 425

Example of the Process

Lecture 8 ECE 425

Estimating Stage Delay

At most one node should be the input node to the stage,

corresponding to either V

dd

or V

ss

Generally, were interested in the delay at a specific

output node

Question: how to compute R

eq

and C

eq

?

When the RC-network is a tree (no loops), there is a good

estimate that is also easy to compute.

This estimate of is called the Elmore Time

Constant

Lecture 8 ECE 425

Estimating the Stage delay

1. Identify an input node and an output node, and the

unique path between them. Call the path P

2. For every node n in the tree other than the input node

1. Identify the unique path between the input node and n

2. Identify the sub-path that is the intersection of this

path and P

3. Sum the resistances along the sub-path, call it R

n

4. If Cn is the capacitance at n, create a !

n

= R

n

C

n

3. Sum the !

n to get

!

eq

for the network

4. Given !

eq

, can select R

eq

and C

eq

values to match, but

generally dont need to, !

eq

is enough

Lecture 8 ECE 425

Example

Lecture 8 ECE 425

Example

Lecture 8 ECE 425

One Note

If a node n is already at the voltage it will have after the

transition, set !

n

= 0, since the node will not be charging

or discharging

Example:

Lecture 8 ECE 425

Cascade of Stages

Suppose stage 1 feeds stage 2

If the time constant of stage 1 is !

1

, when is stage 2

triggered? (I.e., when does it start switching)

Time for yet another approximation

Lecture 8 ECE 425

Cascade of Stages

By convention, assume that stage 2 is triggered when the

output of stage 1 has completed 90% of its logic swing

and is thus well within V

t

of one of the rails

Thus, the delay through stage 1 is

Thus, if stage 1 triggers at time 0, stage 2 triggers at time

2.3 !

1

, stage 3 triggers at time 2.3 !

1

+ 2.3 !

2

, etc.

Lecture 8 ECE 425

Interconnect Delay

Interconnect delay can be a big issue, particularly for

systems larger than a few gates

Interconnect delay is a function of interconnect length

To be fully accurate, youd treat interconnects as

transmission lines and analyze them that way

Were not going to do that, surprise surprise

Lecture 8 ECE 425

Interconnect Delay

Instead, break long lines into lumped RC-segments

Lecture 8 ECE 425

Interconnect Delay

Lecture 8 ECE 425

Interconnect Delay

Lecture 8 ECE 425

Rules of Thumb

Formally, lowest delay of an interconnect occurs when the

delay of each wire segment equals the delay of the buffer

With this model, interconnect delays become linear, not

quadratic

Lecture 8 ECE 425

Next Time

Logical effort: a way of making circuits fast, not just

knowing how slow they are.

Anda mungkin juga menyukai

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Dari EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Belum ada peringkat

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Dari EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Penilaian: 2.5 dari 5 bintang2.5/5 (3)

- Power Distribution and Clock Design: R. Saleh Dept. of ECE University of British Columbia Res@ece - Ubc.caDokumen55 halamanPower Distribution and Clock Design: R. Saleh Dept. of ECE University of British Columbia Res@ece - Ubc.caSiva RaoBelum ada peringkat

- BJT Switching CircuitsDokumen48 halamanBJT Switching CircuitsMohammad Gulam AhamadBelum ada peringkat

- Ky 96a PDFDokumen237 halamanKy 96a PDFMauri VillarBelum ada peringkat

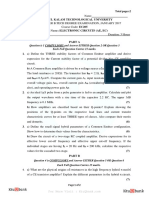

- DVD2 JNTU Set1 SolutionsDokumen12 halamanDVD2 JNTU Set1 Solutionsకిరణ్ కుమార్ పగడాలBelum ada peringkat

- Microprocessor System Design: A Practical IntroductionDari EverandMicroprocessor System Design: A Practical IntroductionBelum ada peringkat

- DE-2-India BixDokumen17 halamanDE-2-India BixbhagBelum ada peringkat

- Module 3Dokumen25 halamanModule 3Sushanth M100% (3)

- Physical DesignDokumen45 halamanPhysical DesignMalka RavikrishnaBelum ada peringkat

- ANUE SCENARIOS Heynen Mobile BackhaulDokumen29 halamanANUE SCENARIOS Heynen Mobile BackhaulJoao HortaBelum ada peringkat

- Lecture24 Clock Power RoutingDokumen30 halamanLecture24 Clock Power Routingapi-3834272100% (1)

- Clock and SynchronizationDokumen99 halamanClock and SynchronizationpawanzBelum ada peringkat

- VLSI TimingDokumen23 halamanVLSI TimingAhmed ZЗzЗBelum ada peringkat

- Physical DesignDokumen45 halamanPhysical DesignSameer Badachi100% (10)

- SOC Unit 1 Part2Dokumen24 halamanSOC Unit 1 Part2Karthick NpBelum ada peringkat

- Ee 587 Soc Design & Test: Partha Pande School of Eecs Washington State University Pande@Eecs - Wsu.EduDokumen41 halamanEe 587 Soc Design & Test: Partha Pande School of Eecs Washington State University Pande@Eecs - Wsu.EduRanganadh MvBelum ada peringkat

- Revisit: Resistance and Capacitance MOSFET Model For Digital CircuitsDokumen33 halamanRevisit: Resistance and Capacitance MOSFET Model For Digital Circuitsdilshan singhBelum ada peringkat

- ELECH409 Th05Dokumen57 halamanELECH409 Th05hung kungBelum ada peringkat

- EE 115C Lect 4B DelayDokumen9 halamanEE 115C Lect 4B DelaypchengoesBelum ada peringkat

- Lecture06 LatchesDokumen30 halamanLecture06 LatchesBala KrishnaBelum ada peringkat

- VLSI Physical Design Automation: Clock and Power RoutingDokumen30 halamanVLSI Physical Design Automation: Clock and Power RoutingmaheshasicBelum ada peringkat

- What Are The Different Clocking Strategies Employed in VLSI System ? Discuss H-Tree' Clock Distribution in High Density CMOS Circuits ? AnsDokumen6 halamanWhat Are The Different Clocking Strategies Employed in VLSI System ? Discuss H-Tree' Clock Distribution in High Density CMOS Circuits ? AnsTozammel Hossain TusharBelum ada peringkat

- SRM Institute of Science and TechnologyDokumen8 halamanSRM Institute of Science and TechnologyRaskshanna100% (1)

- Vlsi Module-3Dokumen129 halamanVlsi Module-3Phanindra ReddyBelum ada peringkat

- Vlsi Final Notes Unit4Dokumen21 halamanVlsi Final Notes Unit4RohitParjapatBelum ada peringkat

- Transistor Level Logic Cmos vs. TTLDokumen33 halamanTransistor Level Logic Cmos vs. TTLChris Louie YalungBelum ada peringkat

- Clock Distribution Networks in Processors and Clock Skew: Aayush Goel, 2010CS10201, IIT DelhiDokumen4 halamanClock Distribution Networks in Processors and Clock Skew: Aayush Goel, 2010CS10201, IIT DelhiAayush GoelBelum ada peringkat

- InverterDokumen231 halamanInverterMaitrik Shah100% (1)

- Delay: Minimum Time From The Input Crossing 50% To The OutputDokumen12 halamanDelay: Minimum Time From The Input Crossing 50% To The Outputakash bhumiBelum ada peringkat

- Project Report of Robot 5 Semester Electronics: Sir Syed University of Engineering and TechnologyDokumen16 halamanProject Report of Robot 5 Semester Electronics: Sir Syed University of Engineering and TechnologyFaraz Ali KhanBelum ada peringkat

- Lecture 9 - CMOS Delay IDokumen28 halamanLecture 9 - CMOS Delay IWambi DanielcollinsBelum ada peringkat

- Digital Electronics: Logic Gates: Using TTLDokumen10 halamanDigital Electronics: Logic Gates: Using TTLfarukBelum ada peringkat

- CHAPTER 4 ElectronicsDokumen47 halamanCHAPTER 4 ElectronicsrenuBelum ada peringkat

- Practical 4Dokumen4 halamanPractical 4sbekezelomenzi19Belum ada peringkat

- Chapter 6 BDokumen22 halamanChapter 6 BSuraj KumarBelum ada peringkat

- Lecture07 Capacitance ResistanceDokumen44 halamanLecture07 Capacitance ResistanceMd MianBelum ada peringkat

- EE215 Lab4Dokumen7 halamanEE215 Lab4Lynn FranklinBelum ada peringkat

- ClocksDokumen4 halamanClocksluizcpimentaBelum ada peringkat

- RealDigital Module 8Dokumen7 halamanRealDigital Module 8Sidney O. EbotBelum ada peringkat

- ECE429 Laboratory 2 Inverter Schematic: Prasanna Nalawar A20489739 21/09/2021Dokumen14 halamanECE429 Laboratory 2 Inverter Schematic: Prasanna Nalawar A20489739 21/09/2021Prasanna NalawarBelum ada peringkat

- Unit 2Dokumen26 halamanUnit 2viren mallyaBelum ada peringkat

- ECE429 Laboratory 3 Inverter Layout: Prasanna N A20489739 21/09/2021Dokumen14 halamanECE429 Laboratory 3 Inverter Layout: Prasanna N A20489739 21/09/2021Prasanna NalawarBelum ada peringkat

- Evolution of Latches and Flip-Flops-1Dokumen24 halamanEvolution of Latches and Flip-Flops-1Ravi ThejaBelum ada peringkat

- ECE429 Laboratory 4 NAND Schematic: Bapu A20489420 21/09/2021Dokumen14 halamanECE429 Laboratory 4 NAND Schematic: Bapu A20489420 21/09/2021Prasanna NalawarBelum ada peringkat

- Week 9 - Module 8 TimingDokumen7 halamanWeek 9 - Module 8 TimingBen GwenBelum ada peringkat

- Plasma DiagnosticsDokumen28 halamanPlasma DiagnosticsRiddhesh PatelBelum ada peringkat

- CMOS PrepdfDokumen3 halamanCMOS Prepdfmingzhen1020Belum ada peringkat

- Le Nguyen Thai Ha Test 19-05-2021: 1. Why CMOS Structure Always Pull-Up PMOS and Pull-Down NMOS, Not Reverse?Dokumen17 halamanLe Nguyen Thai Ha Test 19-05-2021: 1. Why CMOS Structure Always Pull-Up PMOS and Pull-Down NMOS, Not Reverse?emaBelum ada peringkat

- Digital Logic and System Design: Assignment - Ii Name-Prasant Agarwal Roll No - CS16BCAGN006 Standard - BCA 2 SemesterDokumen16 halamanDigital Logic and System Design: Assignment - Ii Name-Prasant Agarwal Roll No - CS16BCAGN006 Standard - BCA 2 SemesterSakil AhmedBelum ada peringkat

- Homework Assignment 12: SolutionDokumen7 halamanHomework Assignment 12: SolutionTarik ZiadBelum ada peringkat

- WatimetroDokumen11 halamanWatimetroLuis Enrique Castillejo GonzalesBelum ada peringkat

- Step Response of RC Circuits 1. Objectives: BEE 233 Laboratory-2Dokumen7 halamanStep Response of RC Circuits 1. Objectives: BEE 233 Laboratory-2Marib SirajBelum ada peringkat

- Ell 100 Lab Submission: Time Constant of A RC Circuit and Step Response of RLC CircuitDokumen25 halamanEll 100 Lab Submission: Time Constant of A RC Circuit and Step Response of RLC CircuitmaheshBelum ada peringkat

- Chapter HazardDokumen44 halamanChapter HazardDƯƠNG NGUYỄN THÁI BÌNHBelum ada peringkat

- Decoder2001 Armatur HorowitzDokumen10 halamanDecoder2001 Armatur HorowitzNK NKBelum ada peringkat

- Digital Integrated CircuitsDokumen27 halamanDigital Integrated CircuitsShivakumar 2108Belum ada peringkat

- IEEE Presentation On Properties of Digital Switching Currents (C'MOS)Dokumen21 halamanIEEE Presentation On Properties of Digital Switching Currents (C'MOS)Trivendra JoshiBelum ada peringkat

- Performance Characterization PDFDokumen46 halamanPerformance Characterization PDFSankalp JainBelum ada peringkat

- CMOS Logic DesignDokumen35 halamanCMOS Logic DesignsomosreeBelum ada peringkat

- University of California, Berkeley College of Engineering Department of Electrical Engineering and Computer Sciences Elad Alon Homework #4 EECS141Dokumen2 halamanUniversity of California, Berkeley College of Engineering Department of Electrical Engineering and Computer Sciences Elad Alon Homework #4 EECS141Vidhya DsBelum ada peringkat

- Dioda AplicationDokumen5 halamanDioda AplicationRahmatbasukiBelum ada peringkat

- Parte2 - Clase03 - Analog View of Digital SignalsDokumen63 halamanParte2 - Clase03 - Analog View of Digital SignalsBala KrishnaBelum ada peringkat

- Lecture16 MemoriasDokumen35 halamanLecture16 MemoriasBala KrishnaBelum ada peringkat

- Lecture14 ALUDokumen26 halamanLecture14 ALUBala KrishnaBelum ada peringkat

- MultiplicationDokumen15 halamanMultiplicationTi I âu PiBelum ada peringkat

- Parte2 Clase04 ADC DCADokumen56 halamanParte2 Clase04 ADC DCABala KrishnaBelum ada peringkat

- Lecture13 AddersDokumen48 halamanLecture13 Addersnguyenbinh12xBelum ada peringkat

- Lecture12 DynamicDokumen22 halamanLecture12 Dynamicarun.sunaniya8701Belum ada peringkat

- Lecture09 Performance 01Dokumen33 halamanLecture09 Performance 01Bala KrishnaBelum ada peringkat

- Lecture09 Performance 01Dokumen33 halamanLecture09 Performance 01Bala KrishnaBelum ada peringkat

- Power Dissipation: Modified From "Digital Integrated Circuits", by J. Rabaey, A. Chandrakasan and B. NikolicDokumen14 halamanPower Dissipation: Modified From "Digital Integrated Circuits", by J. Rabaey, A. Chandrakasan and B. NikolicBala KrishnaBelum ada peringkat

- Lecture10 Power ConsumptionDokumen14 halamanLecture10 Power ConsumptionBala KrishnaBelum ada peringkat

- Lecture06 LatchesDokumen30 halamanLecture06 LatchesBala KrishnaBelum ada peringkat

- Lecture 5 - Gate-Level LayoutDokumen23 halamanLecture 5 - Gate-Level LayoutspvenuBelum ada peringkat

- EulaDokumen2 halamanEulaChad SchroederBelum ada peringkat

- Lecture07 Capacitance ResistanceDokumen44 halamanLecture07 Capacitance ResistanceMd MianBelum ada peringkat

- Lecture04 FabricationDokumen21 halamanLecture04 FabricationBala KrishnaBelum ada peringkat

- Lecture02 InverterDokumen20 halamanLecture02 InverterBala KrishnaBelum ada peringkat

- Win Configure Updated Title "Recommended Settings Updated"Dokumen2 halamanWin Configure Updated Title "Recommended Settings Updated"dams6797Belum ada peringkat

- Lecture03 Static CMOSDokumen24 halamanLecture03 Static CMOSBala KrishnaBelum ada peringkat

- Eee CombinedDokumen89 halamanEee CombinedBala KrishnaBelum ada peringkat

- Win Configure Updated Title "Recommended Settings Updated"Dokumen2 halamanWin Configure Updated Title "Recommended Settings Updated"dams6797Belum ada peringkat

- COD4 ManualDokumen18 halamanCOD4 Manualfastback82Belum ada peringkat

- Videocon ProjectDokumen58 halamanVideocon Projectmrinal_kakkar8215100% (2)

- Linear DielctricsDokumen6 halamanLinear DielctricsBala KrishnaBelum ada peringkat

- Pilani Campus: Birla Institute of Techonology and Science, PilaniDokumen3 halamanPilani Campus: Birla Institute of Techonology and Science, PilaniBala KrishnaBelum ada peringkat

- Win Configure Updated Title "Recommended Settings Updated"Dokumen2 halamanWin Configure Updated Title "Recommended Settings Updated"dams6797Belum ada peringkat

- Lecture16 PDFDokumen32 halamanLecture16 PDFBaphelele MnisiBelum ada peringkat

- LIC UNIT 3 Notes 3.4.2021Dokumen94 halamanLIC UNIT 3 Notes 3.4.2021lyrixxopedia100% (1)

- Introduction 3-12-86Dokumen13 halamanIntroduction 3-12-86Roshdy AbdelRassoulBelum ada peringkat

- Layout and Stick DiagramDokumen70 halamanLayout and Stick DiagramAMRUTHWAR SWAROOPABelum ada peringkat

- Description Features: PT4452 PLL-based OOK/ASK/FSK Transmitter ICDokumen4 halamanDescription Features: PT4452 PLL-based OOK/ASK/FSK Transmitter ICSamerBelum ada peringkat

- CO-PO Analog ElectronicsDokumen3 halamanCO-PO Analog ElectronicsPrabhu KumarBelum ada peringkat

- KTU EC205 ELECTRONIC CIRCUITS (AE, EC) - MAin - Jan - 2017 - Ktu Qbank-MergedDokumen16 halamanKTU EC205 ELECTRONIC CIRCUITS (AE, EC) - MAin - Jan - 2017 - Ktu Qbank-MergedsunBelum ada peringkat

- PHYSICSDokumen15 halamanPHYSICSdr. putul mahantaBelum ada peringkat

- The Depletion LoadDokumen5 halamanThe Depletion LoadVidhya DsBelum ada peringkat

- ECE 209 Homework #2 Solutions: R L R L R L oDokumen5 halamanECE 209 Homework #2 Solutions: R L R L R L oJavier CorralBelum ada peringkat

- Experiment No 02Dokumen4 halamanExperiment No 02noushadBelum ada peringkat

- VLSI Design NOV 19Dokumen2 halamanVLSI Design NOV 19Saurabh BhiseBelum ada peringkat

- Lab Report Operation of A RF Class-A Tuned AmplifierDokumen7 halamanLab Report Operation of A RF Class-A Tuned AmplifierKugaa NesvaranBelum ada peringkat

- TIA+Differential Amplifier TexasDokumen8 halamanTIA+Differential Amplifier TexasHrishikesh KunchepuBelum ada peringkat

- Amplifier Frequency ResponseDokumen4 halamanAmplifier Frequency ResponseDenver G. MagtibayBelum ada peringkat

- ph005 Unit 1 To 7Dokumen109 halamanph005 Unit 1 To 7tapceBelum ada peringkat

- Using The Impedance Method: Z JC Z Z Z ZDokumen15 halamanUsing The Impedance Method: Z JC Z Z Z ZAtyia JavedBelum ada peringkat

- Paper - Theory and Design of Advanced CMOS CurrentDokumen5 halamanPaper - Theory and Design of Advanced CMOS Currentjackal1710Belum ada peringkat

- Analog Communication Lab Manual VTUDokumen53 halamanAnalog Communication Lab Manual VTUDr Narayana Swamy Ramaiah100% (3)

- AMZ Stupidly Wonderful Tone Control 2Dokumen3 halamanAMZ Stupidly Wonderful Tone Control 2morag142Belum ada peringkat

- 078 Lab#8 CSDokumen8 halaman078 Lab#8 CSAsad saeedBelum ada peringkat

- L298motor PDFDokumen12 halamanL298motor PDFpnkjinamdarBelum ada peringkat

- 1 - Logic GatesDokumen7 halaman1 - Logic GatesAlfred GaleaBelum ada peringkat

- CD4047Dokumen15 halamanCD4047mohankumarktvrBelum ada peringkat

- Ejercicios Cap04Dokumen13 halamanEjercicios Cap04Miguel LiceagaBelum ada peringkat

- 9.2 Schmitt TriggerDokumen11 halaman9.2 Schmitt TriggerlvsaruBelum ada peringkat

- Assignment8 ECE3300 F17Dokumen2 halamanAssignment8 ECE3300 F17A124 Muhammad Minam Ur Rehman KhanBelum ada peringkat

- Principles of Electronic Communication Systems: Third EditionDokumen78 halamanPrinciples of Electronic Communication Systems: Third EditionJerico CustodioBelum ada peringkat