Exercícios AOC II Parte 1

Diunggah oleh

msancor0 penilaian0% menganggap dokumen ini bermanfaat (0 suara)

382 tayangan5 halamanO documento apresenta uma lista de exercícios sobre arquitetura de computadores e processamento de sinais digitais. Os exercícios abordam tópicos como conversão entre unidades de tempo e frequência, representação de números em ponto flutuante no padrão IEEE 754, operações aritméticas com números em ponto flutuante, análise do desempenho de algoritmos e arquiteturas, entre outros.

Deskripsi Asli:

Judul Asli

817272_Lista01_Parte1_AOC II _ 2014_2

Hak Cipta

© © All Rights Reserved

Format Tersedia

PDF, TXT atau baca online dari Scribd

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniO documento apresenta uma lista de exercícios sobre arquitetura de computadores e processamento de sinais digitais. Os exercícios abordam tópicos como conversão entre unidades de tempo e frequência, representação de números em ponto flutuante no padrão IEEE 754, operações aritméticas com números em ponto flutuante, análise do desempenho de algoritmos e arquiteturas, entre outros.

Hak Cipta:

© All Rights Reserved

Format Tersedia

Unduh sebagai PDF, TXT atau baca online dari Scribd

0 penilaian0% menganggap dokumen ini bermanfaat (0 suara)

382 tayangan5 halamanExercícios AOC II Parte 1

Diunggah oleh

msancorO documento apresenta uma lista de exercícios sobre arquitetura de computadores e processamento de sinais digitais. Os exercícios abordam tópicos como conversão entre unidades de tempo e frequência, representação de números em ponto flutuante no padrão IEEE 754, operações aritméticas com números em ponto flutuante, análise do desempenho de algoritmos e arquiteturas, entre outros.

Hak Cipta:

© All Rights Reserved

Format Tersedia

Unduh sebagai PDF, TXT atau baca online dari Scribd

Anda di halaman 1dari 5

Lista de Exerccios 1 AOC II Parte 1

1) Determinar o tempo conhecendo-se a freqncia de 150 Mhz:

a) em ms

b) em us

c) em ns

2) Determinar a freqncia conhecendo-se o tempo de 100ns:

a) em Khz

b) em Mhz

c) em GHz

3) Mostrar se para as somas a seguir haver um vai1 para fora do nmero (use CLA):

a) FACA +BABA

b) 3AF1 +45EA

4) Como funciona basicamente o algoritmo de um multiplicador Booth ?

5) Construir um circuito de um multiplicador paralelo que multiplique dois nmeros de

3 bits.

6) Ilustrar atravs de um grfico como a distribuio (densidade de nmeros) para

nmeros na notao IEEE754 onde adotamos 1 bit para o sinal, 3 para expoente e 2

para mantissa.

7) Qual o valor em notao cientfica decimal para os seguintes nmeros na notao

IEEE754 para 32 bits e 64 bits. Dizemos que a notao para 32 bits de preciso

simples e a de 64 bits de preciso dupla. A notao de 32 bits possui 1 bit de sinal, 8

para expoente e 23 para mantissa. A notao de 64 bits possui 1 bit de sinal, 11 para

expoente e 52 para mantissa.

a) 803ACABA

(IEEE 754 1/8/23)

b) 00FAFACA

(IEEE 754 1/8/23)

c) 803ACABA00000000

(IEEE 754 1/11/52)

d) 00FAFACA00000000

(IEEE 754 1/11/52)

8) Representar os seguintes nmeros na notao IEEE754 para 32 bits e 64 bits.

Mostrar os valores em binrio e hexadecimal.

a) 1.1234 x 10

5

b) 7.2354 x 10

-4

9) Converta os seguintes nmeros para IEEE-754 preciso simples. Apresente as

suas respostas em binrio e hexadecimal.

a) 14.125

a) 3.14159

b) -58.375

c) -4096

d) -3.25

10) Apresente os equivalentes decimais dos seguintes nmeros IEEE-754 de preciso

simples, apresentados em binrio.

a) 0 10000001 01100000000000000000000

b) 1 10000001 00010000000000000000000

c) 1 10000000 00000000000000000000000

d) 0 00000001 01011000000000000000000

11) Apresente os equivalentes decimais dos seguintes nmeros IEEE-754 de preciso

simples, apresentados em hexadecimal:

a. 0x41202000

b. 0x00000000

c. 0x42E80000

d. 0xC1DA0000

e. 0xFFFFFFFF

12) Avalie as operaes abaixo indicando os passos nos algoritmos da soma ou

multiplicao

a. 0 10000010 1010...0 +0 10000001 0110...0

b. 0 10000010 1010...0 x 0 10000001 0110...0

13) Considerando os seguintes nmeros hexadecimais no formato IEEE 754, preciso

simples, coloc-los em ordem crescente:

a) 7F7FF800

b) D57F0000

c) 5F7FF800

d) 7F800000

e) D5FFE000

14) Considere a soma e a multiplicao dos nmeros 1.12 x 10

2

e 2.24 x 10

-1

. Mostrar

o erro absoluto e relativo dessas operaes se usarmos as seguintes representaes:

IEEE754 onde adotamos 1 bit para o sinal, 4 para expoente e 3 para mantissa.

IEEE754 onde adotamos 1 bit para o sinal, 3 para expoente e 4 para mantissa.

15) O que foi o Pentium FDIV bug. (consulte na Internet e veja a lambana da Intel)

Lei de Amdahl

16) Considere que a memria cache seja 5 vezes mais rpida que a memria principal.

Se ela ser utilizada 90% do tempo, qual o Speedup total proporcionado pelo uso da

Cache?

17) Considere que um processador sofrer o acoplamento de um coprocessador

aritmtico. Este coprocessador capaz de tornar as operaes 5 vezes mais rpidas.

a) Qual o Speedup se utilizarmos o coprocessador 50% do tempo?

b) Qual deveria ser a utilizao do coprocessador para obtermos uma melhoria

total de 2 vezes?

c) Considere que iremos utilizar o coprocessador 50% do tempo, quantas vezes

esse coprocessador dever tornar as operaes mais rpidas se eu preciso de

uma melhoria total mnima de 2.5 vezes?

18) Podemos substituir um processador por outro 5 vezes mais rpido por 5 vezes o seu

preo. Sabe-se que o processador ser utilizado em 50% do tempo, o restante dever

aguardar operaes de I/O. Se o processador corresponde a 1/3 do preo da

mquina, essa alterao vlida?

(Obs.: Use uma simples relao custo/ganho)

19) As implementaes em FP (ponto flutuante). Em especial as operaes de raiz

quadrada, variam significativamente em performance. Suponha que as FPSQR

(razes em FP) so responsveis por 20% do tempo de execuo em uma mquina.

Nossa proposta adicionar um hardware (coprocessador) que acelere esta operao

por um fator de 10. Existe uma outra proposta que a de melhorar todas as

operaes de FP. As operaes de FP so responsveis por 50% do tempo de

execuo. Os projetistas acreditam que podem melhorar as instrues de FP por um

fator de 2 usando os mesmos recursos que usariam para as FPSQR).

Qual a melhor alternativa?

20) Suponha que tenhamos melhorado uma parcela do tempo de execuo de uma

mquina por um fator de 10. Esse modo melhorado usado 50% do tempo medido

como porcentagem quando o melhoramento est implementado.

a) Qual o Speedup obtido com o melhoramento?

b) Qual a porcentagem de tempo de execuo inicial foi convertida para esse

modo rpido?

Equao da CPU

21) Um programa roda em 10s em uma mquina A que possui um clock de 400MHz.

Queremos um speedup de 1.5 ao executar esse mesmo programa em uma mquina

B. A mquina B poder sofrer um overclock substancial sem nenhuma seqela

adicional, entretanto exigir 1,2 vezes mais ciclos de clock para executar as

instrues do que a mquina A.

Qual a frequencia de clock necessria para a mquina B?

22) Considere um programa com 1000 somas. Suponha que eu gaste 1 ciclo de mquina

para cada soma. Se a mquina opera a 100 MHz, quanto tempo o programa demora?

23) Considere uma mquina e 2 programas diferentes que sero executados. O primeiro

possui 2000 instrues e o segundo possui 3000 instrues.

Qual o tempo de execuo de cada um considerando um CPI de 5 e a freqncia da

mquina de 100 MHz. Qual o speedup?

24) Em uma mquina operando a 100MHz, irei executar um programa que possui 2

tipos de instrues, instrues aritmticas e instrues de desvio.O programa possui

10000 instrues, onde 60% so as instrues aritmticas o restante corresponde s

instrues de desvio. O CPI para as instrues aritmticas 4 e para as outras

instrues 5.

Qual o CPI mdio da mquina

Considere um novo hardware onde o CPI para as instrues aritmticas passe a

ser 3. Qual o speedup sobre a mquina original?

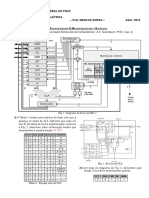

25) Considere uma mquina funcionando a 100 MHz e o Benchmark B1. Considere

ainda a tabela com os CPIs de cada tipo de instruo.

a) Qual o CPI mdio da mquina ?

b) Suponha um overclock de 12%. Qual o speedup sobre a mquina original ?

c) Suponha uma alterao no Hardware e no acesso memria. Essa alterao

reduz em dois ciclos as instrues da ALU ao custo de aumentar em 1 ciclo

os acessos memria. Qual o speedup sobre a mquina original?

d) Considere um novo compilador que reduza em 50% as instrues da ALU.

Qual o speedup sobre a mquina original?

e) Qual a melhor alterao sobre a mq. original: b, c ou d ?

f) Qual o speedup sobre a mq. original se aplicarmos todas as alteraes.

Instrues da ALU

Instrues de desvio

Instrues de acesso

memria

Outras

B1

B2 B2 B3

40%

30%

20%

10%

Tipo de instrues

Benchmarks

Instrues da ALU

Instrues de desvio

Instrues de acesso

memria

Outras

CPI

4

3

5

6

Tipo de instrues

Anda mungkin juga menyukai

- Lista OC - DesempenhoDokumen5 halamanLista OC - Desempenhorlorenzetto93Belum ada peringkat

- Gabarito AD1 - Organização de ComputadoresDokumen14 halamanGabarito AD1 - Organização de Computadoresccaetanoa2Belum ada peringkat

- 2 ExercíciosACIIIDokumen5 halaman2 ExercíciosACIIIMarlon Bento AzevedoBelum ada peringkat

- Explicando Suas EscolhasDokumen2 halamanExplicando Suas EscolhasLeandro da Cruz Farias MatosBelum ada peringkat

- AOC - Lista de Exercícios 1b - RESPOSTASDokumen4 halamanAOC - Lista de Exercícios 1b - RESPOSTASJonatas OliveiraBelum ada peringkat

- Exercícios de Arquitetura de ComputadoresDokumen5 halamanExercícios de Arquitetura de ComputadoresDuarlem RobertoBelum ada peringkat

- Exercício Lei de AmdahlDokumen2 halamanExercício Lei de AmdahlNikolas AugustoBelum ada peringkat

- Gabarito Top Av Arq MM Prova Av1 2018 2Dokumen5 halamanGabarito Top Av Arq MM Prova Av1 2018 2Alexandre Melo100% (1)

- Avaliação Desempenho Sistema FatoresDokumen27 halamanAvaliação Desempenho Sistema FatoresRobson FerreiraBelum ada peringkat

- Exercicios Aula 2Dokumen2 halamanExercicios Aula 2Leonardo MenegonBelum ada peringkat

- Lista de Exercícios ADokumen4 halamanLista de Exercícios AbrunoBelum ada peringkat

- Microcontroladores 2 Exercicios Macro e Microarquitetura v2Dokumen4 halamanMicrocontroladores 2 Exercicios Macro e Microarquitetura v2Marcelo LimaBelum ada peringkat

- AD1 - 2018-2 - Gabarito - Organização de Computadores PDFDokumen6 halamanAD1 - 2018-2 - Gabarito - Organização de Computadores PDFccaetanoa2Belum ada peringkat

- ListaExercíciosIADokumen4 halamanListaExercíciosIAbrunoBelum ada peringkat

- SO Gerenciamento de Processos Lista Exercícios UFSCDokumen3 halamanSO Gerenciamento de Processos Lista Exercícios UFSCNetSul InternetBelum ada peringkat

- SD Lista1 Vinicius OliveiraDokumen6 halamanSD Lista1 Vinicius OliveiraVinícius CésarBelum ada peringkat

- Resposta Da Lista de Exercícios de Lei de Moore e Hardware X SoftwareDokumen2 halamanResposta Da Lista de Exercícios de Lei de Moore e Hardware X SoftwaresribeirofernandesBelum ada peringkat

- SIOPrespostasDokumen24 halamanSIOPrespostasLyan Lourençco100% (1)

- Memória cache e desempenho de sistemasDokumen3 halamanMemória cache e desempenho de sistemasLeandro da Cruz Farias MatosBelum ada peringkat

- Cronômetro digital com LogisimDokumen11 halamanCronômetro digital com LogisimRosCibelyBelum ada peringkat

- 05-Organização de ComputadorDokumen13 halaman05-Organização de ComputadorAdalberto MendesBelum ada peringkat

- AOC - Lista de Exercícios 1a - RESPOSTASDokumen5 halamanAOC - Lista de Exercícios 1a - RESPOSTASJonatas Oliveira100% (1)

- Respostas Arquitetura de ComputadoresDokumen10 halamanRespostas Arquitetura de ComputadoresUbiratan LoureiroBelum ada peringkat

- Arquitetura Computadores QuestionárioDokumen5 halamanArquitetura Computadores QuestionárioMarcus RamosBelum ada peringkat

- Lista 3Dokumen3 halamanLista 3renan correa de.mouraBelum ada peringkat

- OC - Aula 3Dokumen19 halamanOC - Aula 3João Pedro ConteBelum ada peringkat

- Capítulo 06Dokumen6 halamanCapítulo 06Samuel LeonhardtBelum ada peringkat

- Resumo Hardware para ComputacaoDokumen22 halamanResumo Hardware para ComputacaoDouglas Basilio Dos SantosBelum ada peringkat

- APX2 - 2020-1 - Gabarito - Organização de ComputadoresDokumen4 halamanAPX2 - 2020-1 - Gabarito - Organização de ComputadoresGabriel De Souza FerreiraBelum ada peringkat

- ArtigoDokumen12 halamanArtigoMatheus MariniBelum ada peringkat

- Lista01Dokumen10 halamanLista01João SilvaBelum ada peringkat

- Arquitetura de Computadores - Questões sobre representação numérica, formatos de ponto fixo e flutuanteDokumen3 halamanArquitetura de Computadores - Questões sobre representação numérica, formatos de ponto fixo e flutuanteLucas ViveirosBelum ada peringkat

- Lista de Exercicios 1 e 2Dokumen4 halamanLista de Exercicios 1 e 2Mauricio Soneka100% (3)

- Microcontroladores - Avaliação IndividualDokumen2 halamanMicrocontroladores - Avaliação IndividualMatheus SerpaBelum ada peringkat

- FATEC Questionário sobre componentes e funções de um processadorDokumen4 halamanFATEC Questionário sobre componentes e funções de um processadorCassie100% (1)

- 2013 2014-So-Exame Normal PDFDokumen3 halaman2013 2014-So-Exame Normal PDFAlfredo SoldadinhoBelum ada peringkat

- SO Exercícios EscalonamentoDokumen4 halamanSO Exercícios EscalonamentoCelio EstevesBelum ada peringkat

- Lista de Exercícios 1Dokumen5 halamanLista de Exercícios 1Flávia SantosBelum ada peringkat

- Competencias Transversais para EngenhariaDokumen10 halamanCompetencias Transversais para EngenhariatavaresaninejoBelum ada peringkat

- ECA602 - Lista - 1 - Controle ClássicoDokumen4 halamanECA602 - Lista - 1 - Controle ClássicoThiago ValimBelum ada peringkat

- Assembly 0001Dokumen9 halamanAssembly 0001Pablo PinheiroBelum ada peringkat

- Gabarito Ap2Dokumen4 halamanGabarito Ap2AliceBelum ada peringkat

- Folha 01Dokumen5 halamanFolha 01efjnfeaeffeBelum ada peringkat

- AP1 - 2013-2 - Gabarito - Organização de ComputadoresDokumen4 halamanAP1 - 2013-2 - Gabarito - Organização de ComputadoresJoeme AlvesBelum ada peringkat

- Ap1 - QuestionárioDokumen5 halamanAp1 - QuestionárioThiago Francisco Paes AlvesBelum ada peringkat

- Computer_Architecture_IIDokumen7 halamanComputer_Architecture_IIRicardoBelum ada peringkat

- Aula 8 Programacao Do 8085 (Cont.)Dokumen30 halamanAula 8 Programacao Do 8085 (Cont.)joaoluisjorge4Belum ada peringkat

- Teste FormativoDokumen10 halamanTeste Formativovaldimiro.gaspar16Belum ada peringkat

- Arquitetura de computadores - QuestõesDokumen13 halamanArquitetura de computadores - QuestõesSergio de Oliveira0% (2)

- Microcontrolador ATMega328Dokumen7 halamanMicrocontrolador ATMega328Jorge Luiz A. MorgadoBelum ada peringkat

- Funções da UCP e componentes de uma CPUDokumen4 halamanFunções da UCP e componentes de uma CPUNatalFonseca0% (2)

- Arquitetura de Computadores - QuestionárioDokumen5 halamanArquitetura de Computadores - QuestionárioMarcus RamosBelum ada peringkat

- Lista 2 - Marcone Gabriel Da SilvaDokumen5 halamanLista 2 - Marcone Gabriel Da SilvaMARCONE GABRIEL DA SILVABelum ada peringkat

- Arquitetura Computadores Lista ExercíciosDokumen3 halamanArquitetura Computadores Lista ExercíciosNicolas HiroshiBelum ada peringkat

- 2 Lista Pipeline RespostaDokumen4 halaman2 Lista Pipeline RespostaRairon FernandesBelum ada peringkat

- 0w94ijsf 11Dokumen6 halaman0w94ijsf 11Twi tchBelum ada peringkat

- Exercícios Organização de ComputadoresDokumen31 halamanExercícios Organização de ComputadoresMattheus Santos0% (2)

- Desempenho e Pipeline PDFDokumen38 halamanDesempenho e Pipeline PDFThiago PereiraBelum ada peringkat

- Implementando Um Inversor De Frequência Escalar Programado No Arduino Com Driver Para Motor De Até 3 CvDari EverandImplementando Um Inversor De Frequência Escalar Programado No Arduino Com Driver Para Motor De Até 3 CvBelum ada peringkat

- Desempenho e Pipeline PDFDokumen38 halamanDesempenho e Pipeline PDFThiago PereiraBelum ada peringkat

- Tema 1 - Fundamentos de Sistemas DistribuídosDokumen77 halamanTema 1 - Fundamentos de Sistemas DistribuídosJorge Filipe †Belum ada peringkat

- 05-Organização de ComputadorDokumen13 halaman05-Organização de ComputadorAdalberto MendesBelum ada peringkat

- Evolução dos ComputadoresDokumen226 halamanEvolução dos ComputadoresCoutinho ThiagoBelum ada peringkat

- CRIAR UM CLUSTER DE PROCESSAMENTO PARALELO MPI COM RASPBERRIESDokumen6 halamanCRIAR UM CLUSTER DE PROCESSAMENTO PARALELO MPI COM RASPBERRIESamilcarsoaresBelum ada peringkat

- Desempenho, Multicore, Leis Amdahl e LittleDokumen37 halamanDesempenho, Multicore, Leis Amdahl e LittleEduardo Miguel Perotti OliveiraBelum ada peringkat

- Estudo Sobre Linguagens de Programação Paralela e Os Conceitos Chave de Paralelismo em Nível de ProgramaçãoDokumen51 halamanEstudo Sobre Linguagens de Programação Paralela e Os Conceitos Chave de Paralelismo em Nível de ProgramaçãoRedação PopBelum ada peringkat

- Dedução Da Lei de Amdahl PDFDokumen2 halamanDedução Da Lei de Amdahl PDFRicardo Bruno FelixBelum ada peringkat

- Aula 5Dokumen54 halamanAula 5Gustavo RibeiroBelum ada peringkat

- Avaliação Desempenho Sistema FatoresDokumen27 halamanAvaliação Desempenho Sistema FatoresRobson FerreiraBelum ada peringkat

- Programação Concorrente e DistribuídaDokumen2 halamanProgramação Concorrente e DistribuídaHerval JuniorBelum ada peringkat

- Computação Escalável - COM460Dokumen408 halamanComputação Escalável - COM460newchessBelum ada peringkat

- Implementação Paralela do Algoritmo Rank Sort usando MPIDokumen2 halamanImplementação Paralela do Algoritmo Rank Sort usando MPICarlos Henrique OliveiraBelum ada peringkat

- Exercícios AOC II Parte 1Dokumen5 halamanExercícios AOC II Parte 1msancorBelum ada peringkat

- Olhonavaga - PROVA - FCC - DPE-RS - Analista - Segurança Da InformaçãoDokumen17 halamanOlhonavaga - PROVA - FCC - DPE-RS - Analista - Segurança Da Informaçãonotat80726Belum ada peringkat

- Exercício Lei de AmdahlDokumen2 halamanExercício Lei de AmdahlNikolas AugustoBelum ada peringkat