Chapter 1-Introduction To The Semiconductor Industry-NEW

Diunggah oleh

hrrameshhrJudul Asli

Hak Cipta

Format Tersedia

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniHak Cipta:

Format Tersedia

Chapter 1-Introduction To The Semiconductor Industry-NEW

Diunggah oleh

hrrameshhrHak Cipta:

Format Tersedia

2005 VLSI TECH.

'] "} 1

Chapter 1

Introduction to The

Semiconductor Industry

2005 VLSI TECH.

'] "} 2

The Semiconductor Industry

PRODUCT

APPLICATIONS

INFRASTRUCTURE

Consumers:

Computers

Automotive

Aerospace

Medical

other industries

Customer Service

Original Equipment Manufacturers

Printed Circuit Board Industry

Industry Standards

(SIA, SEMI, NIST, etc.)

Production Tools

Utilities

Materials & Chemicals

Metrology Tools

Analytical Laboratories

Technical Work Force

Colleges & Universities

Chip

Manufacturer

Worldwide sales of microchips : > $250 billion in 2005

SIA: semiconductor industry association

2005 VLSI TECH.

'] "} 3

From Devices to Integrated Circuits

1950s: Transistor Technology

1960s: Process Technology

1970s: Competition

1980s: Automation

1990s: Volume Production

Fairchild Semiconductor, California

(Silicon Valley), Robert Noyce

(1947) The First Solid-state Transistor

(1958) The First Integrated

Circuit (IC) Device - Oscillator

IC ( 5 components )

(1961) The First Planar

IC (Transistor+R+C)

Lucent Technologies, Bell Labs

Innovations, William Shockley, J ohn

Bardeen, Walter Brattain (1956 Nobel

Prize in physics)

Texas Instruments, Inc., J ack Kilby

2005 VLSI TECH.

'] "} 4

Top View of Wafer with Chips

A single integrated

circuit, also known

as a die, chip, and

microchip

2005 VLSI TECH.

'] "} 5

Snapshot- Profile of IC

8 metal layers over the past 25 years

Silicon

M6

Via 5

M5

M4

M3

M2

M1

Via 4

Via 3

Via 2

Via 1

Contact(W)

Cu

2005 VLSI TECH.

'] "} 6

IC Fabrication

Silicon

Wafer

Wafer Sizes

Devices and Layers

Wafer Fab

Stages of IC Fabrication

Wafer preparation

Wafer fabrication

Wafer test/sort

Assembly and packaging

Final test

2005 VLSI TECH.

'] "} 7

Evolution of Wafer Size

2000

1992

1987

1981

1975

1965

2005 VLSI TECH.

'] "} 8

Devices and Layers from a Silicon Chip

Silicon substrate

drain

Silicon substrate

Top protective layer

Metal layer

Insulation layers

Recessed conductive

layer

Conductive layer

2005 VLSI TECH.

'] "} 9

Stages of IC Fabrication

Wafer Preparation

includes crystal

growing, rounding,

slicing and polishing.

Wafer Fabrication

includes cleaning,

layering, patterning,

etching and doping.

Assembly and Packaging:

The wafer is cut

along scribe lines

to separate each die.

Metal connections

are made and the

chip is encapsulated.

Test/Sort includes

probing, testing and

sorting of each die on

the wafer.

Final Test ensures IC

passes electrical and

environmental

testing.

Defective die

1.

2.

3.

Scribe line

A single die

Assembly Packaging

4.

5.

Wafers sliced from ingot

Single crystal silicon

2005 VLSI TECH.

'] "} 10

Preparation of Silicon Wafers

1. Crystal Growth

2. Single Crystal Ingot

3. Crystal Trimming and

Diameter Grind

4. Flat Grinding

5. Wafer Slicing

6. Edge Rounding

7. Lapping

8. Wafer Etching

9. Polishong

10. Wafer Inspection

Slurry

Polishing table

Polishing

head

Polysilicon Seed crystal

Heater

Crucible

(Note: Terms in Figure 1.7 are explained in Chapter 4.)

2005 VLSI TECH.

'] "} 11

Wafer Fab

Photo courtesy of Advanced Micro Devices-Dresden, S. Doering

2005 VLSI TECH.

'] "} 12

Career Paths in the

Semiconductor Industry

ManufacturingTechnician

Wafer FabTechnician

Maintenance Technician Lab Technician

Yield & Failure Analysis Technician Equipment Technician

Equipment Engineer

Associate Engineer

Process Engineer

Production Supervisor

Production Manager

Maintenance Supervisor

Fab Manager

Maintenance Manager

Process Technician

Engineering Manager

Production Operator

HS +

AS+

AS

BS

MS

HS

Education

BSET*

* Bachelor of Science in

Electronics Technology

2005 VLSI TECH.

'] "} 13

Circuit Integration of Semiconductors

- Integration Eras

Circuit Integration

Semiconductor

Industry Time Period

Number of

Components per

Chip

No integration (discrete components) Prior to 1960 1

Small scale integration (SSI) Early 1960s 2 to 50

Medium scale integration (MSI) 1960s to Early 1970s 50 to 5,000

Large scale integration (LSI)

Early 1970s to Late

1970s

5,000 to 100,000

Very large scale integration (VLSI)

Late 1970s to Late

1980s

100,000 to 1,000,000

Ultra large scale integration (ULSI) 1990s to present > 1,000,000

Increase in Chip Performance

Components per Chip

Power Consumption

Increase in Chip Reliability

Reduction in Chip Price

Semiconductor Trends :

2005 VLSI TECH.

'] "} 14

Size Comparison of Early and

Modern Semiconductors

1990s Microchip

(5~25 million transistors)

1960s Transistor

U.S. coin, 10 cents

2005 VLSI TECH.

'] "} 15

2005 VLSI TECH.

'] "} 16

Past and Future Technology Nodes for

Device Critical Dimension (CD)

1988 1992 1995 1997 1999 2001 2002 2005

CD

(m)

1.0 0.5 0.35 0.25 0.18 0.15 0.13 0.10

Common IC Features

Contact Hole

Line Width Space

2005 VLSI TECH.

'] "} 17

Feature Technology and Size

/

!

Wafer

0.35 m technology

0.25 m technology

0.18 m technology

0.13 m

technology

0.09 m

technology

0.065 m

technology

12-Inch

8-Inch

6-Inch

When compared to the 0.18-micron process, the

new 0.13-micron process results in less than 60

percent the die size and nearly 70 percent

improvement in performance

The 90-nm process will be manufactured on

300mm wafers

NEC devises low-k film for second-generation

65-nm process

2005 VLSI TECH.

'] "} 18

Die Size

Wafer photo

Single die

Wafer

From http:/ / www.amd.com

2005 VLSI TECH.

'] "} 19

Price Decrease of Semiconductor Chips

Redrawn from C. Chang & S. Sze, McGraw-Hill, ULSI Technology, (New York: McGraw-Hill, 1996), xxiii.

1930 1940 1950 1960 1970 1980 1990 2000

Year

10

4

10

2

1

10

-2

10

-4

10

-6

10

-8

10

-10

R

e

l

a

t

i

v

e

v

a

l

u

e

Device size=

Price=

Bipolar transistor

MSI

LSI

VLSI

ULSI

Standard tube

Electron tubes

Semiconductor devices

Integrated circuits

Miniature tube

1958 : $10 / 1 Transistor

2001 : $10 / 20 million Transistor

1995 : CD=0.35 m

1997 : CD=0.25 m

2002 : CD=0.13 m

increase 150~275

chips per wafer

2005 VLSI TECH.

'] "} 20

Reliability Improvement of Chips &

Reduction in Chip Power Consumption per IC

1972 1976 1980 1984 1988 1992 1996 2000

700

600

500

400

300

200

100

0

Year

L

o

n

g

-

T

e

r

m

F

a

i

l

u

r

e

R

a

t

e

G

o

a

l

s

i

n

p

a

r

t

s

p

e

r

m

i

l

l

i

o

n

(

P

P

M

)

10

8

6

4

2

0

1997 1999 2001 2003 2006 2009 2012

A

v

e

r

a

g

e

P

o

w

e

r

i

n

m

i

c

r

o

W

a

t

t

s

(

1

0

-

6

W

)

Year

Redrawn from Semiconductor Industry Association (SIA)

National Technology Roadmap, 1997

2005 VLSI TECH.

'] "} 21

ULSI Chip

Gross world product (GWP) and sales

volumes of the electronics, automobile,

semiconductor, and steel industries from

1980 to 2000 and projected to 2010.

Intel Corporation, Pentium III

2005 VLSI TECH.

'] "} 22

IC Product #1:

Semiconductor Memory Devices

(a) A schematic diagram of the first nonvolatile semiconductor

memory (NVSM) with a floating gate. (b) A limiting case of the

floating-gate NVSMthe single-electron memory cell.

Exponential increase of dynamic random access

memory (DRAM) density versus year based on the

Semiconductor Industry Association (SIA) roadmap.

NVSM : non-volatility; high device density; low-

power consumption; electrical rewritability.

2005 VLSI TECH.

'] "} 23

IC Product #2 : Microprocessor Chips

Moores Law for Microprocessors

The number of transistors on a chip double every (12) 18 months.

Advanced Micro Devices

Intel Corporation

Year

4004

8080

8086

80286

80386

80486

Pentium

Pentium Pro

100M

10M

1M

100K

10K

T

r

a

n

s

i

s

t

o

r

s

1975 1980 1985 1990 1995 2000

500

25

1.0

.1

.01

Proceedings of the IEEE, J anuary, 1998, 1998 IEEE

2005 VLSI TECH.

'] "} 24

Moores Law

Intel co-founder Gordon Moore notices in 1964

Number of transistors doubled every 12 months

Slowed down in the 1980s to every 18 months

Amazingly still correct likely to keep until 2010

With Moores Law, IC

products can reach low

costs, improve performance,

and increase the functions.

Gordon Moore

Intel Co-Founder and Chairmain

Emeritus

2005 VLSI TECH.

'] "} 25

Start-Up Cost of Wafer Fabs

$100,000,000,000

$10,000,000,000

$1,000,000,000

$100,000,000

$10,000,000

C

o

s

t

1970 1980 1990 2000 2010 2020

Year

Actual Costs

Projected Costs

Used with permission from Proceedings of IEEE, J anuary, 1998 1998 IEEE

2005 VLSI TECH.

'] "} 26

Productivity Measurements in a Wafer Fab

Metallization

Production Bay

Etch

Production Bay

Thin Films

Production Bay

Diffusion

Production Bay

Photo

Production Bay

Ion Implant

Production Bay

Misprocessing

Production Equipment

Inspection

Rework

Inspection

Scrap

Production

Equipment

Inspection

Production

Equipment

Inspection

Production

Equipment

Inspection Production

Equipment

Inspection

Production

Equipment

Wafer Starts

1 2 3 4

5 6 7 8 9 10 11

12 13 14 15 16 17 18

19 20 21 22 23 24 25

26 27 28 29 30 31

1 2 3 4

5 6 7 8 9 10 11

12 13 14 15 16 17 18

19 20 21 22 23 24 25

26 27 28 29 30 31

1

2 3 4 5 6 7 8

9 10 11 12 13 14 15

16 17 18 19 20 21 22

23 24 25 26 27 28 29

30 31

1

2 3 4 5 6 7 8

9 10 11 12 13 14 15

16 17 18 19 20 21 22

23 24 25 26 27 28 29

30 31

Wafer Outs

Time In

Time Out

12

3

6

9

Cycle Time

per Operation

Production Cycle Time = (Date and Time of Wafer Start) - (Date and Time of Wafer Out)

Wafer Outs = Wafer Starts - Wafers Scrapped

Operator Efficiency = Theoretical Cycle Time / Actual Cycle Time

Wafer Moves

2005 VLSI TECH.

'] "} 27

Equipment Technician in a Wafer Fab

Photograph courtesy of Advanced Micro Devices

2005 VLSI TECH.

'] "} 28

Technician in Wafer Fab

Photo courtesy of Advanced Micro Devices

Anda mungkin juga menyukai

- AMD's Customer-Centric Approach and Potential for Commercially Viable Innovation/TITLEDokumen5 halamanAMD's Customer-Centric Approach and Potential for Commercially Viable Innovation/TITLEMukund KabraBelum ada peringkat

- Synopsis On Car Parking Using SCADADokumen6 halamanSynopsis On Car Parking Using SCADAPrakhar JindalBelum ada peringkat

- Cloud Computing PresentationDokumen57 halamanCloud Computing PresentationTANVIR RAHMANBelum ada peringkat

- Introducing Windows Azure, V1.2 - ChappellDokumen25 halamanIntroducing Windows Azure, V1.2 - ChappellSister101Belum ada peringkat

- 11.a Cloud - WikiDokumen19 halaman11.a Cloud - WikiIvan StankovicBelum ada peringkat

- POMADokumen4 halamanPOMAMuhammad Umer Anjum MirzaBelum ada peringkat

- Cores RAM Temporary SSD Storage Block Storage Amazon Price (Hour) Amazon Price (30 Days)Dokumen3 halamanCores RAM Temporary SSD Storage Block Storage Amazon Price (Hour) Amazon Price (30 Days)sriuae1982Belum ada peringkat

- Markets - Data VirtualizationDokumen6 halamanMarkets - Data Virtualizationdeepak162162Belum ada peringkat

- Azure Stack Operator Azs 2301Dokumen1.506 halamanAzure Stack Operator Azs 2301Pt BuddhakirdBelum ada peringkat

- Snow Avalanche Project ReportDokumen25 halamanSnow Avalanche Project Reportyogendra rana100% (1)

- An Overview of Internet Mapping Technology: Charlie CrockerDokumen23 halamanAn Overview of Internet Mapping Technology: Charlie CrockerPuspala ManojkumarBelum ada peringkat

- Intent Discovery From Conversational Logs To Prepare A Student Admission Chatbot For Tecnol Gico de MonterreyDokumen102 halamanIntent Discovery From Conversational Logs To Prepare A Student Admission Chatbot For Tecnol Gico de MonterreyYenny ReyesBelum ada peringkat

- Gartner Reprint - Object Storageoct21Dokumen20 halamanGartner Reprint - Object Storageoct21Wolf RichardBelum ada peringkat

- Olympic InnovationDokumen40 halamanOlympic InnovationBBVA Innovation CenterBelum ada peringkat

- Python Language Advantages and Applications PDFDokumen5 halamanPython Language Advantages and Applications PDFMuhammad SaniyanBelum ada peringkat

- Analysys Mason ReportDokumen216 halamanAnalysys Mason ReportBrian Jan AdelaBelum ada peringkat

- Simulation in Manufacturing Review and Challenges PDFDokumen17 halamanSimulation in Manufacturing Review and Challenges PDFHoracioGutierrezBelum ada peringkat

- Azure Virtual Desktop Overview & JourneyDokumen3 halamanAzure Virtual Desktop Overview & JourneyAlex (ali01) BonfiettiBelum ada peringkat

- Google Cloud Fundamentals Core InfrastructureDokumen2 halamanGoogle Cloud Fundamentals Core InfrastructureAnupama SBelum ada peringkat

- Calculate, Communicate and Compare Your Cyber Exposure Key BenefitsDokumen2 halamanCalculate, Communicate and Compare Your Cyber Exposure Key BenefitsSantiago HuilcamaiguaBelum ada peringkat

- Dua of Prophet Musa ASDokumen1 halamanDua of Prophet Musa ASFaiza GulbazBelum ada peringkat

- Semiconducter MemoryDokumen13 halamanSemiconducter MemorySayed AsifBelum ada peringkat

- LP SemiconductorDokumen7 halamanLP SemiconductorChennawit YulueBelum ada peringkat

- Emc VNX Series Unified Storage Systems: SpecificationsDokumen13 halamanEmc VNX Series Unified Storage Systems: Specificationssiddy8108Belum ada peringkat

- SP3D Automation Toolkit User GuideDokumen55 halamanSP3D Automation Toolkit User GuideMx Trailers100% (1)

- 15min ITILDokumen8 halaman15min ITILVeronica AguilaBelum ada peringkat

- Avalanche Snow-Slide Margreth Tecdoc enDokumen16 halamanAvalanche Snow-Slide Margreth Tecdoc enAlo RoviBelum ada peringkat

- Industry 4.0 Revolution PowerPoint TemplatesDokumen47 halamanIndustry 4.0 Revolution PowerPoint TemplatesRico ArdianBelum ada peringkat

- PWC - Semiconductor-Opportunities For Market - Global-2019.4 PDFDokumen18 halamanPWC - Semiconductor-Opportunities For Market - Global-2019.4 PDFSisleyBelum ada peringkat

- IDC Whitepaper Demonstrating Business ValueDokumen15 halamanIDC Whitepaper Demonstrating Business ValueRamon MateoBelum ada peringkat

- Understanding The Professional Cloud Architect CertificationDokumen27 halamanUnderstanding The Professional Cloud Architect CertificationPrem KumarBelum ada peringkat

- Transformation From 5G For Verticals Towards A 6GDokumen6 halamanTransformation From 5G For Verticals Towards A 6GShraddha ChopraBelum ada peringkat

- OPC UA & Smart-Ready Factory: All About Data Connectivity SolutionsDokumen46 halamanOPC UA & Smart-Ready Factory: All About Data Connectivity SolutionsMahrus FuadBelum ada peringkat

- DFN 4043 - Practical Task 3Dokumen11 halamanDFN 4043 - Practical Task 3Dumbo YanBelum ada peringkat

- Trusted ScholarsDokumen46 halamanTrusted ScholarsNabeelBelum ada peringkat

- Islamic InfoDokumen58 halamanIslamic InfoMajid KhanBelum ada peringkat

- AmdDokumen9 halamanAmdPeejay OllabracBelum ada peringkat

- Enterprise Wide ComputingDokumen4 halamanEnterprise Wide ComputingShahbaz Khan0% (1)

- Power System Automation: Eminar EportDokumen16 halamanPower System Automation: Eminar EportAnurajBelum ada peringkat

- Distributed Cloud Computing - Take Home ExamsDokumen3 halamanDistributed Cloud Computing - Take Home Examssamee Seth0% (1)

- ECM en AIDokumen43 halamanECM en AIReinoud KaasschieterBelum ada peringkat

- Advanced Database SystemsDokumen7 halamanAdvanced Database SystemsKeng Oei QuekBelum ada peringkat

- A New IT Experience in The Era of Digital Transformation (PDFDrive)Dokumen178 halamanA New IT Experience in The Era of Digital Transformation (PDFDrive)ionutalexandruBelum ada peringkat

- Cost AnalysisDokumen15 halamanCost AnalysisAman NaBelum ada peringkat

- Dev OpsDokumen13 halamanDev OpsPrathamesh JabareBelum ada peringkat

- Azure Stack HCI Overview WhitepaperDokumen12 halamanAzure Stack HCI Overview Whitepaperjohnlondon125Belum ada peringkat

- Aneka Magazine Article 3Dokumen12 halamanAneka Magazine Article 3Maryanna SchynneiderBelum ada peringkat

- AMD Embedded Solutions GuideDokumen32 halamanAMD Embedded Solutions Guidesukaryadi1Belum ada peringkat

- MANUFACTURING AUTOMATION COURSEDokumen2 halamanMANUFACTURING AUTOMATION COURSEAtul NarayananBelum ada peringkat

- Strategic Management - Modified Maps - Coloured - February 2020Dokumen11 halamanStrategic Management - Modified Maps - Coloured - February 2020ahmedgelixBelum ada peringkat

- Minimization of Waiting Time in Traffic Signals On Indian Roads Based On Wireless Sensor NetworkDokumen5 halamanMinimization of Waiting Time in Traffic Signals On Indian Roads Based On Wireless Sensor NetworkJournal of Computing100% (1)

- Azure Stack HciDokumen1.600 halamanAzure Stack HciPt BuddhakirdBelum ada peringkat

- Tech Spec of Cpu - EnnoreDokumen683 halamanTech Spec of Cpu - Ennoretanumay.geminiBelum ada peringkat

- IT Transformation in Large Technology Organization - Case Telco's Fault ManagementDokumen68 halamanIT Transformation in Large Technology Organization - Case Telco's Fault ManagementfriendprakashBelum ada peringkat

- Matching The Scale at With KafkaDokumen52 halamanMatching The Scale at With KafkaSam TanejaBelum ada peringkat

- 716 - UniGear ZS2 With VD4 05Dokumen6 halaman716 - UniGear ZS2 With VD4 05srmohapatra5086Belum ada peringkat

- Coverage DocumentDokumen2 halamanCoverage Documentsushant24x7Belum ada peringkat

- 01 IntroductionDokumen36 halaman01 IntroductionzailekBelum ada peringkat

- 01 IntroductionDokumen36 halaman01 IntroductionManjunath ChandrappaBelum ada peringkat

- Mechanical Properties and Performance of Engineering Ceramics and Composites X: A Collection of Papers Presented at the 39th International Conference on Advanced Ceramics and CompositesDari EverandMechanical Properties and Performance of Engineering Ceramics and Composites X: A Collection of Papers Presented at the 39th International Conference on Advanced Ceramics and CompositesDileep SinghBelum ada peringkat

- Unit 4 DFT and FFTDokumen42 halamanUnit 4 DFT and FFThrrameshhrBelum ada peringkat

- Microprocessor 8086 Memory and ArchitectureDokumen13 halamanMicroprocessor 8086 Memory and ArchitecturehrrameshhrBelum ada peringkat

- Introduction To Microprocessors and ComputersDokumen24 halamanIntroduction To Microprocessors and ComputershrrameshhrBelum ada peringkat

- Electrical Lab ManaulDokumen36 halamanElectrical Lab ManaulhrrameshhrBelum ada peringkat

- B01Dokumen49 halamanB01hrrameshhrBelum ada peringkat

- Unit - 2: Asic Library Design O Delay EstimationDokumen43 halamanUnit - 2: Asic Library Design O Delay EstimationhrrameshhrBelum ada peringkat

- ECE VLSI Design Course OverviewDokumen30 halamanECE VLSI Design Course OverviewhrrameshhrBelum ada peringkat

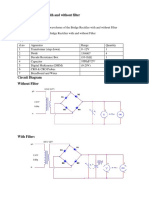

- Experiment No5 Full Wave RectfifierDokumen3 halamanExperiment No5 Full Wave RectfifierhrrameshhrBelum ada peringkat

- Chapter 2 Introduction To MicroprocessorDokumen20 halamanChapter 2 Introduction To MicroprocessorhrrameshhrBelum ada peringkat

- Electrical Engineering Lab 2Dokumen2 halamanElectrical Engineering Lab 2hrrameshhr100% (1)

- ECE VLSI Design Course OverviewDokumen30 halamanECE VLSI Design Course OverviewhrrameshhrBelum ada peringkat

- GoodDokumen69 halamanGoodC Radhika ReddyBelum ada peringkat

- Unit 7 & 8 - Z-TransformDokumen42 halamanUnit 7 & 8 - Z-TransformhrrameshhrBelum ada peringkat

- LD ManualDokumen85 halamanLD ManualhrrameshhrBelum ada peringkat

- Class No. Title Percentage of Portions CoveredDokumen2 halamanClass No. Title Percentage of Portions CoveredhrrameshhrBelum ada peringkat

- Vlsi 1Dokumen24 halamanVlsi 1hrrameshhrBelum ada peringkat

- Ascii Instructions8086Dokumen15 halamanAscii Instructions8086hrrameshhrBelum ada peringkat

- Microprocessor: Viva QuestionsDokumen6 halamanMicroprocessor: Viva QuestionshrrameshhrBelum ada peringkat

- Stepper Motor Theory of OperationDokumen11 halamanStepper Motor Theory of OperationSherif EltoukhiBelum ada peringkat

- 8086 InstructionDokumen44 halaman8086 InstructionhrrameshhrBelum ada peringkat

- CMOS Technology: 240 - 451 VLSI, 2000 1Dokumen11 halamanCMOS Technology: 240 - 451 VLSI, 2000 1hrrameshhrBelum ada peringkat

- FinalProjectPresentation Fareena3Dokumen36 halamanFinalProjectPresentation Fareena3hrrameshhrBelum ada peringkat

- 1220e Manual enDokumen72 halaman1220e Manual enAlexandra GarciaBelum ada peringkat

- Design FrequencyDokumen5 halamanDesign FrequencyGustavo SánchezBelum ada peringkat

- Wall Mounted G4 Series High Performance and Powerful Air Ow: DC InverterDokumen2 halamanWall Mounted G4 Series High Performance and Powerful Air Ow: DC InverterZacke EsmaBelum ada peringkat

- Datasheet LA76812Dokumen3 halamanDatasheet LA76812Kevin Villacis AvelinoBelum ada peringkat

- Astm e 426Dokumen4 halamanAstm e 426김경은Belum ada peringkat

- Lecture11 EE101A W16Dokumen13 halamanLecture11 EE101A W16ankitgoyal100Belum ada peringkat

- Overview of Power Integrity Solutions On Package and PCB: Decoupling and EBG IsolationDokumen39 halamanOverview of Power Integrity Solutions On Package and PCB: Decoupling and EBG IsolationIsmaiel KaladiBelum ada peringkat

- Atl® Ultramark® 9: SpecificationsDokumen1 halamanAtl® Ultramark® 9: SpecificationsRicardoRiveraBelum ada peringkat

- OMICRON CPL 542 543 Measuring Impedance DatasheetDokumen2 halamanOMICRON CPL 542 543 Measuring Impedance DatasheetHany KamelBelum ada peringkat

- RDS Technical SpecificationDokumen163 halamanRDS Technical Specificationwhistle-blower100% (1)

- Sans 1507Dokumen5 halamanSans 1507Raj shah100% (1)

- Gis PDFDokumen29 halamanGis PDFKarunBelum ada peringkat

- Amplifier Audio Transistor Guitar Pre-Amp Circuit Simplest Operating Self BiasDokumen2 halamanAmplifier Audio Transistor Guitar Pre-Amp Circuit Simplest Operating Self Biasdreyes2288Belum ada peringkat

- Data Acquisition With LabVIEWDokumen22 halamanData Acquisition With LabVIEWliubingxyBelum ada peringkat

- Description: 4 Channel Audio Processor PT2313LDokumen25 halamanDescription: 4 Channel Audio Processor PT2313LCarlos RamirezBelum ada peringkat

- A Practical Introduction To Hardwaresoftware Codesign 1Dokumen64 halamanA Practical Introduction To Hardwaresoftware Codesign 1s_subbulakshmiBelum ada peringkat

- BE - Service Manual P Series - 30K36K - 220VDokumen89 halamanBE - Service Manual P Series - 30K36K - 220Vhospital hggsBelum ada peringkat

- La 76832Dokumen39 halamanLa 76832carbalin5622Belum ada peringkat

- Samsung Le37m86bdx Le40m86bdx Le46m86bdx Le52m86bdx Le40m87bdx Le46m87bdx Chassis Gtu37,40,46,52sen LCD-TV SMDokumen196 halamanSamsung Le37m86bdx Le40m86bdx Le46m86bdx Le52m86bdx Le40m87bdx Le46m87bdx Chassis Gtu37,40,46,52sen LCD-TV SMPE TruBelum ada peringkat

- PFC Device Corporation: 40A 60V MOS Schottky RectifierDokumen7 halamanPFC Device Corporation: 40A 60V MOS Schottky RectifierАндрей АкимовBelum ada peringkat

- Circuit Symbols: Wires and Connections Compone NT Circuit Symbol Function of ComponentDokumen7 halamanCircuit Symbols: Wires and Connections Compone NT Circuit Symbol Function of ComponentRalph MedinaBelum ada peringkat

- PEE, IIEE Fellow, APEC Engr., ACPE: Power System Analysis I (Electrical Transmission Lines)Dokumen27 halamanPEE, IIEE Fellow, APEC Engr., ACPE: Power System Analysis I (Electrical Transmission Lines)Hendrick Brian QuezaBelum ada peringkat

- Unitrol 1000Dokumen4 halamanUnitrol 1000irfanWPKBelum ada peringkat

- Amperes Circuital LawDokumen14 halamanAmperes Circuital LawMeenaChi VermaBelum ada peringkat

- Motor PassoDokumen2 halamanMotor Passoaldoable2895Belum ada peringkat

- LTE Logical Channels (What Info is TransferredDokumen13 halamanLTE Logical Channels (What Info is TransferredAnshul GuptaBelum ada peringkat

- Step Response Unit ResponseDokumen6 halamanStep Response Unit ResponsetirsollantadaBelum ada peringkat

- Fire Extinguishing RobotDokumen4 halamanFire Extinguishing RobotPrajwal shettyBelum ada peringkat

- Cadence Design Tools TutorialDokumen124 halamanCadence Design Tools TutorialBhupender KumawatBelum ada peringkat

- 74738Dokumen12 halaman74738sontuyet82Belum ada peringkat