Digital Counters

Diunggah oleh

Harold WilsonHak Cipta

Format Tersedia

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniHak Cipta:

Format Tersedia

Digital Counters

Diunggah oleh

Harold WilsonHak Cipta:

Format Tersedia

http://www.tutorialspoint.com/computer_log ical_org aniz ation/dig ital_counters.htm Copyright tutorialspoint.

com

DIGITAL COUNTERS

Counter is a sequential circuit. A digital circuit which is used for a counting pulses is known counter. Counter is the

widest application of flip-flops. It is a group of flip-flops with a clock signal applied. Counters are of two types.

Asynchronous or ripple counters

Synchronous counters.

Asynchronous or ripple counters

The logic diagram of a 2-bit ripple up counter is shown in figure. The toggle(T) flip-flop are being used. But we

can use the JK flip-flop also with J and K connected permanently to logic 1. External clock is applied to the clock

input of flip-flop A and Q

A

output is applied to the clock input of the next flip-flop i.e. FF-B.

Logical Diagram

Operation

S.N. Condition Operation

1 Initially let both the FFs

be in the reset state

Q

B

Q

A

= 00................initially

2 After 1st negative clock

edge

As soon as the first negative clock edge is applied, FF-A will

toggle and Q

A

will be equal to 1.

Q

A

is connected to clock input of FF-B. Since Q

A

has

changed from 0 to 1, it is treated as the positive clock edge

by FF-B. There is no change in Q

B

because FF-B is a

negative edge triggered FF.

Q

B

Q

A

= 01................After the first clock pulse

3 After 2nd negative clock

edge

On the arrival of second negative clock edge, FF-A toggles

again and Q

A

= 0.

The change in Q

A

acts as a negative clock edge for FF-B. So

it will also toggle, and Q

B

will be 1.

Q

B

Q

A

= 10................After the second clock pulse

4 After 3rd negative clock

edge

On the arrival of 3rd negative clock edge, FF-A toggles

again and Q

A

become 1 from 0.

Since this is a positive going change,FF-B does not respond

to it and remains inactive. So Q

B

does not change and

continues to be equal to 1.

Q

B

Q

A

= 11................After the third clock pulse

5 After 4th negative clock

edge

On the arrival of 4th negative clock edge, FF-A toggles

again and Q

A

become 1 from 0.

This negative change in Q

A

acts as clock pulse for FF-B.

Hence it toggles to change Q

B

from 1 to 0.

Q

B

Q

A

= 00................After the fourth clock pulse

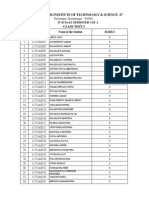

Truth Table

Synchronous counters

If the "clock" pulses are applied to all the flip-flops in a counter simultaneously, then such a counter is called as

synchronous counter.

2-bit Synchronous up counter

The J

A

and K

A

inputs of FF-A are tied to logic 1. So FF-A will work as a toggle flip-flop. The J

B

and K

B

inputs are

connected to Q

A

.

Logical Diagram

Operation

S.N. Condition Operation

1 Initially let both the FFs

be in the reset state

Q

B

Q

A

= 00................initially

2 After 1st negative clock

edge

As soon as the first negative clock edge is applied, FF-A will

toggle and Q

A

will change from 0 to 1.

But at the instant of application of negative clock edge, Q

A

,J

B

= K

B

=0 Hence FF-B will not change its state. So Q

B

will

remain 0.

Q

B

Q

A

= 01................After the first clock pulse

3 After 2nd negative clock

edge

On the arrival of second negative clock edge, FF-A toggles

again and Q

A

change from 1 to 0.

But at this instant Q

A

was 1. So J

B

= K

B

=1 and FF-B will

toggle. Hence Q

B

changes from 0 to 1.

Q

B

Q

A

= 10................After the second clock pulse

4 After 3rd negative clock

edge

On application of the third falling clock edge, FF-A will toggle

from 0 to 1 but there is no change of state for FF-B.

Q

B

Q

A

= 11................After the third clock pulse

5 After 4th negative clock

edge

On application of the next clock pulse, Q

A

will change from 1

to 0 as Q

B

will also change from 1 to 0.

Q

B

Q

A

= 00................After the fourth clock pulse

Classification of counters

Depending on the way in which the counting progresses, the synchronous or asynchronous counters are

Depending on the way in which the counting progresses, the synchronous or asynchronous counters are

classified as follows.

Up counters

Down counters

Up/Down counters

UP/DOWN Counter

In the up/down counter, when up counter and down counter combined together to obtain an UP/DOWN counter.

A mode control (M) input is also provided to select either up or down mode. A combinational circuit is required to

be designed and used between each pair of flip-flop in order to achieve the up/down operation.

Type of up/down counters

UP/DOWN ripple counters

UP/DOWN synchronous counters

UP/DOWN Ripple Counters

In the UP/DOWN ripple counter all the FFs operate in the toggle mode. So either T flip-flops or JK flip-flops

are to be used. The LSB flip-flop receives clock directly. But the clock to every other FF is obtained from (Q = Q

bar) output of the previous FF.

UP counting mode (M=0) - The Q output of the preceding FF is connected to the clock of the next

stage if up counting is to be achieved. For this mode, the mode select input M is at logic 0 (M=0).

DOWN counting mode (M=1) - If M =1, then the Q bar output of the preceding FF is connected to

the next FF. This will operate the counter in the counting mode.

Example

3-bit binary up/down ripple counter.

3-bit : hence three FFs are required.

UP/DOWN : So a mode control input is essential.

For a ripple up counter, the Q output of preceding FF is connected to the clock input of the next one.

For a ripple up counter, the Q output of preceding FF is connected to the clock input of the next one.

For a ripple down counter, the Q bar output of preceding FF is connected to the clock input of the next

one.

Let the selection of Q and Q bar output of the preceding FF be controlled by the mode control input M

such that, If M = 0, UP counting. So connect Q to CLK. If M = 1, DOWN counting. So connect Q bar to

CLK

Block Diagram

Truth Table

Operation

S.N. Condition Operation

1 Case 1: With M = 0 (Up

counting mode)

If M = 0 and M bar = 1, then the AND gates 1 and 3 in fig. will

be enabled whereas the AND gates 2 and 4 will be disabled.

Hence Q

A

gets connected to the clock input of FF-B and Q

B

gets connected to the clock input of FF-C.

These connections are same as those for the normal up

counter. Thus with M = 0 the circuit work as an up counter.

2 Case 2: With M = 1

(Down counting mode)

If M = 1, then AND gates 2 and 4 in fig. are enabled whereas

the AND gates 1 and 3 are disabled.

Hence Q

A

bar gets connected to the clock input of FF-B and

Q

B

bar gets connected to the clock input of FF-C.

These connections will produce a down counter. Thus with M

= 1 the circuit works as a down counter.

Modulus Counter (MOD-N Counter)

The 2-bit ripple counter is called as MOD-4 counter and 3-bit ripple counter is called as MOD-8 counter. So in

general, an n-bit ripple counter is called as modulo-N counter. Where,MOD number = 2

n

Type of modulus

2-bit up or down (MOD-4)

3-bit up or down (MOD-8)

4-bit up or down (MOD-16)

Application of the counters

Frequency counters

Digital clock

Time measurement

A to D converter

Frequency divider circuits

Digital triangular wave generator

Anda mungkin juga menyukai

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeDari EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifePenilaian: 4 dari 5 bintang4/5 (5794)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreDari EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You ArePenilaian: 4 dari 5 bintang4/5 (1090)

- Never Split the Difference: Negotiating As If Your Life Depended On ItDari EverandNever Split the Difference: Negotiating As If Your Life Depended On ItPenilaian: 4.5 dari 5 bintang4.5/5 (838)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceDari EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RacePenilaian: 4 dari 5 bintang4/5 (895)

- Grit: The Power of Passion and PerseveranceDari EverandGrit: The Power of Passion and PerseverancePenilaian: 4 dari 5 bintang4/5 (588)

- Shoe Dog: A Memoir by the Creator of NikeDari EverandShoe Dog: A Memoir by the Creator of NikePenilaian: 4.5 dari 5 bintang4.5/5 (537)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersDari EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersPenilaian: 4.5 dari 5 bintang4.5/5 (344)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureDari EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FuturePenilaian: 4.5 dari 5 bintang4.5/5 (474)

- Her Body and Other Parties: StoriesDari EverandHer Body and Other Parties: StoriesPenilaian: 4 dari 5 bintang4/5 (821)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Dari EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Penilaian: 4.5 dari 5 bintang4.5/5 (121)

- The Emperor of All Maladies: A Biography of CancerDari EverandThe Emperor of All Maladies: A Biography of CancerPenilaian: 4.5 dari 5 bintang4.5/5 (271)

- The Little Book of Hygge: Danish Secrets to Happy LivingDari EverandThe Little Book of Hygge: Danish Secrets to Happy LivingPenilaian: 3.5 dari 5 bintang3.5/5 (399)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyDari EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyPenilaian: 3.5 dari 5 bintang3.5/5 (2259)

- The Yellow House: A Memoir (2019 National Book Award Winner)Dari EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Penilaian: 4 dari 5 bintang4/5 (98)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaDari EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaPenilaian: 4.5 dari 5 bintang4.5/5 (266)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryDari EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryPenilaian: 3.5 dari 5 bintang3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnDari EverandTeam of Rivals: The Political Genius of Abraham LincolnPenilaian: 4.5 dari 5 bintang4.5/5 (234)

- On Fire: The (Burning) Case for a Green New DealDari EverandOn Fire: The (Burning) Case for a Green New DealPenilaian: 4 dari 5 bintang4/5 (73)

- Digital System Designs and Practices: Using Verilog HDL and FpgasDokumen14 halamanDigital System Designs and Practices: Using Verilog HDL and FpgasHarold WilsonBelum ada peringkat

- The Unwinding: An Inner History of the New AmericaDari EverandThe Unwinding: An Inner History of the New AmericaPenilaian: 4 dari 5 bintang4/5 (45)

- Rise of ISIS: A Threat We Can't IgnoreDari EverandRise of ISIS: A Threat We Can't IgnorePenilaian: 3.5 dari 5 bintang3.5/5 (137)

- Atlas v2Dokumen288 halamanAtlas v2Ashok GadhwalBelum ada peringkat

- Revised M Tech r13 RegulationsDokumen9 halamanRevised M Tech r13 RegulationsSal ExcelBelum ada peringkat

- Notes 326 Set8Dokumen16 halamanNotes 326 Set8Bakshi AmitBelum ada peringkat

- Question Bank Iii Semester BtechDokumen18 halamanQuestion Bank Iii Semester BtechHarold WilsonBelum ada peringkat

- ELE2120 Digital Circuits and Systems: Tutorial Note 7Dokumen19 halamanELE2120 Digital Circuits and Systems: Tutorial Note 7Harold Wilson100% (1)

- STLD Bits & Exercise Problems Unit-IVDokumen5 halamanSTLD Bits & Exercise Problems Unit-IVHarold WilsonBelum ada peringkat

- FGDFGFDokumen5 halamanFGDFGFHarold WilsonBelum ada peringkat

- ECAD and VLSI Lab ManualDokumen107 halamanECAD and VLSI Lab ManualHarold WilsonBelum ada peringkat

- Flip-Flops & Sequential CircuitsDokumen7 halamanFlip-Flops & Sequential Circuitsmanishbhardwaj8131Belum ada peringkat

- STLD Question Bank Unit I 1: (RR, R05, Nov 08SET II, III)Dokumen16 halamanSTLD Question Bank Unit I 1: (RR, R05, Nov 08SET II, III)Harold WilsonBelum ada peringkat

- Vlsi TD I Mtech I Sem II Mid Vlsi Es DsceDokumen2 halamanVlsi TD I Mtech I Sem II Mid Vlsi Es DsceHarold WilsonBelum ada peringkat

- EceDokumen12 halamanEcesrijha9Belum ada peringkat

- FGDFGFDokumen5 halamanFGDFGFHarold WilsonBelum ada peringkat

- Karnaugh MapsDokumen9 halamanKarnaugh MapsshijinbgopalBelum ada peringkat

- Eca Lab ManualDokumen56 halamanEca Lab Manualtnj_sundarBelum ada peringkat

- Kavitha.p Ece Asst ProfDokumen2 halamanKavitha.p Ece Asst ProfHarold WilsonBelum ada peringkat

- TSGENCO Recruitment 2015Dokumen2 halamanTSGENCO Recruitment 2015Sarepalli NaveenBelum ada peringkat

- Computer Organization May 2008 Question PaperDokumen4 halamanComputer Organization May 2008 Question Paperelimelek100% (1)

- Antennas and Wave PropagationDokumen2 halamanAntennas and Wave PropagationHarold WilsonBelum ada peringkat

- ECE 4514 Digital Design II Spring 2008 Functions and Tasks: A Language LectureDokumen27 halamanECE 4514 Digital Design II Spring 2008 Functions and Tasks: A Language LectureHarold WilsonBelum ada peringkat

- Analog CommunicationsDokumen8 halamanAnalog CommunicationsHarold WilsonBelum ada peringkat

- Nominal Rolls Cse A & B 3 Class TestDokumen4 halamanNominal Rolls Cse A & B 3 Class TestHarold WilsonBelum ada peringkat

- Veltech PG Vlsi RegCDokumen43 halamanVeltech PG Vlsi RegCtiitumaBelum ada peringkat

- Kavitha.p Ece Asst ProfDokumen2 halamanKavitha.p Ece Asst ProfHarold WilsonBelum ada peringkat

- ECE 4514 Digital Design II Spring 2008 Timing Analysis and Timed SimulationDokumen49 halamanECE 4514 Digital Design II Spring 2008 Timing Analysis and Timed SimulationHarold WilsonBelum ada peringkat

- Batch-3 First Contact PGMDokumen58 halamanBatch-3 First Contact PGMHarold WilsonBelum ada peringkat

- Frequently Asked Questions On PGEC/PGECET AdmissionsDokumen1 halamanFrequently Asked Questions On PGEC/PGECET AdmissionsHarold WilsonBelum ada peringkat

- Introduction To Verilog (Dr. Vu)Dokumen183 halamanIntroduction To Verilog (Dr. Vu)htnguyen304Belum ada peringkat

- List of Helpline Centers: S.No Name of The Help Line CentreDokumen1 halamanList of Helpline Centers: S.No Name of The Help Line CentreHarold WilsonBelum ada peringkat

- Phase-I Admissions: Admission Schedule PGECET-2014Dokumen1 halamanPhase-I Admissions: Admission Schedule PGECET-2014Harold WilsonBelum ada peringkat

- 28C64Dokumen19 halaman28C64Muhammad Yunus AndrianBelum ada peringkat

- Owner's Manual & Installation Instructions: Remote Strobe PacksDokumen11 halamanOwner's Manual & Installation Instructions: Remote Strobe PacksPatrick HermanBelum ada peringkat

- Advance Semiconductor DevicesDokumen4 halamanAdvance Semiconductor DevicesShubhi SinghBelum ada peringkat

- ARM7 UM10139 - LPC214xDokumen354 halamanARM7 UM10139 - LPC214xnilmak2u2Belum ada peringkat

- WS/WE24-2B430: Compact Photoelectric SensorsDokumen7 halamanWS/WE24-2B430: Compact Photoelectric SensorsedwinBelum ada peringkat

- 20W LED Tube (1) .CompressedDokumen8 halaman20W LED Tube (1) .CompressedRamya RBelum ada peringkat

- Tcd650bx Service ManulDokumen79 halamanTcd650bx Service ManulcvijovicBelum ada peringkat

- TDA7442Dokumen16 halamanTDA7442gaston30-3@Belum ada peringkat

- Chameleon ChipDokumen27 halamanChameleon ChipJanu GeethakumariBelum ada peringkat

- VACC VibrationInResearchSettingsDokumen1 halamanVACC VibrationInResearchSettingsrernitmcBelum ada peringkat

- 508 - Asco 7000 Series - Operator's Manual-381333 - 283bDokumen10 halaman508 - Asco 7000 Series - Operator's Manual-381333 - 283bGeorge AsuncionBelum ada peringkat

- LINEAR INTEGRATED CIRCUITS AND APPLICATIONS (2 Marks)Dokumen16 halamanLINEAR INTEGRATED CIRCUITS AND APPLICATIONS (2 Marks)Gokul G-Factor Kumar100% (5)

- Reconfigurable AntennasDokumen74 halamanReconfigurable Antennassasinnn100% (1)

- Ac & DC CurrentDokumen11 halamanAc & DC CurrentAniketBelum ada peringkat

- Manual Tecnico DWC-300MDokumen52 halamanManual Tecnico DWC-300Msting30Belum ada peringkat

- R S Flipflop With PR and CRDokumen3 halamanR S Flipflop With PR and CRAshok Ekanath KalangeBelum ada peringkat

- High-Side Power Distribution Switch: Features General DescriptionDokumen1 halamanHigh-Side Power Distribution Switch: Features General DescriptionRafael Roel Robles BaezBelum ada peringkat

- EEE 53 NotesDokumen11 halamanEEE 53 NotesmiuhasdaBelum ada peringkat

- Applications - Wavelength Tunable LedDokumen6 halamanApplications - Wavelength Tunable LedkingboyBelum ada peringkat

- CCM Boost PFC Converter ReviewDokumen18 halamanCCM Boost PFC Converter ReviewМилан ЛукићBelum ada peringkat

- 1 Low-Voltage Current-Mode Analog Cells Mohit Kumar Iit Bomb Ay 2002Dokumen16 halaman1 Low-Voltage Current-Mode Analog Cells Mohit Kumar Iit Bomb Ay 2002jaigodaraBelum ada peringkat

- Centralized Mobile Detection in Examination Hall Using Arduino PDFDokumen14 halamanCentralized Mobile Detection in Examination Hall Using Arduino PDFAkhil.PitlaBelum ada peringkat

- APM9435Dokumen5 halamanAPM9435ivangunawan71Belum ada peringkat

- 2SC1586 PDFDokumen3 halaman2SC1586 PDFisaiasvaBelum ada peringkat

- NDBDokumen58 halamanNDBSumindak GultomBelum ada peringkat

- 2he PDFDokumen188 halaman2he PDFnbr67sceBelum ada peringkat

- Ternary Circuits: Why R 3 Is Not The Optimal Radix For ComputationDokumen9 halamanTernary Circuits: Why R 3 Is Not The Optimal Radix For ComputationAlex LaiknBelum ada peringkat

- BECE Module-1 NOTESDokumen28 halamanBECE Module-1 NOTESmahendra naik100% (5)

- User Manual PVM ControllerDokumen32 halamanUser Manual PVM Controllerpram29cBelum ada peringkat