Laboratorio de Electrónica Digital

Diunggah oleh

Cristian Sanchez Vargas0 penilaian0% menganggap dokumen ini bermanfaat (0 suara)

31 tayangan10 halamanEste documento presenta el diseño de un circuito lógico multiplicador de 4 bits. Describe los objetivos, marco teórico, materiales, problema y procedimiento para diseñar el circuito. Se realiza la tabla de verdad del multiplicador y los cálculos lógicos para cada salida mediante álgebra de Boole. Finalmente, se muestran los diagramas de bloques y esquemático del circuito diseñado.

Deskripsi Asli:

Hak Cipta

© © All Rights Reserved

Format Tersedia

DOCX, PDF, TXT atau baca online dari Scribd

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniEste documento presenta el diseño de un circuito lógico multiplicador de 4 bits. Describe los objetivos, marco teórico, materiales, problema y procedimiento para diseñar el circuito. Se realiza la tabla de verdad del multiplicador y los cálculos lógicos para cada salida mediante álgebra de Boole. Finalmente, se muestran los diagramas de bloques y esquemático del circuito diseñado.

Hak Cipta:

© All Rights Reserved

Format Tersedia

Unduh sebagai DOCX, PDF, TXT atau baca online dari Scribd

0 penilaian0% menganggap dokumen ini bermanfaat (0 suara)

31 tayangan10 halamanLaboratorio de Electrónica Digital

Diunggah oleh

Cristian Sanchez VargasEste documento presenta el diseño de un circuito lógico multiplicador de 4 bits. Describe los objetivos, marco teórico, materiales, problema y procedimiento para diseñar el circuito. Se realiza la tabla de verdad del multiplicador y los cálculos lógicos para cada salida mediante álgebra de Boole. Finalmente, se muestran los diagramas de bloques y esquemático del circuito diseñado.

Hak Cipta:

© All Rights Reserved

Format Tersedia

Unduh sebagai DOCX, PDF, TXT atau baca online dari Scribd

Anda di halaman 1dari 10

Universidad de Pamplona - Ciudad Universitaria - Pamplona (Norte de Santander - Colombia)

Tels: (7) 5685303 - 5685304 - 5685305 Fax: 5682750 www.unipamplona.edu.co

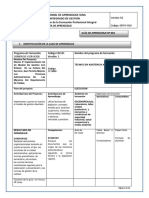

LABORATORIO DE ELECTRNICA DIGITAL

PRACTICA 1.

DISEO DE CIRCUITOS LOGICOS COMBINACIONALES

CRISTIAN ANDRES SNCHEZ VARGAS

COD. 89053153381

DIEGO FERNANDO MORA ARVALO

COD. 89113062186

HECTOR LISANDRO GARCA

COD. 1099204785

PRESENTADO A:

ING.ESP. BLANCA JUDITH CRISTANCHO

UNIVERSIDAD DE PAMPLONA

FACULTAD DE INGENIERIAS Y ARQUITECTURA

ELECTRONICA DIGITAL

PAMPLONA, NORTE DE SANTANDER

2009

Universidad de Pamplona - Ciudad Universitaria - Pamplona (Norte de Santander - Colombia)

Tels: (7) 5685303 - 5685304 - 5685305 Fax: 5682750 www.unipamplona.edu.co

PRACTICA 1.

DISEO DE CIRCUITOS LOGICOS COMBINACIONALES

OBJETIVOS:

Reconocer, utilizar y conjugar cada uno de los dispositivos vistos

en el desarrollo de la materia, para disear circuitos lgicos

combinatorios con el fin de solucionar problemas de forma eficiente

y econmica.

Disear, analizar y comprender la tabla de verdad para este tipo de

circuitos lgicos.

Aplicar y realizar los clculos lgicos por medio de el algebra de

boole.

MARCO TERICO

Configuracin de un interruptor lgico:

Numeracin de pines de un circuito integrado: todos los circuitos

integrados tienen una muesca o marca, la cual se utiliza para

identificar los pines,

Universidad de Pamplona - Ciudad Universitaria - Pamplona (Norte de Santander - Colombia)

Tels: (7) 5685303 - 5685304 - 5685305 Fax: 5682750 www.unipamplona.edu.co

proceso que se lleva a cabo de la siguiente manera: tome el

integrado ubique la muesca hacia arriba y numere los pines

iniciando por el que se encuentra a la izquierda y continu en forma

de u, como lo muestra la figura.

MATERIALES:

Circuitos integrados TTL o CMOS (Compuertas lgicas AND,

NOR, NOT, NOR, NAND, las necesarias segn su diseo)

Protoboard

Resistencias 220

Leds

Interruptores

Universidad de Pamplona - Ciudad Universitaria - Pamplona (Norte de Santander - Colombia)

Tels: (7) 5685303 - 5685304 - 5685305 Fax: 5682750 www.unipamplona.edu.co

PROBLEMA

La Figura representa un circuito multiplicador que toma dos nmeros

binarios X

0

X

1

y Y

0

Y

1

y produce un numero binario de salida Z

0

Z

1

Z

2

Z

3

,

igual al producto aritmtico de los dos nmeros de entrada. Disee un

circuito lgico para el multiplicador, mediante lgebra booleana. Las

variables X

0

Y

0

Z

0

, son LSB.

TCNICA OPERATORIA.

1. Realice el diseo de la solucin del problema propuesto, utilizando

lgebra de boole atendiendo las indicaciones y procedimientos visto

en clase.

2. Grafique el diagrama esquemtico.

3. Realice el montaje del circuito obtenido en el punto anterior,

colocando un led por cada bit, teniendo en cuenta utilizar un lerd de

otro color para el bit menos significativo. Conecte la fuente de

alimentacin, teniendo cuidado de empalmar tierra con tierra y

VCC con VCC, compruebe el funcionamiento del circuito mediante

la tabla de verdad.

CIRCUITO

MULTIPLICAD

OR

X

0

X

1

Y

0

Y

1

Z

2

Z

3

Z

0

Z

1

Universidad de Pamplona - Ciudad Universitaria - Pamplona (Norte de Santander - Colombia)

Tels: (7) 5685303 - 5685304 - 5685305 Fax: 5682750 www.unipamplona.edu.co

PROCEDIMIENTO

Tabla de verdad:

X

0

X

1

Y

0

Y

1

0 0 0 0

0 0 0 1

0 0 1 0

0 0 1 1

0 1 0 0

0 1 0 1

0 1 1 0

0 1 1 1

1 0 0 0

1 0 0 1

1 0 1 0

1 0 1 1

1 1 0 0

1 1 0 1

1 1 1 0

1 1 1 1

Z

3

Z

2

Z

1

Z

0

0 0 0 0

0 0 0 0

0 0 0 0

0 0 0 0

0 0 0 0

0 0 0 1

0 0 1 0

0 0 1 1

0 0 0 0

0 0 1 0

0 1 0 0

0 1 1 0

0 0 0 0

0 0 1 1

0 1 1 0

1 0 0 1

Universidad de Pamplona - Ciudad Universitaria - Pamplona (Norte de Santander - Colombia)

Tels: (7) 5685303 - 5685304 - 5685305 Fax: 5682750 www.unipamplona.edu.co

Donde:

Z

3

=

X1X0Y1Y0

Z

2

=X1X0Y1Y0+ X1X0Y1Y0 + X1X0Y1Y0

Z

2

=X1X0Y1(YO+Y0)+X1XOY1Y0

Z

2

=X1X0Y1+ X1XOY1Y0

Z

2

=X1Y1(XO+XOY0)

Z

2

=X1Y1XO+Y0X1Y1

Z

1

=X1X0Y1Y0+X1X0Y1Y0+X11X0Y1Y0+X1X0Y1Y0+X1X0Y1

Y0+X1X0Y1Y0

Z

1

=X1X0Y1(YO+Y0)+X1YOXO(Y1+Y1)+X1(X0Y1Y0+X0Y1Y0)

Z

1

=X1X0Y1+X1Y0X0+X1X0Y1Y0+X1X0Y1Y0

Z

1

=X1Y0(X0+X0Y1)+X0Y1(X1+X1Y0)

Z

1

=X1Y08X0+Y1)+X0Y1(X1+Y0)

Z

1

=X1Y0X0+X1Y0Y1+X0Y1X1+Y0X0Y1

Z

0

=X1X0Y1Y0+X1X0Y1Y0+X1X0Y1Y0+X1X0Y1Y0

Z

0

=X1X0Y0(Y1+Y1)+X1X0Y0(Y1+Y1)

Z

0

=X0Y0(X1+X1)

Z

0

=X0Y0

Universidad de Pamplona - Ciudad Universitaria - Pamplona (Norte de Santander - Colombia)

Tels: (7) 5685303 - 5685304 - 5685305 Fax: 5682750 www.unipamplona.edu.co

DIAGRAMA DE BLOQUES

A

B

C

D

Y

1

X

1

X

0

Y

0

Z

0

Z

1

Z

2

Z

3

Universidad de Pamplona - Ciudad Universitaria - Pamplona (Norte de Santander - Colombia)

Tels: (7) 5685303 - 5685304 - 5685305 Fax: 5682750 www.unipamplona.edu.co

DIAGRAMA ESQUEMATICO

Z

0

=

Z

1

=

Z

2

=

Universidad de Pamplona - Ciudad Universitaria - Pamplona (Norte de Santander - Colombia)

Tels: (7) 5685303 - 5685304 - 5685305 Fax: 5682750 www.unipamplona.edu.co

Z

3

=

DIAGRAMA FINAL DEL CIRCUITO:

Universidad de Pamplona - Ciudad Universitaria - Pamplona (Norte de Santander - Colombia)

Tels: (7) 5685303 - 5685304 - 5685305 Fax: 5682750 www.unipamplona.edu.co

Anda mungkin juga menyukai

- P3 Satuquinga Evelin ContadoresDokumen15 halamanP3 Satuquinga Evelin ContadoresEvelin SatuquingaBelum ada peringkat

- Informe 5 - Decodificadores - Circuitos DigitalesDokumen3 halamanInforme 5 - Decodificadores - Circuitos DigitalesBrenda CastilloBelum ada peringkat

- Circuito ElevadorDokumen17 halamanCircuito ElevadorFelipe Perez PeñaBelum ada peringkat

- Informe 8Dokumen8 halamanInforme 8Alejandro FernándezBelum ada peringkat

- Previo de La Practica 7 de Sistemas Digitales (FESC-C4)Dokumen10 halamanPrevio de La Practica 7 de Sistemas Digitales (FESC-C4)Jesús GarcíaBelum ada peringkat

- PARQUEADERODokumen16 halamanPARQUEADEROCristianCamiloHernandezSuarez100% (1)

- Informe Digitales 3Dokumen18 halamanInforme Digitales 3MiguelAngelOchoaBolanosBelum ada peringkat

- Informe Previo Microelectronica 02Dokumen14 halamanInforme Previo Microelectronica 02Eleazar CastilloBelum ada peringkat

- Multiplexor y DemultiplexorDokumen12 halamanMultiplexor y DemultiplexorSigur Svenska100% (7)

- Fase 4 Grupo 61Dokumen31 halamanFase 4 Grupo 61Umo ComunicacionesBelum ada peringkat

- Decodificador Exceso 3 A BCDDokumen8 halamanDecodificador Exceso 3 A BCDManuel UribeBelum ada peringkat

- PRACTICA 11 CONTADORES BINARIOSeditDokumen12 halamanPRACTICA 11 CONTADORES BINARIOSeditJoaquín RivasBelum ada peringkat

- Previo 4 DigitalesDokumen15 halamanPrevio 4 DigitalesHarold Cruz SalasBelum ada peringkat

- Semana 5 - LeccionesDokumen78 halamanSemana 5 - LeccionesPROJECTMADBelum ada peringkat

- Contador BinarioDokumen8 halamanContador BinarioOzkar LlergoBelum ada peringkat

- Examen Practico U1 FinalDokumen14 halamanExamen Practico U1 FinalRamón McCartneyBelum ada peringkat

- Laboratorio Puente HDokumen10 halamanLaboratorio Puente Hjulio cesar mendozaBelum ada peringkat

- Tarea DomiciliariaDokumen26 halamanTarea DomiciliariaAndy1902100% (2)

- Laboratorio de Sistemas Digitales 6Dokumen14 halamanLaboratorio de Sistemas Digitales 6ian barrigaBelum ada peringkat

- Circuitos Integrados SumadorDokumen8 halamanCircuitos Integrados SumadorBal HdezBelum ada peringkat

- Lab 6 - Micro Nano Sistemas ElectrónicosDokumen25 halamanLab 6 - Micro Nano Sistemas ElectrónicosGabriel Hostiliano CoblentzBelum ada peringkat

- Informe 6 Circuitos DigitalesDokumen8 halamanInforme 6 Circuitos Digitalesnoe luna venturoBelum ada peringkat

- Circuitos DigitalesDokumen20 halamanCircuitos DigitalesJOAQUIN ALESSANDRO CABRERA CHAMORROBelum ada peringkat

- DARLIGTONDokumen16 halamanDARLIGTONDarney aguasBelum ada peringkat

- Labotatorio TinkercadDokumen12 halamanLabotatorio TinkercadLuis VargasBelum ada peringkat

- Informe LogicaDokumen8 halamanInforme LogicaYasert PerezBelum ada peringkat

- Tarea Extra Clases "Medición y Diagnóstico de Circuitos Eléctricos", Esquema y Simulación.Dokumen14 halamanTarea Extra Clases "Medición y Diagnóstico de Circuitos Eléctricos", Esquema y Simulación.Danilo BohórquezBelum ada peringkat

- Reloj Digital Con Flip Flop JK - Ing. Bruss Roman HuertaDokumen18 halamanReloj Digital Con Flip Flop JK - Ing. Bruss Roman HuertahalfordBelum ada peringkat

- Multiplexor y DemultiplexorDokumen13 halamanMultiplexor y DemultiplexorIvOn HerreRaBelum ada peringkat

- Ene-Diego BugueñoDokumen10 halamanEne-Diego Bugueñodiego BuguenoBelum ada peringkat

- Ene 2023 Daniel Flores y Jorge GodoyDokumen11 halamanEne 2023 Daniel Flores y Jorge GodoyPablo BarreraBelum ada peringkat

- 3 - Practica Rectificador de Onda Completa - Filtro CapacitivoDokumen6 halaman3 - Practica Rectificador de Onda Completa - Filtro Capacitivosommer solerBelum ada peringkat

- 3 - Practica Rectificador de Onda Completa - Filtro CapacitivoDokumen6 halaman3 - Practica Rectificador de Onda Completa - Filtro Capacitivosommer solerBelum ada peringkat

- InformeDokumen18 halamanInformeEstrella CarolinqBelum ada peringkat

- PérezHP Practica 06 Display de 7 SegmentosDokumen11 halamanPérezHP Practica 06 Display de 7 SegmentosGabriel Perez HernandezBelum ada peringkat

- Informe Previo N°6Dokumen8 halamanInforme Previo N°6dsdBelum ada peringkat

- Máquina SecuencialDokumen18 halamanMáquina SecuencialCarlos OrozcoBelum ada peringkat

- Tarea 1Dokumen3 halamanTarea 1LUIS CARLOS DURAN RODRIGUEZBelum ada peringkat

- Practica 1 Diseño Digital PDFDokumen25 halamanPractica 1 Diseño Digital PDFRenán GRBelum ada peringkat

- Practica 2 - 2023-1Dokumen12 halamanPractica 2 - 2023-1ulisesBelum ada peringkat

- Sesión 07, Circuitos CombinacionalesDokumen44 halamanSesión 07, Circuitos CombinacionalesDANIEL ANTONIO ENCALADA SALAZARBelum ada peringkat

- Reporte de AlarmaDokumen13 halamanReporte de AlarmaEdilbertoBelum ada peringkat

- Solucion de ExmnDokumen8 halamanSolucion de ExmnDaniel AbantoBelum ada peringkat

- Practica 5 Electronica DigitalDokumen9 halamanPractica 5 Electronica DigitalRodolfo HerreraBelum ada peringkat

- Sesión 15Dokumen17 halamanSesión 15GUSTAVO ALEX DOMINGUEZ JARAMILLOBelum ada peringkat

- Taller - 1 - CorteDokumen2 halamanTaller - 1 - CorteAlberto LizcanoBelum ada peringkat

- Informe Previo 02 - Microelectronica1Dokumen19 halamanInforme Previo 02 - Microelectronica1Sergio MarceloBelum ada peringkat

- INFORME Electrónica DigitalDokumen4 halamanINFORME Electrónica DigitalAlvaro HaroBelum ada peringkat

- Sistemas Digitales - EpisunsaDokumen7 halamanSistemas Digitales - EpisunsaHenrryk LarssonBelum ada peringkat

- Trabajo de Circuitos 1Dokumen5 halamanTrabajo de Circuitos 1- AFCBelum ada peringkat

- Semana VII, AR - 24 - Borrador - Esquema - Proyecto - MultímetroDokumen9 halamanSemana VII, AR - 24 - Borrador - Esquema - Proyecto - Multímetro- AFCBelum ada peringkat

- Tarea 3 IODokumen4 halamanTarea 3 IOCesar Villagra ObandoBelum ada peringkat

- Saber Electronica 002Dokumen64 halamanSaber Electronica 002parascoli100% (5)

- Trabajo Práctico #6 FINALDokumen34 halamanTrabajo Práctico #6 FINALANTHONY VALENCIA ZUTABelum ada peringkat

- Anexo 3. Sistema de Puesta A TierraDokumen12 halamanAnexo 3. Sistema de Puesta A TierraCristian Sanchez VargasBelum ada peringkat

- Construccion de Corrales en El Municipio de Fortul Departamento de AraucaDokumen36 halamanConstruccion de Corrales en El Municipio de Fortul Departamento de AraucaCristian Sanchez VargasBelum ada peringkat

- Anexo 1. Descargas AtmosfericasDokumen4 halamanAnexo 1. Descargas AtmosfericasCristian Sanchez VargasBelum ada peringkat

- Alameda La PazDokumen1 halamanAlameda La PazCristian Sanchez VargasBelum ada peringkat

- Informe de Avance de Obra Doble CalzadaDokumen7 halamanInforme de Avance de Obra Doble CalzadaCristian Sanchez VargasBelum ada peringkat

- Anexo 4. Puesta A TierraDokumen12 halamanAnexo 4. Puesta A TierraCristian Sanchez VargasBelum ada peringkat

- OFICIO 02-06-22 RespuestaDokumen3 halamanOFICIO 02-06-22 RespuestaCristian Sanchez VargasBelum ada peringkat

- 1015209809Dokumen129 halaman1015209809Cristian Sanchez VargasBelum ada peringkat

- Anexo 3. Riesgo ElectricoDokumen10 halamanAnexo 3. Riesgo ElectricoCristian Sanchez VargasBelum ada peringkat

- Planodeplanta 1 PlantaPrimerPiso Modelo PDFDokumen1 halamanPlanodeplanta 1 PlantaPrimerPiso Modelo PDFCristian Sanchez VargasBelum ada peringkat

- Sistema General de Regalías SGR Verificación de Requisitos en ProyectosDokumen2 halamanSistema General de Regalías SGR Verificación de Requisitos en ProyectosCristian Sanchez VargasBelum ada peringkat

- Diseño Electrico de Malla de Encerramiento Industrial Subestacion Banadia HD (Tda)Dokumen23 halamanDiseño Electrico de Malla de Encerramiento Industrial Subestacion Banadia HD (Tda)Cristian Sanchez VargasBelum ada peringkat

- Instalacion de Puestas A Tierra TemporalDokumen4 halamanInstalacion de Puestas A Tierra TemporalCristian Sanchez VargasBelum ada peringkat

- Levantamiento de Una Poligonal Cerrada Con Cinta y Jalo Metodo de Las CuerdasDokumen9 halamanLevantamiento de Una Poligonal Cerrada Con Cinta y Jalo Metodo de Las CuerdasMarco Cotrina TeatinoBelum ada peringkat

- Atmega16 Contadores y TemporizadoresDokumen12 halamanAtmega16 Contadores y TemporizadoresRick HunterBelum ada peringkat

- AI LA 03890S999 XX 2011Dokumen14 halamanAI LA 03890S999 XX 2011edwardBelum ada peringkat

- Aplicaciones Moviles Con KIVYDokumen15 halamanAplicaciones Moviles Con KIVYAlexander RamirezBelum ada peringkat

- Ejercicio Clases en Java Introduc A La ProgramacionDokumen2 halamanEjercicio Clases en Java Introduc A La ProgramacionKalethistas MonteriaBelum ada peringkat

- Trabajando Con LiDAR en FUSIONDokumen13 halamanTrabajando Con LiDAR en FUSIONPat YqllBelum ada peringkat

- Sem 1Dokumen17 halamanSem 1Nata AcevedoBelum ada peringkat

- Modelo Montecarlo, Back Testing y Stress TestingDokumen4 halamanModelo Montecarlo, Back Testing y Stress TestingMarina Oña CatotaBelum ada peringkat

- 9520 Manual SpanishDokumen98 halaman9520 Manual SpanishArturo Martinez LeonBelum ada peringkat

- PatchDokumen343 halamanPatchDe La O Roman MauricioBelum ada peringkat

- Experimento 2Dokumen3 halamanExperimento 2Ruben BarriaBelum ada peringkat

- Bnc-Ps-Reqts-Mobilization Activation Debitcard Funds FCDokumen1 halamanBnc-Ps-Reqts-Mobilization Activation Debitcard Funds FCdennysBelum ada peringkat

- Formato Veracidad Información Ficha Caracterización PadresDokumen2 halamanFormato Veracidad Información Ficha Caracterización PadresLeidy viviana Gil ramirezBelum ada peringkat

- Como Usar Estacion TotalDokumen5 halamanComo Usar Estacion TotalDiegoGonzales100% (2)

- Examen 2da Unidad - 2013-IDokumen3 halamanExamen 2da Unidad - 2013-ILucas Fabrizzio Moreno AlemanBelum ada peringkat

- Guia - de - Aprendizaje 004Dokumen18 halamanGuia - de - Aprendizaje 004maria nidia gutierrezBelum ada peringkat

- Linux en LatinoamericaDokumen35 halamanLinux en LatinoamericaEMMANUEL BRANDO QUILLA ROMEROBelum ada peringkat

- UNTREF Historia CCC PDFDokumen18 halamanUNTREF Historia CCC PDFSergio Lugo López0% (1)

- Processing ManualDokumen16 halamanProcessing ManualEmmanuel CocomBelum ada peringkat

- Escoffery OnlineDokumen11 halamanEscoffery OnlineAbner Bboy-GohanBelum ada peringkat

- Actividad 1-2083239Dokumen3 halamanActividad 1-2083239fige80Belum ada peringkat

- InterpretaciDokumen22 halamanInterpretaciSofia RodriguezBelum ada peringkat

- Erp Empresa en VentasDokumen16 halamanErp Empresa en VentasMARCO ANTONIO ORTIZ PURIZACABelum ada peringkat

- Tema 2 Actividad 3Dokumen4 halamanTema 2 Actividad 3David Staser ToralBelum ada peringkat

- Delvin PPDokumen5 halamanDelvin PPbaduu artBelum ada peringkat

- La Regla de Calculo - Extincion ProgramadaDokumen7 halamanLa Regla de Calculo - Extincion Programadaloiso2Belum ada peringkat

- Revista Sololinux N29 Junio 2021Dokumen54 halamanRevista Sololinux N29 Junio 2021elfoman123Belum ada peringkat

- Aplicaciones Del Georadar de Subsuelo en ObrasDokumen9 halamanAplicaciones Del Georadar de Subsuelo en ObrasArwin TroconisBelum ada peringkat

- La Administracion y La Colaboracion de Un ProyectoDokumen7 halamanLa Administracion y La Colaboracion de Un ProyectoJosé Luis Méndez PinedaBelum ada peringkat

- M11 U2Dokumen28 halamanM11 U2Meris VelazquezBelum ada peringkat