Mitsubishi Semiconductor Mitsubishi Semiconductor

Diunggah oleh

amired2Judul Asli

Hak Cipta

Format Tersedia

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniHak Cipta:

Format Tersedia

Mitsubishi Semiconductor Mitsubishi Semiconductor

Diunggah oleh

amired2Hak Cipta:

Format Tersedia

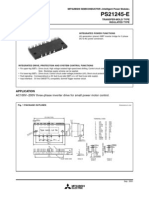

MITSUBISHI SEMICONDUCTOR <Dual-In-Line Package Intelligent Power Module>

PS21767

TRANSFER-MOLD TYPE

INSULATED TYPE

Aug. 2007

1

PS21767

INTEGRATED POWER FUNCTIONS

600V/30A low-loss CSTBT

TM

inverter bridge with N-side

three-phase output DC-to-AC power conversion

APPLICATION

AC100V~200V three-phase inverter drive for small power motor control.

Fig. 1 PACKAGE OUTLINES

INTEGRATED DRIVE, PROTECTION AND SYSTEM CONTROL FUNCTIONS

For upper-leg IGBTS : Drive circuit, High voltage high-speed level shifting, Control supply under-voltage (UV) protection.

For lower-leg IGBTS : Drive circuit, Control supply under-voltage protection (UV), Short circuit protection (SC).

Fault signaling : Corresponding to an SC fault (Lower-leg IGBT) or a UV fault (Lower-side supply).

Input interface : 3, 5V line (High Active)

UL Approved : Yellow Card No. E80276

Dimensions in mm

MITSUBISHI SEMICONDUCTOR <Dual-In-Line Package Intelligent Power Module>

PS21767

TRANSFER-MOLD TYPE

INSULATED TYPE

QR

CODE

1.78 0.2

3.3 0.3

3.3 0.3

6.6 0.3 7.62 0.3 7.62 0.3 7.62 0.3 7.62 0.3

3.95 0.3

2

-

3

.3

5

-

2

.2

(D

E

P

T

H

2

.6

)

A = 1.78 0.2

B = 4.32 0.2 2.04 0.3

3

5

.

9

0

.

5

3.1 0.1

(111.78)

3

1

1

5

.

5

46 0.2 3.25

0.5

3.3

(3.5)

(3.7)

C-C

1.5

1

2

52.5

E

B

7

.

1 1

2

.

7

A

B

A

B

A

B

A

B

5.6

(2.2)

(1.7)

(

2

.

8

)

(

1

3

)

(

1

2

.

7

8

)

(

1

3

.

5

)

F

2

2

.

2

A

1

7

.

7

(

1

.

9

6

)

(

3

.

5

)

(

5

.

5

)

(1)

1.55

HEAT SI NK SI DE

1

.

5

1

7

.

7

0

.

5

0

.

5

C C

D

(2.2)

(1.7)

TERMINAL CODE

(2.9)

(

1

.

7

5

)

(1.6)

(0.75)

(0.6)

(

0

~

5

)

(1)

(

1

)

DETAIL D DETAIL E

VUFS

(UPG)

VUFB

VP1

(COM)

UP

VVFS

(VPG)

VVFB

VP1

(COM)

VP

VWFS

(WPG)

VWFB

VP1

(COM)

WP

(UNG)

VNO

UN

VN

WN

FO

CFO

CIN

VNC

VN1

(WNG)

(VNG)

NW

NV

NU

W

V

U

P

NC

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

28

29

30

31

32 33 34 35 36 37 38

27 26 25 24 23 22 21 201918

17

16 15

14

13 12

11

10 9

8

7 6

5

4 3

2

1

Type name, Lot No.

Note: All outer lead terminals are with lead free solder (Sn-Cu) plating.

MITSUBISHI SEMICONDUCTOR <Dual-In-Line Package Intelligent Power Module>

PS21767

TRANSFER-MOLD TYPE

INSULATED TYPE

Aug. 2007

2

Note 1 : TC measurement point

400

20~+100

40~+125

2500

VD = 13.5~16.5V, Inverter part

Tj = 125C, non-repetitive, less than 2 s

(Note 1)

60Hz, Sinusoidal, AC 1 minute,

All pins to heat-sink plate

VCC(PROT)

Tc

Tstg

Viso

V

V

V

V

mA

V

20

20

0.5~VD+0.5

0.5~VD+0.5

1

0.5~VD+0.5

Applied between VP1-VNC, VN1-VNC

Applied between VUFB-VUFS, VVFB-VVFS,

VWFB-VWFS

Applied between UP, VP, WP, UN, VN, WN-

VNC

Applied between FO-VNC

Sink current at FO terminal

Applied between CIN-VNC

Control supply voltage

Control supply voltage

Input voltage

Fault output supply voltage

Fault output current

Current sensing input voltage

VD

VDB

VIN

VFO

IFO

VSC

450

500

600

30

60

90.9

20~+150

Applied between P-NU, NV, NW

Applied between P-NU, NV, NW

Tc = 25C

Tc = 25C, less than 1ms

Tc = 25C, per 1 chip

VCC

VCC(surge)

VCES

IC

ICP

PC

Tj

Condition Symbol Parameter Ratings Unit

Supply voltage

Supply voltage (surge)

Collector-emitter voltage

Each IGBT collector current

Each IGBT collector current (peak)

Collector dissipation

Junction temperature

V

V

V

A

A

W

C

MAXIMUM RATINGS (Tj = 25C, unless otherwise noted)

INVERTER PART

Condition Symbol Parameter Ratings Unit

CONTROL (PROTECTION) PART

Symbol Ratings Unit

Self protection supply voltage limit

(short circuit protection capability)

Module case operation temperature

Storage temperature

Isolation voltage

V

C

C

Vrms

TOTAL SYSTEM

Parameter Condition

Power Terminals

Tc point

Control Terminals

IGBT Chip position

FWDi Chip position

Groove

18mm

18mm

Heat sink side

DIP-IPM

MITSUBISHI SEMICONDUCTOR <Dual-In-Line Package Intelligent Power Module>

PS21767

TRANSFER-MOLD TYPE

INSULATED TYPE

Aug. 2007

3

2.10

2.20

2.00

1.90

0.80

2.10

0.60

1

10

1.1

2.8

mA

V

Tj = 25C

Tj = 125C

IC = 30A, Tj = 25C

IC = 30A, Tj = 125C

VCE(sat)

VEC

ton

trr

tc(on)

toff

tc(off)

ICES

Condition Symbol Parameter

Limits

Inverter IGBT part (per 1/6 module)

Inverter FWD part (per 1/6 module)

Rth(j-c)Q

Rth(j-c)F

Min.

THERMAL RESISTANCE

Typ. Max.

Unit

Tj = 25C, IC = 30A, VIN = 0V

Condition Symbol Parameter

Limits

Min. Typ. Max.

0.70

Unit

ELECTRICAL CHARACTERISTICS (Tj = 25C, unless otherwise noted)

INVERTER PART

Collector-emitter saturation

voltage

FWDi forward voltage

Junction to case thermal

resistance (Note 2)

VD = VDB = 15V

VIN = 5V

Switching times

VCC = 300V, VD = VDB = 15V

IC = 30A, Tj = 125C, VIN = 0 5V

Inductive load (upper-lower arm)

Collector-emitter cut-off

current

VCE = VCES

1.60

1.70

1.50

1.30

0.30

0.50

1.50

0.40

V

s

s

s

s

s

C/W

C/W

CONTROL (PROTECTION) PART

Note 3: Short circuit protection is functioning only at the low-arms. Please select the external shunt resistance such that the SC trip-level is

less than 2.0 times of the current rating.

4: Fault signal is output when the low-arms short circuit or control supply under-voltage protective functions works. The fault output pulse-

width tFO depends on the capacitance of CFO according to the following approximate equation : CFO = 12.2 10

-6

tFO [F].

Symbol

ID

VFOH

VFOL

VSC(ref)

IIN

UVDBt

UVDBr

UVDt

UVDr

tFO

Vth(on)

Vth(off)

Vth(hys)

Parameter Condition

Limits

Unit

Circuit current

Fault output voltage

Short circuit trip level

Control supply under-voltage

protection

Fault output pulse width

ON threshold voltage

OFF threshold voltage

ON/OFF threshold hysteresis voltage

VD = VDB = 15V

VIN = 5V

Total of VP1-VNC, VN1-VNC

VUFB-VUFS, VVFB-VVFS, VWFB-VWFS

VSC = 0V, FO terminal pull-up to 5V with 10k

VSC = 1V, IFO = 1mA

Tj = 25C, VD = 15V (Note 3)

VIN = 5V

Trip level

Reset level

Trip level

Reset level

CFO = 22nF (Note 4)

Applied between UP, VP, WP, UN, VN, WN-VNC

4.9

0.43

1.0

10.0

10.5

10.3

10.8

1.0

0.8

0.5

0.48

1.5

1.8

2.3

1.4

0.9

7.00

0.55

7.00

0.55

0.95

0.53

2.0

12.0

12.5

12.5

13.0

2.6

Min. Typ. Max.

mA

mA

mA

mA

V

V

V

mA

V

V

V

V

ms

V

V

V

VD = VDB = 15V

VIN = 0V

Total of VP1-VNC, VN1-VNC

VUFB-VUFS, VVFB-VVFS, VWFB-VWFS

Tj 125C

Note 2 : Grease with good thermal conductivity should be applied evenly with about +100m~+200m on the contacting surface of DIP-IPM

and heat-sink.

The contacting thermal resistance between DIP-IPM case and heat sink (Rth(c-f)) is determined by the thickness and the thermal con-

ductivity of the applied grease. For reference, Rth(c-f) (per 1/6 module) is about 0.3C/W when the grease thickness is 20m and the

thermal conductivity is 1.0W/mk

Input current

MITSUBISHI SEMICONDUCTOR <Dual-In-Line Package Intelligent Power Module>

PS21767

TRANSFER-MOLD TYPE

INSULATED TYPE

Aug. 2007

4

Note 5 : Flatness measurement position

Mounting screw : M3

Condition Parameter

Limits

Mounting torque

Weight

Heat-sink flatness

Min.

MECHANICAL CHARACTERISTICS AND RATINGS

Typ. Max.

0.59

50

Unit

21

0.98

100

Nm

g

m

Recommended : 0.78 Nm

(Note 5)

V

V

V

V/s

s

kHz

Arms

s

V

C

Supply voltage

Control supply voltage

Control supply voltage

Control supply variation

Arm shoot-through blocking time

PWM input frequency

Output r.m.s. current

Minimum input

pulse width

VNC voltage variation

Junction temperature

Applied between P-NU, NV, NW

Applied between VP1-VNC, VN1-VNC

Applied between VUFB-VUFS, VVFB-VVFS, VWFB-VWFS

For each input signal, Tc 100C

Tc 100C, Tj 125C

VCC = 300V, VD = VDB = 15V,

P.F = 0.8, sinusoidal PWM

Tc 100C, Tj 125C (Note 6)

(Note 7)

200 VCC 350V,

13.5 VD 16.5V,

13.0 VDB 18.5V,

20C Tc 100C,

N-line wiring inductance less

than 10nH (Note 8)

Between VNC-NU, NV, NW (including surge)

400

16.5

18.5

1

20

21

16

5.0

125

VCC

VD

VDB

VD, VDB

tdead

fPWM

IO

PWIN(on)

PWIN(off)

VNC

Tj

Condition Symbol Parameter

Recommended value

Min. Typ. Max.

0

13.5

13.0

1

2

0.3

1.5

3.0

3.6

5.0

20

Unit

RECOMMENDED OPERATION CONDITIONS

300

15.0

15.0

Note 6: The allowable r.m.s. current value depends on the actual application conditions.

7: Input signal with ON pulse width less than PWIN(on) might make no response.

8: IPM might make delayed response (less than about 2sec) or no response for the input signal with off pulse width less than PWIN(off).

Please refer Fig. 2 about delayed response and Fig. 6 about N-line inductance.

fPWM = 5kHz

fPWM = 15kHz

Below rated current

Between rated current and

1.7 times of rated current

Between 1.7 ti mes and

2.0 times of rated current

Heat sink side

Measurement position

3mm

Heat sink side

+

+

MITSUBISHI SEMICONDUCTOR <Dual-In-Line Package Intelligent Power Module>

PS21767

TRANSFER-MOLD TYPE

INSULATED TYPE

Aug. 2007

5

Fig. 2 ABOUT DELAYED RESPONSE AGAINST SHORTER INPUT OFF SIGNAL THAN PWIN (off) (P side only)

Fig. 3 THE DIP-IPM INTERNAL CIRCUIT

t1 t2

Real line

...

off pulse width > PWIN(off) : turn on time t1

Broken line

...

off pulse width < PWIN(off) : turn on time t2

P side control input

Internal IGBT gate

Output current Ic

DIP-IPM

UOUT

VOUT

WOUT

VNO

CFO

GND

WN

VN

UN

VCC

HVIC3

HVIC2

HVIC1

LVIC

CFO CIN

CIN

VNO

W

V

U

P

HO IN

COM

VB

VS

VCC

HO IN

COM

VB

VS

VCC

HO IN

COM

VB

VS

VCC

WN

VN

UN

VP

VP

UP

VNC

VN1

VP1

VP1

VP1

VWFS

VVFS

VUFS

VWFB

VVFB

VUFB

IGBT1

IGBT2

IGBT3

IGBT4

IGBT5

IGBT6

Di1

Di2

Di3

Di4

Di5

Di6

NU

NV

NW

Fo Fo

MITSUBISHI SEMICONDUCTOR <Dual-In-Line Package Intelligent Power Module>

PS21767

TRANSFER-MOLD TYPE

INSULATED TYPE

Aug. 2007

6

Fault output Fo

Output current Ic

Control supply voltage VD

Protection circuit state

Control input

b1

b2

b3

b4

b5

RESET

RESET

UVDt

UVDr

SET

b6

b7

Protection circuit state

Lower-arms control

input

Fault output Fo

Sense voltage of the

shunt resistor

Output current Ic

Internal IGBT gate

SC reference voltage

CR circuit time

constant DELAY

a5

a8

a4

a3

a1

a2

SC

RESET

SET

a7 a6

Fig. 4 TIMING CHARTS OF THE DIP-IPM PROTECTIVE FUNCTIONS

[A] Short-Circuit Protection (Lower-arms only with the external shunt resistor and CR filter)

a1. Normal operation : IGBT ON and carrying current.

a2. Short circuit current detection (SC trigger).

a3. IGBT gate hard interruption.

a4. IGBT turns OFF.

a5. FO timer operation starts : The pulse width of the FO signal is set by the external capacitor CFO.

a6. Input L : IGBT OFF.

a7. Input H

a8. IGBT OFF state in spite of input H.

[B] Under-Voltage Protection (Lower-arm, UVD)

b1. Control supply voltage rising : After the voltage level reaches UVDr, the circuits start to operate when next input is applied.

b2. Normal operation : IGBT ON and carrying current.

b3. Under voltage trip (UVDt).

b4. IGBT turns OFF in spite of control input condition.

b5. FO operation starts.

b6. Under voltage reset (UVDr).

b7. Normal operation : IGBT ON and carrying current.

MITSUBISHI SEMICONDUCTOR <Dual-In-Line Package Intelligent Power Module>

PS21767

TRANSFER-MOLD TYPE

INSULATED TYPE

Aug. 2007

7

MCU

10k

UP,VP,WP,UN,VN,WN

VNC(Logic)

Fo

DIP-IPM

5V line

[C] Under-Voltage Protection (Upper-arm, UVDB)

c1. Control supply voltage rises : After the voltage level reaches UVDBr, the circuits start to operate.

c2. Protection circuit state reset : IGBT ON and carrying current.

c3. Normal operation : IGBT ON and carrying current.

c4. Under-voltage trip (UVDBt).

c5. IGBT OFF inspite of control input condition, but there is no FO signal output.

c6. Under-voltage reset (UVDBr).

c7. Normal operation : IGBT ON and carrying current.

Fig. 5 RECOMMENDED MCU I/O INTERFACE CIRCUIT

Note : RC coupling at each input (parts shown dotted) may change depending on the PWM control scheme used in

the application and the wiring impedance of the applications printed circuit board.

The DIP-IPM input signal section integrates a 2.5k(min) pull-down resistor. Therefore, when using a external

filtering resistor, care must be taken to satisfy the turn-on threshold voltage requirement.

Fig. 6 RECOMMENDED WIRING AROUND THE SHUNT RESISTOR

Control input

Protection circuit state

Control supply voltage VDB

Output current Ic

Fault output Fo

High-level (no fault output)

UVDBr

RESET SET

RESET

UVDBt

c1

c3

c4

c5

c6

c7

c2

NW

VNC

NV

NU

DIP-IPM

The GND wiring from VNO, VNC should be

as close to the shunt resistors as possible

VNO

Each wiring inductance should be less than 10nH

Shunt resistor

Equivalent to the inductance of a copper

pattern in dimension of width=3mm,

thickness=100m, length=17mm

MITSUBISHI SEMICONDUCTOR <Dual-In-Line Package Intelligent Power Module>

PS21767

TRANSFER-MOLD TYPE

INSULATED TYPE

Aug. 2007

8

Note 1 : Input drive is High-active type. There is a 2.5k(Min.) pull-down resistor integrated in the IC input circuit. To prevent malfunction, the wiring of each in-

put should be as short as possible. When using RC coupling circuit, make sure the input signal level meet the turn-on and turn-off threshold voltage.

2 : Thanks to HVIC inside the module, direct coupling to MCU without any opto-coupler or transformer isolation is possible.

3 : FO output is open drain type. It should be pulled up to the positive side of a 5V power supply by a resistor of about 10k.

FO output pulse width is determined by the external capacitor (CFO) between CFO and VNC terminals (e.g CFO = 22nF tFO =

1.8ms (typ.))

4 : To prevent erroneous protection, the wiring of A, B should be as short as possible.

5 : The time constant R1C5 of the protection circuit should be selected in the range of 1.5-2s. SC interrupting time might vary with the

wiring pattern. Tight tolerance, temp-compensated type is recommended for R1, C5.

6 : All capacitors should be mounted as close to the terminals of the DIP-IPM as possible. (C1: good temperature, frequency character-

istic electrolytic type, and C2, C3: good temperature, frequency and DC bias characteristic ceramic type are recommended.)

7 : To prevent surge destruction, the wiring between the smoothing capacitor and the P, N1 terminals should be as short as possible.

Generally a 0.1-0.22F snubber between the P-N1 terminals is recommended.

8 : It is recommended to insert a Zener diode (24V/1W) between each pair of control supply terminals to prevent surge destruction.

9 : If control GND is connected to power GND by broad pattern, it may cause malfunction by power GND fluctuation. It is recommended

to connect control GND and power GND at only a point.

10 : The reference voltage Vref of comparator should be set up the same rating of short circuit trip level (Vsc(ref): min.0.43V to max.0.53V).

11 : OR logic output high level should exceed the maximum short circuit trip level (Vsc(ref): max.0.53V).

Fig. 7 TYPICAL DIP-IPM APPLICATION CIRCUIT EXAMPLE

C1: Tight tolerance temp-compensated electrolytic type C2,C3: 0.22~2F R-category ceramic capacitor for noise filtering

HO

HO

DIP-IPM

C3

C3

C3

C2

C2

C2

C1

C1

C1

IN

IN

IN

COM

COM

COM

UOUT

VOUT

WOUT

CFO

VNO

GND

Fo

WN

VN

VCC

C

A

C4(CFO)

CFO CIN

NW

CIN

VS

VS

VB

VB

HO

VS

VB

VCC

VCC

VCC

Fo

WN

VN

UN

UN

WP

VP

UP

VNC

VNO

VN1

VP1

VP1

VP1

VWFS

VVFS

VUFS

VWFB

VVFB

VUFB

M

C3

HVIC1

HVIC2

HVIC3

LVIC

W

V

U

P

C5

R1 B

Vref

+

-

C5

R1 B

Vref

+

-

C5

N1

R1 B

Vref

+

-

15V line

5V line

C

O

N

T

R

O

L

L

E

R

Too long wiring here might

cause short-circuit.

If this wiring is too long, the SC

level fluctuation might be larger

and cause SC malfunction.

Long GND wiring here might

generate noise to input and cause

IGBT malfunction.

Comparator External protection circuit

Shunt resistors

OR Logic

NV

NU

Anda mungkin juga menyukai

- MITSUBISHI PS21245-E 4th Gen IGBT Inverter ModuleDokumen9 halamanMITSUBISHI PS21245-E 4th Gen IGBT Inverter ModulepukymottoBelum ada peringkat

- PS21245 eDokumen9 halamanPS21245 eTol SirtBelum ada peringkat

- Air Acond Ps21246 OnduladorDokumen10 halamanAir Acond Ps21246 OnduladorJ CorreoBelum ada peringkat

- Ps 21 A 79Dokumen10 halamanPs 21 A 79Omar LeonBelum ada peringkat

- Mitsubishi SemiconductorDokumen8 halamanMitsubishi Semiconductoredgardo2004Belum ada peringkat

- Optimize Motor Drive Inverter Module Application NoteDokumen10 halamanOptimize Motor Drive Inverter Module Application Notevishwa_001Belum ada peringkat

- PM 150 CSD 120Dokumen7 halamanPM 150 CSD 120elecompinnBelum ada peringkat

- 10884Dokumen13 halaman10884karthikeidBelum ada peringkat

- Ps 11034Dokumen5 halamanPs 11034Tanvon MalikBelum ada peringkat

- IRAMX16UP60ADokumen18 halamanIRAMX16UP60Atheylor1990Belum ada peringkat

- Infineon BTS740S2Dokumen15 halamanInfineon BTS740S2dasho1Belum ada peringkat

- Tda 7293Dokumen16 halamanTda 7293Gerson FelipeBelum ada peringkat

- Irams 06 Up 60 ADokumen18 halamanIrams 06 Up 60 AAndré Roberto EvangelistaBelum ada peringkat

- STCC05-B: Home Appliance Control CircuitDokumen13 halamanSTCC05-B: Home Appliance Control Circuitsvhanu4010Belum ada peringkat

- Line Regulator Controller: Features General DescriptionDokumen16 halamanLine Regulator Controller: Features General DescriptionfuzulibabaBelum ada peringkat

- Tda 7296Dokumen14 halamanTda 7296Mayra GonzálezBelum ada peringkat

- Double Channel High Side Solid State Relay: VND600SPDokumen17 halamanDouble Channel High Side Solid State Relay: VND600SPDan EsentherBelum ada peringkat

- Ssm2120 2 ExpanderDokumen12 halamanSsm2120 2 ExpandershirtquittersBelum ada peringkat

- Iramx 16 Up 60 ADokumen17 halamanIramx 16 Up 60 AJandfor Tansfg ErrottBelum ada peringkat

- 3000W Single Output Power Supply Spec SheetDokumen6 halaman3000W Single Output Power Supply Spec SheetGrigoriu CodrutaBelum ada peringkat

- VN800S VN800PT: High Side DriverDokumen21 halamanVN800S VN800PT: High Side DriverDan EsentherBelum ada peringkat

- ZXCT1009: High-Side Current MonitorDokumen8 halamanZXCT1009: High-Side Current MonitorDomingo ArroyoBelum ada peringkat

- Linear Technology LTC3728EG28400Dokumen37 halamanLinear Technology LTC3728EG28400Rickz2k8Belum ada peringkat

- 5V-0.5A Very Low Drop Regulator With Reset: DescriptionDokumen6 halaman5V-0.5A Very Low Drop Regulator With Reset: DescriptionDan EsentherBelum ada peringkat

- MITSUBISHI Intelligent Power Modules PM150RL1A120 FeaturesDokumen9 halamanMITSUBISHI Intelligent Power Modules PM150RL1A120 FeaturesDamiano ZitoBelum ada peringkat

- STR W6753 DatasheetDokumen8 halamanSTR W6753 DatasheetjgerabmBelum ada peringkat

- Features Description: LT3085 Adjustable 500ma Single Resistor Low Dropout RegulatorDokumen28 halamanFeatures Description: LT3085 Adjustable 500ma Single Resistor Low Dropout Regulatoram1liBelum ada peringkat

- 04 Spec Sheet PWM Controller ChipDokumen16 halaman04 Spec Sheet PWM Controller Chipxuanhiendk2Belum ada peringkat

- Uc3842b 3843BDokumen10 halamanUc3842b 3843Bbob75Belum ada peringkat

- 1A Step-Down LED Driver Data SheetDokumen12 halaman1A Step-Down LED Driver Data SheetselocaBelum ada peringkat

- 9432Dokumen18 halaman9432Dan EsentherBelum ada peringkat

- Ltc1871ems (LTSX, Frntoluz Welch Allyn)Dokumen36 halamanLtc1871ems (LTSX, Frntoluz Welch Allyn)RICHIHOTS2Belum ada peringkat

- LTC 1625Dokumen24 halamanLTC 1625Sakura KunBelum ada peringkat

- Ncl30160 1.0A Constant-Current Buck Regulator For Driving High Power LedsDokumen10 halamanNcl30160 1.0A Constant-Current Buck Regulator For Driving High Power LedsKhúc Hành QuânBelum ada peringkat

- 2A, 28V, 1.5Mhz Step-Down Converter: The Future of Analog Ic TechnologyDokumen16 halaman2A, 28V, 1.5Mhz Step-Down Converter: The Future of Analog Ic TechnologyCazbir MariAndradaBelum ada peringkat

- BTS5215LDokumen14 halamanBTS5215LVanny Is AresBelum ada peringkat

- Fully Integrated H-Bridge Motor Driver: VNH3SP30Dokumen26 halamanFully Integrated H-Bridge Motor Driver: VNH3SP30Dan EsentherBelum ada peringkat

- 5101 Motor DriverDokumen11 halaman5101 Motor DriverMoise CristinaBelum ada peringkat

- PM20CSJ060Dokumen6 halamanPM20CSJ060Dany Carrasco Ysus TecladosBelum ada peringkat

- C324G Low Power Quad OpAmpDokumen12 halamanC324G Low Power Quad OpAmpwhynot05Belum ada peringkat

- TDA7294Dokumen18 halamanTDA7294frank121212Belum ada peringkat

- ECN3021Dokumen10 halamanECN3021Wasang Juwi PracihnoBelum ada peringkat

- L6565Dokumen18 halamanL6565Sergio Daniel BarretoBelum ada peringkat

- L 6565Dokumen17 halamanL 6565tatatabuchoBelum ada peringkat

- TDA7372BDokumen10 halamanTDA7372BCarlos MartinezBelum ada peringkat

- Smart High-Side Power Switch Four Channels: 4 X 90m Status FeedbackDokumen14 halamanSmart High-Side Power Switch Four Channels: 4 X 90m Status FeedbackSeyed Amir Ali MousavianBelum ada peringkat

- 3000W Single Output Power Supply: SeriesDokumen7 halaman3000W Single Output Power Supply: SeriesAlexander PekarovskiyBelum ada peringkat

- Low Power Energy Harvester IC From Linear Technologies - LTC3108Dokumen22 halamanLow Power Energy Harvester IC From Linear Technologies - LTC3108shawnleegabrielBelum ada peringkat

- LT1618 DatasheetDokumen16 halamanLT1618 DatasheetkurabyqldBelum ada peringkat

- Icl 8038 DataDokumen10 halamanIcl 8038 DataTushar Kanti BeraBelum ada peringkat

- TLC 2934Dokumen9 halamanTLC 2934Carlos DanielBelum ada peringkat

- 700ma H V A C R W E C: IGH Oltage Djustable Urrent Egulator ITH Nable OntrolDokumen6 halaman700ma H V A C R W E C: IGH Oltage Djustable Urrent Egulator ITH Nable OntrolNathan WilliamsBelum ada peringkat

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Dari EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Belum ada peringkat

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Dari EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Penilaian: 2.5 dari 5 bintang2.5/5 (3)

- 110 Waveform Generator Projects for the Home ConstructorDari Everand110 Waveform Generator Projects for the Home ConstructorPenilaian: 4 dari 5 bintang4/5 (1)

- Analog Circuit Design Volume Three: Design Note CollectionDari EverandAnalog Circuit Design Volume Three: Design Note CollectionPenilaian: 3 dari 5 bintang3/5 (2)

- Semiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsDari EverandSemiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsBelum ada peringkat

- Analog Circuit Design: A Tutorial Guide to Applications and SolutionsDari EverandAnalog Circuit Design: A Tutorial Guide to Applications and SolutionsPenilaian: 3.5 dari 5 bintang3.5/5 (6)

- (Week 4, Day 1, Activity # 7) : TLE 9 - ICT (Fourth Quarter)Dokumen3 halaman(Week 4, Day 1, Activity # 7) : TLE 9 - ICT (Fourth Quarter)armand lagriaBelum ada peringkat

- 5 Lab WorkDokumen3 halaman5 Lab WorkSabina IsmagulovaBelum ada peringkat

- Flyback Converter DesignDokumen7 halamanFlyback Converter DesignRobert AlbuquerqueBelum ada peringkat

- ATV312 CANopen Manual BBV52819 03Dokumen49 halamanATV312 CANopen Manual BBV52819 03Rafael BispoBelum ada peringkat

- Sect 12Dokumen10 halamanSect 12Sry SantosBelum ada peringkat

- Linear Integrated Circuit Tone RingerDokumen3 halamanLinear Integrated Circuit Tone RingerLenon Salazar100% (1)

- As 60044.5-2004 Instrument Transformers Capacitor Voltage TransformersDokumen10 halamanAs 60044.5-2004 Instrument Transformers Capacitor Voltage TransformersSAI Global - APAC100% (1)

- Mam Ky02sDokumen34 halamanMam Ky02sTaufan Justvands67% (3)

- Project Title: - Tracking and Border Alert System For Fishermen Using GPSDokumen22 halamanProject Title: - Tracking and Border Alert System For Fishermen Using GPSArchit MeenaBelum ada peringkat

- THX203 HDokumen21 halamanTHX203 HPuiuMerisBelum ada peringkat

- US Pat. 4,002,994, Treble Bleed Circuit For Guitar (Fender), 1977.Dokumen6 halamanUS Pat. 4,002,994, Treble Bleed Circuit For Guitar (Fender), 1977.Duane BlakeBelum ada peringkat

- Chap 19Dokumen55 halamanChap 19Arnab DeBelum ada peringkat

- NSEA 2013 Astronomy Test PaperDokumen9 halamanNSEA 2013 Astronomy Test PaperAnkit AkashBelum ada peringkat

- Principles of Insulation TestingDokumen10 halamanPrinciples of Insulation Testingm khBelum ada peringkat

- Basic Stamp 2 TutorialDokumen376 halamanBasic Stamp 2 TutorialTWChan69Belum ada peringkat

- 4.5V To 18V Input, 3-A SYNCHRONOUS STEP DOWN CONVERTERDokumen26 halaman4.5V To 18V Input, 3-A SYNCHRONOUS STEP DOWN CONVERTERFelipeAndrésLondoñoGrandaBelum ada peringkat

- Neelema Computer-1 PDFDokumen315 halamanNeelema Computer-1 PDFLokesh VaswaniBelum ada peringkat

- 12 Physics PP 23Dokumen36 halaman12 Physics PP 23Pro HackerBelum ada peringkat

- Engineering Physics LaboratoryDokumen14 halamanEngineering Physics Laboratorys d p vaishnavBelum ada peringkat

- Magnetotheranostics - Nano-Tera 2016Dokumen46 halamanMagnetotheranostics - Nano-Tera 2016nanoteraCHBelum ada peringkat

- Csr1010 Data Sheet Cs-231986-DsDokumen48 halamanCsr1010 Data Sheet Cs-231986-DspadrititaBelum ada peringkat

- BAT - Operation and Maintenance Manual Rev2.5Dokumen123 halamanBAT - Operation and Maintenance Manual Rev2.5Truong Hung50% (2)

- MS 2135FDokumen34 halamanMS 2135FManuel NolascoBelum ada peringkat

- Makalah KomputerDokumen17 halamanMakalah KomputerMatludin100% (1)

- El Timer 555 PDFDokumen28 halamanEl Timer 555 PDFAnonymous 1LD5bpJ15dBelum ada peringkat

- Infineon-Motor Control Shield With IFX007T For Arduino-UserManual-V02 00-EnDokumen15 halamanInfineon-Motor Control Shield With IFX007T For Arduino-UserManual-V02 00-EnMR. VAIBHAVSINGH VARMABelum ada peringkat

- Capacitor WorksheetDokumen12 halamanCapacitor WorksheetGogull GogullBelum ada peringkat

- Schematics and DiagramDokumen67 halamanSchematics and DiagramArgel Linard Francisco Mabaga100% (1)

- Zldo1117 PDFDokumen12 halamanZldo1117 PDFJose Barroso GuerraBelum ada peringkat

- Hand Soldering Large Radial Ceramic CapacitorsDokumen3 halamanHand Soldering Large Radial Ceramic Capacitorsabdulyunus_amirBelum ada peringkat