Administracion Del Procesador

Diunggah oleh

Abbie Johnson100%(1)100% menganggap dokumen ini bermanfaat (1 suara)

25 tayangan31 halamanJudul Asli

Administracion_del_Procesador.doc

Hak Cipta

© © All Rights Reserved

Format Tersedia

DOC, PDF, TXT atau baca online dari Scribd

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniHak Cipta:

© All Rights Reserved

Format Tersedia

Unduh sebagai DOC, PDF, TXT atau baca online dari Scribd

100%(1)100% menganggap dokumen ini bermanfaat (1 suara)

25 tayangan31 halamanAdministracion Del Procesador

Diunggah oleh

Abbie JohnsonHak Cipta:

© All Rights Reserved

Format Tersedia

Unduh sebagai DOC, PDF, TXT atau baca online dari Scribd

Anda di halaman 1dari 31

Procesos y Administracin del Procesador

1. Introduccin y Definiciones Sobre Procesos

2. Estados de Procesos

3. Procesamiento de Interrupciones

4. El Ncleo del Sistema perati!o

". Planificacin de Procesos

#. Ni!eles de Planificacin del Procesador

$. b%eti!os de la Planificacin

&. 'riterios de Planificacin

(. Planificacin )propiati!a *ersus No )propiati!a

1+. ,empori-ador de Inter!alos o .elo% de Interrupcin

11. Prioridades

12. ,ipos de Planificacin

1. Planificacin a Pla-o /i%o

2. Planificacin 0aranti-ada

3. Planificacin del Primero en Entrar Primero en Salir 1/I/2

4. Planificacin de )si3nacin en .ueda 1..4 .ound .obin2

". ,ama5o del 'uanto o 6uantum

#. Planificacin del ,raba%o 78s 'orto Primero 1S9/2

$. Planificacin del ,iempo .estante 78s 'orto 1S.,2

&. Planificacin el Si3uiente con .elacin de .espuesta 78:ima 1;.N2

(. Planificacin por Prioridad

1+. 'olas de .etroalimentacin de Ni!eles 7ltiples

11. Pol<tica *ersus 7ecanismo de Planificacin

12. Planificacin de Dos Ni!eles

13. 7ultiprocesamiento

1. Introduccin

2. 'onfiabilidad

3. E:plotacin del Paralelismo

4. Paralelismo 7asi!o

". 7etas de los Sistemas de 7ultiprocesamiento

#. Deteccin )utom8tica del Paralelismo

$. Distribucin de 'iclos

&. .educcin de la )ltura del =rbol

14. r3ani-acin del ;ard>are del 7ultiprocesador

1. ,iempo 'ompartido o ?us 'omn 1o 'onductor 'omn2

2. 7atri- de ?arras 'ru-adas e Interruptores

3. )lmacenamiento de Intercone:in 7ltiple

1". 0rados de )coplamiento en 7ultiprocesamiento

1. r3ani-acin 7aestro @ SatAlite

1#. Sistema perati!o de 7ultiprocesadores

1. 7aestro @ SatAlite

2. E%ecuti!os Separados

3. ,ratamiento SimAtrico

1$. .endimiento del Sistema de 7ultiprocesamiento

1&. .ecuperacin de Errores

1(. 7ultiprocesamiento SimAtrico 17PS2

2+. ,endencias de los 7ultiprocesadores

Introduccin y Definiciones Sobre Procesos

El concepto central de cualBuier Sistema perati!o es el de proceso4 una abstraccin de un

pro3rama en e%ecucin tambiAn llamada tarea.

No Cay un acuerdo uni!ersal sobre una definicin de procesoD pero s< al3unas definiciones

aceptadas4

En pro3rama Bue se est8 e%ecutando.

Ena acti!idad asincrnica.

El emplazamiento del control de un procedimiento Bue est8 siendo e%ecutado.

)Buello Bue se manifiesta por la e:istencia en el Sistema perati!o de un bloque de

control de proceso.

)Buella entidad a la cual son asi3nados los procesadores.

Fa unidad despachable.

En sistemas de multiprogramacin la cpu alterna de pro3rama en pro3ramaD en un esBuema de

seudo paralelismo D es decir Bue la cpu e%ecuta en cierto instante un solo pro3ramaD

intercambiando muy r8pidamente entre uno y otro.

El paralelismo real de hardware se da en las si3uientes situaciones4

En e%ecucin de instrucciones de pro3rama con m8s de un procesador de instrucciones

en uso simult8neamente.

'on la superposicin de e%ecucin de instrucciones de pro3rama con la e%ecucin de una

o m8s operaciones de entrada @ salida.

El ob%eti!o es aumentar el paralelismo en la e%ecucin.

El modelo de procesos posee las si3uientes caracter<sticas4

,odo el soft>are e%ecutableD inclusi!e el Sistema perati!oD se or3ani-a en !arios

procesos secuenciales o procesos.

En proceso incluye al pro3rama en e%ecucin y a los !alores acti!os del contadorD

re3istros y !ariables del mismo.

'onceptualmente cada proceso tiene su propia cpu !irtual.

Si la cpu alterna entre los procesosD la !elocidad a la Bue e%ecuta un proceso no ser8

uniformeD por lo Bue es necesario aclarar lo si3uiente4

o 6ue los procesos no deben pro3ramarse con Ciptesis impl<citas acerca del

tiempo.

o 6ue normalmente la mayor<a de los procesos no son afectados por la

multipro3ramacin subyacente de la cpu o las !elocidades relati!as de procesos

distintos.

En proceso es una acti!idad de un cierto tipoD Bue tiene un pro3ramaD entradaD salida y

estado.

En solo procesador puede ser compartido entre !arios procesos con cierto algoritmo

de planificacin D el cual determina cu8ndo detener el traba%o en un proceso y dar

ser!icio a otro distinto 1!er /i3ura 2.12.

En cuanto a las jerarquas de procesos es necesario se5alar Bue los Sistemas perati!os deben

disponer de una forma de crear y destruir procesos cuando se reBuiera durante la operacinD

teniendo adem8s presente Bue los procesos pueden 3enerar procesos Ci%os mediante llamadas al

Sistema perati!oD pudiendo darse e%ecucin en paralelo.

.especto de los estados del proceso deben efectuarse las si3uientes consideraciones4

'ada proceso es una entidad independiente pero frecuentemente debe interactuar con

otros procesos 1!er /i3ura 2.22.

Fos procesos pueden bloBuearse en su e%ecucin porBue4

o Desde el punto de !ista l3ico no puede continuar porBue espera datos Bue an

no est8n disponibles.

o El Sistema perati!o asi3n la cpu a otro proceso.

Fos estados Bue puede tener un proceso son 1!er /i3ura 2.324

o !n ejecucin" utili-a la cpu en el instante dado.

o #isto" e%ecutableD se detiene en forma temporal para Bue se e%ecute otro

proceso.

o $loqueado" no se puede ejecutar debido a la ocurrencia de al3n e!ento

e:terno.

Son posibles cuatro transiciones entre estos estados.

!stados de Procesos

Durante su e:istencia un proceso pasa por una serie de estados discretosD siendo !arias las

circunstancias Bue pueden Cacer Bue el mismo cambie de estado.

Debido a ello se puede establecer una GFista de FistosH para los procesos GlistosH y una GFista

de ?loBueadosH para los GbloBueadosH.

Fa Lista de Listos se mantiene en orden prioritario y la Lista de Bloqueados est8

desordenadaD ya Bue los procesos se desbloBuean en el orden en Bue tienen lu3ar los e!entos Bue

est8n esperando.

)l admitirse un traba%o en el sistema se crea un proceso eBui!alente y es insertado en la ltima

parte de la Lista de Listos.

Fa asi3nacin de la cpu al primer proceso de la Lista de Listos se denomina GDespacCoHD Bue

es e%ecutado por una entidad del Sistema perati!o llamada Despachador.

El G?loBueoH es la nica transicin de estado iniciada por el propio proceso del usuarioD puesto

Bue las otras transiciones son iniciadas por entidades a%enas al proceso.

Fa manifestacin de un proceso en un Sistema perati!o es un Bloque de Control de

Proceso 1P'?2 con informacin Bue incluye4

Estado actual del proceso.

Identificacin nica del proceso.

Prioridad del proceso.

)puntadores para locali-ar la memoria del proceso.

)puntadores para asi3nar recursos.

=rea para preser!ar re3istros.

'uando el Sistema perati!o cambia la atencin de la cpu entre los procesosD utili-a las 8reas de

preser!acin del P'? para mantener la informacin Bue necesita para reiniciar el proceso

cuando consi3a de nue!o la cpu.

Fos sistemas Bue administran los procesos deben poder crearD destruirD suspenderD reanudarD

cambiar la prioridadD bloBuearD despertar y despacCar un proceso.

Fa creacin de un proceso si3nifica4

Dar nombre al proceso.

Insertar un proceso en la lista del sistema de procesos conocidos.

Determinar la prioridad inicial del proceso.

'rear el bloBue de control del proceso.

)si3nar los recursos iniciales del proceso.

En proceso puede crear un nuevo procesoD en cuyo caso el proceso creador se denomina

proceso padre y el proceso creado proceso hijo y se obtiene una estructura jerrquica de

procesos.

Fa destruccin de un proceso implica4

?orrarlo del sistema.

De!ol!er sus recursos al sistema.

Pur3arlo de todas las listas o tablas del sistema.

?orrar su bloBue de control de procesos.

En proceso suspendido no puede prose3uir Casta Bue otro proceso lo reanude.

.eanudar 1reacti!ar2 un proceso implica reiniciarlo en el punto donde fue suspendido.

Fa destruccin de un proceso puede o no si3nificar la destruccin de los procesos Ci%osD

se3n el Sistema perati!o.

0eneralmente se denomina a!la de Procesos al con%unto de informacin de control sobre

los distintos procesos.

Procesamiento de Interrupciones

Ena GinterrupcinH es un e!ento Bue altera la secuencia en Bue el procesador e%ecuta las

instruccionesI es un CecCo 3enerado por el Card>are del computador.

'uando ocurre una interrupcinD el Sistema perati!o4

btiene el control.

Sal!a el estado del proceso interrumpidoD 3eneralmente en su bloBue de control de

procesos.

)nali-a la interrupcin.

,ransfiere el control a la rutina apropiada para la manipulacin de la interrupcin.

Ena interrupcin puede ser iniciada por un proceso en estado de e%ecucin o por un e!ento Bue

puede o no estar relacionado con un proceso en e%ecucin.

0eneralmente las interrupciones se pueden clasificar por tipos se3n el si3uiente detalle 1!er

,abla 2.14

"#C $llamada al supervisor%& es una peticin 3enerada por el usuario para un

ser!icio particular del sistemaD por e%emploD reali-acin de Entrada @ Salida u obtencin

de m8s memoria.

'ntrada ( "alida& son iniciadas por el Card>are de Entrada @ SalidaD indicando a la

cpu Bue Ca cambiado el estado de un canal o dispositi!oD por e%emploD finali-acin de

Entrada @ Salida u ocurrencia de un error.

')ternas& son causadas por distintos e!entosD por e%emploD e:piracin de un cuanto

en un relo% de interrupcin o recepcin de una se5al de otro procesador en un sistema

multiprocesador.

De reinicio& ocurren al presionar la Gtecla de reinicioH o cuando lle3a una instruccin

de reinicio de otro procesador en un sistema multiprocesador.

De verificacin de programa& son causadas por errores producidos durante la

e%ecucin de procesosD por e%emplo4

o En intento de di!idir por cero.

o En intento de un proceso de usuario de e%ecutar una instruccin pri!ile3iada.

o En intento de e%ecutar un cdi3o de operacin in!8lido.

De verificacin de mquina& son ocasionadas por un mal funcionamiento del

Card>are.

%ipo de Interrupcin Descripcin

S*' Flamada al Sistema perati!o

Entrada @ Salida

'ambio de estado de un canal

o dispositi!o

E:terna E!ento e:terno al sistema

De .einicio .einicio del procesamiento

De *erificacin de

Pro3rama

Errores de procesos

De *erificacin de

78Buina

Errores de Card>are

%abla &.'" %ipos de interrupciones.

El Sistema perati!o incluye rutinas llamadas ()anipuladores de Interrupciones *I+,- para

procesar cada tipo diferente de interrupcin.

'uando se produce una interrupcin el Sistema perati!o efecta las si3uientes acciones4

Sal!a el estado del proceso interrumpido.

Diri3e el control al manipulador de interrupciones adecuado.

Se aplica la tAcnica de G'ambio de 'onte:toH .

Fos Sistemas perati!os instrumentan informacin de control Bue puede aparecer como las

GPalabras de Estado de Pro3rama 1PSJ2HD las cuales controlan el orden de e%ecucin de las

instrucciones y contienen informacin sobre el estado del proceso.

E:isten tres tipos de PSJD Bue son la GactualHD la Gnue!aH y la G!ie%aH.

Fa GPSJ )ctualH almacena la direccin de la pr:ima instruccin Bue ser8 e%ecutada e indica

los tipos de instrucciones actualmente GCabilitadasH e inCabilitadasH.

En un sistema uniprocesador e:iste4

Solo una PSJ actual.

Seis PSJ nue!as 1una para cada tipo de interrupcin2.

Seis PSJ !ie%as 1una para cada tipo de interrupcin2.

Fa PSJ nue!a para un tipo de interrupcin dado contiene la direccin en el Card>are donde

reside el manipulador de interrupciones para este tipo espec<fico.

'uando ocurre una interrupcin para la cual el procesador no est8 inCabilitadoD ocurren las

si3uientes acciones4

El Card>are cambia las PSJ en los casos si3uientes4

o )l almacenar la PSJ actual en la PSJ !ie%aD para este tipo de interrupcin.

o )l almacenar la PSJ nue!a en la PSJ actualD para este tipo de interrupcin.

Fue3o de este Gintercambio de PSJH4

o Fa PSJ actual contiene la direccin del manipulador de interrupcin adecuado.

o El manipulador de interrupciones procesa la interrupcin.

o Fue3o de procesar la interrupcinD la cpu es en!iada al4

Proceso Bue estaba en e%ecucin en el momento de la interrupcinD o al

Proceso de listo de m8s alta prioridad.

o Fa accin precedente depende de si el proceso de interrupcin es4

(Apropiati.o-" obtiene la cpu solo si no Cay procesos de listos.

(/o apropiati.o-" obtiene de nue!o la cpu.

!l /0cleo del Sistema 1perati.o

El n*cleo del Sistema perati!o controla todas las operaciones Bue implican procesos y

representa solo una peBue5a porcin del cdi3o de todo el Sistema perati!o pero es de amplio

uso.

0eneralmente permanece en el almacenamiento primario.

El proceso de interrupciones se incluye en el ncleo ya Bue debe ser r8pido 1especialmente en

sistemas multiusuario2D para optimi-ar el uso de los recursos del sistema y pro!eer tiempos de

respuesta aceptables a los usuarios interacti!os.

El n0cleo inCabilita las interrupciones mientras responde a una interrupcin. Fas interrupciones

son Cabilitadas de nue!o despuAs de completar el proceso de una interrupcin.

El n0cleo del Sistema perati!o 3eneralmente reali-a las si3uientes funciones"

7anipulacin de interrupciones.

'reacin y destruccin de procesos.

'ambio de estados de procesos.

DespacCo.

Suspensin y reanudacin de procesos.

Sincroni-acin de procesos.

'omunicacin entre procesos.

7anipulacin de bloBues de control de proceso.

Soporte de las acti!idades de Entrada @ Salida.

Soporte de la asi3nacin y desasi3nacin de almacenamiento.

Soporte del sistema de arcCi!os.

Soporte de un mecanismo de llamada @ re3reso al procedimiento.

Soporte de ciertas funciones contables 1estad<sticas2 del sistema.

Planificacin de Procesos

'uando m8s de un proceso es e%ecutable desde el punto de !ista l3icoD el Sistema perati!o

debe decidir cu8l de ellos debe e%ecutarse en primer tArmino.

El Planificador es la porcin del Sistema perati!o Bue decide y el Algoritmo de

Planificacin es el utili-ado.

Fos principales criterios respecto de un buen al3oritmo de planificacin son la eBuidadD la

eficaciaD el tiempo de respuestaD el tiempo de re3reso y el rendimiento 1!er ,abla 2.22.

2riterio Descripcin

EBuidad

0aranti-ar Bue cada proceso obtiene su

proporcin %usta de la cpu

Eficacia

7antener ocupada la cpu el ciento por ciento

del tiempo

,iempo de

respuesta

7inimi-ar el tiempo de respuesta para los

usuarios interacti!os

,iempo de

re3reso

7inimi-ar el tiempo Bue deben esperar los

usuarios por lotes 1batcC2 para obtener sus

resultados

.endimiento

7a:imi-ar el nmero de tareas procesadas por

Cora

%abla &.&" 2riterios de un buen algoritmo de

planificacin.

)l3unas de estas metas son contradictoriasD por e%emploD minimi-ar el tiempo de respuesta para

los usuarios interacti!os si3nificar<a no e%ecutar las tareas batcC.

'ada proceso es nico e impredecibleD es decir Bue pueden reBuerir intensi!amente operaciones

de Entrada @ Salida o intensi!amente cpuI el planificador del Sistema perati!o no tiene la

certe-a de cu8nto tiempo transcurrir8 Casta Bue un proceso se bloBueeD ya sea por una operacin

de Entrada @ Salida o por otra ra-n .

Para e!itar Bue un proceso se apropie de la cpu un tiempo e:cesi!oD los eBuipos poseen un

dispositi!o Bue pro!oca una interrupcin en forma peridicaD por e%emplo #+ C-D o sea sesenta

!eces por se3undo.

En cada interrupcin del relo% el Sistema perati!o decide si el proceso Bue se est8 e%ecutando

contina o si el proceso a3ot su tiempo de cpu y debe suspenderse y ceder la cpu a otro

proceso.

Fos principales conceptos relacionados con la Planificacin del Procesador son los si3uientes4

Planificacin apropiativa& es la estrate3ia de permitir Bue procesos e%ecutables 1desde el

punto de !ista l3ico2 sean suspendidos temporalmente.

Planificacin no apropiativa& es la estrate3ia de permitir la e%ecucin de un proceso

Casta terminar.

Planificacin del procesador& determinar cu8ndo deben asi3narse los procesadores y a

BuA procesosD lo cual es responsabilidad del Sistema perati!o.

/i.eles de Planificacin del Procesador

Se consideran tres ni!eles importantes de planificacinD los Bue se detallan a continuacin 1!er

/i3ura 2.424

Planificacin de alto nivel&

o ,ambiAn se denomina Planificacin de traba%os.

o Determina a BuA traba%os se les !a a permitir competir acti!amente por los

recursos del sistemaD lo cual se denomina Planificacin de admisin.

Planificacin de nivel intermedio&

o Determina a BuA procesos se les puede permitir competir por la cpu.

o .esponde a fluctuaciones a corto pla-o en la car3a del sistema y efecta

GsuspensionesH y Gacti!acionesH 1GreanudacionesH2 de procesos.

o Debe ayudar a alcan-ar ciertas metas en el rendimiento total del sistema.

Planificacin de !ajo nivel&

o Determina a BuA proceso listo se le asi3na la cpu cuando esta Bueda disponible

y asi3na la cpu al mismoD es decir Bue GdespacCaH la cpu al proceso.

o Fa efecta el Despachador del Sistema perati!oD el Bue opera mucCas !eces

por se3undo y reside siempre en el almacenamiento primario.

Fos distintos Sistemas perati!os utili-an !arias Polticas de PlanificacinD Bue se

instrumentan mediante )ecanismos de Planificacin.

1bjeti.os de la Planificacin

Fos ob%eti!os de la planificacin del procesador son los si3uientes e in!olucran a los conceptos

detallados se3uidamente4

Ser justa"

o ,odos los procesos son tratados de i3ual manera.

o Nin3n proceso es poster3ado indefinidamente.

)a3imizar la capacidad de ejecucin"

o 7a:imi-ar el nmero de procesos ser!idos por unidad de tiempo.

)a3imizar el n0mero de usuarios interacti.os que reciban unos tiempos de

respuesta aceptables"

o En un m8:imo de unos se3undos.

Ser predecible"

o En traba%o dado debe e%ecutarse apro:imadamente en la misma cantidad de

tiempo independientemente de la car3a del sistema.

)inimizar la sobrecarga"

o No suele considerarse un ob%eti!o muy importante.

!quilibrar el uso de recursos"

o /a!orecer a los procesos Bue utili-ar8n recursos infrautili-ados.

!quilibrar respuesta y utilizacin"

o Fa me%or manera de 3aranti-ar buenos tiempos de respuesta es disponer de los

recursos suficientes cuando se necesitanD pero la utili-acin total de recursos

podr8 ser pobre.

!.itar la postergacin indefinida"

o Se utili-a la estrate3ia del Gen!e%ecimientoH .

o 7ientras un proceso espera por un recurso su prioridad debe aumentarD as< la

prioridad lle3ar8 a ser tan alta Bue el proceso recibir8 el recurso esperado.

Asegurar la prioridad"

o Fos mecanismos de planificacin deben fa!orecer a los procesos con

prioridades m8s altas.

Dar preferencia a los procesos que mantienen recursos cla.es"

o En proceso de ba%a prioridad podr<a mantener un recurso cla!eD Bue puede ser

reBuerido por un proceso de m8s alta prioridad.

o Si el recurso es no apropiati!oD el mecanismo de planificacin debe otor3ar al

proceso un tratamiento me%or del Bue le corresponder<a normalmenteD puesto

Bue es necesario liberar r8pidamente el recurso cla!e.

Dar mejor tratamiento a los procesos que muestren un (comportamiento

deseable-"

o En e%emplo de comportamiento deseable es una tasa ba%a de pa3inacin.

Degradarse sua.emente con cargas pesadas"

o En mecanismo de planificacin no debe colapsar con el peso de una e:i3ente

car3a del sistema.

o Se debe e!itar una car3a e:cesi!a mediante las si3uientes acciones4

No permitiendo Bue se creen nue!os procesos cuando la car3a ya es

pesada.

Dando ser!icio a la car3a m8s pesada al proporcionar un ni!el

moderadamente reducido de ser!icio a todos los procesos.

7ucCas de estas metas se encuentran en conflicto entre s<D por lo Bue la planificacin se

con!ierte en un problema comple%o.

2riterios de Planificacin

Para reali-ar los ob%eti!os de la planificacinD un mecanismo de planificacin debe considerar lo

si3uiente4

Fa limitacin de un proceso a las operaciones de Entrada @ Salida4 cuando un proceso

consi3ue la cpuD Kla utili-a solo bre!emente antes de 3enerar una peticin de Entrada @

SalidaL.

Fa limitacin de un proceso a la cpu4 cuando un proceso obtiene la cpuD Ktiende a usarla

Casta Bue e:pira su tiempoL.

Si un proceso es por lote 1batcC2 o interacti!o4 los usuarios interacti!os deben recibir

inmediato ser!icio para 3aranti-ar buenos tiempos de respuesta.

K6uA ur3encia tiene una respuesta r8pidaL4 por e%emploD un proceso de tiempo real de

un sistema de control Bue super!ise una refiner<a de combustible reBuiere una respuesta

r8pidaD m8s r8pida Bue la respuesta reBuerida por un proceso en lotes 1batcC2 Bue deber8

entre3arse al d<a si3uiente.

Fa prioridad de un proceso4 a mayor prioridad me%or tratamiento.

/recuentemente un proceso 3enera fallos 1carencias2 de p83ina4

o Probablemente los procesos Bue 3eneran pocos fallos de p83ina Cayan

acumulado sus Gcon%untos de traba%oH en el almacenamiento principal.

o Fos procesos Bue e:perimentan 3ran cantidad de fallos de p83ina an no Can

establecido sus con%untos de traba%o.

o En criterio indica fa!orecer a los procesos Bue Can establecido sus con%untos de

traba%o.

o tro criterio indica fa!orecer a los procesos con una tasa alta de fallos de

p83ina ya Bue r8pidamente 3enerar8n una peticin de Entrada @ Salida.

/recuentemente un proceso Ca sido apropiado por otro de m8s alta prioridadD lo cual

si3nifica lo si3uiente4

o ) menudo los procesos apropiados deben recibir un tratamiento menos

fa!orable.

o 'ada !e- Bue el Sistema perati!o asume la sobrecar3a para Cacer e%ecutar este

procesoD el corto tiempo de e%ecucin antes de la apropiacin no %ustifica la

sobrecar3a de Cacer e%ecutar al proceso en primer lu3ar.

K'u8nto tiempo de e%ecucin real Ca recibido el procesoL4 un criterio considera Bue

debe ser fa!orecido un proceso Bue Ca recibido muy poco tiempo de cpu.

K'u8nto tiempo adicional !a a necesitar el proceso para terminarL4 los tiempos

promedio de espera pueden reducirse priori-ando los procesos Bue reBuieren de un

tiempo de e%ecucin m<nimo para su terminacinD pero pocas !eces es posible conocer

la cantidad de tiempo adicional Bue cada proceso necesita para terminar.

Planificacin Apropiati.a 4ersus /o Apropiati.a

Fas Disciplinas de Planificacin pueden ser Apropiati.as o /o Apropiati.as 1!er ,abla 2.32.

Disciplina Descripcin

G)propiati!aH Ena !e- Bue se le Ca otor3ado la cpu a un procesoD le puede ser retirada

GNo )propiati!aH Ena !e- Bue se le Ca otor3ado la cpu a un procesoD no le puede ser retirada

%abla &.5" Disciplinas de planificacin del procesador.

Fas principales caracter<sticas de la planificacin apropiati.a son las si3uientes4

Es til cuando los procesos de alta prioridad reBuieren atencin r8pida.

Es importante para 3aranti-ar buenos tiempos de respuesta en sistemas interacti!os de

tiempo compartido.

,iene su costo en recursosD ya Bue el intercambio de conte:to implica sobrecar3a y

adem8s reBuiere mantener mucCos procesos en el almacenamiento principalD en espera

de la cpuD lo Bue tambiAn implica sobrecar3a.

Fas principales caracter<sticas de la planificacin no apropiati.a son las si3uientes4

Si3nifica Bue los traba%os Glar3osH Cacen esperar a los traba%os GcortosH.

Fo3ra m8s eBuidad en el tratamiento de los procesos.

Fo3ra Cacer m8s predecibles los tiempos de respuesta puesto Bue los traba%os nue!os de

prioridad alta no pueden despla-ar a los traba%os en espera.

El dise5o de un mecanismo apropiati!o Cace necesario considerar las arbitrariedades de casi

cualBuier esBuema de prioridadesD en ra-n de Bue mucCas !eces las propias prioridades no son

asi3nadas de forma si3nificati!a.

El mecanismo deber<a ser sencillo pero efecti!o y si3nificati!o.

%emporizador de Inter.alos o 6eloj de Interrupcin

El proceso al cual est8 asi3nada la cpu se dice Bue est8 en e%ecucin y puede ser un proceso de

Sistema perati!o o de usuario.

El Sistema perati!o dispone de mecanismos para Buitarle la cpu a un proceso de usuario para

e!itar Bue monopolice el sistema.

El Sistema perati!o posee un reloj de interrupcin o tempori+ador de intervalos para

3enerar una interrupcinD en al3n tiempo futuro espec<fico o despuAs de un transcurso de

tiempo en el futuroI la cpu es entonces despacCada Cacia el si3uiente proceso.

En proceso retiene el control de la cpu Casta Bue ocurra al3una de las si3uientes situaciones4

Fa libera !oluntariamente.

El relo% la interrumpe.

)l3una otra interrupcin atrae la atencin de la cpu.

Si el relo% interrumpe un proceso de usuarioD la interrupcin causa la e%ecucin del Sistema

perati!oD el Bue decide cu8l ser8 el proceso Bue obtendr8 la cpu.

El relo% de interrupcin ayuda a 3aranti-ar tiempos de respuesta ra-onables a usuarios

interacti!osD ya Bue e!ita Bue el sistema se Gcuel3ueH a un solo usuario en un ciclo infinito y

permite Bue los procesos respondan a Ge!entos dependientes del tiempoH.

)simismoD los procesos Bue necesitan una e%ecucin peridica dependen del relo% de

interrupcin.

Prioridades

Fas prioridades pueden ser de distinto tipo 1!er ,abla 2.42.

%ipos de prioridades

)si3nadas autom8ticamente

por el sistema

)si3nadas desde el e:terior

Din8micas

Est8ticas

)si3nadas racionalmente

)si3nadas arbitrariamente

%abla &.7" %ipos de

prioridades.

En el caso de prioridades asi3nadas arbitrariamenteD un mecanismo del sistema necesita

distin3uir entre procesos sin importarle cu8l es el m8s importante.

Fas principales caracter<sticas de las prioridades est8ticas son las si3uientes4

No cambian.

Fos mecanismos de implementacin son sencillos.

Implican una sobrecar3a relati!amente ba%a.

No responden a cambios en el ambiente 1conte:to2 Bue Car<an deseable a%ustar al3una

prioridad.

Fas principales caracter<sticas de las prioridades din8micas son las si3uientes4

.esponden al cambio.

Fa prioridad inicial asi3nada a un proceso puede durar poco tiempoD lue3o se la rea%usta

a un me%or !alor.

Fos mecanismos de implementacin son m8s complicados Bue para prioridades

est8ticas.

Implican una sobrecar3a mayor Bue para esBuemas est8ticos.

.especto de las prioridades adquiridasD se Cace referencia al tratamiento especial Bue en

situaciones e:cepcionales reBuiere un cierto procesoD lo Bue puede si3nificar restar recursos a

los dem8s procesos.

%ipos de Planificacin

Planificacin a Plazo 9ijo

'iertos traba%os se planifican para ser terminados en un tiempo espec<fico o pla-o fi%o. Es una

planificacin comple%a debido a los si3uientes factores4

El usuario debe suministrar anticipadamente una lista precisa de recursos necesarios

para el procesoD pero 3eneralmente no se dispone de dicCa informacin.

Fa e%ecucin del traba%o de pla-o fi%o no debe producir una 3ra!e de3radacin del

ser!icio a otros usuarios.

El sistema debe planificar cuidadosamente sus necesidades de recursos Casta el pla-o

fi%oD lo Bue se puede complicar con las demandas de recursos de nue!os procesos Bue

in3resen al sistema.

Fa concurrencia de !arios procesos de pla-o fi%o 1acti!os a la !e-2 puede reBuerir

mAtodos sofisticados de optimi-acin.

Fa administracin intensi!a de recursos puede 3enerar una considerable sobrecar3a

adicional.

Planificacin :arantizada

Se establecen compromisos de desempe5o con el proceso del usuarioD por e%emploD si e:isten

n procesos en el sistemaD el proceso del usuario recibir8 cerca del , ( n de la potencia de la

cpu.

El sistema debe tener un re3istro del tiempo de cpu Bue cada proceso Ca tenido desde su entrada

al sistema y del tiempo transcurrido desde esa entrada.

'on los datos anteriores y el re3istro de procesos en curso de e%ecucinD el sistema calcula y

determina BuA procesos est8n m8s ale%ados por defecto de la relacin , ( n prometida y

priori-a los procesos Bue Can recibido menos cpu de la prometida.

Planificacin del Primero en !ntrar Primero en Salir *9I91,

Es muy simpleD los procesos se despacCan de acuerdo con su tiempo de lle3ada a la cola de

listos.

Ena !e- Bue el proceso obtiene la cpuD se e%ecuta Casta terminarD ya Bue es una disciplina Gno

apropiati!aH.

Puede ocasionar Bue procesos lar3os Ca3an esperar a procesos cortos y Bue procesos no

importantes Ca3an esperar a procesos importantes.

Es m8s predecible Bue otros esBuemas.

No puede 3aranti-ar buenos tiempos de respuesta interacti!os.

Suele utili-arse inte3rado a otros esBuemasD por e%emploD de la si3uiente manera4

Fos procesos se despacCan con al3n esBuema de prioridad.

Fos procesos con i3ual prioridad se despacCan G/I/H.

Planificacin de Asignacin en 6ueda *66" 6ound 6obin,

Fos procesos se despacCan en G/I/H y disponen de una cantidad limitada de tiempo de cpuD

llamada Gdi!isin de tiempoH o GcuantoH.

Si un proceso no termina antes de e:pirar su tiempo de cpu ocurren las si3uientes acciones4

1. Fa cpu es apropiada.

2. Fa cpu es otor3ada al si3uiente proceso en espera.

3. El proceso apropiado es situado al final de la lista de listos.

Es efecti!a en ambientes de tiempo compartido.

Fa sobrecar3a de la apropiacin se mantiene ba%a mediante mecanismos eficientes de

intercambio de conte:to y con suficiente memoria principal para los procesos.

%ama;o del 2uanto o <uantum

Fa determinacin del tama5o del cuanto es decisi!a para la operacin efecti!a de un sistema

computacional.

Fos interro3antes son4 Kcuanto peBue5o o 3randeLD Kcuanto fi%o o !ariableL y Kcuanto i3ual para

todos los procesos de usuarios o determinado por separado para cada uno de ellosL.

Si el cuanto se Cace muy 3randeD cada proceso recibe todo el tiempo necesario para lle3ar a su

terminacinD por lo cual la asi3nacin en rueda 1G..H2 de3enera en G/I/H.

Si el cuanto se Cace muy peBue5oD la sobrecar3a del intercambio de conte:to se con!ierte en un

factor dominante y el rendimiento del sistema se de3radaD puesto Bue la mayor parte del tiempo

de cpu se in!ierte en el intercambio del procesador 1cambio de conte:to2 y los procesos de

usuario disponen de muy poco tiempo de cpu.

El cuanto debe ser lo suficientemente 3rande como para permitir Bue la 3ran mayor<a de las

peticiones interacti!as reBuieran de menos tiempo Bue la duracin del cuantoD es decir Bue el

tiempo transcurrido desde el otor3amiento de la cpu a un proceso Casta Bue 3enera una peticin

de Entrada @ Salida debe ser menor Bue el cuanto establecidoD de esta formaD ocurrida la peticin

la cpu pasa a otro proceso y como el cuanto es mayor Bue el tiempo transcurrido Casta la

peticin de Entrada @ SalidaD los procesos traba%an al m8:imo de !elocidadD se minimi-a la

sobrecar3a de apropiacin y se ma:imi-a la utili-acin de la

Entrada @ Salida.

El cuanto ptimo !ar<a de un sistema a otro y con la car3aD siendo un !alor de referencia 1++

mse3 1cien milise3undos2.

Planificacin del %rabajo )8s 2orto Primero *S=9,

Es una disciplina no apropiati!a y por lo tanto no recomendable en ambientes de tiempo

compartido.

El proceso en espera con el menor tiempo estimado de e%ecucin Casta su terminacin es el

si3uiente en e%ecutarse.

Fos tiempos promedio de espera son menores Bue con G/I/H.

Fos tiempos de espera son menos predecibles Bue en G/I/H.

/a!orece a los procesos cortos en detrimento de los lar3os.

,iende a reducir el nmero de procesos en espera y el nmero de procesos Bue esperan detr8s de

procesos lar3os.

.eBuiere un conocimiento preciso del tiempo de e%ecucin de un procesoD lo Bue 3eneralmente

se desconoce.

Se pueden estimar los tiempos en base a series de !alores anteriores.

Planificacin del %iempo 6estante )8s 2orto *S6%,

Es la contraparte apropiati!a del S9/.

Es til en sistemas de tiempo compartido.

El proceso con el tiempo estimado de e%ecucin menor para Mfinali-ar es el si3uiente en ser

e%ecutado.

En proceso en e%ecucin puede ser apropiado por un nue!o proceso con un tiempo estimado de

e%ecucin menor.

,iene mayor sobrecar3a Bue la planificacin S9/.

Debe mantener un re3istro del tiempo de ser!icio transcurrido del proceso en e%ecucinD lo Bue

aumenta la sobrecar3a.

Fos traba%os lar3os tienen un promedio y una !arian-a de los tiempos de espera an mayor Bue

en S9/.

Fa apropiacin de un proceso a punto de terminar por otro de menor duracin reciAn lle3ado

podr<a si3nificar un mayor tiempo de cambio de conte:to 1administracin del procesador2 Bue el

tiempo de finali-acin del primero.

-l dise.arse los "istemas /perativos se de!e considerar cuidadosamente la so!recarga de los

mecanismos de administracin de recursos comparndola con los !eneficios esperados.

Planificacin el Siguiente con 6elacin de 6espuesta )83ima *+6/,

'orri3e al3unas de las debilidades del S9/D tales como el e:ceso de per%uicio Cacia los procesos

1traba%os2 lar3os y el e:ceso de fa!oritismo Cacia los nue!os traba%os cortos.

Es una disciplina no apropiati!a.

Fa prioridad de cada proceso est8 en funcin no slo del tiempo de ser!icio del traba%oD sino Bue

tambiAn influye la cantidad de tiempo Bue el traba%o Ca estado esperando ser ser!ido.

'uando un proceso Ca obtenido la cpuD corre Casta terminar.

Fas prioridadesD Bue son din8micasD se calculan se3n la si3uiente frmulaD donde p

r

es la

prioridadD t

e

es el tiempo de espera y t

s

es el tiempo de servicio&

Planificacin por Prioridad

'onsidera factores e:ternos al proceso.

Fas ideas centrales son Bue cada proceso tiene asociada una prioridad y Bue el proceso

e%ecutable con m8:ima prioridad es el Bue tiene el permiso de e%ecucin.

Fos procesos de alta prioridad podr<an e%ecutar indefinidamenteD ya Bue el planificador del

sistema puede disminuir la prioridad del proceso en e%ecucin en cada interrupcin del relo%.

Fas prioridades tambiAn pueden ser asi3nadas din8micamente por el sistema para lo3rar ciertas

metas relacionadas con el procesador o la Entrada @ Salida.

Fos procesos limitados por la Entrada @ Salida 1reBuerimientos intensi!os de Entrada @ Salida2

ocupan mucCo de su tiempo en espera de operaciones de Entrada @ SalidaD por lo tanto4

Deben tener prioridad para usar la cpu y efectuar la si3uiente peticin de Entrada @

SalidaD ya Bue se e%ecutar8 1la operacin de Entrada @ Salida2 en paralelo con otro

proceso Bue utilice la cpu.

Si deben esperar mucCo tiempo a la cpu estar8n ocupando memoria por un tiempo

innecesario.

En al3oritmo sencillo consiste en establecer Bue la prioridad sea , ( f0 donde f es la

fraccin del ltimo cuanto utili-ado por el proceso.

En proceso Bue utilice 2 mse3 1dos milise3undos2 de su cuanto de 1++ mse3 1cien

milise3undos2 tendr8 prioridad "+ 1cincuenta2.

En proceso Bue se e%ecut "+ mse3 antes del bloBueo tendr8 prioridad 2.

En proceso Bue utili- todo el cuanto tendr8 prioridad 1.

/recuentemente los procesos se a3rupan en Clases de Prioridad0 en cuyo caso se utili-a la

Planificacin con Prioridades entre las clases y con .ound .obin 1..2 dentro de cada clase. Si

las prioridades no se rea%ustan en al3n momentoD los procesos de las clases de prioridad

m<nima podr<an demorarse indefinidamente.

2olas de 6etroalimentacin de /i.eles )0ltiples

Proporcionan una estructura para lo3rar los si3uientes ob%eti!os4

/a!orecer traba%os cortos.

/a!orecer traba%os limitados por la Entrada @ Salida para optimi-ar el uso de los

dispositi!os de Entrada @ Salida.

Determinar la naturale-a de un traba%o lo m8s r8pido posible y planificar el traba%o

1proceso2 en consecuencia.

En nue!o proceso entra en la red de l<nea de espera al final de la cola superior.

Se mue!e por esta cola G/I/H Casta obtener la cpu.

Si el traba%o termina o abandona la cpu para esperar por la terminacin de una operacin de

Entrada @ Salida o la terminacin de al3n otro sucesoD el traba%o abandona la red de l<nea de

espera.

Si su cuanto e:pira antes de abandonar la cpu !oluntariamenteD el proceso se coloca en la parte

trasera de la cola del si3uiente ni!el inferior.

El traba%o recibe ser!icio al lle3ar a la cabe-a de esta cola si la primera est8 !ac<a.

7ientras el proceso contine consumiendo totalmente su cuanto en cada ni!elD continuar8

mo!iAndose Cacia el final de las colas inferiores.

0eneralmente Cay una cola en la parte m8s profunda a tra!As de la cual el proceso circula en

asi3nacin de rueda Casta Bue termina.

E:isten esBuemas en los Bue el cuanto otor3ado al proceso aumenta a medida Bue el proceso se

mue!e Cacia las colas de los ni!eles inferioresD en tal casoD cuanto m8s tiempo Caya estado el

proceso en la red de l<nea de esperaD mayor ser8 su cuanto cada !e- Bue obtiene la cpu y no

podr8 obtener la cpu muy a menudo debido a la mayor prioridad de los procesos de las colas

superiores.

En proceso situado en una cola dada no podr8 ser e%ecutado Casta Bue las colas de los ni!eles

superiores estAn !ac<as.

En proceso en e%ecucin es apropiado por un proceso Bue lle3ue a una cola superior.

Es un mecanismo adaptableD es decir Bue se adapta a car3as !ariables.

) los efectos de una re!isin 3r8fica de lo enunciado precedentementeD !er la fi3ura 2.".

Poltica 4ersus )ecanismo de Planificacin

Puede ocurrir Bue Caya procesos con mucCos procesos Ci%os e%ecut8ndose ba%o su controlD por

e%emploD un proceso en un D?7S con procesos Ci%os atendiendo funciones espec<ficasD tales

comoD an8lisis de interro3antesD acceso a discosD etc.

Es posible Bue el proceso principal 1padre2 pueda identificar la importancia 1o criticidad2 de sus

procesos Ci%osD pero los planificadores anali-ados no aceptan datos de los procesos de usuario

relati!os a decisiones de planificacin.

Fa solucin es separar el mecanismo de planificacin de la poltica de planificacinD para ello

se parametri-a el al3oritmo de planificacin y los par8metros pueden ser determinados por

medio de procesos del usuarioI as< el mecanismo est8 en el ncleo del Sistema perati!o pero la

pol<tica Bueda establecida por un proceso del usuario.

Planificacin de Dos /i.eles

Fos esBuemas anali-ados Casta aCora suponen Bue todos los procesos e%ecutables est8n en la

memoria principal.

Si la memoria principal es insuficienteD ocurrir8 lo si3uiente4

;abr8 procesos e%ecutables Bue se manten3an en disco.

;abr8 importantes implicaciones para la planificacinD tales como las si3uientes4

o El tiempo de alternancia entre procesos para traer y procesar un proceso del

disco es considerablemente mayor Bue el tiempo para un proceso Bue ya est8 en

la memoria principal.

o Es m8s eficiente el intercambio de los procesos con un planificador de dos

ni!eles.

El esBuema operati!o de un planificador de dos ni!eles es como si3ue4

1. Se car3a en la memoria principal cierto subcon%unto de los procesos e%ecutables.

2. El planificador se restrin3e a ellos durante cierto tiempo.

3. Peridicamente se llama a un planificador de ni!el superior para efectuar las si3uientes

tareas4

1. Eliminar de la memoria los procesos Bue Cayan permanecido en ella el tiempo

suficiente.

2. 'ar3ar a memoria los procesos Bue Cayan estado en disco demasiado tiempo.

4. El planificador de ni!el inferior se restrin3e de nue!o a los procesos e%ecutables Bue se

encuentren en la memoria.

". El planificador de ni!el superior se encar3a de despla-ar los procesos de memoria a

disco y !ice!ersa.

Fos criterios Bue podr<a utili-ar el planificador de ni!el superior para tomar sus decisiones son

los Bue se indican a continuacin4

K'u8nto tiempo Ca transcurrido desde el ltimo intercambio del procesoL.

K'u8nto tiempo de cpu Ca utili-ado recientemente el procesoL.

K6uA tan 3rande es el procesoL 13eneralmente los procesos peBue5os no causan tantos

problemas en este sentido2.

K6uA tan alta es la prioridad del procesoL.

El planificador de ni!el superior podr<a utili-ar cualBuiera de los mAtodos de planificacin

anali-ados.

)ultiprocesamiento

Introduccin

Es una tendencia si3nificati!a en el campo de la computacin.

'onsiste en confi3urar un sistema de computacin con !arios procesadores .

No es un enfoBue nue!o pero s< posee 3randes perspecti!as en funcin del desarrollo de los

microprocesadores.

Se podr<an concebir sistemas construidos por cientos o miles de microprocesadores.

2onfiabilidad

Si un procesador fallaD los restantes continan operandoD lo cual no es autom8tico y reBuiere de

un dise5o cuidadoso.

En procesador Bue falla Cabr8 de informarlo a los dem8s de al3una maneraD para Bue se Ca3an

car3o de su traba%o.

Fos procesadores en funcionamiento deben poder detectar el fallo de un procesador

determinado.

El Sistema perati!o debe percibir Bue Ca fallado un procesador determinado y ya no podr8

asi3narlo y tambiAn debe a%ustar sus estrate3ias de asi3nacin de recursos para e!itar la

sobrecar3a del sistema Bue est8 de3radado.

!3plotacin del Paralelismo

La ma1or2a de los sistemas de multiprocesamiento tienen como meta principal el incremento de

la capacidad de ejecucin.

Fa pro3ramacin si3ue siendo esencialmente secuencial y 3eneralmente no se e:plota la

concurrencia.

Fas principales ra-ones son las si3uientes4

Fas personas piensan en forma secuencial.

Nin3n len3ua%e Cumano proporciona la e:presin adecuada de paralelismoD pero

e:isten len3ua%es de computacin con soporte de concurrencia 1por e%emploD )daD

Pascal 'oncurrenteD etc.2.

Ni el multiprocesamiento Ca sido usado con amplitud para e:plotar el paralelismo.

El Card>are tradicional del computador est8 orientado Cacia la operacin secuencial.

Es muy dif<cil depurar pro3ramas en paralelo.

Fos multiprocesadores no se utili-an a menudo para e:plotar el paralelismo ya Bue es muy

escaso el soft>are Bue e:plote el paralelismo.

Fo deseable es Bue los Sistemas perati!os y compiladores puedan detectar e implementar el

paralelismo autom8ticamente.

Paralelismo )asi.o

Se debe disponer de suficientes procesadores como para Bue todas las operaciones Bue puedan

ser e%ecutadas en paralelo puedan ser asi3nadas a procesadores separados.

Esto ofrece una forma de e%ecutar un pro3rama en el menor tiempo posible.

Fa cuestin central esD disponiendo del paralelismo masi!oD Kcu8l es el tiempo m<nimo

reBuerido para e%ecutar un al3oritmo determinadoL.

)etas de los Sistemas de )ultiprocesamiento

Fas metas de los sistemas de multiprocesamiento 3eneralmente son la confiabilidad y la

disponibilidad muy altasD como as< tambiAn el incremento del poder de computacin.

El dise5o modular proporciona una fle:ibilidad importante y facilita la e:pansin de la

capacidad.

Deteccin Autom8tica del Paralelismo

Fos multiprocesadores Cacen posible la e:plotacin del paralelismo.

Fos sistemas de computacin obtienen los beneficios del procesamiento concurrente m8s por la

multiprogramacin de !arios procesos y menos por la e:plotacin del paralelismo dentro

de un solo proceso.

Fa deteccin del paralelismo es un problema comple%o y la puede efectuar el pro3ramadorD el

traductor del len3ua%eD el Card>are o el Sistema perati!o.

El paralelismo dentro de los pro3ramas puede ser e)pl2cito o impl2cito.

Fas principales caracter<sticas del paralelismo e)pl2cito son las Bue se detallan a continuacin4

Es indicado de forma espec<fica por un pro3ramador mediante una Gconstruccin de

concurrenciaH como la si3uiente4

cobegin>

proposicin '>

................

proposicin n>

coend>

Se pueden utili-ar procesadores separados para e%ecutar cada una de las proposiciones.

Es susceptible de errores de pro3ramacin dif<ciles de detectar y depurar.

El pro3ramador puede omitir tratar situaciones donde ser<a aplicable el paralelismo.

Fas principales caracter<sticas del paralelismo impl2cito son las Bue se detallan a continuacin4

Fa !erdadera esperan-a est8 en la deteccin autom8tica del paralelismo impl<cito.

Es el paralelismo intr<nseco del al3oritmo pero no establecido e:pl<citamente por el

pro3ramador.

Fos compiladores e:plotan el paralelismo impl<cito mediante las tAcnicas de

Gdistribucin de ciclosH y de Greduccin de la altura del 8rbolH.

Distribucin de 2iclos

Ena Gestructura de ciclos o de repeticinH implica la repeticin de una serie de proposiciones

1cuerpo del ciclo2 Casta Bue ocurre al3una condicin de terminacinD por e%emplo4

9or i ? ' to 5

Do

>

El procesador secuencial reali-ar8 en secuencia lo si3uiente4

En un sistema de multiprocesamiento con tres procesadores disponibles se podr<an e%ecutar

concurrentemente.

En compilador Bue detecte autom8ticamente el paralelismo impl<cito puede con!ertir el ciclo

del e%emplo 2.2 en lo si3uiente4

cobegin>

coend>

Esta tAcnica se denomina distribucin de ciclos.

6educcin de la Altura del @rbol

Etili-ando las propiedades asociati!aD conmutati!a y distributi!a de la aritmAticaD los

compiladores pueden4

1. Detectar el paralelismo impl<cito en e:presiones al3ebraicas.

2. Producir un cdi3o ob%eto para multiprocesadores Bue indiBue las operaciones Bue se

pueden reali-ar simult8neamente.

3. .eordenar e:presiones para Bue sean m8s apropiadas para la computacin en paralelo.

Se in!ierten m8s tiempo y recursos durante la compilacin para reducir el tiempo de e%ecucinD

es decir Bue se busca optimi-acin en el momento de la compilacin para lo3rar e%ecucin en

tiempo m<nimoD lo Bue es aplicable especialmente cuando los sistemas pasan a produccinD no

tanto cuando est8n en desarrollo 1!er /i3ura 2.#D /i3ura 2.$D /i3ura 2.& y /i3ura 2.(2.

3'4L- D'

565C-

'"P'3-3& 's mejor darle a un procesador una tarea que puede llegar a no ser utili+ada0 que

tenerlo ocioso.

1rganizacin del +ardware del )ultiprocesador

El problema cla!e es determinar los medios de cone:in de los procesadores mltiples y los

procesadores de Entrada @ Salida a las unidades de almacenamiento.

Fos multiprocesadores se caracteri-an por los si3uientes aspectos4

En multiprocesador contiene dos o m8s procesadores con capacidades

apro:imadamente comparables.

,odos los procesadores comparten el acceso a un almacenamiento comn y a canales de

Entrada @ SalidaD unidades de control y dispositi!os.

,odo est8 controlado por un Sistema perati!o Bue proporciona interaccin entre

procesadores y sus pro3ramas en los ni!eles de traba%oD tareaD pasoD arcCi!o y elementos

de datos.

Fas or3ani-aciones m8s comunes son las si3uientes4

,iempo compartido o bus comn 1conductor comn2.

7atri- de barras cru-adas e interruptores.

)lmacenamiento de intercone:in mltiple.

%iempo 2ompartido o $us 2om0n *o 2onductor 2om0n,

Esa un solo camino de comunicacin entre todas las unidades funcionales 1!er /i3ura 2.1+2.

El bus comn es en esencia una unidad pasi!a.

En procesador o procesador de Entrada @ Salida Bue desee transferir datos debe efectuar los

si3uientes pasos4

1. *erificar la disponibilidad del conductor y de la unidad de destino.

2. Informar a la unidad de destino de lo Bue se !a a Cacer con los datos.

3. Iniciar la transferencia de datos.

Fas unidades receptoras deben poder reconocer BuA mensa%es del bus son en!iados Cacia ellas y

se3uir y confirmar las se5ales de control recibidas de la unidad emisora.

Es una or3ani-acin econmicaD simple y fle:ible pero con una sola !<a de comunicacinD por lo

cual4

El sistema falla totalmente si falla el bus.

Fa tasa neta de transmisiones est8 limitada por la tasa neta de transmisin del conductor.

Fa contencin por el uso del bus en un sistema sobrecar3ado puede ocasionar una seria

de3radacin.

)atriz de $arras 2ruzadas e Interruptores

En este caso e:iste un camino diferente para cada unidad de almacenamientoD por lo cual las

referencias a dos unidades diferentes de almacenamiento no son bloBueantes sino simult8neas y

la multiplicidad de caminos de transmisin puede proporcionar tasas de transferencia muy altas

1!er /i3ura 2.112.

Almacenamiento de Intercone3in )0ltiple

Se obtiene al sacar las l3icas de controlD de conmutacin y de arbitra%e de prioridades fuera del

interruptor de barras cru-adas y se las coloca en la interfa- de cada unidad de almacenamiento

1!er /i3ura 2.122.

'ada unidad funcional puede acceder a cada unidad de almacenamientoD pero slo en una

Gcone:in de almacenamientoH espec<ficaD es decir Bue Cay una cone:in de almacenamiento

por unidad funcional.

El cone:ionado es m8s comple%o Bue en los otros esBuemas.

Se puede restrin3ir el acceso a las unidades de almacenamiento para Bue no todas las unidades

de procesamiento las accedanD en tal caso Cabr8 unidades de almacenamiento Gpri!adasH de

determinados procesadores 1!er /i3ura 2.132.

:rados de Acoplamiento en )ultiprocesamiento

Fos 3rados de acoplamiento en multiprocesamiento pueden clasificarse de ligeramente

acoplados 1!er /i3ura 2.142 o rgidamente acoplados 1!er /i3ura 2.1"2D se3n las

caracter<sticas Bue se detallan en la ,abla 2.".

:rados de acoplamiento

en multiprocesamiento

Descripcin

Fi3eramente acoplado

Incluye la cone:in de dos o m8s sistemas independientes por

medio de un enlace de comunicacin.

'ada sistema tiene su propio Sistema perati!o y

almacenamiento.

Fos sistemas pueden funcionar independientemente y se

comunican cuando sea necesario.

Fos sistemas separados pueden acceder a los arcCi!os de los

otros e intercambiar tareas a procesadores menos car3ados.

.<3idamente acoplado

Etili-a un solo almacenamiento compartido por !arios

procesadores.

Emplea un solo Sistema perati!o Bue controla todos los

procesadores y el Card>are del sistema.

%abla &.A" :rados de acoplamiento en multiprocesamiento.

1rganizacin )aestro B SatClite

En procesador est8 dise5ado como el GmaestroH y los otros como GsatAlitesH.

El procesador GmaestroH es de propsito 3eneral y reali-a operaciones de Entrada @ Salida y

computaciones.

Fos procesadores GsatAlitesH slo reali-an computaciones.

Fos procesos limitados por computacin pueden e%ecutarse con efecti!idad en los satAlites.

Fos procesos limitados por la Entrada @ Salida e%ecutados en los satAlites 3eneran frecuentes

llamadas de ser!icios al procesador maestroD pudiendo resultar ineficientes.

Si falla un satAlite se pierde capacidad computacional pero el sistema no falla.

Si falla el maestro el sistema falla al no poder efectuar operaciones de Entrada @ SalidaD por lo

Bue un satAlite deber<a asumir las funciones del maestro pre!io cambio de los perifAricos y

reinicio del sistema.

En el multiprocesamiento simAtrico todos pueden Cacer Entrada @ Salida.

Sistema 1perati.o de )ultiprocesadores

Fas capacidades funcionales de los Sistema perati!o de multipro3ramacin y de

multiprocesadores incluyen lo si3uiente4

)si3nacin y administracin de recursos.

Proteccin de tablas y con%untos de datos.

Pre!encin contra el interbloBueo del sistema.

,erminacin anormal.

EBuilibrio de car3as de Entrada @ Salida.

EBuilibrio de car3a del procesador.

.econfi3uracin.

Fas tres ltimas son especialmente importantes en Sistemas perati!os de multiprocesadoresD

donde es fundamental e:plotar el paralelismo en el Card>are y en los pro3ramas y Cacerlo

autom8ticamente.

Fas or3ani-aciones b8sicas de los Sistemas perati!os para multiprocesadores son las

si3uientes4

7aestro @ satAlite.

E%ecuti!o separado para cada procesador.

,ratamiento simAtrico 1o annimo2 para todos los procesadores.

)aestro B SatClite

Es la or3ani-acin m8s f8cil de implementar.

No lo3ra la utili-acin ptima del Card>are dado Bue slo el procesador maestro puede e%ecutar

el Sistema perati!o y el procesador satAlite slo puede e%ecutar pro3ramas del usuario.

Fas interrupciones 3eneradas por los procesos en e%ecucin en los procesadores satAlites Bue

precisan atencin del Sistema perati!o deben ser atendidas por el procesador maestro y por

ello pueden 3enerarse lar3as colas de reBuerimientos pendientes.

!jecuti.os Separados

'ada procesador tiene su propio Sistema perati!o y responde a interrupciones de los usuarios

Bue operan en ese procesador.

E:isten tablas de control con informacin 3lobal de todo el sistema 1por e%emploD lista de

procesadores conocidos por el Sistema perati!o2 a las Bue se debe acceder utili-ando

e:clusin mutua.

Es m8s confiable Bue la or3ani-acin maestro @ satAlite.

'ada procesador controla sus propios recursos dedicados.

Fa reconfi3uracin de los dispositi!os de Entrada @ Salida puede implicar el cambio de

dispositi!os a diferentes procesadores con distintos Sistemas perati!os.

Fa contencin sobre las tablas del Sistema perati!o es m<nima.

Fos procesadores no cooperan en la e%ecucin de un proceso indi!idualD Bue Cabr8 sido asi3nado

a uno de ellos.

%ratamiento SimCtrico

Es la or3ani-acin m8s complicada de implementar y tambiAn la m8s poderosa y confiable.

El Sistema perati!o administra un 3rupo de procesadores idAnticosD donde cualBuiera puede

utili-ar cualBuier dispositi!o de Entrada @ Salida y cualBuiera puede referenciar a cualBuier

unidad de almacenamiento.

El Sistema perati!o precisa cdi3o reentrante y e:clusin mutua.

Es posible eBuilibrar la car3a de traba%o m8s precisamente Bue en las otras or3ani-aciones.

)dBuieren si3nificati!a importancia el Card>are y el soft>are para resolucin de conflictos.

,odos los procesadores pueden cooperar en la e%ecucin de un proceso determinado.

El procesador ejecuti.o es el responsable 1uno slo2 en un momento dado de las tablas y

funciones del sistemaI as< se e!itan los conflictos sobre la informacin 3lobal.

6endimiento del Sistema de )ultiprocesamiento

)n con multiprocesamiento completamente simAtricoD la adicin de un nue!o procesador no

Car8 Bue la capacidad de e%ecucin del sistema aumente se3n la capacidad del nue!o

procesadorD siendo las causas las si3uientes4

;ay sobrecar3a adicional del Sistema perati!o.

Se incrementa la contencin por recursos del sistema.

;ay retrasos del Card>are en el intercambio y en el encaminamiento de las

transmisiones entre un nmero mayor de componentes.

)l incrementar el nmero de procesadores n similares en un multiprocesadorD el incremento

de la producti!idad no es lineal y tiende a disminuir cuando n crece.

6ecuperacin de !rrores

Ena de las capacidades m8s importantes de los Sistemas perati!os de multiprocesadores es la

de soportar fallas de Card>are en procesadores indi!iduales y continuar su operacin.

Debe e:istir el soporte correspondiente en el Sistema perati!o.

Fas tAcnicas de recuperacin de errores incluyen los si3uientes aspectos4

Fos datos cr<ticos 1del sistema y de usuario2 deben mantenerse en copias mltiples y en

bancos de almacenamiento separados.

El Sistema perati!o debe e%ecutar efecti!amente con la confi3uracin m8:ima y con

subcon%untos ante fallas.

Debe Caber capacidad de deteccin y correccin de errores de Card>are sin interferir

con la eficiencia operacional del sistema.

Se debe utili-ar la capacidad ociosa del procesador para tratar de detectar posibles fallos

antes de Bue se produ-can.

El Sistema perati!o debe diri3ir un procesador operati!o para Bue tome el control de

un proceso Bue se estaba e%ecutando en un procesador Bue falla.

)ultiprocesamiento SimCtrico *)PS,

'ada procesador posee capacidades funcionales completas.

Fos dispositi!os de Entrada @ Salida pueden ser conectados a cada uno de los procesadores 1!er

/i3ura 2.1#2.

,odas las llamadas al super!isor pueden ser e%ecutadas en todos los procesadoresD inclusi!e las

de Entrada @ Salida.

Si un pro3rama en e%ecucin en un procesador pide una operacin de Entrada @ Salida en un

dispositi!o conectado a un procesador diferenteD el procesador puede continuar e%ecutando el

traba%o y la Entrada @ Salida se coloca en una cola para su iniciacin por el procesador

apropiado.

Se considera procesador ejecutante al Bue est8 e%ecutando un proceso determinado.

Se considera procesador propietario al Bue est8 conectado a los diferentes dispositi!os

utili-ados por el proceso.

Es m8s eficiente Bue la or3ani-acin maestro @ satAliteD ya Bue los reBuerimientos de Entrada @

Salida se encolan y no sobrecar3an con intercambio de conte:to y a Bue en la or3ani-acin

maestro @ satAlite las peticiones de Entrada @ Salida en el satAlite pro!ocan un intercambio de

conte:to en el maestro.

'ada procesador puede e%ecutar el planificador para buscar el si3uiente traba%o a e%ecutarD de

forma Bue un proceso determinado se e%ecuta en diferentes procesadores en distintos momentosI

adem8sD el 7PS utili-a una sola cola de traba%os y cada procesador puede seleccionar traba%os

de ellaD con lo cual se eBuilibra la car3a entre los procesadores.

Para minimi-ar la contencin en el despacCo de procesosD los relo%es de los procesadores tienen

oblicuidadD debido a ello las interrupciones de relo% ocurren en diferentes momentos.

%endencias de los )ultiprocesadores

,odo indica Bue el uso de los multiprocesadores se incrementar8 considerablemente en el futuro.

Fas principales ra-ones son las si3uientes4

Fa confiabilidad reBuerida es cada !e- mayor.

Fa reduccin de costos consecuencia de los a!ances en microelectrnica.

El pre!isible desarrollo de len3ua%es Bue permitan a los usuarios e:presar el paralelismo

e:pl<citamente.

El pro3reso en la deteccin autom8tica del paralelismo.

El CecCo de Bue se estar<a lle3ando a los l<mites del uniprocesador debido a la

compactacin de componentesD es decir Bue se estar<a pr:imo a los l<mites de lon3itud

y de pro:imidad de los Gcaminos electroma3nAticosH 1lon3itud del recorrido de la se5al

electroma3nAtica2I alcan-ados los l<mites mencionadosD la nica posibilidad de

incrementar capacidad de cmputo es mediante multiprocesamiento.

E:isten estudios de tendencias en arBuitectura de computadoras Bue apuntan a los

poliprocesadoresD es decirD sistemas Bue combinan el multiprocesamientoD simAtrico y

asimAtricoD para crear una %erarBu<a de procesadores dentro de un sistema.

Anda mungkin juga menyukai

- Necesidades Del EntornoDokumen6 halamanNecesidades Del EntornoEsthela VillanuevaBelum ada peringkat

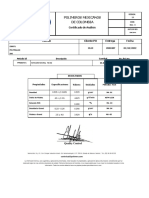

- Certicado de Calidad de Materia PrimaDokumen3 halamanCerticado de Calidad de Materia PrimaEDUAR ENRIQUE RIOS VEGABelum ada peringkat

- INFORME 2 BioquimmicaDokumen5 halamanINFORME 2 BioquimmicaEduardo Jose Lopez EspañolBelum ada peringkat

- Informe Vereda Los SochesDokumen5 halamanInforme Vereda Los SochesProtohistoriadorBelum ada peringkat

- T EspeDokumen174 halamanT EspeEdison BonillaBelum ada peringkat

- 2019-10-24 Legalizacion de GastosDokumen1 halaman2019-10-24 Legalizacion de GastosWendy AlarconBelum ada peringkat

- Taller 20 SSTDokumen3 halamanTaller 20 SSTLaura Cano100% (1)

- CO007-00-0911-SI-091 Plan - de - Izaje - Con - Side - BoomDokumen2 halamanCO007-00-0911-SI-091 Plan - de - Izaje - Con - Side - Boomroberto veraBelum ada peringkat

- Teoría de La DerivaDokumen13 halamanTeoría de La Derivaabyssmo100% (1)

- Manual Vmware WorkstationDokumen45 halamanManual Vmware WorkstationVictor Manuel Rojas SamameBelum ada peringkat

- Espectroscopia UV-Vis Determinación Simultánea de Co y CR 2019Dokumen4 halamanEspectroscopia UV-Vis Determinación Simultánea de Co y CR 2019Sebastian OchoaBelum ada peringkat

- Ley Del Sentido ComúnDokumen3 halamanLey Del Sentido ComúnMilagros Becerra RamirezBelum ada peringkat

- Taller Parte 2Dokumen8 halamanTaller Parte 2BrandacaBelum ada peringkat

- Actividad Lúdica Proceso Estratégico IIDokumen3 halamanActividad Lúdica Proceso Estratégico IIGust CéspedesBelum ada peringkat

- Tablaturas y Acordes de Música en Españo1Dokumen2 halamanTablaturas y Acordes de Música en Españo1Josué OrdoñezBelum ada peringkat

- v4 Anexo5 PPI - Elementos Metálicos CFarallonesDokumen1 halamanv4 Anexo5 PPI - Elementos Metálicos CFarallonesJuan Pablo TrujilloBelum ada peringkat

- Libro Multidivi.2024Dokumen176 halamanLibro Multidivi.2024anita24091966Belum ada peringkat

- Gestion Del Agua 2013 PDFDokumen48 halamanGestion Del Agua 2013 PDFJulian GonzalezBelum ada peringkat

- Manual de Guías de Turismo y Operación TurísticaDokumen16 halamanManual de Guías de Turismo y Operación Turísticasaibag56% (9)

- 1 Actividad Visitando La IslaDokumen4 halaman1 Actividad Visitando La IslaAlina Medina100% (1)

- Sesion de Matematica Primer GradoDokumen6 halamanSesion de Matematica Primer GradomiluskaBelum ada peringkat

- Ejercicio 05 Transportacion TuristicaDokumen2 halamanEjercicio 05 Transportacion TuristicaRicardo Dzacun EstrellaBelum ada peringkat

- Calculo Soldadura PDFDokumen39 halamanCalculo Soldadura PDFMaycol Ccoya CondoriBelum ada peringkat

- Grupo #4 - Casos DidácticosDokumen4 halamanGrupo #4 - Casos DidácticosSebas CardozoBelum ada peringkat

- Glosario UnescoDokumen12 halamanGlosario UnescoRicardo DoldanBelum ada peringkat

- Pennini, Gerardo.-Asesinato en El Cabare de La Manon - Mayo06 (Dokumen24 halamanPennini, Gerardo.-Asesinato en El Cabare de La Manon - Mayo06 (Santiago MiniñoBelum ada peringkat

- Rolando CcamaDokumen13 halamanRolando CcamaRolo CcBelum ada peringkat

- Plan Estratégico de Desarrollo Local Colonia Caroya: Área: Usos Del Suelo Y Ordenamiento UrbanoDokumen33 halamanPlan Estratégico de Desarrollo Local Colonia Caroya: Área: Usos Del Suelo Y Ordenamiento UrbanoAlicia Marina CavallinBelum ada peringkat

- Perfil Cargo - PresidenteDokumen1 halamanPerfil Cargo - PresidenteAsesorias PsicoFile33% (3)

- Eda 5 - 1 y 2 - Vi Ciclo Sociales ModificadoDokumen8 halamanEda 5 - 1 y 2 - Vi Ciclo Sociales ModificadoMartinMoriArrunateguiBelum ada peringkat