AR TEWS CADSTAR Electronic Specifier Power 2014

Diunggah oleh

Ganesan S0 penilaian0% menganggap dokumen ini bermanfaat (0 suara)

38 tayangan4 halamanTEWS Technologies faced increasing challenges with power integrity on their FPGA-based boards due to multiple voltage rails and power distribution networks. They added Zuken's CADSTAR Power-Integrity Advance module to their high-speed design flow to address these problems. The integrated power integrity simulation allowed TEWS to test design options early, match simulations with measurements, and reduce development time and costs by creating more right-first-time designs with fewer decoupling capacitors.

Deskripsi Asli:

About Cadstar

Hak Cipta

© © All Rights Reserved

Format Tersedia

PDF, TXT atau baca online dari Scribd

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniTEWS Technologies faced increasing challenges with power integrity on their FPGA-based boards due to multiple voltage rails and power distribution networks. They added Zuken's CADSTAR Power-Integrity Advance module to their high-speed design flow to address these problems. The integrated power integrity simulation allowed TEWS to test design options early, match simulations with measurements, and reduce development time and costs by creating more right-first-time designs with fewer decoupling capacitors.

Hak Cipta:

© All Rights Reserved

Format Tersedia

Unduh sebagai PDF, TXT atau baca online dari Scribd

0 penilaian0% menganggap dokumen ini bermanfaat (0 suara)

38 tayangan4 halamanAR TEWS CADSTAR Electronic Specifier Power 2014

Diunggah oleh

Ganesan STEWS Technologies faced increasing challenges with power integrity on their FPGA-based boards due to multiple voltage rails and power distribution networks. They added Zuken's CADSTAR Power-Integrity Advance module to their high-speed design flow to address these problems. The integrated power integrity simulation allowed TEWS to test design options early, match simulations with measurements, and reduce development time and costs by creating more right-first-time designs with fewer decoupling capacitors.

Hak Cipta:

© All Rights Reserved

Format Tersedia

Unduh sebagai PDF, TXT atau baca online dari Scribd

Anda di halaman 1dari 4

Industrial design

The truth about TRus

Conversion

IC protection

Sensors

Energy-harvesting networking

New

products

www.electronicspecier.com

april 2014 | volume 1, issue 4

Power modelling

Power integrity

is a star turn

Like many companies working with FPGA-

based boards, TEWS Technologies, the

embedded interface manufacturer based in

Hamburg, faces increasing power integrity

challenges due to the multiple voltage rails

needed by ICs. Todays designs can contain

dozens of power distribution networks

(PDNs), creating complex design scenarios

for the engineers who have to make them

work. In addition, they needed to meet

the highly complex impedance targets

and decoupling requirements specied

by semiconductor vendors, while still

complying with signal integrity rules.

The company has been using Zukens

CADSTAR for its PCB design process,

increasing their use of different high-speed

options in recent years, using tools such as

advanced high-

speed modules

for constraint

management and

constraint-driven

routing, and

signal integrity

simulation in

pre- and post-

layout phases.

The company

recently added

CADSTAR

Power-Integrity

Advance module to the

high-speed design ow to

address design problems

around power distribution on PCBs.

Acting early in

the design phase

Ralf Brning, senior product specialist for

high-speed and analysis tools at Zuken

EMC Technology Center Paderborn,

Germany, worked alongside TEWS in the

initial implementation to ensure smooth

setup of the new analysis module. Several

initial projects were designed to shorten the

tool introduction phase, and Ralf made sure

there was close cooperation in the initial

stages.

We had been working with TEWS for

a number of years, which made getting

the project up and running much easier.

Having an established high-speed process

Power integrity module

is a star turn

TEWS reduced development time and

cost of complex high-speed PCBs using

concurrent power integrity simulation.

Michael Kltzow, TEWS Technologies

explains how it was done.

12

electronicspecier.com

Application story

TEWS

interface card.

in place also made it more straightforward

when it came to enhancing the design

process analysis capability, as for example

information such as IBIS models were

already available for each new design.

To verify signal integrity, TEWS compared

the simulation and impedance results with

measurements performed by their board

manufacturers. Then they compared the

Power Integrity Advance analysis results

with analytical attempts on specially

designed structures. The company

was pleased by the match between the

simulation results and measurements and

gained condence in the power integrity

simulation capabilities as well.

It is essential that correct signal routing and

bus termination is guaranteed to ensure

reliable operation. The impedance-controlled

layer and target of 55 needed to closely

match PCB specications for SI and power

distribution systems.

Tight integration

The Zuken SI Verify and Power Integrity

Advance tools were quick and easy to use

from the outset. TEWS soon began to take

advantage of a recently added link from

Constraint Manager and high-speed routing

into the Power Integrity Advance tool that

allows the design engineer to perform

power integrity analysis (AC and decoupling

analysis, as well DC investigations) prior to

full board routing. This supports a virtual

power integrity prototyping environment

in which the designer can test different

design options without the delay and cost of

creating a full prototype.

Integrating signal integrity or power integrity

tools into a CAD design environment often

involves a translator that extracts the design

database and creates intermediate les for

the analysis. The resulting design process

can be cumbersome: the engineer must

export a design le, invoke the analysis

software, make notes of the results, return

to the design tool to make adjustments, and

then repeat this process until an acceptable

solution is found.

Integration

The integrated Signal Integrity and

Power Integrity analysis modules offer

a more streamlined alternative. The

engineer invokes the simulator from

the PCB CAD tool, works on selected

elements, or even the entire design,

makes design changes and immediately

re-analyses the results.

This is a much higher level of integration

than has previously been possible with third-

party analysis solutions. It lets us integrate

analysis very early in the design process;

a capability that is becoming increasingly

critical to a projects success, said Peter

Zimmermann, head of hardware design,

TEWS.

With power integrity analysis linked directly

to the CADSTAR constraint-based PCB

design process, the design can be re-

simulated during or after each layout step to

ensure no problems have been introduced.

14

electronicspecier.com

Application story

High speed

design ow

EMI compliance

TEWS soon realised that they were able

to try different decoupling schemes, layer

spacing and power distribution area layout

schemes using what-if capabilities. The

company supplies products to international

markets, so EMI and EMC compliance are

also critical. This requirement was satised

by using the EMI module within the Power

Integrity Advance toolset, using algorithms

developed at Missouri University of Science

and Technology (formerly the University of

Missouri-Rolla), to predict the worst-case

emission levels of a PCB.

Even though the company did not expect

to match chamber measurement with

accurate dBs, the ease-of-use and reliability

of the results of Power-Integrity Advance

EMI, together with its fast analysis, gave

important hints about radiation hot spots on

the board well before the rst prototype.

Decoupling

reduction

Since integrating

Power Integrity

Advance in

design ow,

TEWS has realised its goal of designing

a PDN capable of providing charge to

all the ICs on a minimal number of PCB

layers. CAD designers are able to perform

power integrity analysis during the power

distribution layout and work closely with

electronics engineers to ensure that

sufcient power is being delivered to all ICs.

Design changes may then dictate changes

to PDNs and/or the placement of capacitors

on the PCB.

Designers were condent the layer stack-

up that matched the PDN impedance

target, an optimal power-net routing and an

effective decoupling scheme even before

manufacturing the rst board. Prototypes

testing agreed with what had been

experienced using Zukens simulation tools.

Creating more right-the-rst-time designs,

the company reports that another benet

is being able to reduce the number of

decoupling capacitors, which adds up to a

signicant reduction in manufacturing costs.

www.zuken.com

Application story

Power Integrity

Advance illustrates

current distribution.

CAD designers are able to

perform power integrity analysis

during the power distribution

layout ensuring sufcient power

is being delivered to all ICs.

Anda mungkin juga menyukai

- Design and Test Strategies for 2D/3D Integration for NoC-based Multicore ArchitecturesDari EverandDesign and Test Strategies for 2D/3D Integration for NoC-based Multicore ArchitecturesBelum ada peringkat

- Mesh Generation For Modelling in Magnet - 1988 - Mathematical and Computer ModelDokumen5 halamanMesh Generation For Modelling in Magnet - 1988 - Mathematical and Computer ModeldarshanBelum ada peringkat

- Arduino Measurements in Science: Advanced Techniques and Data ProjectsDari EverandArduino Measurements in Science: Advanced Techniques and Data ProjectsBelum ada peringkat

- Electromagnetics: Realize Your Product PromiseDokumen12 halamanElectromagnetics: Realize Your Product PromisemirfanbilalBelum ada peringkat

- 2021 Price List: Power ToolsDokumen7 halaman2021 Price List: Power ToolsRolando Albuquerque MartinsBelum ada peringkat

- Mentorpaper 102410Dokumen7 halamanMentorpaper 102410Sandesh Kumar B VBelum ada peringkat

- 079 01ismot BbruDokumen8 halaman079 01ismot Bbrutabu1099Belum ada peringkat

- SKM 2019 Price ListDokumen7 halamanSKM 2019 Price ListDaniel CamargoBelum ada peringkat

- 7555-Article Text-24162-3-10-20230418Dokumen14 halaman7555-Article Text-24162-3-10-20230418Victor BermejoBelum ada peringkat

- Review of The CAD Process: Chapter TwoDokumen49 halamanReview of The CAD Process: Chapter TwoAlagu MurugesanBelum ada peringkat

- GaN TransistorsDokumen4 halamanGaN TransistorsDheeraj SharmaBelum ada peringkat

- NI CaseStudy Cs 13453Dokumen7 halamanNI CaseStudy Cs 13453Anonymous C6PQv75QZBelum ada peringkat

- LjusevDokumen6 halamanLjusevrute silvaBelum ada peringkat

- Testing Challenges of A Complete PAC Digital SubstationDokumen9 halamanTesting Challenges of A Complete PAC Digital Substationchandraippa2Belum ada peringkat

- SPEL ThailandDokumen38 halamanSPEL ThailandRajesh Barkur100% (1)

- Best Practices For High Speed Digital PCB DesignDokumen25 halamanBest Practices For High Speed Digital PCB DesignhishuresBelum ada peringkat

- Electronics Engineering Thesis TitleDokumen4 halamanElectronics Engineering Thesis Titleaflnzraiaaetew100% (2)

- Electronics 10 00271 v2Dokumen22 halamanElectronics 10 00271 v2rathorsumit2006Belum ada peringkat

- Wattch: Framework For Architectural-Level Power Analysis and OptimizationsDokumen12 halamanWattch: Framework For Architectural-Level Power Analysis and OptimizationsUmekalsoomBelum ada peringkat

- DSP Architecture Design EssentialsDokumen353 halamanDSP Architecture Design Essentialssup3rnarutoBelum ada peringkat

- Electrical Systems Test Engineer in Phoenix AZ Resume Edward SchultzDokumen3 halamanElectrical Systems Test Engineer in Phoenix AZ Resume Edward SchultzEdwardSchultzBelum ada peringkat

- Defect Based TestDokumen14 halamanDefect Based TestCiprian FloreaBelum ada peringkat

- Real-Time Electro-Thermal Modelling and Predictive Control Design of Resonant Power Converter in Full Electric Vehicle ApplicationsDokumen20 halamanReal-Time Electro-Thermal Modelling and Predictive Control Design of Resonant Power Converter in Full Electric Vehicle ApplicationsTejas krishnakanthBelum ada peringkat

- Full Adder SynopsisDokumen10 halamanFull Adder SynopsisAbhishek ShekBelum ada peringkat

- Electrical Engineer ThesisDokumen6 halamanElectrical Engineer Thesislcdmrkygg100% (2)

- A Simple Yet Efficient Accuracy-Configurable Adder DesignDokumen14 halamanA Simple Yet Efficient Accuracy-Configurable Adder DesignVinay KelurBelum ada peringkat

- Siemens PLM Improving Electromechanical Design Collaboration WP 71985 A7Dokumen7 halamanSiemens PLM Improving Electromechanical Design Collaboration WP 71985 A7Avante TanBelum ada peringkat

- Optimized Design of Substation Grounding System UsDokumen7 halamanOptimized Design of Substation Grounding System Usmehrnoosh fakhariBelum ada peringkat

- Research Paper Electrical EngineeringDokumen6 halamanResearch Paper Electrical Engineeringc9rvcwhf100% (1)

- NeedsDokumen4 halamanNeedsSK kmBelum ada peringkat

- CST Flyer EMC Web RfmsDokumen4 halamanCST Flyer EMC Web Rfmsfahadned5717Belum ada peringkat

- Master Thesis Topics in Electrical EngineeringDokumen6 halamanMaster Thesis Topics in Electrical EngineeringDoMyCollegePaperForMeSingapore100% (2)

- RSRC TEL Making Substations PaperDokumen9 halamanRSRC TEL Making Substations PaperCrit TandBelum ada peringkat

- Engineer Technician Electronics Design in Portland Oregon Resume Gary SailerDokumen3 halamanEngineer Technician Electronics Design in Portland Oregon Resume Gary SailerGarySailer2Belum ada peringkat

- Pre Synthesis and Post Synthesis Power Estimation of VLSI Circuits Using Machine Learning ApproachDokumen15 halamanPre Synthesis and Post Synthesis Power Estimation of VLSI Circuits Using Machine Learning Approachsohan kambleBelum ada peringkat

- A Modular Simulink-Based Controlled Three-Phase Switch Mode InverterDokumen7 halamanA Modular Simulink-Based Controlled Three-Phase Switch Mode InverterLee EzzitouniBelum ada peringkat

- Software EEE2Dokumen12 halamanSoftware EEE2dchidembaram941967Belum ada peringkat

- Electrical Engineering Thesis TitlesDokumen4 halamanElectrical Engineering Thesis Titlesdwc59njw100% (2)

- Practices Resulting From Migration To IEC 61850Dokumen9 halamanPractices Resulting From Migration To IEC 61850DanielAlejandroRamosQueroBelum ada peringkat

- Drofenik APE07Dokumen11 halamanDrofenik APE07saravanajsrBelum ada peringkat

- Mohit Sarwal 1272392794Dokumen5 halamanMohit Sarwal 1272392794techgovindBelum ada peringkat

- The Azerbaijani Experiences in Digital Substation Deployment. How Process Bus and IEC 61850 Addresses Utility RequirementsDokumen18 halamanThe Azerbaijani Experiences in Digital Substation Deployment. How Process Bus and IEC 61850 Addresses Utility Requirementspo ghBelum ada peringkat

- Signal Integrity Engineer or Power Integrity Engineer or HardwarDokumen3 halamanSignal Integrity Engineer or Power Integrity Engineer or Hardwarapi-121403633Belum ada peringkat

- VlsiDokumen32 halamanVlsibalasaravanan0408Belum ada peringkat

- Automating Wire Harness Design in Today's Automotive, Aerospace and Marine IndustryDokumen8 halamanAutomating Wire Harness Design in Today's Automotive, Aerospace and Marine IndustryMos CraciunBelum ada peringkat

- High Speed Digital Design PrinciplesDokumen16 halamanHigh Speed Digital Design PrinciplesXiaofang ChenBelum ada peringkat

- IET Computers Digital Tech - 2023 - Cao - Multi Objective Digital Circuit Block Optimisation Based On Cell Mapping in AnDokumen15 halamanIET Computers Digital Tech - 2023 - Cao - Multi Objective Digital Circuit Block Optimisation Based On Cell Mapping in Anabel belaBelum ada peringkat

- DS CR 5000 Board Designer en v2Dokumen2 halamanDS CR 5000 Board Designer en v2mryalamrbBelum ada peringkat

- Sample Thesis For Electrical Engineering StudentsDokumen5 halamanSample Thesis For Electrical Engineering Studentsamymoorecincinnati100% (2)

- 2.06095515-Compiler-Directed Energy Reduction Using Dynamic Voltage Scaling and Voltage Islands For Embedded SystemsDokumen11 halaman2.06095515-Compiler-Directed Energy Reduction Using Dynamic Voltage Scaling and Voltage Islands For Embedded SystemsPhan Giang ChâuBelum ada peringkat

- Whitepaper Substation Automation Schneider ElectricDokumen5 halamanWhitepaper Substation Automation Schneider Electricsahil4INDBelum ada peringkat

- An On Chip Design For Prepaid Electricity Billing System: P .G, S.D P, T C SDokumen7 halamanAn On Chip Design For Prepaid Electricity Billing System: P .G, S.D P, T C SBhaskar YalamoluBelum ada peringkat

- DVR Based ThesisDokumen5 halamanDVR Based Thesistinajordanhuntsville100% (1)

- Siemens PLM Adding Intelligence To Your Electrical System EbookDokumen8 halamanSiemens PLM Adding Intelligence To Your Electrical System EbookSARABelum ada peringkat

- Digital Substation Deployment AjarbaizanDokumen8 halamanDigital Substation Deployment AjarbaizanInayat HathiariBelum ada peringkat

- Design of A Novel Energy Efficient Double Tail Dynamic ComparatorDokumen5 halamanDesign of A Novel Energy Efficient Double Tail Dynamic ComparatorerpublicationBelum ada peringkat

- CYME Power Engineering SoftwareDokumen4 halamanCYME Power Engineering SoftwareMuhammad Faizan AwanBelum ada peringkat

- A Review of Low Power Processor DesignDokumen9 halamanA Review of Low Power Processor DesignNalini RadhakrishnanBelum ada peringkat

- 0710ijcnc04 PDFDokumen10 halaman0710ijcnc04 PDFJam 234Belum ada peringkat

- Predicting Fusing Time of Overloaded PCB Traces Can We Predict It at All - With Douglas Brooks, PHD and Dr. Johannes Adam - ARTECH HOUSE INSIDERDokumen12 halamanPredicting Fusing Time of Overloaded PCB Traces Can We Predict It at All - With Douglas Brooks, PHD and Dr. Johannes Adam - ARTECH HOUSE INSIDERGanesan SBelum ada peringkat

- Final - Radio Technology WuDokumen15 halamanFinal - Radio Technology WuGanesan SBelum ada peringkat

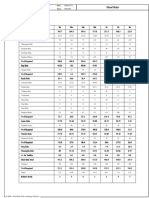

- PCB Trace Width Calculator - Trace Width vs. Current TableDokumen5 halamanPCB Trace Width Calculator - Trace Width vs. Current TableGanesan SBelum ada peringkat

- Gap Analysis of GNSS Receivers and Technology: GSA-227890 GRAMMAR D1.4 Version 1.17Dokumen72 halamanGap Analysis of GNSS Receivers and Technology: GSA-227890 GRAMMAR D1.4 Version 1.17Ganesan SBelum ada peringkat

- MMIC/RFIC For Receivers Front-End: To Cite This VersionDokumen7 halamanMMIC/RFIC For Receivers Front-End: To Cite This VersionGanesan SBelum ada peringkat

- Angelina Jolie VARSHAPHALADokumen1 halamanAngelina Jolie VARSHAPHALAGanesan SBelum ada peringkat

- Angelina Jolie Shad BalaDokumen1 halamanAngelina Jolie Shad BalaGanesan S100% (1)

- New Thermasim™ Online Mosfet Thermal Simulation ToolDokumen4 halamanNew Thermasim™ Online Mosfet Thermal Simulation ToolGanesan SBelum ada peringkat

- Installation Guide of AstrotransitDokumen3 halamanInstallation Guide of AstrotransitGanesan SBelum ada peringkat

- Prepared and Compiled by Govindon Gopalan (Harish)Dokumen1 halamanPrepared and Compiled by Govindon Gopalan (Harish)Ganesan SBelum ada peringkat

- 25 Myths About PATENTS Demystified EbookDokumen52 halaman25 Myths About PATENTS Demystified EbookGanesan SBelum ada peringkat

- Using PATENTS To Reduce R&D Efforts: First Edition 2016Dokumen31 halamanUsing PATENTS To Reduce R&D Efforts: First Edition 2016Ganesan SBelum ada peringkat

- Intellectual Property Rights: Handbook OnDokumen50 halamanIntellectual Property Rights: Handbook OnGanesan SBelum ada peringkat

- Rarnasu: Sub: - Contactless Book Scanner RegDokumen1 halamanRarnasu: Sub: - Contactless Book Scanner RegGanesan SBelum ada peringkat

- Unep Pops Nip Belgium 1.englishDokumen115 halamanUnep Pops Nip Belgium 1.englishGanesan SBelum ada peringkat

- Thermal Management of Visible Leds: Application Bulletin 228Dokumen4 halamanThermal Management of Visible Leds: Application Bulletin 228Ganesan SBelum ada peringkat

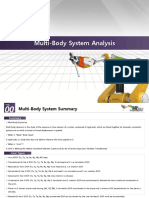

- A11 MBS (Analyst)Dokumen15 halamanA11 MBS (Analyst)Ganesan SBelum ada peringkat

- A6 Direct Frequency Response (a-NFX2014)Dokumen41 halamanA6 Direct Frequency Response (a-NFX2014)Ganesan SBelum ada peringkat

- Alternator: From Wikipedia, The Free EncyclopediaDokumen8 halamanAlternator: From Wikipedia, The Free EncyclopediaAsif Al FaisalBelum ada peringkat

- Chapter 1: Investment Landscape: Financial GoalsDokumen8 halamanChapter 1: Investment Landscape: Financial GoalsshubhamBelum ada peringkat

- Concrete For Water StructureDokumen22 halamanConcrete For Water StructureIntan MadiaaBelum ada peringkat

- Lemon AidDokumen17 halamanLemon AidJade Anne Mercado BalmesBelum ada peringkat

- Binder 1Dokumen107 halamanBinder 1Ana Maria Gálvez Velasquez0% (1)

- Writing Task The Strategy of Regional Economic DevelopementDokumen4 halamanWriting Task The Strategy of Regional Economic DevelopementyosiBelum ada peringkat

- Scope of Internet As A ICTDokumen10 halamanScope of Internet As A ICTJohnBelum ada peringkat

- Fletcher Theophilus Ato CVDokumen7 halamanFletcher Theophilus Ato CVTHEOPHILUS ATO FLETCHERBelum ada peringkat

- Load Sharing Strategies in Multiple Compressor Refrigeration SystemsDokumen8 halamanLoad Sharing Strategies in Multiple Compressor Refrigeration SystemsLiu YangtzeBelum ada peringkat

- OrganometallicsDokumen53 halamanOrganometallicsSaman KadambBelum ada peringkat

- Managerial Accounting-Fundamental Concepts and Costing Systems For Cost Analysis Module 1Dokumen40 halamanManagerial Accounting-Fundamental Concepts and Costing Systems For Cost Analysis Module 1Uzma Khan100% (1)

- EE1000 DC Networks Problem SetDokumen7 halamanEE1000 DC Networks Problem SetAmit DipankarBelum ada peringkat

- Study of Risk Perception and Potfolio Management of Equity InvestorsDokumen58 halamanStudy of Risk Perception and Potfolio Management of Equity InvestorsAqshay Bachhav100% (1)

- Nat Law 2 - CasesDokumen12 halamanNat Law 2 - CasesLylo BesaresBelum ada peringkat

- Payment of GratuityDokumen5 halamanPayment of Gratuitypawan2225Belum ada peringkat

- Effects of Organic Manures and Inorganic Fertilizer On Growth and Yield Performance of Radish (Raphanus Sativus L.) C.V. Japanese WhiteDokumen5 halamanEffects of Organic Manures and Inorganic Fertilizer On Growth and Yield Performance of Radish (Raphanus Sativus L.) C.V. Japanese Whitepranjals8996Belum ada peringkat

- CEA 4.0 2022 - Current Draft AgendaDokumen10 halamanCEA 4.0 2022 - Current Draft AgendaThi TranBelum ada peringkat

- 7Dokumen101 halaman7Navindra JaggernauthBelum ada peringkat

- Powerpoint Presentation R.A 7877 - Anti Sexual Harassment ActDokumen14 halamanPowerpoint Presentation R.A 7877 - Anti Sexual Harassment ActApple100% (1)

- Sun Nuclear 3D SCANNERDokumen7 halamanSun Nuclear 3D SCANNERFranco OrlandoBelum ada peringkat

- PPB 3193 Operation Management - Group 10Dokumen11 halamanPPB 3193 Operation Management - Group 10树荫世界Belum ada peringkat

- 0063 - Proforma Accompanying The Application For Leave WITHOUT ALLOWANCE Is FORWARDED To GOVERNMEDokumen4 halaman0063 - Proforma Accompanying The Application For Leave WITHOUT ALLOWANCE Is FORWARDED To GOVERNMESreedharanPN100% (4)

- Sign Language To Speech ConversionDokumen6 halamanSign Language To Speech ConversionGokul RajaBelum ada peringkat

- We Move You. With Passion.: YachtDokumen27 halamanWe Move You. With Passion.: YachthatelBelum ada peringkat

- The Role of OrganisationDokumen9 halamanThe Role of OrganisationMadhury MosharrofBelum ada peringkat

- Lexington School District Two Return To School GuideDokumen20 halamanLexington School District Two Return To School GuideWLTXBelum ada peringkat

- Rehabilitation and Retrofitting of Structurs Question PapersDokumen4 halamanRehabilitation and Retrofitting of Structurs Question PapersYaswanthGorantlaBelum ada peringkat

- Projects: Term ProjectDokumen2 halamanProjects: Term ProjectCoursePinBelum ada peringkat

- Millionaire Next Door QuestionsDokumen7 halamanMillionaire Next Door Questionsapi-360370073Belum ada peringkat

- Sealant Solutions: Nitoseal Thioflex FlamexDokumen16 halamanSealant Solutions: Nitoseal Thioflex FlamexBhagwat PatilBelum ada peringkat

- The 7 Habits of Highly Effective PeopleDari EverandThe 7 Habits of Highly Effective PeoplePenilaian: 4 dari 5 bintang4/5 (2567)

- High Road Leadership: Bringing People Together in a World That DividesDari EverandHigh Road Leadership: Bringing People Together in a World That DividesBelum ada peringkat

- Summary of Noah Kagan's Million Dollar WeekendDari EverandSummary of Noah Kagan's Million Dollar WeekendPenilaian: 5 dari 5 bintang5/5 (2)

- The Coaching Habit: Say Less, Ask More & Change the Way You Lead ForeverDari EverandThe Coaching Habit: Say Less, Ask More & Change the Way You Lead ForeverPenilaian: 4.5 dari 5 bintang4.5/5 (186)

- Scaling Up: How a Few Companies Make It...and Why the Rest Don't, Rockefeller Habits 2.0Dari EverandScaling Up: How a Few Companies Make It...and Why the Rest Don't, Rockefeller Habits 2.0Penilaian: 5 dari 5 bintang5/5 (2)

- The First Minute: How to start conversations that get resultsDari EverandThe First Minute: How to start conversations that get resultsPenilaian: 4.5 dari 5 bintang4.5/5 (57)

- The Emotionally Intelligent LeaderDari EverandThe Emotionally Intelligent LeaderPenilaian: 4.5 dari 5 bintang4.5/5 (204)

- How to Talk to Anyone at Work: 72 Little Tricks for Big Success Communicating on the JobDari EverandHow to Talk to Anyone at Work: 72 Little Tricks for Big Success Communicating on the JobPenilaian: 4.5 dari 5 bintang4.5/5 (37)

- Billion Dollar Lessons: What You Can Learn from the Most Inexcusable Business Failures of the Last Twenty-five YearsDari EverandBillion Dollar Lessons: What You Can Learn from the Most Inexcusable Business Failures of the Last Twenty-five YearsPenilaian: 4.5 dari 5 bintang4.5/5 (52)

- Transformed: Moving to the Product Operating ModelDari EverandTransformed: Moving to the Product Operating ModelPenilaian: 4.5 dari 5 bintang4.5/5 (2)

- How to Lead: Wisdom from the World's Greatest CEOs, Founders, and Game ChangersDari EverandHow to Lead: Wisdom from the World's Greatest CEOs, Founders, and Game ChangersPenilaian: 4.5 dari 5 bintang4.5/5 (95)

- The Power of People Skills: How to Eliminate 90% of Your HR Problems and Dramatically Increase Team and Company Morale and PerformanceDari EverandThe Power of People Skills: How to Eliminate 90% of Your HR Problems and Dramatically Increase Team and Company Morale and PerformancePenilaian: 5 dari 5 bintang5/5 (22)

- Spark: How to Lead Yourself and Others to Greater SuccessDari EverandSpark: How to Lead Yourself and Others to Greater SuccessPenilaian: 4.5 dari 5 bintang4.5/5 (132)

- The Introverted Leader: Building on Your Quiet StrengthDari EverandThe Introverted Leader: Building on Your Quiet StrengthPenilaian: 4.5 dari 5 bintang4.5/5 (35)

- Unlocking Potential: 7 Coaching Skills That Transform Individuals, Teams, & OrganizationsDari EverandUnlocking Potential: 7 Coaching Skills That Transform Individuals, Teams, & OrganizationsPenilaian: 4.5 dari 5 bintang4.5/5 (28)

- Transformed: Moving to the Product Operating ModelDari EverandTransformed: Moving to the Product Operating ModelPenilaian: 4 dari 5 bintang4/5 (1)

- 7 Principles of Transformational Leadership: Create a Mindset of Passion, Innovation, and GrowthDari Everand7 Principles of Transformational Leadership: Create a Mindset of Passion, Innovation, and GrowthPenilaian: 5 dari 5 bintang5/5 (52)

- The 7 Habits of Highly Effective People: 30th Anniversary EditionDari EverandThe 7 Habits of Highly Effective People: 30th Anniversary EditionPenilaian: 5 dari 5 bintang5/5 (337)

- The E-Myth Revisited: Why Most Small Businesses Don't Work andDari EverandThe E-Myth Revisited: Why Most Small Businesses Don't Work andPenilaian: 4.5 dari 5 bintang4.5/5 (709)

- Management Mess to Leadership Success: 30 Challenges to Become the Leader You Would FollowDari EverandManagement Mess to Leadership Success: 30 Challenges to Become the Leader You Would FollowPenilaian: 4.5 dari 5 bintang4.5/5 (27)

- Good to Great by Jim Collins - Book Summary: Why Some Companies Make the Leap...And Others Don'tDari EverandGood to Great by Jim Collins - Book Summary: Why Some Companies Make the Leap...And Others Don'tPenilaian: 4.5 dari 5 bintang4.5/5 (64)

- Leadership Skills that Inspire Incredible ResultsDari EverandLeadership Skills that Inspire Incredible ResultsPenilaian: 4.5 dari 5 bintang4.5/5 (11)

- Summary: Choose Your Enemies Wisely: Business Planning for the Audacious Few: Key Takeaways, Summary and AnalysisDari EverandSummary: Choose Your Enemies Wisely: Business Planning for the Audacious Few: Key Takeaways, Summary and AnalysisPenilaian: 4.5 dari 5 bintang4.5/5 (3)

- Summary of Marshall Goldsmith & Mark Reiter's What Got You Here Won't Get You ThereDari EverandSummary of Marshall Goldsmith & Mark Reiter's What Got You Here Won't Get You TherePenilaian: 3 dari 5 bintang3/5 (2)

- Leading with Character: 10 Minutes a Day to a Brilliant Legacy SetDari EverandLeading with Character: 10 Minutes a Day to a Brilliant Legacy SetBelum ada peringkat

- 300+ PMP Practice Questions Aligned with PMBOK 7, Agile Methods, and Key Process Groups - 2024: First EditionDari Everand300+ PMP Practice Questions Aligned with PMBOK 7, Agile Methods, and Key Process Groups - 2024: First EditionPenilaian: 5 dari 5 bintang5/5 (1)

- Sun Tzu: The Art of War for Managers; 50 Strategic RulesDari EverandSun Tzu: The Art of War for Managers; 50 Strategic RulesPenilaian: 5 dari 5 bintang5/5 (5)