Ijiris:: Area Efficient Encoding Technique For Reducing Power in DSRC

Judul Asli

Hak Cipta

Format Tersedia

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniHak Cipta:

Format Tersedia

Ijiris:: Area Efficient Encoding Technique For Reducing Power in DSRC

Hak Cipta:

Format Tersedia

International Journal of Innovative Research in Information Security (IJIRIS)

Volume 1 Issue 3 (September 2014)

ISSN: 2349-7017(O)

ISSN: 2349-7009(P)

www.ijiris.com

AREA EFFICIENT ENCODING TECHNIQUE FOR

REDUCING POWER IN DSRC

Mr.S.PRAKASH1, K.UMADEVI2, Dr.V.NAGARAJAN3

Assistant Professor, PG Scholar, Head of the Department

Dept.of.ECE, Adhiparasakthi Engineering College, Melmaruvathur.

Abstract ---- The Dedicated Short Range Communication is an emerging Technique. It is one way or two way short range to

medium range wireless communication which is important in real time applications such as safety application commercial

vehicle application emergency warning system for vehicle and intersection collision avoidance etc. The DSRC adopts the

FM0/MANCHESTER code. The codes are used to achieve dc-balance and signal reliability. The similarity oriented logic

simplification Technique (SOLS) is used here. This method is used to overcome the limitations and it also used to improve the

hardware utilization rate. In these both coding have the number of the components. In this paper analyzed to reduce the number

of components. Using the both code to reduce the power, delay, area in DSRC. The power consumption is 29392.843nW for

Manchester and fm0 encoding, and area is 203M. This paper implemented in cadence software.

Key words DSRC,FM0,MANCHESTER,SOLS.

1.

INTRODUCTION

The dedicated short range communication is a protocol for one or two way medium range communication. The DSRC can be briefly

classified into two categories: automobile-to-automobile and automobile-to roadside. In automobile-to-automobile, the DSRC

enables the message sending and broadcasting among automobile. The automobile-to-roadside focuses on the intelligent

transportation service, such as electronic toll collection (ETC).The DSRC architecture having the transceiver. The transceiver

having the baseband processing, RF front end and microprocessor. The microprocessor is used to transfer the instruction to the

baseband processing and RF front end. the RF front end is used to transmit and receive the wireless signals using the antenna. The

baseband processing is responsible for modulation, error correction, encoding and synchronization. The transmitted signal consists

of the arbitrary binary sequence, it is very difficult to obtain the dc-balance.the fm0 and Manchester are provide the transmitted

signal and then the dc-balance. The (SOLS) similarity oriented logic simplification having the two methods: area compact retiming

and balance logic operation sharing. The area compact retiming used to reduce the transistor counts .the balance logic operation

sharing is used to combine the fm0 and Manchester encoding.

II.

PRINCIPLES OF FM0 CODE AND MANCHESTER CODE

A .Fm0 encoding

The FM0 having the following three rules.

1) If X is the logic-0,The fm0 code has the transition between the A and B.

2) If X is the logic-1,There is no transition is allowed between the A and B.

3) The transition is allocated in each FM0 code.

The wave form is given below the following diagram.the fm0 having the clock and then the x.the clock and then the cycle having

the cycle in each transaction.

Fig.1.FM0 encoding

B. Manchester encoding

The Manchester encoding is realized with the XOR operation for using the CLOCK and X. The clock always has a transition within

the one cycle.

__________________________________________________________________________________________________________

2014, IJIRIS- All Rights Reserved

Page -7

International Journal of Innovative Research in Information Security (IJIRIS)

Volume 1 Issue 3 (September 2014)

ISSN: 2349-7017(O)

ISSN: 2349-7009(P)

www.ijiris.com

Fig.2. Manchester encoding

III. THE STATE CODE PRINCIPLE FOR FM0/MANCHESTER:

The Manchester encoding is an XOR operation only. The FM0 code starts with the FSM principle. The FSM of FM0 code classified

into four states. The four states as shown in the below figure.

Fig.3.FSM of FM0

Fig.4.State diagram

Suppose the initial state is S1, and its state code is 11 for A and B, respectively.

1) If the X is logic-0, the state-transition must follow both rules for FM01 and 3. The only one next-state that can satisfy both

rules for the X of logic-0 is S3. If the X is logic-1, the state-transition must follow both rules for FM0 2 and 3. The only

one next-state that can satisfy both rules for the X of logic-1 is S4. Thus, the state-transition of each state can be completely

constructed. The FSM of FM0 can also conduct the transition table of each state A(t) and B(t) represent the discrete-time

state code of current-state at time instant t. Their previous-states are denoted as the A(t 1)and the B(t 1), respectively.

With this transition table, the Boolean functions of A(t) and B(t) are given as

2)

A(t) = B(t 1)

B(t) = X B(t 1)

With both A(t) and B(t), the Boolean function of FM0 code is denoted as

CLK A(t) +~ CLK B(t)

TABLE-I

Previous state

Current state

A(t-1)

A(t)

X=0

0

1

1

1

1

1

0

0

B(t-1)

1

0

1

0

X=1

0

1

0

1

B(t)

X=0 X=1

1 0

0

1

1

1

0

1

__________________________________________________________________________________________________________

2014, IJIRIS- All Rights Reserved

Page -8

International Journal of Innovative Research in Information Security (IJIRIS)

Volume 1 Issue 3 (September 2014)

ISSN: 2349-7017(O)

ISSN: 2349-7009(P)

www.ijiris.com

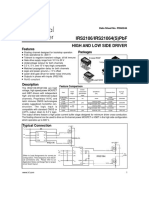

IV. HARDWARE ARCHITECTURE OF FM0/MANCHESTER CODE.

Fig.5.Hardware architecture

This is the hardware architecture of the fm0/Manchester code. the top part is denoted the fm0 code and then the bottom part is

denoted as the Manchester code. in fm0 code the DFFA and DFFB are used to store the state code of the fm0 code and also mux_1

and not gate is used in the fm0 code. when the mode=0 is for the fm0 code. the Manchester code is developed only using the XOR

gate and when the mode=1 is for the Manchester code. the hardware utilization rate is defined as the following.

=

The active components means the components are work in the both fm0 and Manchester code. The total components means the

number of the components are present in the hole circuit. the HUR rate is given below the following section

TABLE-II

Coding

Active components(transistor

count)/ total components

(transistor count)

HUR

FM0

6(86)/7(98)

2(26)/7(98)

4(56)/7(98)

85.71%

28.57%

57.14%

MANCHESTER

AVERAGE

For both the encoding methods the total components is 7.for the fm0 code the total component is 7 and then the active component is

6.in Manchester code the total component is 7 the active component is 2.in both coding having 98 transistors are used without

SOLS. The fm0 having 86 transistor, and then the Manchester having the 26 transistor. the average for both coding is 56 transistors

.In proposed work reduce the total components from 7 to 6 and reduce the transistor counts. In this paper two multiplexer is used in

proposed work reduce two multiplexer from one multiplexer, when reduce the multiplexer the total components are reduced the area

and then the power consumption also reduced.

V. FMO AND MANCHESTER ENCODER USING SOLS TECHNIQUE:

The SOLS technique is classified into two parts area compact retiming and balance logic operation sharing

A. area compact retiming

For fm0 the state code of the each state is stored into DFFA and DFFB .the transition of the state code is only depends on

the previous state of B(t-1) instead of the both A(t-1) and B(t-1)

__________________________________________________________________________________________________________

2014, IJIRIS- All Rights Reserved

Page -9

International Journal of Innovative Research in Information Security (IJIRIS)

Volume 1 Issue 3 (September 2014)

Fig.6.Area compact retiming

ISSN: 2349-7017(O)

ISSN: 2349-7009(P)

www.ijiris.com

Fig.7.FM0 encoding without area compact retiming.

The previous state is denoted as the A(t-1) and then the B(t-1).and then the current state is denoted as the A(t) and then the B(t)

Fig.8.FM0 encoding with area compact retiming.

Thus, the FM0 encoding just requires a single 1-bitflip-flop to store the previous value B(t1).If the DFFA is directly removed, a

non synchronization between A(t) and B(t)causes the logic fault of FM0 code. To avoid this logic-fault, the DFFB is relocated right

after the MUX1, where the DFFB is assumed be positive-edge triggered flip flop. At each cycle, the FM0 code, comprising A and

B, is derived from the logic of A(t) and the logic of B(t), respectively. The FM0 code is alternatively switched between A(t) and B(t)

through the MUX1 by the control signal of the CLK. In the Q of DFFB is directly updated from the logic of B(t)with 1-cycle

latency. when the CLK is logic-0, the B(t) is passed through MUX1 to the D of DFFB. Then, the upcoming positive-edge of CLK

updates it to the Q of DFFB. the timing diagram for the Q of DFFB is consistent whether the DFFB is relocated or not. the B(t) is

passed through MUX1 to the D of DFFB. Then, the upcoming positive-edge of CLK updates it to the Q of DFFB. the timing

diagram for the Q of DFFB is consistent whether the DFFB is relocated or not. The transistor count of the FM0 encoding

architecture without area-compact retiming is 72,and that with area-compact retiming is 50. The area-compact retiming technique

reduces 22 transistors.

B.Bbalance logic operation sharing

The Manchester encoding is derived using the XOR operation. the equation of the XOR gate is given below.

X CLK=X CLK+~ X CLK

the concept of balance logic-operation sharing is to integrate the X into A(t) and X into B(t).the fm0 and Manchester logics have a

common point of the multiplexer like logic with the selection of the CLK. the diagram for the balance logic operation sharing given

the following.

The A(t) can be derived from an inverter of B(t 1), and X is obtained by an inverter of X. The logic for A(t)/X can share

the same inverter, and then a multiplexer is placed before the inverter to switch he operands of B(t 1) and X. The Mode indicates

eitherFM0 or Manchester encoding is adopted. The similar concept can be also applied to the logic for B(t)/X

Fig.9.Balance logic operation sharing

__________________________________________________________________________________________________________

2014, IJIRIS- All Rights Reserved

Page -10

International Journal of Innovative Research in Information Security (IJIRIS)

Volume 1 Issue 3 (September 2014)

ISSN: 2349-7017(O)

ISSN: 2349-7009(P)

www.ijiris.com

Nevertheless, this architecture exhibits a drawback that the XOR is only dedicated for FM0 encoding, and is not shared with

Manchester encoding. Therefore, the HUR of this architecture is certainly limited. The X can be also interpreted as the X 0, and

thereby the XOR operation can be shared with Manchester and FM0 encodings, where the multiplexer irresponsible to switch the

operands of B(t1) and logic-0. This architecture shares the XOR for both B(t) and X, and there by increases the HUR. When the

FM0 code is adopted, the CLR is disabled, and the B(t 1) can be derived from DFFB .Hence, the multiplexer can be totally saved,

and its function can be completely integrated into the relocated DFF. The logic for A(t)/X includes the MUX2 and an inverter.

Instead ,the logic for B(t)/X just incorporates a XOR gate. In the logic for A(t)/X, the computation time of MUX2is almost

identical to that of XOR in the logic for B(t)/X. However, the logic for A(t)/X further incorporates an inverter in the series of

MUX2. This unbalance computation time between A(t)/X and B(t)/X results in the glitch to MUX1,possibly causing the logicfault on coding. To alleviate this unbalance computation time, the architecture of the balance computation time between A(t)/X and

B(t)/X The XOR in the logic for B(t)/X is translated into the XNOR with an inverter, and then this inverter is shared with that of the

logic for A(t)/X. This shared inverter is relocated backward to the output of MUX1. Thus, the logic computation time between

A(t)/X and B(t)/X is more balance to each other.

TABLE-II

Coding methods

realization

2003

Manchester

0.35umm CMOS

2009

Manchester

90nm CMOS

1.2 V

CMOS switch

2008

Manchester

Xilinx FPGA

Spartan 2

N/A

FSM based design

2009

FM0

Xilinx FPGA

Spartan 2

N/A

FSM based design

N/A

1GHZ[1.94GHZ]

N/A

5GHZ[2.5GHZ

N/A

256.54MHZ

N/A

192.64MHZ

2013

Manchester

Xilinx FPGA

Spartan 2

N/A

Joint MODEM

codec

N/A

612MHZ

Supply voltage

Technique

3.3 V

Gated inverter

HUR

Operation

frequency

Power

consumption

Area

Transistor count

N/A

N/A

N/A

N/A

34MW

N/A

54

N/A

26

N/A

N/A

N/A

N/A

N/A

N/A

FPGA resource

usage

N/A

N/A

Slice:1

Filp flop:2

LUTS:2

Bonded IOBS:3

Slice:5

Filp flop:4

LUTS:10

Bonded IOBS:4

Slice:1

Filp flop:0

LUTS:1

Bonded IOBS:3

The adoption of FM0 or Manchester code depends on Mode and CLR. In addition, the CLR further has another individual function

of a hardware initialization. If the CLR is simply derived by inverting Mode without assigning an individual CLR control signal,

this leads to a conflict between the coding mode selection and the hardware initialization. To avoid this conflict, both Mode and

CLR are assumed to be separately allocated to this design froma system controller. Whether FM0 or Manchester code is adopted, no

logic component of the proposed VLSI architecture is wasted. Every component is active in both FM0 and Manchester encodings.

Therefore, the HUR of the proposed VLSI architecture is greatly improved

VI. CONCLUSION

The coding-diversity between FM0 and Manchester encodings causes the limitation on hardware utilization of VLSI architecture

design. A limitation analysis on hardware utilization of FM0 and Manchester encodings is discussed in detail. In this paper, the fully

reused VLSI architecture using SOLS technique for both FM0 and Manchester encodings is proposed. The SOLS technique

eliminates the limitation on hardware utilization by two core techniques: area compact retiming and balance logic-operation sharing.

The area-compact retiming relocates the hardware resource to reduce the transistors. The balance logic-operation sharing efficiently

combines FM0 and Manchester encodings with the identical logic components. This paper is realized in 180nm technology with an

outstanding device efficiency. The power consumption is 29392.843nW for Manchester encoding and FM0 encoding.

__________________________________________________________________________________________________________

2014, IJIRIS- All Rights Reserved

Page -11

International Journal of Innovative Research in Information Security (IJIRIS)

Volume 1 Issue 3 (September 2014)

ISSN: 2349-7017(O)

ISSN: 2349-7009(P)

www.ijiris.com

VII. RESULT

VIII.

REFERENCE

[1] F. Ahmed-Zaid, F. Bai, S. Bai, C. Basnayake, B. Bellur, S. Brovold, et al., Vehicle safety communicationsApplications

(VSC-A) final report, U.S. Dept. Trans., Nat. Highway Traffic Safety Admin., Washington,DC, USA, Rep. DOT HS 810 591,

Sep. 2011.

[2] J. B. Kenney, Dedicated short-range communications (DSRC) standards in the United States, Proc. IEEE, vol. 99, no. 7, pp.

11621182,Jul. 2011.

[3] J. Daniel, V. Taliwal, A. Meier, W. Holfelder, and R. Herrtwich,Design of 5.9 GHz DSRC-based vehicular safety

communication,IEEE Wireless Commun. Mag., vol. 13, no. 5, pp. 3643, Oct. 2006.

[4] P. Benabes, A. Gauthier, and J. Oksman, A Manchester code generator running at 1 GHz, in Proc. IEEE, Int. Conf. Electron.,

Circuits Syst.,vol. 3. Dec. 2003, pp. 11561159.

[5] A. Karagounis, A. Polyzos, B. Kotsos, and N. Assimakis, A 90nm Manchester code generator with CMOS switches running at

2.4 GHz and 5 GHz, in Proc. 16th Int. Conf. Syst., Signals Image Process., Jun. 2009, pp. 14.

[6] Y.-C. Hung, M.-M. Kuo, C.-K. Tung, and S.-H. Shieh, High-speedCMOS chip design for Manchester and Miller encoder, in

Proc. Intell. Inf. Hiding Multimedia Signal Process., Sep. 2009, pp. 538541.

[7] M. A. Khan, M. Sharma, and P. R. Brahmanandha, FSM based Manchester encoder for UHF RFID tag emulator, in Proc. Int.

Conf.Comput., Commun. Netw., Dec. 2008, pp. 16.

[8] M. A. Khan, M. Sharma, and P. R. Brahmanandha, FSM based FM0 and Miller encoder for UHF RFID tag emulator, in Proc.

IEEE Adv. Comput. Conf., Mar. 2009, pp. 13171322.

[9] J.-H. Deng, F.-C. Hsiao, and Y.-H. Lin, Top down design of joint MODEM and CODEC detection schemes for DSRC codedFSK systems over high mobility fading channels, in Proc. Adv. Commun. Technol. Jan. 2013, pp. 98103.

[10] I.-M. Liu, T.-H. Liu, H. Zhou, and A. Aziz, Simultaneous PTL buffer insertion and sizing for minimizing Elmore delay, in

Proc. Int. Workshop Logic Synth., May 1998, pp. 162168.

[11] H. Zhou and A. Aziz, Buffer minimization in pass transistor logic, IEEE Trans. Comput. Aided Des. Integr. Circuits Syst.,

vol. 20, no. 5, pp. 693697, May 2001.

[12] N. H. E. Weste and K. Eshraghian, Principles of CMOS VLSI Design: A Systems Perspective, 2nd ed., Upper Saddle River,

NJ, USA: Pearson Educ. Ltd., 1993, pp. 98103.

[13] Fully Reused VLSI Architecture of FM0/Manchester Encoding Using SOLS Technique for DSRC Applications Yu-Hsuan Lee,

Member, IEEE, and Cheng-Wei Pan

__________________________________________________________________________________________________________

2014, IJIRIS- All Rights Reserved

Page -12

Anda mungkin juga menyukai

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeDari EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifePenilaian: 4 dari 5 bintang4/5 (5794)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreDari EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You ArePenilaian: 4 dari 5 bintang4/5 (1090)

- Never Split the Difference: Negotiating As If Your Life Depended On ItDari EverandNever Split the Difference: Negotiating As If Your Life Depended On ItPenilaian: 4.5 dari 5 bintang4.5/5 (838)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceDari EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RacePenilaian: 4 dari 5 bintang4/5 (894)

- Grit: The Power of Passion and PerseveranceDari EverandGrit: The Power of Passion and PerseverancePenilaian: 4 dari 5 bintang4/5 (587)

- Shoe Dog: A Memoir by the Creator of NikeDari EverandShoe Dog: A Memoir by the Creator of NikePenilaian: 4.5 dari 5 bintang4.5/5 (537)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureDari EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FuturePenilaian: 4.5 dari 5 bintang4.5/5 (474)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersDari EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersPenilaian: 4.5 dari 5 bintang4.5/5 (344)

- Her Body and Other Parties: StoriesDari EverandHer Body and Other Parties: StoriesPenilaian: 4 dari 5 bintang4/5 (821)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Dari EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Penilaian: 4.5 dari 5 bintang4.5/5 (119)

- The Emperor of All Maladies: A Biography of CancerDari EverandThe Emperor of All Maladies: A Biography of CancerPenilaian: 4.5 dari 5 bintang4.5/5 (271)

- The Little Book of Hygge: Danish Secrets to Happy LivingDari EverandThe Little Book of Hygge: Danish Secrets to Happy LivingPenilaian: 3.5 dari 5 bintang3.5/5 (399)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyDari EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyPenilaian: 3.5 dari 5 bintang3.5/5 (2219)

- The Yellow House: A Memoir (2019 National Book Award Winner)Dari EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Penilaian: 4 dari 5 bintang4/5 (98)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaDari EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaPenilaian: 4.5 dari 5 bintang4.5/5 (265)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryDari EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryPenilaian: 3.5 dari 5 bintang3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnDari EverandTeam of Rivals: The Political Genius of Abraham LincolnPenilaian: 4.5 dari 5 bintang4.5/5 (234)

- On Fire: The (Burning) Case for a Green New DealDari EverandOn Fire: The (Burning) Case for a Green New DealPenilaian: 4 dari 5 bintang4/5 (73)

- The Unwinding: An Inner History of the New AmericaDari EverandThe Unwinding: An Inner History of the New AmericaPenilaian: 4 dari 5 bintang4/5 (45)

- Rise of ISIS: A Threat We Can't IgnoreDari EverandRise of ISIS: A Threat We Can't IgnorePenilaian: 3.5 dari 5 bintang3.5/5 (137)

- Automated Packaging Systems Autolabel Pi-4000 In-Line, Programmable, Thermal Transfer PrinterDokumen2 halamanAutomated Packaging Systems Autolabel Pi-4000 In-Line, Programmable, Thermal Transfer PrinterEdgar HoowerBelum ada peringkat

- IJIRIS:: Design and Development of An E-Commerce Security Using RSA CryptosystemDokumen13 halamanIJIRIS:: Design and Development of An E-Commerce Security Using RSA CryptosystemIJIRIS - INTERNATIONAL JOURNAL OF INNOVATIVE RESEARCH IN INFORMATION SECURITY100% (1)

- IJIRIS:: The Analysis of Marketing Personnel Performance Appraisal Problems of Small and Medium-Sized EnterprisesDokumen3 halamanIJIRIS:: The Analysis of Marketing Personnel Performance Appraisal Problems of Small and Medium-Sized EnterprisesIJIRIS - INTERNATIONAL JOURNAL OF INNOVATIVE RESEARCH IN INFORMATION SECURITYBelum ada peringkat

- IJIRIS:: Enhancing The Security in WSN Using Three Tier Security ArchitectureDokumen8 halamanIJIRIS:: Enhancing The Security in WSN Using Three Tier Security ArchitectureIJIRIS - INTERNATIONAL JOURNAL OF INNOVATIVE RESEARCH IN INFORMATION SECURITYBelum ada peringkat

- IJIRIS:: To Analyze Conflicts Between Software Developer and Software TesterDokumen5 halamanIJIRIS:: To Analyze Conflicts Between Software Developer and Software TesterIJIRIS - INTERNATIONAL JOURNAL OF INNOVATIVE RESEARCH IN INFORMATION SECURITYBelum ada peringkat

- IJIRIS:: Implementation and Secured Authentication Key Using Elliptic Curve CryptographyDokumen6 halamanIJIRIS:: Implementation and Secured Authentication Key Using Elliptic Curve CryptographyIJIRIS - INTERNATIONAL JOURNAL OF INNOVATIVE RESEARCH IN INFORMATION SECURITYBelum ada peringkat

- IJIRIS:: Enhancing Energy Efficiency in WSN Using Energy Potential and Energy BalancingDokumen5 halamanIJIRIS:: Enhancing Energy Efficiency in WSN Using Energy Potential and Energy BalancingIJIRIS - INTERNATIONAL JOURNAL OF INNOVATIVE RESEARCH IN INFORMATION SECURITYBelum ada peringkat

- IJIRIS:: Object Tracking System Using Motion Detection and Sound DetectionDokumen6 halamanIJIRIS:: Object Tracking System Using Motion Detection and Sound DetectionIJIRIS - INTERNATIONAL JOURNAL OF INNOVATIVE RESEARCH IN INFORMATION SECURITYBelum ada peringkat

- IJIRIS:: Coarse Grain Reconfigurable Floating Point UnitDokumen5 halamanIJIRIS:: Coarse Grain Reconfigurable Floating Point UnitIJIRIS - INTERNATIONAL JOURNAL OF INNOVATIVE RESEARCH IN INFORMATION SECURITYBelum ada peringkat

- IJIRIS:: CT-SVD and Arnold Transform For Secure Color Image WatermarkingDokumen7 halamanIJIRIS:: CT-SVD and Arnold Transform For Secure Color Image WatermarkingIJIRIS - INTERNATIONAL JOURNAL OF INNOVATIVE RESEARCH IN INFORMATION SECURITYBelum ada peringkat

- IJIRIS:: Hand Segmentation For Hand Gesture RecognitionDokumen5 halamanIJIRIS:: Hand Segmentation For Hand Gesture RecognitionIJIRIS - INTERNATIONAL JOURNAL OF INNOVATIVE RESEARCH IN INFORMATION SECURITYBelum ada peringkat

- Ijiris:: Analyse and Implement of Cryptography With High Security Using QuaternionDokumen9 halamanIjiris:: Analyse and Implement of Cryptography With High Security Using QuaternionIJIRIS - INTERNATIONAL JOURNAL OF INNOVATIVE RESEARCH IN INFORMATION SECURITYBelum ada peringkat

- IJIRIS:: Advanced Data Protection and Key Organization Framework For Mobile Ad-Hoc NetworksDokumen5 halamanIJIRIS:: Advanced Data Protection and Key Organization Framework For Mobile Ad-Hoc NetworksIJIRIS - INTERNATIONAL JOURNAL OF INNOVATIVE RESEARCH IN INFORMATION SECURITYBelum ada peringkat

- IJIRIS:: Mathematical Foundations of Multithreaded Programming Concepts in Java LanguageDokumen12 halamanIJIRIS:: Mathematical Foundations of Multithreaded Programming Concepts in Java LanguageIJIRIS - INTERNATIONAL JOURNAL OF INNOVATIVE RESEARCH IN INFORMATION SECURITYBelum ada peringkat

- IJIRIS:: A Survey of Key Management Framework For Wireless Mobile EnvironmentDokumen15 halamanIJIRIS:: A Survey of Key Management Framework For Wireless Mobile EnvironmentIJIRIS - INTERNATIONAL JOURNAL OF INNOVATIVE RESEARCH IN INFORMATION SECURITYBelum ada peringkat

- Ijiris:: Survey On Big Data Processing Using Hadoop, Map ReduceDokumen5 halamanIjiris:: Survey On Big Data Processing Using Hadoop, Map ReduceIJIRIS - INTERNATIONAL JOURNAL OF INNOVATIVE RESEARCH IN INFORMATION SECURITY100% (1)

- IJIRIS:: Coarse Grain Reconfigurable Floating Point UnitDokumen5 halamanIJIRIS:: Coarse Grain Reconfigurable Floating Point UnitIJIRIS - INTERNATIONAL JOURNAL OF INNOVATIVE RESEARCH IN INFORMATION SECURITYBelum ada peringkat

- Ijiris:: Role and Significance of Communication in Corporate WorldDokumen6 halamanIjiris:: Role and Significance of Communication in Corporate WorldIJIRIS - INTERNATIONAL JOURNAL OF INNOVATIVE RESEARCH IN INFORMATION SECURITYBelum ada peringkat

- IJIRIS:: SRAAA - Secured Right Angled and Ant Search Hybrid Routing Protocol For MANETsDokumen11 halamanIJIRIS:: SRAAA - Secured Right Angled and Ant Search Hybrid Routing Protocol For MANETsIJIRIS - INTERNATIONAL JOURNAL OF INNOVATIVE RESEARCH IN INFORMATION SECURITYBelum ada peringkat

- IJIRIS:: Big Data: Review, Classification and Analysis SurveyDokumen7 halamanIJIRIS:: Big Data: Review, Classification and Analysis SurveyIJIRIS - INTERNATIONAL JOURNAL OF INNOVATIVE RESEARCH IN INFORMATION SECURITYBelum ada peringkat

- IJIRIS:: Modernisation of Avionics and C.N.S. FacilitiesDokumen4 halamanIJIRIS:: Modernisation of Avionics and C.N.S. FacilitiesIJIRIS - INTERNATIONAL JOURNAL OF INNOVATIVE RESEARCH IN INFORMATION SECURITYBelum ada peringkat

- Ijiris:: Analyse and Implement of Cryptography With High Security Using QuaternionDokumen9 halamanIjiris:: Analyse and Implement of Cryptography With High Security Using QuaternionIJIRIS - INTERNATIONAL JOURNAL OF INNOVATIVE RESEARCH IN INFORMATION SECURITYBelum ada peringkat

- IJIRIS:: Implementation and Secured Authentication Key Using Elliptic Curve CryptographyDokumen6 halamanIJIRIS:: Implementation and Secured Authentication Key Using Elliptic Curve CryptographyIJIRIS - INTERNATIONAL JOURNAL OF INNOVATIVE RESEARCH IN INFORMATION SECURITYBelum ada peringkat

- IJIRIS:: Object Tracking System Using Motion Detection and Sound DetectionDokumen6 halamanIJIRIS:: Object Tracking System Using Motion Detection and Sound DetectionIJIRIS - INTERNATIONAL JOURNAL OF INNOVATIVE RESEARCH IN INFORMATION SECURITYBelum ada peringkat

- IJIRIS:: CT-SVD and Arnold Transform For Secure Color Image WatermarkingDokumen7 halamanIJIRIS:: CT-SVD and Arnold Transform For Secure Color Image WatermarkingIJIRIS - INTERNATIONAL JOURNAL OF INNOVATIVE RESEARCH IN INFORMATION SECURITYBelum ada peringkat

- IJIRIS:: Enhancing The Security in WSN Using Three Tier Security ArchitectureDokumen8 halamanIJIRIS:: Enhancing The Security in WSN Using Three Tier Security ArchitectureIJIRIS - INTERNATIONAL JOURNAL OF INNOVATIVE RESEARCH IN INFORMATION SECURITYBelum ada peringkat

- IJIRIS:: A Survey of Key Management Framework For Wireless Mobile EnvironmentDokumen15 halamanIJIRIS:: A Survey of Key Management Framework For Wireless Mobile EnvironmentIJIRIS - INTERNATIONAL JOURNAL OF INNOVATIVE RESEARCH IN INFORMATION SECURITYBelum ada peringkat

- IJIRIS:: Advanced Data Protection and Key Organization Framework For Mobile Ad-Hoc NetworksDokumen5 halamanIJIRIS:: Advanced Data Protection and Key Organization Framework For Mobile Ad-Hoc NetworksIJIRIS - INTERNATIONAL JOURNAL OF INNOVATIVE RESEARCH IN INFORMATION SECURITYBelum ada peringkat

- IJIRIS:: Hand Segmentation For Hand Gesture RecognitionDokumen5 halamanIJIRIS:: Hand Segmentation For Hand Gesture RecognitionIJIRIS - INTERNATIONAL JOURNAL OF INNOVATIVE RESEARCH IN INFORMATION SECURITYBelum ada peringkat

- IJIRIS:: To Analyze Conflicts Between Software Developer and Software TesterDokumen5 halamanIJIRIS:: To Analyze Conflicts Between Software Developer and Software TesterIJIRIS - INTERNATIONAL JOURNAL OF INNOVATIVE RESEARCH IN INFORMATION SECURITYBelum ada peringkat

- Embedded Systems An Integrated Approach - (PG 55 - 67)Dokumen13 halamanEmbedded Systems An Integrated Approach - (PG 55 - 67)anjul0% (1)

- Verilog TutDokumen21 halamanVerilog TutNishana KumarBelum ada peringkat

- Diagram Guardall Board With Kentic Relay Board 1Dokumen1 halamanDiagram Guardall Board With Kentic Relay Board 1Heather WallaceBelum ada peringkat

- A 32 BIT MAC Unit Design Using Vedic MultiplierDokumen6 halamanA 32 BIT MAC Unit Design Using Vedic MultiplierdycsteiznBelum ada peringkat

- IRS2106/IRS21064 high and low side driver datasheetDokumen25 halamanIRS2106/IRS21064 high and low side driver datasheetmohamedBelum ada peringkat

- AMD64 Technology AMD64 Architecture Programmer's Manual 128-Bit and 256-Bit XOP and FMA4 InstructionsDokumen276 halamanAMD64 Technology AMD64 Architecture Programmer's Manual 128-Bit and 256-Bit XOP and FMA4 Instructionsd_corsoBelum ada peringkat

- Capacitance Effect On Crosstalk Lecture26-IODokumen22 halamanCapacitance Effect On Crosstalk Lecture26-IOHema Sundar BattaBelum ada peringkat

- Uart Ip Core Specification: Systemverilog VersionDokumen20 halamanUart Ip Core Specification: Systemverilog VersionSujay M100% (1)

- Lecture 1 Introduction 2018 19 PDFDokumen36 halamanLecture 1 Introduction 2018 19 PDFswams_suni647Belum ada peringkat

- VIVEKANANDA COLLEGE Matrix Keyboard Interfacing Using 8085 and 8255 PPIDokumen4 halamanVIVEKANANDA COLLEGE Matrix Keyboard Interfacing Using 8085 and 8255 PPIParamartha BanerjeeBelum ada peringkat

- Computer Organization and Architecture MCQ8Dokumen2 halamanComputer Organization and Architecture MCQ8Kuldeep KushwahaBelum ada peringkat

- Manual DPC 3305Dokumen33 halamanManual DPC 3305Omar FernandoBelum ada peringkat

- ATtiny13, ATtiny2313, Instruction SetDokumen19 halamanATtiny13, ATtiny2313, Instruction SetMihai PaunBelum ada peringkat

- Sun Systems - Competitive Edge: Executive SummaryDokumen6 halamanSun Systems - Competitive Edge: Executive Summarysaulius_prBelum ada peringkat

- AcknowledgementsDokumen7 halamanAcknowledgementsvenkatkrishnaBelum ada peringkat

- Canonical HuffmanDokumen13 halamanCanonical HuffmanMarius IonitaBelum ada peringkat

- MDA-EMS51: 8bit Microprocessor Emulation 8051 BoardDokumen3 halamanMDA-EMS51: 8bit Microprocessor Emulation 8051 BoardAhmed BisengarBelum ada peringkat

- Question PaperDokumen6 halamanQuestion PaperLavanya Vaishnavi D.A.Belum ada peringkat

- Applied Physics: (Lab Report 08)Dokumen7 halamanApplied Physics: (Lab Report 08)NAJAMUL HassanBelum ada peringkat

- Códigos de Error MicroMotionDokumen2 halamanCódigos de Error MicroMotionCarlos Zamyr GonzalezBelum ada peringkat

- Types of Computers ExplainedDokumen28 halamanTypes of Computers ExplainedMadeehah AatifBelum ada peringkat

- MC74HC14A Hex Schmitt Trigger Inverter: High Performance Silicon Gate CMOSDokumen7 halamanMC74HC14A Hex Schmitt Trigger Inverter: High Performance Silicon Gate CMOSСтефан ТасиќBelum ada peringkat

- 15A04601 Microprocessors & MicrocontrollersDokumen1 halaman15A04601 Microprocessors & Microcontrollers17BF1A04L7 kalyanBelum ada peringkat

- Using DHCP To Control WDS PXEDokumen19 halamanUsing DHCP To Control WDS PXELeandro FerreiraBelum ada peringkat

- Experiment 8Dokumen6 halamanExperiment 8a57f06c601f1Belum ada peringkat

- Viotech 3200+ - 20190527Dokumen2 halamanViotech 3200+ - 20190527Jesus ManuelBelum ada peringkat

- Difference Between Cache and BufferDokumen2 halamanDifference Between Cache and BufferFrancesHsiehBelum ada peringkat

- Submitted To: Submitted byDokumen5 halamanSubmitted To: Submitted byIrene SultanaBelum ada peringkat

- CEGP013091: 49.248.216.238 01/02/2023 13:36:42 Static-238Dokumen5 halamanCEGP013091: 49.248.216.238 01/02/2023 13:36:42 Static-238forfives2Belum ada peringkat