Adda

Diunggah oleh

Ruri KenHak Cipta

Format Tersedia

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniHak Cipta:

Format Tersedia

Adda

Diunggah oleh

Ruri KenHak Cipta:

Format Tersedia

Prof. Ailson Rosetti de Almeida (ailson@ele.ufes.

br) Departamento de Engenharia Eltrica UFES

Eletrnica Digital II

Conversores Digital-Analgicos (DAC) e Analgico-Digitais (ADC)

Introduo

Muitas fontes de informao de variveis fsico-qumicas (sensores) que sero processadas

por sistemas digitais so de natureza analgica. O mesmo ocorre com uma vasta gama de

dispositivos que so atuados por sistemas digitais. Isto implica na necessidade de dispositivos

especiais, de natureza hbrida analgica e digital, cujas funes so a converso, ou

transformao, da amplitude analgica medida para um valor numrico, digital (conversores

analgico-digitais) ou vice-versa (conversores digital-analgicos), para fazer a interface entre

estes dois mundos.

Sinais analgicos so, em geral, contnuos no tempo e na sua amplitude. Especificamente

neste contexto, a continuidade no tempo significa que o sinal existe para qualquer instante,

dentro do intervalo de tempo considerado. A continuidade na amplitude significa que o sinal

pode assumir qualquer valor, dentro de sua faixa dinmica (a faixa dentro da qual o sinal

pode excursionar). impraticvel a aquisio (para posterior processamento e/ou

armazenamento) de sinais contnuos e variantes no tempo em todos os instantes de sua

evoluo. Necessitam, portanto, ser convertidos para digital (adquiridos) de tempo em tempo

(mas sem perda de informao), numa taxa que deve ser compatvel com a mxima freqncia

do sinal. A freqncia na qual o sinal adquirido (para converso para valor digital)

chamada freqncia de amostragem, fa. Isto acarreta a primeira discretizao introduzida

neste processo: a discretizao no tempo. O teorema de Nyquist nos diz que, desde que a

freqncia de amostragem fa seja superior ao dobro da mxima freqncia (componente

espectral) existente no sinal, no h perda de informao no processo de discretizao

temporal, e a seqncia discreta (sinal discretizado no tempo) pode ser transformada de volta,

fielmente, em um sinal contnuo no tempo.

Am plitude

(contnua)

Tem po

(contnuo)

Am plitude

(contnua)

Tem po

(dis creto)

Prof. Ailson Rosetti de Almeida (ailson@ele.ufes.br) Departamento de Engenharia Eltrica UFES

Am plitude

(dis creta)

Tem po

(dis creto)

Da mesma forma que impraticvel a aquisio do sinal a todo instante de sua evoluo,

tambm o a converso para digital do sinal adquirido com uma resoluo infinita, uma vez

que isto implicaria em um nmero digital de largura da palavra infinita. Significa que, para

que possamos armazenar e processar o nmero convertido para digital com um nmero de bits

praticvel (digamos, 8, 12 ou 16 bits), deveremos abrir mo da fidelidade da converso,

aceitando um erro de (tambm chamado rudo de) discretizao (de amplitude). A cada

instante discreto de converso, o sinal aproximado (arredondado ou truncado) para o valor

permissvel mais prximo. Os valores permissveis (discretos) esto (geralmente) igualmente

espaados ao longo de toda a faixa dinmica de converso, e o nmero de valores discretos

dependente do nmero de bits (largura da palavra) do conversor usado. O conceito de

resoluo est ligado ao passo de discretizao P, dado por:

P=

F .D.

2n

Para uma mesma faixa dinmica de converso, quanto maior a largura da palavra n, menor

ser o passo P, e portanto melhor ser a resoluo (menor a incerteza sobre o correto valor).

(2**n)P

(2**n -1)P

2P

P

P

P/2

-P/2

Prof. Ailson Rosetti de Almeida (ailson@ele.ufes.br) Departamento de Engenharia Eltrica UFES

Conversores Digital-Analgicos (D/A)

Conversores D/A so dispositivos que transformam um nmero digital binrio como entrada

em uma varivel analgica (tenso ou corrente) proporcional ao nmero digital, como sada.

O conversor aqui considerado o baseado no diagrama resistivo tipo escada (ladder) R/2R,

mostrado abaixo:

Z3

IREF

VREF

I3

Z2

R

I2

Z1

R

I1

Z0

R

I0

I3

I2

I1

I0

2R

2R

2R

2R

b3

b1

b2

0 1

0 1

0 1

2R

b0

0 1

Rf

Iout

Terra virtual

Vout

Cada chave eletrnica controlada por um bit do nmero a ser convertido para um valor

analgico. O nvel lgico de cada bit que controla a respectiva chave est indicado ao lado da

posio correspondente.

Como uma posio das chaves est aterrada (correspondente ao nvel "0" do bit controlador) e

a outra est ligada a um n que um terra virtual, portanto zero Volts (devido realimentao

negativa do amplificador operacional na configurao inversor, provocando a entrada

inversora a se aproximar da tenso da entrada no-inversora, que est aterrada), o polo de

cada chave estar sempre a zero Volts, independente da posio da chave (e portanto do

nmero binrio). Sendo assim, a impedncia Z0 ser sempre R (2R // 2R), e percorrendo da

direita para a esquerda vemos que o mesmo ocorre com as outras impedncias:

Z0 = Z1 = Z2 = Z3 = R

Assim, a corrente IREF ser constante (independente do nmero digital) e igual a I REF =

VREF

.

R

Lembre-se que VREF deve ser uma tenso muito bem estabilizada.

Alm disso, a corrente em cada n do diagrama resistivo ladder (R-2R) v dois ramos de

igual impedncia (2R) e queda de tenso, dividindo-se portanto em duas correntes iguais.

Assim,

I REF = 2 I 3 = 4 I 2 = 8 I 1 = 16 I 0

O terra virtual somente recebe contribuies de correntes das chaves cujos bits controladores

esto em nvel "1". Ento,

V

I out = b3 I 3 + b2 I 2 + b1 I 1 + bo I 0 = REF (8 b3 + 4 b2 + 2 b1 + b0 )

16 R

Algebricamente, na equao acima, cada bit bi um coeficiente de valor um ou zero

(correspondendo aos nveis lgicos "1" e "0", respectivamente), contribuindo ou no

Prof. Ailson Rosetti de Almeida (ailson@ele.ufes.br) Departamento de Engenharia Eltrica UFES

contribuindo com a respectiva corrente Ii para a corrente total do n terra virtual, Iout. Para um

nmero genrico n de largura da palavra temos:

V n 1 i

I out = REF

2 bi

n

2 R i =0

n 1

R f n 1 i

V

2

2 i bi

Vout = REF

b

P

i

n

R i =0

i =0

2

onde P o passo de discretizao (ou converso), que como sabemos a menor quantidade (o

quantum) que o conversor pode resolver.

Conversores Analgico-Digitais (ADC)

Os tipos mais importantes (e que sero considerados aqui) de conversores AD so:

Rampa ou Integrao (simples e dupla);

Aproximao Sucessiva;

Paralelo (ou Flash).

Com exceo do conversor flash, cuja parte digital combinacional, todos os outros tipos de

conversores AD envolvem mquinas finitas de estado, tendo portanto como parte digital

circuitos seqenciais.

Conversor A/D (analgico/digital) de integrao simples (rampa simples)

Uma das formas mais simples de converso A/D, o ADC de integrao (rampa) simples

utiliza um contador crescente, um integrador, e um comparador analgico:

VRef

start

clock

Q

SET

CLR

!EOC

-

+

+

count

contador

OE

Vi

BUS

Na figura acima, com alguma simplificao para facilidade, temos um integrador com

constante de tempo de integrao RC cuja entrada uma tenso de referncia VRef, uma

chave eletronicamente controlada para zerar o integrador (descarregar o capacitor), um

comparador analgico com sada compatvel TTL que compara a tenso desconhecida Vi que

se pretende converter para digital com a sada do integrador, e um bloco digital, funcionando

como uma mquina de estado, que faz o controle do conversor e a interface com o sistema

que se utiliza do conversor (cliente), como por exemplo um microprocessador.

Com o conversor inativo, a entrada start (ativa no nvel alto) est em "0", e a sada Q do flipflop tambm est zerada ("0"), garantindo o fechamento da chave eletronicamente controlada

(entrada de controle ativa no nvel baixo), mantendo o capacitor de integrao descarregado, e

inibindo o incremento do contador (count em "0"). A sada do integrador estar tambm em

zero volts, fazendo com que qualquer tenso a ser convertida Vi diferente de zero (positiva)

mantenha a sada do comparador em "1". Para iniciar uma converso, aplica-se nvel alto em

start. No prximo clock, Q estar em nvel alto, abrindo a chave, permitindo a integrao de

VRef a produz uma rampa crescente, ao mesmo tempo que libera a contagem no contador

(count = "1"). start pode ser levado novamente a "0", mas o flip-flop continua com Q = "1"

Prof. Ailson Rosetti de Almeida (ailson@ele.ufes.br) Departamento de Engenharia Eltrica UFES

devido realimentao pela porta OU. Quando a rampa ultrapassar o valor em Vi, a sada do

comparador ir para "0", congelando a contagem e zerando novamente o flip-flop no prximo

clock (Q = "0"). O prprio sinal count serve tambm como indicativo de fim de converso,

ativo em nvel baixo (!EOC) para que o sistema cliente possa saber quando o barramento de

sada conter o valor vlido da converso. O sistema cliente esto, sua convenincia, aplica

nvel alto em OE para abrir o conjunto de buffers tri-state e ler o contedo do contador, que

proporcional ao valor analgico em Vi. Na figura acima, supe-se que haja um mecanismo de

zeramento do contador antes de cada nova converso.

Para um contador com largura da palavra n bits e um perodo de clock Tclock, o maior tempo

permitido pelo contador, at atingir sua contagem mxima,

Tmax = 2 n 1 Tclock

Temos, ento, como mxima tenso atingida pela rampa do integrador correspondendo a Tmax:

T

T

1 max

(VRe f ) dt = max VRe f

RC 0

RC

que dever ser inferior tenso de saturao do amplificador operacional para manter a

linearidade da rampa.

O passo de converso P ser a tenso correspondente a um nico perodo de clock Tclock:

Vmax =

Tclock

1 clock

(

)

P=

V

dt

=

VRe f

Re

f

RC 0

RC

e o nmero de clocks (que corresponder ao valor N da contagem) necessrios para atingir Vi

ser a parte inteira (truncamento) de Vi/P. Portanto, temos

RC

V

V

contagem (valor digital) N = int i = int

i

T

P

clock V Re f

O erro de converso (de discretizao) ser a parte fracionria (mdulo) da diviso Vi/P,

podendo portanto variar de 0 a P.

Como exemplo, considere um conversor de 8 bits (n = 8), com R = 10KOhms, C = 25,5nF,

Fclock = 1MHz, VRef = 5V, e que Vi possui faixa dinmica de 0 a 5V. Na converso de uma

tenso Vi = 3,7896V, o resultado seria int(193,2696D) = 193D = C1HEX. E uma vez de posse

deste valor digital, tudo o que poderemos dizer sobre Vi que seu valor situa-se entre os

valores analgicos correspondentes aos valores digitais C1HEX e C2HEX (193D e 194D), ou seja,

entre 3,7843V e 3,8039V (usando 4 casas decimais). Nas computaes envolvendo o valor

digital adquirido (por um programa em Assembly, C, Pascal, ou outra linguagem), quando o

sistema um computador possuindo recursos que permitam clculos com nmeros reais

como, por exemplo, um PC, normalmente convertemos o nmero inteiro obtido (193D) em

uma varivel real representativa da tenso analgica (3,7843). Opcionalmente, para um

conversor como este que trunca em vez de arredondar, poderemos adicionar metade do passo

P para obter (via programa) um valor correspondente ao arredondamento. No exemplo acima,

obteramos 3,7941. Quando o sistema escasso em recursos, como um pequeno

microprocessador ou microcontrolador em uma aplicao dedicada, normalmente trabalha-se

diretamente com o valor inteiro (193D = C1HEX).

Este tipo de conversor sofre da dependncia do valor convertido contra variaes de R, de C,

da freqncia do clock, e da tenso de referncia, como mostra a equao acima. O prximo

conversor (dupla-rampa) eliminar algumas destas dependncias.

Prof. Ailson Rosetti de Almeida (ailson@ele.ufes.br) Departamento de Engenharia Eltrica UFES

Conversor A/D de integrao por dupla-rampa

Um circuito simplificado de um conversor A/D deste tipo mostrado abaixo, e seu princpio

de funcionamento como segue:

Suponha, por simplicidade, que o sinal analgico de entrada Vin unipolar positivo, podendo

variar de zero Volts at um valor mximo igual ao valor da fonte de referncia VRef. A fonte

de referncia tambm positiva (digamos, +5 Volts). O sinal de entrada passa por um buffer

inversor, fazendo com que o circuito veja Vin negativo, com polaridade oposta a VRef, ao

mesmo tempo que prov alta impedncia para o sinal a ser convertido. Quando a chave de

entrada, eletronicamente controlada, est na posio do sinal a ser medido (convertido), a

sada do integrador apresenta uma rampa ascendente, e este intervalo de tempo chamado

integrao. Quando a chave mudada para a posio VRef (que positiva), a sada do

integrador apresenta rampa descendente, e este intervalo de tempo chamado deintegrao.

A inclinao da rampa, em ambos os casos, depende dos valores de R e C (constantes), e da

tenso aplicada na entrada do integrador (Vin , que pode variar, e VRef , que constante).

Fora de um intervalo de converso, a chave eletrnica de zeramento do integrador (descarga

do capacitor) est na posio fechada, correspondendo aplicao do nvel 1 no sinal de

controle ADZero, pelo controlador digital, mantendo o integrador sempre em estado de reset;

Aps receber a solicitao para iniciar uma nova converso, o controlador digital abre a chave

de zeramento (ADZero = 0), ao mesmo tempo que posiciona a chave eletrnica de entrada

(integrao/deintegrao) na posio Vin, correspondente ao nvel 1 do sinal de controle

I/D* (Integrao/Deintegrao).

O controlador conta um intervalo de tempo fixo,

correspondendo ao tempo de integrao, que o tempo para o contador atingir seu mximo

valor (no clock seguinte voltar a zero). Atingido este tempo fixo, a chave mudada para a

posio VRef (I/D* = 0), comeando o tempo de deintegrao, a partir do qual o controlador

inicia (desde zero) uma nova contagem crescente (observe que o contador j tinha,

automaticamente, "rolado" para zero). Imediatamente, o controlador passa a monitorar o sinal

de sada do comparador (Conv), cuja sada TTL compatvel, e o controlador continua

contando at que Conv transite para o nvel alto (indicando que a sada em rampa descendente

do integrador cruzou o zero). O valor da contagem diretamente proporcional, em forma

digital, ao valor da tenso de entrada.

C

-1

Vi

VRe

I/D

Conv

ADZero

Controlador

Prof. Ailson Rosetti de Almeida (ailson@ele.ufes.br) Departamento de Engenharia Eltrica UFES

Deintegrao (VRef)

Integrao (Vin)

Vm

Contagem Fixa

Contagem

Incio Converso

vint (t1 ) =

1

RC

t1

t0

Fim (Cruz. Zero)

v(t ) dt + vint (t 0 )

onde vint(t0) a condio inicial do intervalo sendo integrado.

Inclinao da rampa tan = Vint/t = -V/RC

tanI = Vint/TI = Vi/RC (I varivel, TI fixo) tanD = Vint/TD = -VRef/RC (D fixo, TD varivel)

Para o perodo de integrao, temos:

v(t) = -Vi;

t0 = 0;

vint(t0) = 0;

t1 = TI = (2n)Tclock;

v int (TI ) =

TI

Vi

RC

Para o perodo de deintegrao, temos;

v(t) = VRef; t0 = TI; vint(t0) = vint(TI); t1 = TD = NTclock;

vint(TD) = 0 (cruzamento de zero);

onde N o valor da contagem quando ocorreu o cruzamento de zero (fim do perodo de

deintegrao).

2 n Tclock

TD

N Tclock

v int (TD ) = 0 =

VRe f + v int (TI ) =

VRe f +

VI

RC

RC

RC

2 n Tclock

N Tclock

Vi =

V Re f

RC

RC

Portanto, vemos que qualquer desvio no valor de R, C, ou Tclock afetar a integrao mas ser

cancelado na deintegrao, desde que o desvio no ocorra durante uma converso. Como

variaes em valores de componentes no costumam ser abruptas e sim lentamente ao longo

do tempo, seja por envelhecimento (fadiga), por variaes de temperatura, etc, podemos

considerar que durante uma converso (cujo tempo para este conversor da ordem de

milisegundos), os valores destes parmetros, embora possivelmente alterados, permanecem

constantes e sero cancelados. A dependncia sobre VRef ainda permanece, como ocorre em

todo tipo de conversor (afinal, no fosse assim no precisaramos chamar de referncia). A

relao entre o nmero digital e o valor analgico ento ser:

Prof. Ailson Rosetti de Almeida (ailson@ele.ufes.br) Departamento de Engenharia Eltrica UFES

2n

V

N = int

Vi = int i

VRe

P

f

Observe que Vi no pode ser superior a VRef sob pena de a deintegrao no conseguir cruzar

o zero antes do contador atingir seu valor mximo, em cuja situao ele "rolaria" para zero

continuando contando at o evento de cruzamento.

Uma caracterstica muito vantajosa do conversor por dupla-rampa a seguinte: suponha que

durante uma converso (que dura, tipicamente para este tipo, ordem de milisegundos) o sinal

Vi no seja retido constante, sendo deixado variar no seu curso. Durante o perodo de

integrao, o valor vint(TI) atingido pelo integrador no final deste perodo ser o mesmo que se

tivssemos utilizado o valor mdio da varivel a ser convertida vi(t) neste mesmo perodo.

Significa que, alm de obtermos um valor representativo de vi(t) neste perodo ao invs de um

valor digital errneo, rudos aditivos de rpida flutuao sero eliminados.

Conversor A/D por aproximao sucessiva

Para melhor entendermos e apreciarmos o conversor por aproximao sucessiva,

conveniente voltarmos ao conversor de rampa (integrao) simples. L, vimos que aquele

conversor tinha dependncia com os valores de R e C. Que tal se substitussemos o integrador

analgico por um "integrador digital", construdo com um contador crescente (o mesmo que

j existe) cuja sada alimenta um conversor digital-analgico? A sada deste "integrador

digital" ser uma rampa discretizada (em "escadinha") que ser aplicada entrada do

comparador para a comparao com Vi. Assim, embora com o custo adicional de um

conversor D/A, teremos eliminado a dependncia de R e C (bem como os prprios

componentes). Alm do mais, agora no h mais a necessidade da chave eletrnica, pois o

zeramento (reset) do "integrador digital" ser feito simplesmente pelo reset de seu contador

associado. O que este integrador digital faz (bem como seu equivalente analgico) uma

busca linear, ou seja, parte de um valor mnimo (zero), crescendo linearmente na busca de um

valor comparvel com a tenso desconhecida. Se o valor instantneo de Vi sendo convertido

for baixo dentro de sua faixa dinmica, a busca ser rpida. Caso contrrio, ser mais

demorada. No caso do conversor original de rampa-simples, isto tinha que ser assim, uma vez

que estvamos limitados gerao analgica de formas de ondas simples, como a rampa.

Agora que modernizamos para digital, podemos fazer a busca de forma mais eficiente: em vez

de usar um simples contador crescente, que faz uma busca linear, podemos utilizar um

registrador (ou contador) de aproximao sucessiva, que permite uma busca binria.

Vi

comp

Registrador de

aproximao sucessiva

clock

OE

BUS

VRef

start

Conversor D/A

de n bits

EOC

Prof. Ailson Rosetti de Almeida (ailson@ele.ufes.br) Departamento de Engenharia Eltrica UFES

No incio de uma converso (iniciada pela entrada start), o valor do registrador de

aproximao sucessiva de n bits ajustado no valor binrio 1000...0 (somente o bit bn-1 = 1),

que corresponde metade da faixa de valores com n bits. Sua sada (digital) serve de entrada

para o conversor D/A, cuja referncia VRef. Para este valor digital inicial, a sada (analgica)

do DAC metade de VRef. Esta sada do DAC comparada com Vi pelo comparador com

sada compatvel TTL. Se comp = 0, significa que Vi localiza-se na sub-faixa inferior

(primeira metade) de VRef. Caso contrrio, na superior, e podemos prosseguir a busca

restringindo-a apenas sub-faixa correspondente. Isto feito fixando (e no mais alterando) o

valor do bit mais significativo bn-1 a 0 ou 1, de acordo com o indicado pela comparao comp.

Para o esquema acima, basta fazer bi = comp. O prximo passo ser o teste do bit bn-2. Faz-se

bn-2 = 1 e testa-se comp. Se comp = 0 (1), significa que Vi situa-se na sub-faixa (metade)

inferior (superior) da sub-faixa anteriormente encontrada. Fixamos, ento, bn-2 = comp e

prosseguimos para o teste dos demais bits, at o menos significativo. Vemos que,

independente do valor de Vi, a busca por aproximao sucessiva (ou binria) leva um tempo

fixo, dependente somente do nmero n de bits (e, claro, do clock). A busca leva exatamente n

passos de teste, como visto no algoritmo abaixo. O registrador de aproximao sucessiva RAS

nada mais que um registrador simples de n flip-flops regido por este algoritmo:

RAS = 0000...0;

Para i = (n-1) at 0 faa

{

bi = 1;

Se (comp == 0) ento bi = 0;

}

/* onde bi o bit i de RAS */

/* caso contrrio, deixe-o em 1 */

Como o tempo de converso deste ADC por aproximao sucessiva determinstico

(plenamente conhecido e independente do valor instantneo de Vi) e pequeno, ele um dos

mais utilizados, especialmente em aplicaes de tempo real como controle e automao.

Como exemplo, suponha um conversor de 12 bits com um clock de 12 MHz. Se conseguirmos

realizar cada teste em um s perodo de clock, a converso levar 1 seg.

Prof. Ailson Rosetti de Almeida (ailson@ele.ufes.br) Departamento de Engenharia Eltrica UFES

10

Conversor A/D paralelo (flash)

O conversor paralelo, ou flash, de funcionamento muito simples, embora dispendioso. Para

uma largura da palavra (resoluo) de n bits, consiste em um divisor resistivo multi-tomadas

com (2n ) resistores, (2n-1) comparadores com sadas compatveis com a lgica utilizada, e um

circuito lgico combinacional, como mostra a figura abaixo:

Vi

VRef

Rf

R

R

+

+

OE

Circuito combinacional

conversor de codificao

esparsa para codificao

densa (compacta)

BUS

R

Ri

O divisor resistivo faz a gerao dos valores (analgicos) discretos relativos a VRef. Os

comparadores informam ao circuito combinacional em que posio entre dois valores

discretos consecutivos (mltiplos de um passo P) encontra-se Vi. Este, por sua vez, faz a

transformao desta informao em uma codificao densa (compacta), que a combinao

de n bits que utilizamos. Como exemplo, se tivermos Ri = Rf = R e se Vi estiver entre o ksimo e (k+1)-simo passo de discretizao, teremos como sadas dos comparadores, do

superior para o inferior:

000000...001111..11

com 2n-1 bits, onde os k menos significativos so "1" e os demais "0", porque Vi superior a

todas as tomadas do divisor abaixo da posio k. O que o circuito combinacional tem que

fazer somar todos os 1's de sua entrada de 2n-1 bits, para obter a combinao normal

(compacta), o que se consegue usando somente n bits como sadas do bloco combinacional.

Com Ri = Rf = R, obtemos uma discretizao com truncamento. Com estes valores de Ri e Rf,

a primeira tomada de comparao (1,0)*P, a segunda (2,0)*P, e assim por diante, at a

ltima que (2n-1)*P, onde P o passo de discretizao, igual a VRef/2n.

Para termos arredondamento, basta que Ri = R/2 e Rf = 3R/2. Com estes valores de Ri e Rf, a

primeira tomada de comparao 0,5P, a segunda 1,5P, e assim por diante, at a ltima que

(2n-1,5)*P.

Este conversor praticamente dispensa sinais de interface como start e EOC (fim de

converso), uma vez que sua operao virtualmente instantnea, limitada somente pelos

atrasos de propagao nos comparadores e no bloco combinacional. Dado seu relativamente

alto custo de implementao e consumo de energia, atualmente encontramos dispositivos

comerciais deste conversor limitados ao redor dos 8 bits. Sua grande rea de aplicao na

digitalizao de sinais de vdeo.

Anda mungkin juga menyukai

- Manual Tecnico Levsahggsajhgante SP HibridaDokumen15 halamanManual Tecnico Levsahggsajhgante SP HibridaRuri KenBelum ada peringkat

- Wiki ArqDokumen1 halamanWiki ArqRuri KenBelum ada peringkat

- Aula5 MicroDokumen17 halamanAula5 MicroRuri KenBelum ada peringkat

- Apostila 8051 PDFDokumen60 halamanApostila 8051 PDFWagner RibeiroBelum ada peringkat

- Comandos IrvineDokumen1 halamanComandos IrvineRuri KenBelum ada peringkat

- Asm 20Dokumen9 halamanAsm 20Ruri KenBelum ada peringkat

- Tabela Intelbras PSDDokumen83 halamanTabela Intelbras PSDDienio VazBelum ada peringkat

- DSE8660 Operators ManualDokumen76 halamanDSE8660 Operators ManualRobertoSoares100% (1)

- Ipet 2Dokumen10 halamanIpet 2Pedrito CoelhoBelum ada peringkat

- Sistema de Som 1DinDokumen23 halamanSistema de Som 1Din81968Belum ada peringkat

- Apostila IniciantesDokumen141 halamanApostila IniciantesGuest100% (2)

- Waves GTR Solo - Funciona Com o Win 7 64 Bit - KVR AudioDokumen4 halamanWaves GTR Solo - Funciona Com o Win 7 64 Bit - KVR AudioHélio MandecoBelum ada peringkat

- Ds m3004v 1615614 PT 1605Dokumen2 halamanDs m3004v 1615614 PT 1605Edilson Marcio BorgesBelum ada peringkat

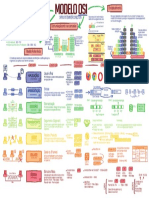

- Modelo OSI e encapsulamento de dadosDokumen1 halamanModelo OSI e encapsulamento de dadosJosinaldo JuniorBelum ada peringkat

- Criação e configuração de políticas no GravityzoneDokumen11 halamanCriação e configuração de políticas no GravityzoneAlyson MoraisBelum ada peringkat

- Exercicios InternetDokumen9 halamanExercicios InternetJoca VidalBelum ada peringkat

- Manual de Treinamento Fiscal de LojaDokumen4 halamanManual de Treinamento Fiscal de LojaFuRyos PowerBelum ada peringkat

- Manual - Kurumim REP3Dokumen31 halamanManual - Kurumim REP3Tais ApcBelum ada peringkat

- Notebook Toshiba Infinity NI 1401 com Windows 8 de 14 polegadasDokumen2 halamanNotebook Toshiba Infinity NI 1401 com Windows 8 de 14 polegadasEurides Vicente MarcondesBelum ada peringkat

- Programa de Designacoes Da Escola Do Ministerio Teocratico Pdemt 2015Dokumen94 halamanPrograma de Designacoes Da Escola Do Ministerio Teocratico Pdemt 2015Felipe Na cozinha com vocêBelum ada peringkat

- My NetAcad Resources Courses Careers MoreDokumen1 halamanMy NetAcad Resources Courses Careers MoreClara Carolina0% (1)

- Teste o Exame Final Do JFo Java FoundationsDokumen16 halamanTeste o Exame Final Do JFo Java FoundationsScribdTranslationsBelum ada peringkat

- Busca Linear Binária Vetor Estrutura DadosDokumen15 halamanBusca Linear Binária Vetor Estrutura DadosAlisson FerreiraBelum ada peringkat

- Rastreabilidade AgroDokumen22 halamanRastreabilidade AgroEduardo SallesBelum ada peringkat

- AULA 4 - Conversor AD e PWM PDFDokumen75 halamanAULA 4 - Conversor AD e PWM PDFLaercio MarquesBelum ada peringkat

- 1 - Administrando SAMBA 4 Pelo Cliente Windows Com RSATDokumen5 halaman1 - Administrando SAMBA 4 Pelo Cliente Windows Com RSATJunior SilvaBelum ada peringkat

- Configuração do SkillSpectorDokumen9 halamanConfiguração do SkillSpectorDezirèè BreganoBelum ada peringkat

- Configuração Básica Serviços PFsenseDokumen23 halamanConfiguração Básica Serviços PFsenseRodrigo Marcolino De OliveiraBelum ada peringkat

- FRAMEWORKS DE BIG DATA: UMA VISÃO GERAL DO HADOOP E SPARKDokumen18 halamanFRAMEWORKS DE BIG DATA: UMA VISÃO GERAL DO HADOOP E SPARKdeniltonBelum ada peringkat

- Pratico Final IPMDokumen2 halamanPratico Final IPMPara AnúncioBelum ada peringkat

- Fundamentos de ProgramaçãoDokumen41 halamanFundamentos de Programaçãocaua bBelum ada peringkat

- Apostila Programacao OP-08 R01 PDFDokumen12 halamanApostila Programacao OP-08 R01 PDFAndre LizBelum ada peringkat

- Aulas de Informatica-I 11-05-2022Dokumen88 halamanAulas de Informatica-I 11-05-2022Daudo DuarteBelum ada peringkat

- Manipulação de Banco de Dados Com JavaDokumen17 halamanManipulação de Banco de Dados Com JavaFiorin AndréBelum ada peringkat

- Trade FollowDokumen32 halamanTrade FollowMarcos SouzaBelum ada peringkat

- Desbloqueio Xbox360 SlimDokumen6 halamanDesbloqueio Xbox360 Slimrpimentel_23Belum ada peringkat