0.13-Um SiGe BiCMOS Radio Front-End Circuits For 24-GHz Automotive Short-Range Radar Sensors

Diunggah oleh

h7q290587Judul Asli

Hak Cipta

Format Tersedia

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniHak Cipta:

Format Tersedia

0.13-Um SiGe BiCMOS Radio Front-End Circuits For 24-GHz Automotive Short-Range Radar Sensors

Diunggah oleh

h7q290587Hak Cipta:

Format Tersedia

0.

13-m SiGe BiCMOS Radio Front-End Circuits

for 24-GHz Automotive Short-Range Radar Sensors

Angelo Scuderi

Egidio Ragonese, Giuseppe Palmisano

Automotive Product Group, RF Competence Center

STMicroelectronics

Stradale Primosole 50, 95121, Catania, Italy

Email: angelo-apg.scuderi@st.com

DIEES

Universit di Catania, Facolt di Ingegneria

Viale A. Doria 6, 95125 Catania, Italy

Email: eragone@diees.unict.it, gpalmisano@diees.unict.it

AbstractThis paper presents the key blocks of a 24-GHz

front-end for vehicular short-range radar sensors implemented

in a 0.13-m SiGe BiCMOS process. In particular, a three-stage

low-noise amplifier with transformer-based loads, a frequency

synthesizer, consisting of 24-GHz voltage-controlled oscillator in

closed loop with an N-integer PLL, and an ultra-wideband

transmitter based on a RF current steering switch are detailed.

The low-noise amplifier provides an outstanding power gain of

35 dB and a noise figure as low as 3.4 dB, guarantying an input

1-dB compression point of 12 dBm. The transmitter is able to

deliver 0-dBm output power at 24 GHz, complying with 1-ns

pulse transmission requirements.

I.

INTRODUCTION

Advanced driver assistance systems (ADAS) are becoming

the most attractive solution to reduce the vehicular accident

probability. ADAS systems face both comfort functionalities

(i.e. ACC, stop&go, night vision, etc.) and safety functions

(i.e. ESP, collision warning, collision mitigation, etc.),

preparing the car for an inevitable accident (belt tensioner,

emergency break, etc.) up to reduce the crash severity acting

on restraint system (airbags) or post-crash devices (telematics,

emergency call, etc.). In this scenario, radar sensors are

considered the eligible technology to interact with both safety

and comfort devices providing data on obstacle positions. To

achieve a complete inspection around the car, a radar system

takes advantage of two classes of sensors. Long-range radar

(LRR) sensors cover a limited angle (10) ahead of the car at

distances of few meters to about 150 m and are typically used

for autonomous cruise control (ACC) applications.

Short-range radar (SRR) sensors cover a significant part of the

azimuth angle and finally look around the car (100 to 360) at

distances up to 20 m.

2002, the FCC regulation indicates a band as large as 7 GHz

between 22 to 29 GHz allowed for SRR devices [1]. In order

to support the development of UWB SRR systems in

commercial silicon-based technology, the EU permits the

temporary use of a band between 22 to 26.625 GHz until June

2013 [2]. From 2013 new cars should be equipped with radar

sensors operating only in the frequency range 76-81 GHz.

Unfortunately, at present the high operating frequency of

such systems limits the large diffusion posing serious

problems concerning cost, yield, manufacturing and testing on

high-volume productions in commercial silicon-based

technologies. In particular, the radio front-end still represents

the bottleneck for the development of a silicon-integrated

radar system.

In this paper several crucial blocks, such as low-noise

amplifier (LNA), phase locked loop (PLL), and UWB

transmitter, for 24-GHz automotive SRR sensor application

are presented.

II.

A.

Although the growing importance of radar systems a

global standardization is not yet achieved. Regulation

institutes, such as the Federal Communication Commission

(FCC) and the European Telecommunications Standards

Institute (ETSI), recently allocate unlicensed bands for

ultra-wideband (UWB) SRR in USA and EU, respectively. In

978-1-4244-2362-0/08/$25.00 2008 IEEE.

494

CIRCUIT DESIGN

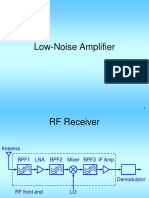

Low-Noise Amplifier

The simplified schematic of the LNA is shown in Fig. 1.

Figure 1. Simplified schematic of the 3-stage LNA.

The circuit consists of three gain stages, which exploit a

fully differential topology to avoid detrimental effects of

parasitic ground inductance and to provide high rejection of

common-mode spurious signals and substrate noise. Each

amplifier stage adopts a transformer-loaded cascode topology,

which allows first-rate reverse isolation, excellent power gain,

and high linearity to be achieved. The first stage, LNA1, was

designed to achieve simultaneous noise/input impedance

matching by using optimum transistor sizing and emitter

inductors (LE1). On the contrary, in both LNA2 and LNA3

inductive emitter degeneration (LE2, LE3) was employed to

trade-off power gain and linearity performance. Transformer

resonant loads (TL1, TL2, and TL3) were accurately designed to

optimize the overall power gain performance by maximizing

the transformer characteristic resistance (TCR) [3]. The design

of an integrated transformer is an issue of great concern at

mm-wave frequencies since the adopted inductance values fall

in the sub-nH range [4]. Moreover, the TCR optimization

procedure requires iterative steps and time consuming

electromagnetic (EM) simulations. For these reasons, scalable

lumped model was first exploited to define the spiral

geometrical parameters, and then a 2D EM simulator (Agilent

Momentum) was used to validate the transformer layout

structure and refine its EM behavior, taking into account the

connection paths. Finally, to guarantee the required gain

bandwidth flatness, which is an issue of great concern in multi

stage amplifiers with resonant load, the inter-matching LC

networks were properly designed.

A variable-gain approach is also adopted to relax linearity

requirements of the I-Q mixers and subsequent blocks in the

receiver chain. As shown in Fig. 1, a single-bit gain control is

achieved by means of the control voltage, VCTRL. In particular,

at low-gain setting (VCTRL = 2.5 V) the current delivered to the

resonant load depends on the emitter area ratio of transistors

Q8,9, Q11,12 (Q16,17, Q19,20), while at high-gain setting

(VCTRL = 0 V) the stages work as traditional cascode

amplifiers. This technique significantly increases the receiver

linearity, still maintaining excellent noise figure performance.

At the output, differential-to-single-ended conversion is

inherently provided by the transformer TL3, while at the input

an integrated balun (Tin) was included for testing purpose.

The layout drawing of mm-wave Si-based blocks is a

crucial phase in the overall design flow. Indeed, geometrical

asymmetries, interconnection path parasites, and EM coupling

produce considerable degradation of the expected results.

Moreover, a poor on-chip ground reference, due to the

stringent metal density rules of modern processes further

deteriorates both circuit reliability and performance. For these

reasons, much attention was paid to the design of differential

signal paths in terms of symmetry and length. This was also

accomplished by adopting a symmetric interleaved structure

for the transformer loads TL and differential folded microstrips

to implement degeneration inductors LE. Furthermore, a

low-resistance/low-inductance ground plane was adopted,

which makes use of an appropriate metal 2/metal 3 pattern to

meet density requirements still implementing a well-defined

on-chip ground reference for the LNA. Finally, extensive EM

post-layout simulations were carried out to take into account

RLC parasitics and coupling effects.

B. 24-GHz Synthesizer

The design of a frequency synthesizer working at

operating frequency higher than 5 GHz is an issue of great

concern. The design of both low-noise oscillator and

high-frequency prescaler represents the bottleneck to

demonstrate the feasibility of Si-based chips for

high-frequency applications. This work uses a 24-GHz PLL,

adopting a well-established architecture composed of

phase/frequency detector (PFD), charge pump, external loop

filter, voltage-controlled oscillator (VCO), and N-integer

divider. Using a division ratio N of 2048 a 24.125-GHz carrier

is achieved with a PLL reference frequency fREF of

11.78 MHz. A second order loop filter is used to set PLL

bandwidth at 200 kHz.

The VCO, whose simplified schematic is depicted Fig. 2,

uses a bipolar core with high-Q LC resonator. An issue of

great concern is the design of both capacitors and inductor in

the LC tank. This resonator exploits accumulation MOS

(A-MOS) variable capacitors and a single-turn inductor whose

value at 24 GHz is as low as 230 pH. As reported in [4], both

measurements and modeling of such sub-nH spirals are quite

critical. To overcome these problems and take into account all

connection paths, EM simulators are extensively adopted

during the resonator design.

Finally, the N-integer divider is designed using a chain of

11 divider-by-two stages. Each stage uses flip-flop in

closed-loop master-slave configuration. High-speed flip-flops

are designed using current-mode-logic D-latches. Each divider

drives the subsequent one using an emitter follower stage. The

design of high-speed D-latches requires accurate RLC

extraction and evaluation of connection paths during layout

drawing. To this aim, in addition to conventional post layout

flows, commercial EM simulator was largely exploited to

guarantee working capabilities beyond 30 GHz.

C. UWB Transmitter

The modulated pulses are generated by using a sub-ns

switch, whose simplified schematic is shown in Fig. 3. A

current steering approach is adopted. The 24-GHz signal

drives the RF port, while the pulse signal coming from the

pulse generator (PG) steers the RF signal into the output port

to generate the 24-GHz modulated pulse. The switch is

properly designed to deliver a 0-dBm output power complying

with 1-ns pulse transmission requirements, thus avoiding the

need of an additional amplifier. A resonant load composed of

MIM capacitor, CL, and stacked transformer, TLOAD, is

adopted. The design of the output transformer TLOAD is an

issue of great concern. First a simplified lumped model [5]

was exploited to define the transformer geometrical

parameters and then a commercial 3D EM simulator, Ansoft

HFSS, was used to simulate the layout structure, taking into

account all the connection paths. The monolithic transformer

provides both differential-to-single-ended conversion of the

output signal and ESD protection, as well. Thanks to the

secondary inductor of TLOAD, the current generated by

electrostatic discharge is shorted to the ground without any

ESD protection diode loading the RF stage.

495

centered at 24.125 GHz carrier is shown in Fig. 8. The carrier

presents two tones at a frequency offset of 11.78 MHz (PLL

reference frequency fREF), whose levels are 50 dBc lower. The

measured output power is about 4.65 dBm, which

corresponds to a delivered power of 0.8 dBm considering a

cable loss of 3.8 dB at 24 GHz. The maximum power is

1.5 dBm measured at 24.9 GHz.

Figure 2. Simplified schematic of the VCO and buffer.

Figure 4. Die photograph of the 3-stage LNA.

Figure 3. Simplified schematic of TX output switch.

III.

EXPERIMENTAL RESULTS

A 0.13-m SiGe:C BiCMOS technology featuring

high-speed npn transistors with fT/fmax of 166/175 GHz, dual

VT dual gate oxide CMOS devices, high-quality passives and

6-level metal copper back-end was used [6]. For testing

purpose, the chips were mounted on a 400-m thick FR4

substrate adopting chip-on-board assembly technique.

The die photograph of the LNA is shown in Fig. 4. The

LNA measurement setup consists of a two-port HP8510

vector network analyzer, a Summit 12000 Cascade Microtech

prober, and an Agilent N8975A noise figure analyzer. Testing

was carried out at 2.5-V supply voltage. Raw data were

de-embedded only for the input stacked balun loss. The power

gain and noise figure at high-gain setting are reported in

Fig. 5. The amplifier achieves a maximum gain of 35 dB and a

3.4-dB noise figure. At low-gain setting the LNA provides a

14.5-dB power gain, while exhibiting a noise figure of 4.5 dB.

Thanks to the gain-control functionality, the circuit achieves a

1-dB compression point (P1dB) of 12 dBm. Both input and

output return losses are shown in Fig. 6. The LNA exhibits a

S12 better than 53 dB in the whole operative frequency range,

thus demonstrating the effectiveness of the adopted isolation

techniques.

The die photograph of the overall UWB transmitter is

shown in Fig. 7. The PLL was characterized using

Agilent 4440A spectrum analyzer, which features an operating

bandwidth as large as 26.5 GHz. The output spectrum

496

Figure 5. Power gain (S21) and noise figure at high-gain setting

(VCTRL = 0 V, PIN = 30 dBm).

Figure 6. Input (S11) and output (S22) return losses.

The VCO exhibits a tuning range of 4.7 GHz from 20.4 to

25.1 GHz, when the fREF sweeps between 9.78 to 12.2 MHz.

The measured phase noise is 104.3 dBc/Hz at 1-MHz offset

from the carrier at 24.125 GHz, as shown in Fig. 9. The VCO

core consumes 5.8 mA from a 2.5-V power supply.

Fig. 10 shows the measured spectrum of the UWB

transceiver with a pulse repetition frequency (PRF) fixed to

10 MHz. The spectrum presents a main lobe centered at

24.125 GHz with two nulls at 23.25 and 25.08 GHz

respectively, which indicate a pulse transmission with TPulse of

1.1 ns. The spectrum presents two secondary lobes, whose

power spectral density is 10 dBc lower than the main lobe.

The carrier at 24.125 GHz is visible as a single tone due to the

continuous leakage, as well. Basically, TX leakage is limited

by the isolation of transistors Q10, Q11, Q12, Q13 in off state

(see at Fig. 3).

Figure 9. Phase-noise at 1-MHz offset from the 24.125-GHz carrier.

Figure 10. Output spectrum for 1-ns trasmitted pulse

(PRF = 10 MHz, RBW = 1 MHz).

ACKNOWLEDGMENT

Figure 7. UWB transmitter die photograph.

The authors would like to thank Alessandro Castorina,

STMicroelectronics, Catania, Italy, for his valuable assistance

with measurements.

REFERENCES

[1]

[2]

[3]

[4]

[5]

[6]

Figure 8. Frequency synthesizer output spectrum.

497

First report and order, revision of part 15 of the commissions rules

regarding ultra wideband transmission systems, FCC, Washington,

DC, ET Docket 98 153, 2002.

ETSI EN 302 288-1: Electromagnetic compatibility and Radio

spectrum Matters (ERM); Short Range Devices; Road Transport and

Traffic Telematics (RTTT); Short range radar equipment operating in

the 24 GHz range; Part 1: Technical requirements and methods of

measurement.

F. Carrara, A. Italia, E. Ragonese, and G. Palmisano, Design

methodology for the optimization of transformer-loaded RF circuits,

IEEE Trans. Circuits Syst. I, vol. 53, pp. 761 768, Apr. 2006.

T. Biondi, A. Scuderi, E. Ragonese, and G. Palmisano, Sub-nH

inductor modeling for RF IC design, IEEE Microwave Wireless Comp.

Lett, vol. 15, pp. 922-924, Dec. 2005.

T. Biondi, A. Scuderi, E. Ragonese, and G. Palmisano, Analysis and

modeling of layout scaling in silicon integrated stacked transformers,

IEEE Trans. Microwave Theory Tech., pp. 2203-2210, Apr. 2006.

M. Laurens et al., A 150 GHz fT/fmax 0.13 m SiGe:C BiCMOS

technology, in Proc. IEEE Bipolar/BiCMOS Circuits Technol.

Meeting, Oct. 2003, pp. 199-202.

Anda mungkin juga menyukai

- Shoe Dog: A Memoir by the Creator of NikeDari EverandShoe Dog: A Memoir by the Creator of NikePenilaian: 4.5 dari 5 bintang4.5/5 (537)

- The Yellow House: A Memoir (2019 National Book Award Winner)Dari EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Penilaian: 4 dari 5 bintang4/5 (98)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeDari EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifePenilaian: 4 dari 5 bintang4/5 (5794)

- The Little Book of Hygge: Danish Secrets to Happy LivingDari EverandThe Little Book of Hygge: Danish Secrets to Happy LivingPenilaian: 3.5 dari 5 bintang3.5/5 (400)

- Grit: The Power of Passion and PerseveranceDari EverandGrit: The Power of Passion and PerseverancePenilaian: 4 dari 5 bintang4/5 (588)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureDari EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FuturePenilaian: 4.5 dari 5 bintang4.5/5 (474)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryDari EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryPenilaian: 3.5 dari 5 bintang3.5/5 (231)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceDari EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RacePenilaian: 4 dari 5 bintang4/5 (895)

- Team of Rivals: The Political Genius of Abraham LincolnDari EverandTeam of Rivals: The Political Genius of Abraham LincolnPenilaian: 4.5 dari 5 bintang4.5/5 (234)

- Never Split the Difference: Negotiating As If Your Life Depended On ItDari EverandNever Split the Difference: Negotiating As If Your Life Depended On ItPenilaian: 4.5 dari 5 bintang4.5/5 (838)

- The Emperor of All Maladies: A Biography of CancerDari EverandThe Emperor of All Maladies: A Biography of CancerPenilaian: 4.5 dari 5 bintang4.5/5 (271)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaDari EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaPenilaian: 4.5 dari 5 bintang4.5/5 (266)

- On Fire: The (Burning) Case for a Green New DealDari EverandOn Fire: The (Burning) Case for a Green New DealPenilaian: 4 dari 5 bintang4/5 (74)

- The Unwinding: An Inner History of the New AmericaDari EverandThe Unwinding: An Inner History of the New AmericaPenilaian: 4 dari 5 bintang4/5 (45)

- Rise of ISIS: A Threat We Can't IgnoreDari EverandRise of ISIS: A Threat We Can't IgnorePenilaian: 3.5 dari 5 bintang3.5/5 (137)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersDari EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersPenilaian: 4.5 dari 5 bintang4.5/5 (345)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyDari EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyPenilaian: 3.5 dari 5 bintang3.5/5 (2259)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreDari EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You ArePenilaian: 4 dari 5 bintang4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Dari EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Penilaian: 4.5 dari 5 bintang4.5/5 (121)

- Her Body and Other Parties: StoriesDari EverandHer Body and Other Parties: StoriesPenilaian: 4 dari 5 bintang4/5 (821)

- MTech Final ThesisDokumen88 halamanMTech Final Thesisprajjawal.202vl017Belum ada peringkat

- Fundamentals of Microelectronics IIDokumen286 halamanFundamentals of Microelectronics IIjamaldaircalBelum ada peringkat

- Question Paper Code:: Reg. No.Dokumen5 halamanQuestion Paper Code:: Reg. No.Samraj JebasinghBelum ada peringkat

- Edc 2 Mumbai University Lab ManualDokumen32 halamanEdc 2 Mumbai University Lab ManualXavier50% (4)

- Experiment No. 4: Transistor-Level Circuit Design Using Cadence Design FlowDokumen7 halamanExperiment No. 4: Transistor-Level Circuit Design Using Cadence Design FlowkingsterBelum ada peringkat

- ENE410 Study Guide 2019Dokumen33 halamanENE410 Study Guide 2019ShivaaniBelum ada peringkat

- Low NoiseamplifierDokumen115 halamanLow NoiseamplifierVedran IbrahimovicBelum ada peringkat

- Design of Fully Differential CMOS AmplifDokumen4 halamanDesign of Fully Differential CMOS AmplifsamactrangBelum ada peringkat

- Electronics Ch8Dokumen31 halamanElectronics Ch8Benazir BegamBelum ada peringkat

- Chapter 3: Multistage Amplifiers: Innovative Entrepreneurial GlobalDokumen29 halamanChapter 3: Multistage Amplifiers: Innovative Entrepreneurial GlobalMuhammad HafizBelum ada peringkat

- A Review of High-Speed GaN Power Modules State of The Art Challenges and SolutionsDokumen23 halamanA Review of High-Speed GaN Power Modules State of The Art Challenges and SolutionsVaishnava devi BalaramanBelum ada peringkat

- Diff Pairs - Behzad Razavi Lecture NotesDokumen14 halamanDiff Pairs - Behzad Razavi Lecture Noteshsharghi75% (4)

- Multistage AmplifierDokumen18 halamanMultistage AmplifierSai SadiqBelum ada peringkat

- Flipped Voltage Follower (Profe)Dokumen4 halamanFlipped Voltage Follower (Profe)nos_joelBelum ada peringkat

- Cascode BJT CircuitDokumen6 halamanCascode BJT CircuitAsim Khan NiaziBelum ada peringkat

- Laboratory Manual Cadence Tste80 07Dokumen26 halamanLaboratory Manual Cadence Tste80 07chetan_bec2834Belum ada peringkat

- V1 - Multistage Amplifier N Current MirrorDokumen18 halamanV1 - Multistage Amplifier N Current MirrorAshiqur Rahman ASBelum ada peringkat

- Telefunken TK2028 29 GE2010 Manual ServiceDokumen66 halamanTelefunken TK2028 29 GE2010 Manual Serviceroto44Belum ada peringkat

- OTA High Pass FilterDokumen4 halamanOTA High Pass FilterJoel Adrián Amador LópezBelum ada peringkat

- Lecture17 Ee474 Folded Cascode OtaDokumen17 halamanLecture17 Ee474 Folded Cascode OtaRinkitori NorikarinBelum ada peringkat

- EC8361 - ADCLab Manual PDFDokumen105 halamanEC8361 - ADCLab Manual PDFeshwari2000100% (1)

- Electronic Devices: FloydDokumen33 halamanElectronic Devices: FloydArman KhanBelum ada peringkat

- Lecture by Navakanta BhattDokumen33 halamanLecture by Navakanta BhattVivek RoyBelum ada peringkat

- A Low-Voltage MOS Cascode Current Mirror For All Current LevelsDokumen23 halamanA Low-Voltage MOS Cascode Current Mirror For All Current LevelsSureshnaidu LekkalaBelum ada peringkat

- 3 Analog Electronics Lab PDFDokumen4 halaman3 Analog Electronics Lab PDFjeyepuvevBelum ada peringkat

- Applied Mathematics For Electronics EngineersDokumen34 halamanApplied Mathematics For Electronics Engineersirfan449Belum ada peringkat

- Practical Switched CapacitorDokumen27 halamanPractical Switched CapacitorNikhil KumarBelum ada peringkat

- EE809: Analog Integrated Circuit Design: Week-4 4 - 8 Oct 2021Dokumen24 halamanEE809: Analog Integrated Circuit Design: Week-4 4 - 8 Oct 2021Muhammad FaizanBelum ada peringkat

- Potentiostat3 PDFDokumen18 halamanPotentiostat3 PDFEisa MoosaviBelum ada peringkat

- Analysis of The Impact of High-Order Integrator Dynamics On SC Sigma-Delta Modulator Performances-Q2KDokumen13 halamanAnalysis of The Impact of High-Order Integrator Dynamics On SC Sigma-Delta Modulator Performances-Q2Kjulio perezBelum ada peringkat