Implementation of High Reliable 6T SRAM Cell Design

Hak Cipta

Format Tersedia

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniHak Cipta:

Format Tersedia

Implementation of High Reliable 6T SRAM Cell Design

Hak Cipta:

Format Tersedia

IOSR Journal of VLSI and Signal Processing (IOSR-JVSP)

Volume 5, Issue 1, Ver. II (Jan - Feb. 2015), PP 21-27

e-ISSN: 2319 4200, p-ISSN No. : 2319 4197

www.iosrjournals.org

Implementation of High Reliable 6T SRAM Cell Design

P. Pavan Kumar 1, Dr. R Ramana Reddy 2, M.Lakshmi Prasanna Rani 3

Department of Electronics and Communication Engineering, MVGR College of Engineering

Vizianagaram, Andhra Pradesh, India.

Abstract: Memory can be formed with the integration of large number of basic storing element called cells.

SRAM cell is one of the basic storing unit of volatile semiconductor memory that stores binary logic '1' or '0' bit.

Modified read and write circuits were proposed in this paper to address incorrect read and write operations in

conventional 6T SRAM cell design available in open literature. Design of a new highly reliable 6T SRAM cell

design is proposed with reliable read, write operations and negative bit line voltage (NBLV). Simulations are

carried out using MENTOR GRAPHICS.

Keywords: Memory, Read, Write, SRAM, NBLV.

I.

Introduction

A random-access memory is a class of semiconductor memory in which the stored data can be accessed

in any fashion and its access time is uniform regardless of the physical location [1,2]. RAM can be classified

based on the storage mode of the memory: volatile and non-volatile memory. Volatile memory retains its data as

long as power is supplied, while non-volatile memory will hold data indefinitely [3,4]. RAM is referred as

volatile memory, while ROM is referred as nonvolatile memory. Memory cells used in volatile memories can be

further classified into static or dynamic structures. Static RAM (SRAM) cells use feedback (or cross coupled

inverters) mechanism to maintain their state, while dynamic RAM (DRAM) cells use floating capacitor to hold

charge as a data. The charged stored in the floating capacitor is leaky, so dynamic cells must be refreshed

periodically to retain stored data[5]. The positive feedback mechanism, between two cross coupled inverters in

SRAM provides a stable data and facilitates high speed read and write operations. However, SRAMs are faster

and it requires more area per bit than DRAMs. SRAMs continue to be critical components across a wide range

of microelectronics applications from consumer wireless to high performance server processors, multimedia and

System on Chip (SOC) applications[6]. It is also projected that the percentage of embedded SRAM in SOC

products will increase further from the current 84% to as high as 94% according to the International

Technology Roadmap for Semiconductors (ITRS). This trend has mainly grown due to ever increased demand

of performance and higher memory bandwidth requirement to minimize the latency.

II.

Conventional 6T SRAM Cell Design

SRAM cell is the key component in memories. A typical SRAM cell uses two cross-coupled inverters

forming a latch and access transistors for enabling access to the cell during read and write operations and

provide cell isolation during the not-accessed state. SRAM cell is designed to provide non-destructive read

access, write capability and data storage (or data retention) as long as cell is powered. Conventional 6T SRAM

cell design is shown in figure-1, four transistors (q1q4) comprise cross-coupled cmos inverters and two nmos

transistors q5 and q6 provide read and write access to the cell.

Figure 1: Conventional 6T SRAM cell design

DOI: 10.9790/4200-05122127

www.iosrjournals.org

21 | Page

Implementation Of High Reliable 6t Sram Cell Design

From the open literature survey the main disadvantage of conventional 6T SRAM cell is not having an

individual write and read circuits.

III.

Read Operation

In this paper new read and write circuits are proposed to overcome the disadvantages in conventional

6T SRAM cells[7].A new read circuit is proposed which is shown in figure 2 in which individual read operation

will be performed and the bit lines are precharged to VDD. The read operation is initiated by enabling the word

line (WL) and connecting the precharged bit lines, BL and BLB, to the internal nodes of the cell[8]. Upon read

access, the bit line voltage VBL remains at the precharge level. The complementary bit line voltage VBLB is

discharged through transistors Q1 and Q5 connected in series. Effectively, transistors Q1 and Q5 form a voltage

divider whose output is now no longer at zero volt and is connected to the input of inverter Q2Q4. Sizing of

Q1 and Q5 should ensure that inverter Q2Q4 do not switch causing a destructive read.

Before reading a value from the storage nodes, both bit lines (BL) are pre-charged to VDD. The word

line is then asserted to VDD. The storage node that stores a 1 will stay at 1 since it is connected to a pre-charged

bit line [9]. The storage node that stores a 0 is statically connected to ground and will drain the charges on the

bit line, which means that the bit line has just read a 0. Note that at the instant when the word line is turned on,

the storage node that stores a 0 will jump to an intermediate voltage because there is now a current path from the

bit line to Ground[10].

Figure 2: Proposed Read circuit for conventional 6T SRAM cell design

The intermediate voltage is determined by voltage dividers constructed by one of the access transistors

and the NMOS transistors (M1 or M3) of the cross-coupled inverters. Since the storage nodes are coupled,

intermediate voltage should not jump too high, otherwise it will invert the data stored at the other storage node.

Therefore, the NMOS transistors of the cross-coupled inverters are made larger than the access transistors to

ensure that the intermediate voltage does not flip the content of the other storage node[11].

Write operation:

Standard write operation of a 6T SRAM cell is performed using a NOR logic, by lowering one of the

BITLINE to ground. To write a 0 BL is lowered, while writing a 1 also requires BL is to be lowered. When

writing a 1 the cell has a0stored. The last operational state of the SRAM is the writing operation, during

which the system has to have the ability to successfully write new data to the bit-cells[12]. The new data might

be the same as or opposite of the stored ones, nevertheless, opposite data is always assumed as it involves more

actions (e.g. flipping the cells) and hence it represents the worst case writing. Based on that successful writing

involves discharging the node holding high voltage, through its corresponding bit-line, below the opposite

inverter trip point within the time when access transistors are enabled. Write driver is the component in charge

of driving the bit-line to discharge that node, where the final voltage of the high voltage node is determined by

the voltage divider between the corresponding pull-up transistor and access transistor. Moreover, since the

access transistors are enabled for a limited time only, the final voltage is also affected by the discharging

current, that is the difference in ON current between the pull-up and access transistor. Proposed write circuit for

correct write operation is shown in figure 3 .Modified conventional 6T SRAM with both proposed write and

read circuits is presented in figure 4. Read and write operation of the 6T SRAM with the proposed circuit are

presented in figure 5&6 respectively. In this write operation is based on BITLINE and BITLINE BAR. The

DOI: 10.9790/4200-05122127

www.iosrjournals.org

22 | Page

Implementation Of High Reliable 6t Sram Cell Design

WORDLINE will raise either from 0 to 1 or 1 to 0 for high reliable write operation. Conventional 6T SRAM

cell has been widely used in the implementation of high performance microprocessors and on-chip caches.

However, aggressive scaling of CMOS technology presents a number of distinct challenges for embedded

memory fabrics.

Figure 3: Write circuit of a 6T SRAM cell.

Figure 4: 6T SRAM cell with proposed Read and Write circuits

Figure 5: Waveform of Read operation of 6T SRAM cell

DOI: 10.9790/4200-05122127

www.iosrjournals.org

23 | Page

Implementation Of High Reliable 6t Sram Cell Design

Figure 6: Waveform of Write operation of 6T SRAM cell

The stability of the circuit depends on the inputs and number of transistors used. To reduce number of

inputs and to increase the stability a new modified 6T SRAM is presented in figure 7.

Figure 7: 6T SRAM using a inverter as a power source.

A pulse voltage and DC voltage is given to inputs and its error report is verified for the results of dc

analysis and transient analysis at different voltages from 0.5v to 2.5v with WL variation from 20ns to 60ns.

From the results it can be observed that perfect write operation is derived.

Write operation will be observed with the terms of BL, BLBAR and WL when applying the inputs BL

and BLBAR will be in opposite condition and WL should raise either from 0 to 1 or from 1 to 0. In the above

circuit the voltage constraint is reduced using inverter condition but it consume more area than the conventional

6T SRAM cell. So, a new design is proposed which uses transmission gates in place of pass transistors.

IV.

Proposed 6T SRAM Cell Design

The proposed SRAM cell is shown in Figure 8, it consists of two transmission gates in place of pass

(access) transistors. The transmission gates have low voltage drop compared to pass transistors. The additional

NMOS in the circuit acts as a switch and also it is necessary to restrict a short circuit current when the data is

written in the elementary cell. Read and Write circuits presented in figure 3&4 can be used with proposed 6T

SRAM cell design.

Figure 8: Proposed 6T SRAM with transmission gates

DOI: 10.9790/4200-05122127

www.iosrjournals.org

24 | Page

Implementation Of High Reliable 6t Sram Cell Design

If more negative voltage peak is generated by negative bit line voltage, less will be reliability of the circuit. To

overcome this problem, a capacitor is connected (whose other end is connected to ground) to the output of the

NBLV generator which increases the absolute capacitance of the NBLV. This capacitor works as a low pass

filter which smoothes out the negative voltage spike. When level of negative voltage spike decreases, VGS of

MOSFET reduces which reduces the strength of electric field. Due to low strength of electric field, there will be

very low chances of dielectric breakdown and hence less chances of transistors to get damaged, hence reliability

of the circuit is increased.

Figure 9: 6T SRAM with NBLV circuit

In the above NBLV circuit the 6T SRAM cell is used for write assist scheme and verified the write operation to

increase the reliability of the circuit.

Level of negative voltage generated by NBLV generator is reduced. But due to this reduced level of negative bit

line voltage, the assisting effect of NBLV write assist scheme reduces which may cause the memory to fail. So,

this reduced influence of assist circuit needs to be compensated to achieve high write ability and hence high

efficiency of the SRAM. By implementing the NBLV schemes with 6T SRAM cell together high reliability as

well as write ability can be achieved.

Results

Simulations are carried out using MENTOR GRAPHICS tools using 130nm technology. . Observed the results

using both DC and transient response . DC output response, write failure and correct write operations

waveforms are shown in figure 10, 11& 12 respectively, write operation of 6T SRAM using NBLV is presented

in figure 13.

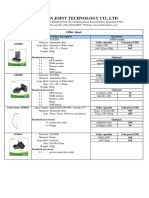

Comparison of delay & power dissipation for the conventional and proposed 6T SRAM is presented in table 1

Table 1: Comparison between conventional and proposed 6T SRAM

Parameters

Delay

Power dissipation

DOI: 10.9790/4200-05122127

Conventional

Proposed

6TSRAM

6TSRAM

32.7ps

24.3ps

541.62w

483w

www.iosrjournals.org

25 | Page

Implementation Of High Reliable 6t Sram Cell Design

Figure 10: DC output of a proposed 6T SRAM cell.

Figure 11: Transient ouput write failure case

Figure 12: Transient output correct write operation.

DOI: 10.9790/4200-05122127

www.iosrjournals.org

26 | Page

Implementation Of High Reliable 6t Sram Cell Design

Figure 13:Write operation waveform of NBLV.

V.

Conclusion

Implemented to obtain correct read and write operations compared to conventional 6T SRAM. To improve the

stability SRAM using an inverter, to reduce power consumption and 6T SRAM using transmission gates are

proposed and to improve reliability SRAM with NBLV circuit is also implemented. From the results it is

evident that the proposed 6T SRAM is more stable, reliable, dissipates less power and delay is also reduced. The

proposed circuit is very useful in system in chip applications.

References

[1].

[2].

[3].

[4].

[5].

[6].

[7].

[8].

[9].

[10].

[11].

[12].

The Impact of Total Ionizing Dose on Unhardened SRAM Cell Margins IEEE TRANSACTIONS ON NUCLEAR SCIENCE, VOL.

55, NO. 6, DECEMBER 2008

Masood Qazi, Mahmut E. Sinangil, and Anantha P. Chandrakasan, Challenges and Directions for Low-Voltage SRAM,

Copublished by the IEEE CS and the IEEE CASS 0740-7475/11/$26.00 2011.

Kaushik Roy, Sharat C. Prasad, Low-Power CMOS VLSI Design, a John Wiley & Sons, 02-Feb-2009.

Jan M. Rabaey, Anantha P. Chandrakasan, Borivoje Nikolic, Digital integrated circuits: a design perspective, Pearson Education,

2003.

Sung-Mo Kang, Yusuf Leblebici, CMOS Digital Integrated Circuits: Analysis and Design, Tata McGraw-Hill Education.

Neil H. E. Weste, David Money Harris, CMOS VLSI Design: A Circuits and Systems Perspective, Addison Wesley, 2011..

Takeuchi, K., Fukai, T., Tsunomura, T., Putra, A., Nishida, A.,Kamohara, S. & Hiramoto, T., Understanding random threshold

voltage fluctuation by comparing multiple fabs and technologies, Electron Devices Meeting, IEDM 2007. IEEE International ,

467 470, 2007.

Tohru Miwa, Junichi Yamada, Hiroki Koike, A 512 Kbit low-voltage NV-SRAM with the size of a conventional SRAM, 2001

Symposium on VLSl Circuits Digest of Technical Papers.

Verma, N. & Chandrakasan, A.P., A 256kb 65nm 8T Subthreshold SRAM Employing Sense- Amplifier Redundancy. IEEE

Journal of Solid-State Circuits, 43, 141149, 2008.

Nayak, A., Haldar, M., Banerjee, P., Chen, C., and Sarrafzadeh, M.: 'Power optimization of delay constrained circuits', ASIC/ SOC

Conference, 2000, pp. 13-16

Keerthi, R., and Chen, C.: 'Stability and Static Noise Margin Analysis of Low-Power SRAM', Instrumentation and Measurement

Technology Conference Proceedings, 2008, pp. 1681-1684

Aly, R., Faisal, M., and Bayoumi, A.: Novel 7T SRAM cell for low power cache design. Proc. IEEE SOC Conf, 2005, pp. 171 174.

DOI: 10.9790/4200-05122127

www.iosrjournals.org

27 | Page

Anda mungkin juga menyukai

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Dari EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Penilaian: 4.5 dari 5 bintang4.5/5 (119)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaDari EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaPenilaian: 4.5 dari 5 bintang4.5/5 (265)

- The Little Book of Hygge: Danish Secrets to Happy LivingDari EverandThe Little Book of Hygge: Danish Secrets to Happy LivingPenilaian: 3.5 dari 5 bintang3.5/5 (399)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryDari EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryPenilaian: 3.5 dari 5 bintang3.5/5 (231)

- Grit: The Power of Passion and PerseveranceDari EverandGrit: The Power of Passion and PerseverancePenilaian: 4 dari 5 bintang4/5 (587)

- Never Split the Difference: Negotiating As If Your Life Depended On ItDari EverandNever Split the Difference: Negotiating As If Your Life Depended On ItPenilaian: 4.5 dari 5 bintang4.5/5 (838)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeDari EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifePenilaian: 4 dari 5 bintang4/5 (5794)

- Rise of ISIS: A Threat We Can't IgnoreDari EverandRise of ISIS: A Threat We Can't IgnorePenilaian: 3.5 dari 5 bintang3.5/5 (137)

- Team of Rivals: The Political Genius of Abraham LincolnDari EverandTeam of Rivals: The Political Genius of Abraham LincolnPenilaian: 4.5 dari 5 bintang4.5/5 (234)

- Shoe Dog: A Memoir by the Creator of NikeDari EverandShoe Dog: A Memoir by the Creator of NikePenilaian: 4.5 dari 5 bintang4.5/5 (537)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyDari EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyPenilaian: 3.5 dari 5 bintang3.5/5 (2219)

- The Emperor of All Maladies: A Biography of CancerDari EverandThe Emperor of All Maladies: A Biography of CancerPenilaian: 4.5 dari 5 bintang4.5/5 (271)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreDari EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You ArePenilaian: 4 dari 5 bintang4/5 (1090)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersDari EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersPenilaian: 4.5 dari 5 bintang4.5/5 (344)

- Her Body and Other Parties: StoriesDari EverandHer Body and Other Parties: StoriesPenilaian: 4 dari 5 bintang4/5 (821)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceDari EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RacePenilaian: 4 dari 5 bintang4/5 (894)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureDari EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FuturePenilaian: 4.5 dari 5 bintang4.5/5 (474)

- The Unwinding: An Inner History of the New AmericaDari EverandThe Unwinding: An Inner History of the New AmericaPenilaian: 4 dari 5 bintang4/5 (45)

- The Yellow House: A Memoir (2019 National Book Award Winner)Dari EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Penilaian: 4 dari 5 bintang4/5 (98)

- On Fire: The (Burning) Case for a Green New DealDari EverandOn Fire: The (Burning) Case for a Green New DealPenilaian: 4 dari 5 bintang4/5 (73)

- The Champion Legal Ads: 11-02-23Dokumen58 halamanThe Champion Legal Ads: 11-02-23Donna S. SeayBelum ada peringkat

- LTE Interview QuestionsDokumen10 halamanLTE Interview QuestionsMahesh Pratap100% (1)

- SECURE ROAD BLOCKERS PREVENT VEHICLE ATTACKSDokumen2 halamanSECURE ROAD BLOCKERS PREVENT VEHICLE ATTACKSMuhammad Tahir QamarBelum ada peringkat

- Ethics in ResearchDokumen21 halamanEthics in Researchmukku_raviBelum ada peringkat

- Youth Entrepreneurship: Opportunities and Challenges in IndiaDokumen5 halamanYouth Entrepreneurship: Opportunities and Challenges in IndiaInternational Organization of Scientific Research (IOSR)100% (1)

- OSC - 2015 - Revised - Oct (Power Cables) PDFDokumen118 halamanOSC - 2015 - Revised - Oct (Power Cables) PDFIván P. MorenoBelum ada peringkat

- Effects of Formative Assessment On Mathematics Test Anxiety and Performance of Senior Secondary School Students in Jos, NigeriaDokumen10 halamanEffects of Formative Assessment On Mathematics Test Anxiety and Performance of Senior Secondary School Students in Jos, NigeriaInternational Organization of Scientific Research (IOSR)100% (1)

- Factors Affecting Success of Construction ProjectDokumen10 halamanFactors Affecting Success of Construction ProjectInternational Organization of Scientific Research (IOSR)Belum ada peringkat

- Clinical TeachingDokumen29 halamanClinical TeachingJeonoh Florida100% (2)

- Study The Changes in Al-Ahwaz Marshal Using Principal Component Analysis and Classification TechniqueDokumen9 halamanStudy The Changes in Al-Ahwaz Marshal Using Principal Component Analysis and Classification TechniqueInternational Organization of Scientific Research (IOSR)Belum ada peringkat

- Enhancing Pupils' Knowledge of Mathematical Concepts Through Game and PoemDokumen7 halamanEnhancing Pupils' Knowledge of Mathematical Concepts Through Game and PoemInternational Organization of Scientific Research (IOSR)Belum ada peringkat

- Development of Dacum As Identification Technique On Job Competence Based-Curriculum in High Vocational EducationDokumen5 halamanDevelopment of Dacum As Identification Technique On Job Competence Based-Curriculum in High Vocational EducationInternational Organization of Scientific Research (IOSR)Belum ada peringkat

- Necessary Evils of Private Tuition: A Case StudyDokumen6 halamanNecessary Evils of Private Tuition: A Case StudyInternational Organization of Scientific Research (IOSR)Belum ada peringkat

- Geohydrological Study of Weathered Basement Aquifers in Oban Massif and Environs Southeastern Nigeria: Using Remote Sensing and Geographic Information System TechniquesDokumen14 halamanGeohydrological Study of Weathered Basement Aquifers in Oban Massif and Environs Southeastern Nigeria: Using Remote Sensing and Geographic Information System TechniquesInternational Organization of Scientific Research (IOSR)Belum ada peringkat

- Project Based Learning Tools Development On Salt Hydrolysis Materials Through Scientific ApproachDokumen5 halamanProject Based Learning Tools Development On Salt Hydrolysis Materials Through Scientific ApproachInternational Organization of Scientific Research (IOSR)Belum ada peringkat

- The Effect of Instructional Methods and Locus of Control On Students' Speaking Ability (An Experimental Study in State Senior High School 01, Cibinong Bogor, West Java)Dokumen11 halamanThe Effect of Instructional Methods and Locus of Control On Students' Speaking Ability (An Experimental Study in State Senior High School 01, Cibinong Bogor, West Java)International Organization of Scientific Research (IOSR)Belum ada peringkat

- Philosophical Analysis of The Theories of Punishment in The Context of Nigerian Educational SystemDokumen6 halamanPhilosophical Analysis of The Theories of Punishment in The Context of Nigerian Educational SystemInternational Organization of Scientific Research (IOSR)Belum ada peringkat

- Students' Perceptions of Grammar Teaching and Learning in English Language Classrooms in LibyaDokumen6 halamanStudents' Perceptions of Grammar Teaching and Learning in English Language Classrooms in LibyaInternational Organization of Scientific Research (IOSR)Belum ada peringkat

- Child Mortality Among Teenage Mothers in OJU MetropolisDokumen6 halamanChild Mortality Among Teenage Mothers in OJU MetropolisInternational Organization of Scientific Research (IOSR)Belum ada peringkat

- Comparison of Selected Anthropometric and Physical Fitness Variables Between Offencive and Defencive Players of Kho-KhoDokumen2 halamanComparison of Selected Anthropometric and Physical Fitness Variables Between Offencive and Defencive Players of Kho-KhoInternational Organization of Scientific Research (IOSR)Belum ada peringkat

- Need of Non - Technical Content in Engineering EducationDokumen3 halamanNeed of Non - Technical Content in Engineering EducationInternational Organization of Scientific Research (IOSR)Belum ada peringkat

- Microencapsulation For Textile FinishingDokumen4 halamanMicroencapsulation For Textile FinishingInternational Organization of Scientific Research (IOSR)Belum ada peringkat

- Comparison of Explosive Strength Between Football and Volley Ball Players of Jamboni BlockDokumen2 halamanComparison of Explosive Strength Between Football and Volley Ball Players of Jamboni BlockInternational Organization of Scientific Research (IOSR)Belum ada peringkat

- Study of Effect of Rotor Speed, Combing-Roll Speed and Type of Recycled Waste On Rotor Yarn Quality Using Response Surface MethodologyDokumen9 halamanStudy of Effect of Rotor Speed, Combing-Roll Speed and Type of Recycled Waste On Rotor Yarn Quality Using Response Surface MethodologyInternational Organization of Scientific Research (IOSR)Belum ada peringkat

- Comparison of Psychological Variables Within Different Positions of Players of The State Junior Boys Ball Badminton Players of ManipurDokumen4 halamanComparison of Psychological Variables Within Different Positions of Players of The State Junior Boys Ball Badminton Players of ManipurInternational Organization of Scientific Research (IOSR)Belum ada peringkat

- Advancing Statistical Education Using Technology and Mobile DevicesDokumen9 halamanAdvancing Statistical Education Using Technology and Mobile DevicesInternational Organization of Scientific Research (IOSR)Belum ada peringkat

- Application of Xylanase Produced by Bacillus Megaterium in Saccharification, Juice Clarification and Oil Extraction From Jatropha Seed KernelDokumen8 halamanApplication of Xylanase Produced by Bacillus Megaterium in Saccharification, Juice Clarification and Oil Extraction From Jatropha Seed KernelInternational Organization of Scientific Research (IOSR)Belum ada peringkat

- Core Components of The Metabolic Syndrome in Nonalcohlic Fatty Liver DiseaseDokumen5 halamanCore Components of The Metabolic Syndrome in Nonalcohlic Fatty Liver DiseaseInternational Organization of Scientific Research (IOSR)Belum ada peringkat

- Lipoproteins and Lipid Peroxidation in Thyroid DisordersDokumen6 halamanLipoproteins and Lipid Peroxidation in Thyroid DisordersInternational Organization of Scientific Research (IOSR)Belum ada peringkat

- A Review On Refrigerants, and Effects On Global Warming For Making Green EnvironmentDokumen4 halamanA Review On Refrigerants, and Effects On Global Warming For Making Green EnvironmentInternational Organization of Scientific Research (IOSR)Belum ada peringkat

- Comparative Effect of Daily Administration of Allium Sativum and Allium Cepa Extracts On Alloxan Induced Diabetic RatsDokumen6 halamanComparative Effect of Daily Administration of Allium Sativum and Allium Cepa Extracts On Alloxan Induced Diabetic RatsInternational Organization of Scientific Research (IOSR)Belum ada peringkat

- Parametric Optimization of Single Cylinder Diesel Engine For Specific Fuel Consumption Using Palm Seed Oil As A BlendDokumen6 halamanParametric Optimization of Single Cylinder Diesel Engine For Specific Fuel Consumption Using Palm Seed Oil As A BlendInternational Organization of Scientific Research (IOSR)Belum ada peringkat

- Auxin Induced Germination and Plantlet Regeneration Via Rhizome Section Culture in Spiranthes Sinensis (Pers.) Ames: A Vulnerable Medicinal Orchid of Kashmir HimalayaDokumen4 halamanAuxin Induced Germination and Plantlet Regeneration Via Rhizome Section Culture in Spiranthes Sinensis (Pers.) Ames: A Vulnerable Medicinal Orchid of Kashmir HimalayaInternational Organization of Scientific Research (IOSR)Belum ada peringkat

- Investigation of Wear Loss in Aluminium Silicon Carbide Mica Hybrid Metal Matrix CompositeDokumen5 halamanInvestigation of Wear Loss in Aluminium Silicon Carbide Mica Hybrid Metal Matrix CompositeInternational Organization of Scientific Research (IOSR)Belum ada peringkat

- Research Analysis On Sustainability Opportunities and Challenges of Bio-Fuels Industry in IndiaDokumen7 halamanResearch Analysis On Sustainability Opportunities and Challenges of Bio-Fuels Industry in IndiaInternational Organization of Scientific Research (IOSR)Belum ada peringkat

- INJSO Answer Key & SolutionDokumen5 halamanINJSO Answer Key & SolutionYatish Goyal100% (1)

- IIT BOMBAY RESUME by SathyamoorthyDokumen1 halamanIIT BOMBAY RESUME by SathyamoorthySathyamoorthy VenkateshBelum ada peringkat

- An Introduction To Pascal Programming MOD 2010Dokumen5 halamanAn Introduction To Pascal Programming MOD 2010Johnas DalusongBelum ada peringkat

- HGDokumen64 halamanHGCharis PapadopoulosBelum ada peringkat

- Ayurveda Signs of LifeDokumen15 halamanAyurveda Signs of LifeSanjeethBelum ada peringkat

- Kerala University 2013 Admission ProspectusDokumen50 halamanKerala University 2013 Admission ProspectusMuneer SainulabdeenBelum ada peringkat

- NCP 1014Dokumen24 halamanNCP 1014rodricaldasBelum ada peringkat

- Check For Palindrome: Compute GCD and LCMDokumen3 halamanCheck For Palindrome: Compute GCD and LCMAadhi JBelum ada peringkat

- Presentation SkillsDokumen22 halamanPresentation SkillsUmang WarudkarBelum ada peringkat

- DVOR Principle 코이카 양식Dokumen71 halamanDVOR Principle 코이카 양식Undral Batbayar100% (1)

- Computers and Operations Research: Yulin Sun, Simon Cong Guo, Xueping LiDokumen12 halamanComputers and Operations Research: Yulin Sun, Simon Cong Guo, Xueping LiQuỳnh NguyễnBelum ada peringkat

- Acer Veriton S480G Service ManualDokumen90 halamanAcer Veriton S480G Service ManualAndreea Georgiana ChirilaBelum ada peringkat

- 182 - GE8076, GE6075 Professional Ethics in Engineering - 2 MarksDokumen17 halaman182 - GE8076, GE6075 Professional Ethics in Engineering - 2 Markssharon sylvia .sBelum ada peringkat

- Mental AspectDokumen29 halamanMental AspectBenjii CarlosBelum ada peringkat

- JZMH aXKBJ3TwcVIkazQwapfCMfeHvtqxB xBJ1YDokumen84 halamanJZMH aXKBJ3TwcVIkazQwapfCMfeHvtqxB xBJ1YReinbrandt malikiyano cahyonoBelum ada peringkat

- CS 704 Socio-Emotional and Moral Development in Middle ChildhoodDokumen25 halamanCS 704 Socio-Emotional and Moral Development in Middle ChildhoodPatricia PamintuanBelum ada peringkat

- 2. Green finance and sustainable development in EuropeDokumen15 halaman2. Green finance and sustainable development in Europengocanhhlee.11Belum ada peringkat

- Advance Distributed ComputingDokumen2 halamanAdvance Distributed ComputingValia Centre of ExcellenceBelum ada peringkat

- Overview On Image Captioning TechniquesDokumen6 halamanOverview On Image Captioning TechniquesWARSE JournalsBelum ada peringkat

- Motorship Oct 2023Dokumen56 halamanMotorship Oct 2023Sahil PakhaliBelum ada peringkat

- Dayal Bagh: Spircon 2013: Book of AbstractsDokumen202 halamanDayal Bagh: Spircon 2013: Book of AbstractsSant Mat100% (2)

- Topic 3Dokumen28 halamanTopic 3Ashraf YusofBelum ada peringkat

- Vehicle Tracker Offer SheetDokumen1 halamanVehicle Tracker Offer SheetBihun PandaBelum ada peringkat

- Sensor Guide: Standard Triaxial Geophones Specialty Triaxial Geophones Standard Overpressure MicrophonesDokumen1 halamanSensor Guide: Standard Triaxial Geophones Specialty Triaxial Geophones Standard Overpressure MicrophonesDennis Elias TaipeBelum ada peringkat