Paper Single Slope ADC

Diunggah oleh

ArdittoTrianggada100%(1)100% menganggap dokumen ini bermanfaat (1 suara)

332 tayangan4 halamanCoursewprk in full-custom IC design

Hak Cipta

© © All Rights Reserved

Format Tersedia

PDF, TXT atau baca online dari Scribd

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniCoursewprk in full-custom IC design

Hak Cipta:

© All Rights Reserved

Format Tersedia

Unduh sebagai PDF, TXT atau baca online dari Scribd

100%(1)100% menganggap dokumen ini bermanfaat (1 suara)

332 tayangan4 halamanPaper Single Slope ADC

Diunggah oleh

ArdittoTrianggadaCoursewprk in full-custom IC design

Hak Cipta:

© All Rights Reserved

Format Tersedia

Unduh sebagai PDF, TXT atau baca online dari Scribd

Anda di halaman 1dari 4

Department of Electrical and Electronic Engineering, Imperial College London

Single Slope ADC with Serial Output

Erasnita, Arditto Trianggada (00890769)

Department of Electrical and Electronic Engineering, Imperial College London

arditto.erasnita13@imperial.ac.uk

Abstract- Rapid development of digital electronic

technology demand a robust ADC design which links the

sensed signal by transducers in the form of analog into

digital signal so that complex computation can be

productively processed. Digital signal also has an advantage

of less susceptible to the noise compared with analog signal.

However, ADC design process often has trade-offs (e.g.,

speed, resolution, accuracy and cost) which have to be

considered depend on the purpose of design.

when ramp signal reach the same level as input signal,

comparator output will be active and trigger the digital stage

to generate digital conversion result. Digital operation stage

consists of three circuits such as control logic, binary

counter and PISO (Parallel Input Serial Output). Binary

counter counts number for every clock cycle to measure the

time needed until comparator switched on. Output of

counter then processed in PISO to output digital number in

sequentially serial with MSB comes first. Those operation

within digital stage is controlled by control logic circuit.

At the beginning, START input signal initiates ADC to

start conversion process. It reset integrator and counter to

their initial condition. On the next rising edge after START

switches low, integrator and counter will start operating

(integrator start generating positive slope ramp and counter

start counting to zero. Fig 2 shows how single slope ADC

operates with waveform simulation. The comparator output,

which will be active whenever VRAMP reach the voltage

level of VIN, control SO output to produce conversion result

by process within control logic function.

In this paper, the writer describes design methodology of

one of commonly used type of ADC that is Single Slope

ADC. It has advantages in terms of its accuracy and highresolution. However, it usually performs in slower speed if

compared with other types like flash ADC, pipeline ADC,

etc.

Keyword: single slope, resolution, hysteresis

I.

INTRODUCTION

In the basic, single slope ADC performs its conversion

process by comparing the input signal with a reference

voltage signal until the comparison process indicates that

those two voltages are equal. The process itself is

implemented in a circuit called comparator. On the other

hand, single slope contains a digital binary counter that

counts in every clock cycle. The comparator hence decide the

time when the counter's output can be considered as ADC's

conversion result (i.e., digital representation of input signal).

Fig. 1: Block Diagram of Single Slope ADC

Main characteristic of single slope ADC described in this

paper is that digital output is produced in serial sequence.

Therefore, the system has to posses a reliable digital circuit

which can handle an operation to generate a serial conversion

output without disturbing analog operation within the system.

It is also commonly known that digital usually consume more

power and amount of transistors, therefore, design efficiency

is important.

II.

Fig. 2: Timing Diagram of Single Slope ADC

III.

SYSTEM OVERVIEW

CIRCUIT IMPLEMENTATION

The first analog function in single slope ADC is an

integrator. In this paper, the writer represents integrator

opamp with switched-capacitor topology to implement the

resistor. It generates a ramp signal whose slope is adjusted

by voltage reference, gain of the opamp and capacitors in

the circuit. Opamp design should consider some

Single slope ADC in this paper comprises three stages

such as integration stage, comparator stage and digital

operation stage. Integration stage function to generate a

ramp signal as a reference voltage. In the comparator stage,

ramp signal is then compared to the input signal to

determine digital representation of input signal. By the time

1

Department of Electrical and Electronic Engineering, Imperial College London

characterization such as gain (adjust the slope of ramp),

bandwidth (speed of integrator) and phase margin

(reliability of integrator to get stable quickly). Opamp which

being used in single slope ADC is a two-stage topology

opamp[2] (shown in Fig. 3) with voltage bias source is

implemented by using CMOS voltage divider topology (Fig.

4). This opamp has a specification of 87 dB gain, 2 kHz

bandwidth and 53 phase margin (Fig. 5). The opamp then

used in integrator to implement integrator circuit with

switched-capacitor topology. Its schematic and waveform

simulation is shown in Fig. 6 and Fig. 7.

Fig. 6: Integrator Circuit Schematic

Fig. 3: Opamp Circuit Shematic

Fig. 7: Waveform Simulation Result of Integrator

hysteresis circuit to shift the operating point hence the speed

is improved. Complete comparator schematic is shown in

Fig. 8 with the same voltage bias implementation as opamp

previously. Simulation which presents the comparator's

performance of speed and input range is shown in Fig. 9 and

Fig. 10.

Fig. 4: Voltage Bias Generator

Fig. 8: Comparator Circuit Schematic

Fig. 5: Opamp Specification

Comparator design in single slope ADC has its most

important consideration in its input range operation and

speed. Comparator has to be able to operate in the desired

input voltage range (i.e., between 0.4 - 1.4 V in this single

slope ADC) and also has an acceptable speed to make sure

that SO can produce a correct conversion result. A threestage comparator topology[1] is implemented which can

handle comparison operation in the input range and also

featured by

Fig. 9: Gain Characteristic of Comparator

Digital part of single slope ADC (shown in Fig. 11) play a

role to operate computations to obtain digital representation

Department of Electrical and Electronic Engineering, Imperial College London

is used to remove an unexpected trouble when START

active, i.e., ADC is reset, and the input signal VIN is in its

minimum level or very close to 400 mV. If mux is removed

from the circuit and VRAMP is directly connected to V+ of

comparator, the comparator output VCOMP will exhibit an

invalid logic value because of unbalance hysteresis stage of

the comparator.

Fig. 10: Waveform Simulation Result of Comparator

of input signal. Control logic function (Fig. 12) control the

READY signal which will activate PISO to output serial

sequence of digital conversion result into SO. Binary

counter in here is using series of TFF and synchronized

START as a reset signal (Fig. 13). Output of the counter,

which represents a result of conversion when comparator

output goes high, then processed within PISO (Fig. 14) to

output conversion in serial.

Fig. 15: Schematic of Single Slope ADC

IV.

SIMULATED RESULT

The single slope ADC design is tested to verify its

performance in term of accuracy, sample rate, power

consumption and silicon area. First, testbench ciruit as in

Fig. 16 is built to verify its result of data conversion. As a

sample, VIN 1.1V is used with 100 MHz clock frequency.

START signal is set active for one clock cycle duration in

every one over 30 kHz (i.e., 33 s). Waveform simulation

result is presented in Fig. 17. After that, another input

voltage values is used to test relative error of the ADC

(simulation result table in Fig. 18).

Fig. 11: Schematic of Digital Block

Fig. 16: Single Slope ADC Testbench Circuit

Fig. 12: Schematic of Control Logic Function

Fig. 13: Schematic of Digital Counter

Fig. 14: Schematic of Parallel Input Serial Output (PISO)

The complete schematic of single slope ADC circuit is

shown in Fig. 15. Mux in between integrator and comparator

Fig. 17: Waveform Simulation of Single Slope ADC

3

Department of Electrical and Electronic Engineering, Imperial College London

REFERENCE

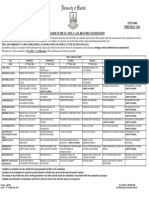

Fig. 18: Error Check Result of Single Slope ADC

Final step of the design is to design the layout. The result

of layout design is shown in Fig. 19 which successfully

passed DRC and LVC check in Cadence Virtuoso software.

Overall technical specification of the single slope ADC

discussed in this paper is shown in Fig. 20

RJ Baker, CMOS: Circuit Design, Layout, and Simulation, WileyIEEE Press (3rd Edition), 2011

[2]

PE Allen and DR Holberg, CMOS Analog Circuit Design, Oxford

University Press (2nd Edition), 2002

[3]

A Hastings, The Art of Analog Layout, Prentice Hall (2nd Edition),

2006

[4]

A Sedra and K Smith, Microelectronic Circuits, Oxford University

Press (6th Edition), 2011

[5]

PR Gray and RG Meyer, MOS Operational Amplifier Design A

Tutorial Overview, IEEE Journal of Solid-State Circuits SC-17, No

6, 1982

[6]

S Brown and Z Vranesic, Fundamentals of Digital Logic with VHDL

Design, McGraw-Hill 2nd ed, 2005

S Franco, Design with Operational Amplifiers and Analog Integrated

Circuits, McGraw-Hill 3rd ed,

[7]

Fig. 19: Layout of Single Slope ADC

Fig. 20: Achieved Technical Specification of Single Slope

ADC

V.

[1]

CONCLUSION

The single slope ADC in this paper can operate to convert

analog signal into digital accurately in most all of input

ranges even though there are one bit error cases in some

points. This occurs because integrator circuit within the

system is impelemented by using switched-capacitor

topology which relatively non-linear in small scale of

voltage. It can be minimized by replacing switchedcapacitor based resistor with polysilicon resistor. However,

it will consume larger silicon area.

If we consider area and powerconsumption of the circuit,

digital is usually weaker than analog. Better performance of

ADC can be achieved when digital circuit within our system

is minimized as simple as possible. Therefore, digital

operation in the single slope ADC can also be modified to

minimize usage of flip-flops circuits. It can be done by

combining digital counter and PISO, hence, both those two

blocks share their flip-flops together then the amount of flipflops used is reduced by half.

Anda mungkin juga menyukai

- Blood Sorcery PathsDokumen18 halamanBlood Sorcery PathsRaoni Julian100% (4)

- Analog To Digital ConverterDokumen7 halamanAnalog To Digital ConverterRavi Patel100% (1)

- Design of An ADC Using High Precision Comparator With Time Domain Offset CancellationDokumen4 halamanDesign of An ADC Using High Precision Comparator With Time Domain Offset CancellationijtetjournalBelum ada peringkat

- Digital Signal Processing: Instant AccessDari EverandDigital Signal Processing: Instant AccessPenilaian: 3.5 dari 5 bintang3.5/5 (2)

- Analog To Digital ConverterDokumen11 halamanAnalog To Digital ConverterFf Fr100% (1)

- 8 A-D ConverterDokumen30 halaman8 A-D Converterneoloader145Belum ada peringkat

- Introduction To Digital Signal ProcessingDokumen284 halamanIntroduction To Digital Signal Processingrandombrein67% (3)

- E1419 PDFDokumen6 halamanE1419 PDFSatwant Singh100% (1)

- A 10-Bit 500-MSs 55-mW CMOS ADCDokumen12 halamanA 10-Bit 500-MSs 55-mW CMOS ADCSoodeh MiraslaniBelum ada peringkat

- Api MPMS 21-1 PDFDokumen8 halamanApi MPMS 21-1 PDFMiguelBelum ada peringkat

- Atpdt9vcu20103 (079 158)Dokumen80 halamanAtpdt9vcu20103 (079 158)Cesar Gotea LoayzaBelum ada peringkat

- Design and Implementation of A 10 Bit SAR ADCDokumen4 halamanDesign and Implementation of A 10 Bit SAR ADCVipul ChauhanBelum ada peringkat

- Analog-To-Digital Conversion Btech IIIDokumen50 halamanAnalog-To-Digital Conversion Btech IIILisa BhagatBelum ada peringkat

- Manual Blocos PCS7Dokumen1.898 halamanManual Blocos PCS7Beto BarcelosBelum ada peringkat

- Cadence Based Imlementation of SuccessiveApproximation ADC Using 45nm Cmos TechnologyDokumen6 halamanCadence Based Imlementation of SuccessiveApproximation ADC Using 45nm Cmos TechnologyUtsavBelum ada peringkat

- Design of A Pipelined 8b 10MSPS Analog To Digital Converter From System To OTADokumen22 halamanDesign of A Pipelined 8b 10MSPS Analog To Digital Converter From System To OTAZarion JacobsBelum ada peringkat

- Study of Various ADCs and Compare Their Performance and ParametersDokumen12 halamanStudy of Various ADCs and Compare Their Performance and ParametersijaertBelum ada peringkat

- Flash ADC Design in ElectricDokumen22 halamanFlash ADC Design in ElectricNagaraj HegdeBelum ada peringkat

- Dual Slope ADC DesignDokumen10 halamanDual Slope ADC DesignMoHaMMeD HaLaByBelum ada peringkat

- Design and Simulation of DAC On The Basis of Capacitor ArrayDokumen4 halamanDesign and Simulation of DAC On The Basis of Capacitor ArrayAmitBelum ada peringkat

- A High-Speed High-Resolution Latch Comparator For Pipeline Analog-to-Digital ConvertersDokumen4 halamanA High-Speed High-Resolution Latch Comparator For Pipeline Analog-to-Digital ConvertersJessyBelum ada peringkat

- 12EC62R20 Ramesh SynopsisDokumen9 halaman12EC62R20 Ramesh Synopsisprasad72207Belum ada peringkat

- A 1-GS/s CMOS 6-Bit Flash ADC With An Offset Calibrating MethodDokumen4 halamanA 1-GS/s CMOS 6-Bit Flash ADC With An Offset Calibrating MethodSunil PandeyBelum ada peringkat

- Design and Simulation of 1-Bit Sigma-Delta ADC Using Ngspice ToolDokumen5 halamanDesign and Simulation of 1-Bit Sigma-Delta ADC Using Ngspice ToolIjarcsee JournalBelum ada peringkat

- Analog To Digital ConverterDokumen4 halamanAnalog To Digital Converterzero kimochiBelum ada peringkat

- Laboratory Experiment 6 - Analog To DigitalDokumen4 halamanLaboratory Experiment 6 - Analog To DigitalyellowsubmirBelum ada peringkat

- L4 EaDokumen7 halamanL4 EaIoanaNicoletaBelum ada peringkat

- Low Power Nine-Bit Sigma-Delta ADC Design Using TSMC 0.18micron TechnologyDokumen5 halamanLow Power Nine-Bit Sigma-Delta ADC Design Using TSMC 0.18micron Technologyeditor_ijtel100% (1)

- IEEE - A 1.8V 1MSps Rail-To-Rail 10-Bit SAR ADC in 0.18um CMOS PDFDokumen3 halamanIEEE - A 1.8V 1MSps Rail-To-Rail 10-Bit SAR ADC in 0.18um CMOS PDFQuoc Thang TranBelum ada peringkat

- Modelling and Simulation of Sigma-Delta Adc in Vhdl-AmsDokumen5 halamanModelling and Simulation of Sigma-Delta Adc in Vhdl-AmsVitu VituBelum ada peringkat

- Low-Power CMOS Image Sensor Based On Column-Parallel Single-Slope/SAR Quantization SchemeDokumen6 halamanLow-Power CMOS Image Sensor Based On Column-Parallel Single-Slope/SAR Quantization SchemeRaghul RamasamyBelum ada peringkat

- FVofDiffOpAmp WPDokumen51 halamanFVofDiffOpAmp WPmarius260Belum ada peringkat

- Differential Analog Data Path DC Offset Calibration MethodsDokumen7 halamanDifferential Analog Data Path DC Offset Calibration MethodsLincoln RibeiroBelum ada peringkat

- Adc 0804Dokumen5 halamanAdc 0804gouttBelum ada peringkat

- Nama: Refin Ananda NIM: 3.32.17.0.20 Kelas: EK-3A Individual Presentation 2 Analog To Digital Converter 1. The Meaning of ADCDokumen4 halamanNama: Refin Ananda NIM: 3.32.17.0.20 Kelas: EK-3A Individual Presentation 2 Analog To Digital Converter 1. The Meaning of ADCRifky Yoga PratamaBelum ada peringkat

- 3 Design and Simulation of First Order Sigma-Delta ModulatorDokumen4 halaman3 Design and Simulation of First Order Sigma-Delta Modulatorlim hyBelum ada peringkat

- Digital-to-Analog Analog-to-Digital: Interface Part IV MicroprocessorDokumen30 halamanDigital-to-Analog Analog-to-Digital: Interface Part IV MicroprocessorVineeth KumarBelum ada peringkat

- ADE - Pspice Lab ManualDokumen12 halamanADE - Pspice Lab ManualShashiBelum ada peringkat

- 8-Bit Level Crossing ADCDokumen31 halaman8-Bit Level Crossing ADCAnilguptaBelum ada peringkat

- A Digital Background Technique For Pipelined Analog-to-Digital ConvertersDokumen5 halamanA Digital Background Technique For Pipelined Analog-to-Digital ConverterskennyBelum ada peringkat

- 一种0 18微米CMOS工艺下超高速宽带折叠内插ADC的数字校正技术Dokumen8 halaman一种0 18微米CMOS工艺下超高速宽带折叠内插ADC的数字校正技术Kirankumar LadBelum ada peringkat

- Chapter 1 IntroductionDokumen39 halamanChapter 1 IntroductionNivedini KuttiBelum ada peringkat

- P109 113 PDFDokumen5 halamanP109 113 PDFSuraj Kumar PrustyBelum ada peringkat

- Oregon State OR 9733 I, USA: Jipeng Gil-Cho Ahn, Dong-Young Chang, and Un-Ku MoonDokumen4 halamanOregon State OR 9733 I, USA: Jipeng Gil-Cho Ahn, Dong-Young Chang, and Un-Ku MoonAlex WongBelum ada peringkat

- Fig 1.1. ADC As An Interface Between Physical World and Digital ProcessorsDokumen51 halamanFig 1.1. ADC As An Interface Between Physical World and Digital ProcessorsSupriyo SrimaniBelum ada peringkat

- Lesson Adc PWMDokumen36 halamanLesson Adc PWMDavidRubeomBelum ada peringkat

- Analog To Digital ConverterDokumen7 halamanAnalog To Digital ConverterPratyay DharBelum ada peringkat

- Icaet2017073 PDFDokumen5 halamanIcaet2017073 PDFKaushik YadiyalBelum ada peringkat

- Experiment No. 4 ADC PDFDokumen16 halamanExperiment No. 4 ADC PDFRia Cordova0% (1)

- An-742 Application Note: Frequency Domain Response of Switched-Capacitor AdcsDokumen8 halamanAn-742 Application Note: Frequency Domain Response of Switched-Capacitor AdcskabuslagakBelum ada peringkat

- Interfacing To The Analog WorldDokumen47 halamanInterfacing To The Analog WorldRM ZhaloBelum ada peringkat

- Simulink Behavioral Modeling of A 10-Bit Pipelined ADCDokumen9 halamanSimulink Behavioral Modeling of A 10-Bit Pipelined ADCbhasin_hemantBelum ada peringkat

- TI Data Converter GuideDokumen16 halamanTI Data Converter GuideDavid PostonBelum ada peringkat

- Analog To Digital Converter - Block Diagram, Types Its ApplicationsDokumen10 halamanAnalog To Digital Converter - Block Diagram, Types Its ApplicationsNikka Hernandez FloresBelum ada peringkat

- A Mosfet-Only Dac For A General Array Configured Device: E. Montane, G. Hornero, G. Chapinal, J. SamitierDokumen5 halamanA Mosfet-Only Dac For A General Array Configured Device: E. Montane, G. Hornero, G. Chapinal, J. SamitierMiguel BrunoBelum ada peringkat

- An Analysis and Design of High Performance Power Consumption Double Tail Comparator Using Gated Clock and Power Gating TechniquesDokumen7 halamanAn Analysis and Design of High Performance Power Consumption Double Tail Comparator Using Gated Clock and Power Gating TechniquesIJIRSTBelum ada peringkat

- A Low Power 6-Bit Flash ADC With Reference Voltage and Common-Mode CalibrationDokumen6 halamanA Low Power 6-Bit Flash ADC With Reference Voltage and Common-Mode CalibrationSherif M. DabourBelum ada peringkat

- Analog To Digital (ADC) and Digital To Analog (DAC) ConvertersDokumen12 halamanAnalog To Digital (ADC) and Digital To Analog (DAC) ConvertersIoana IoanaBelum ada peringkat

- Sar AdcDokumen40 halamanSar AdcNivedini KuttiBelum ada peringkat

- A 1.8V 12-Bit 230-MS/s Pipeline ADC in 0.18 M CMOS TechnologyDokumen4 halamanA 1.8V 12-Bit 230-MS/s Pipeline ADC in 0.18 M CMOS Technologyfaithfully_fatihBelum ada peringkat

- Lab 6. Simulation of Feedback Analog - Digital ConvertersDokumen8 halamanLab 6. Simulation of Feedback Analog - Digital ConvertersIoanaNicoletaBelum ada peringkat

- Analog To Digital ConvertersDokumen11 halamanAnalog To Digital Convertersمحمد ماجدBelum ada peringkat

- Universal Digital Controller For Boost CCM Power Factor Correction Stages Based On Current Rebuilding ConceptDokumen12 halamanUniversal Digital Controller For Boost CCM Power Factor Correction Stages Based On Current Rebuilding ConceptsindhukamitkarBelum ada peringkat

- Data ConversionDokumen4 halamanData ConversionpauliBelum ada peringkat

- An Adaptive Impedance Force Control Approach For Robotic Cell MicroinjectionDokumen6 halamanAn Adaptive Impedance Force Control Approach For Robotic Cell MicroinjectionAlioune Badara DioufBelum ada peringkat

- EU 12400 E-May10Dokumen62 halamanEU 12400 E-May10k_jeyBelum ada peringkat

- TN 517 PDFDokumen8 halamanTN 517 PDFMedoBoudyBelum ada peringkat

- HLW8012 User Manual: Work Phone:0755 29650970Dokumen11 halamanHLW8012 User Manual: Work Phone:0755 29650970Abhishek GuptaBelum ada peringkat

- Smart Transmitter HartDokumen31 halamanSmart Transmitter HartNur Aleeya FazlinBelum ada peringkat

- Supplement S10 To The Airplane Flight Manual Da 42 NG Flight Data Logging DeviceDokumen12 halamanSupplement S10 To The Airplane Flight Manual Da 42 NG Flight Data Logging DeviceVincent LefeuvreBelum ada peringkat

- MMM Lecture - Unit 1 - Intro To MeasurementsDokumen37 halamanMMM Lecture - Unit 1 - Intro To MeasurementsAlanka BhanuBelum ada peringkat

- DX100 HW0486052Dokumen56 halamanDX100 HW0486052Thiago de SousaBelum ada peringkat

- Difference Between Sensor & Transducer (With Comparison Chart) - Circuit GlobeDokumen4 halamanDifference Between Sensor & Transducer (With Comparison Chart) - Circuit Globegyu1751asbBelum ada peringkat

- Building HVAC 03 en - 123Dokumen215 halamanBuilding HVAC 03 en - 123Artur Mkrtchyan100% (1)

- Communication Systems - I - EE 228Dokumen2 halamanCommunication Systems - I - EE 228Asim AliBelum ada peringkat

- Codigos de Falla (Mercedez)Dokumen3 halamanCodigos de Falla (Mercedez)Juan Betancur OsorioBelum ada peringkat

- NC Studio Controller ATC ManualDokumen87 halamanNC Studio Controller ATC ManualMajid RakhshiBelum ada peringkat

- Computer Networks: Characteristics of Data CommunicationDokumen16 halamanComputer Networks: Characteristics of Data CommunicationMaaz AhmadBelum ada peringkat

- Signals, Linear Systems, and ConvolutionDokumen18 halamanSignals, Linear Systems, and ConvolutionmarriyumBelum ada peringkat

- MAS2600: Testing and Recalibration Reference ManualDokumen5 halamanMAS2600: Testing and Recalibration Reference ManualAleksey TopolnytskyBelum ada peringkat

- (592 TO 606) First Half - 2014 Programme of The T.E. (Sem.-V) (All Branches) ExaminationsDokumen1 halaman(592 TO 606) First Half - 2014 Programme of The T.E. (Sem.-V) (All Branches) Examinationsakik_ranadeBelum ada peringkat

- MR3461 - SI - Set BDokumen2 halamanMR3461 - SI - Set BScientist SakthivelBelum ada peringkat

- INST260 Sec1Dokumen118 halamanINST260 Sec1aricanBelum ada peringkat

- CENG 241 Digital Design 1: Amirali Baniasadi Amirali@ece - Uvic.caDokumen36 halamanCENG 241 Digital Design 1: Amirali Baniasadi Amirali@ece - Uvic.camuhammad ibne aminBelum ada peringkat

- Experiment No.1 I DSP TMS320C6713 DSK & O DT & Matlab: Lab Manual EEE324 Digital Signal ProcessingDokumen27 halamanExperiment No.1 I DSP TMS320C6713 DSK & O DT & Matlab: Lab Manual EEE324 Digital Signal ProcessingMirza Riyasat AliBelum ada peringkat

- Transducer Up To 4500 MM Touchless Absolute Series TLM With Start/ Stop-, Ssi-, Dymos-, Analog-InterfaceDokumen4 halamanTransducer Up To 4500 MM Touchless Absolute Series TLM With Start/ Stop-, Ssi-, Dymos-, Analog-Interfacelabtlm ikasariBelum ada peringkat

- Ar007Dokumen20 halamanAr007anithkuBelum ada peringkat