Alcatel Omnipcx 4400: Section XX Cpu3 (Step2-Step3) Board

Diunggah oleh

Edmundo Melchor GarcíaJudul Asli

Hak Cipta

Format Tersedia

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniHak Cipta:

Format Tersedia

Alcatel Omnipcx 4400: Section XX Cpu3 (Step2-Step3) Board

Diunggah oleh

Edmundo Melchor GarcíaHak Cipta:

Format Tersedia

A L C

T E L

Alcatel OmniPCX 4400

SECTION xx

CPU3 (step2-step3) board

Ed.02

A L C

T E L

Alcatel OmniPCX 4400

Section xx - CPU3 (step2-step3) board

Section xx - CPU3 (step2-step3) board

SUMMARY

CPU3 board (step2 - step3)

Operation .......................................................................................................

1. Presentation..........................................................................................

2. Environment..........................................................................................

3. General operating principles ...............................................................

4. Functional blocks ..................................................................................

Configuration..................................................................................................

1. CPU3 step 2 board ................................................................................

2. CPU3 step 3 board ................................................................................

3. Meaning of the LED...............................................................................

Connection ......................................................................................................

1. Connection ............................................................................................

2. Output pins ...........................................................................................

OBCA board

Operation .......................................................................................................

1. Presentation..........................................................................................

2. Environment..........................................................................................

3. General principle of operation.............................................................

4. Functional blocks ..................................................................................

VMU-OBCA board

Operation .......................................................................................................

1. Presentation..........................................................................................

2. Environment..........................................................................................

3. General principe of operation..............................................................

4. Functional blocks ..................................................................................

Ed.02

Ref.3BA19919ENAA

xx. 3

xx. 3

xx. 3

xx. 4

xx. 5

xx.11

xx.11

xx.13

xx.15

xx.17

xx.17

xx.18

xx.23

xx.23

xx.24

xx.25

xx.26

xx.29

xx.29

xx.30

xx.31

xx.32

xx.1

A L C

T E L

Alcatel OmniPCX 4400

Section xx - CPU3 (step2-step3) board

xx.2

Ref.3BA19919ENAA

Ed.02

A L C

T E L

Alcatel OmniPCX 4400

Section xx - CPU3 (step2-step3) board

CPU3 board (step2 - step3)

Operation

44A03222123A100AAEN

CPU3 board (step2 - step3)

Operation

Edition: 02

1.

Presentation

The CPU3 board (step 2 or step 3) is the heart of the system. It generates the clock signals and processes the system applications (atelephone, telematics, messaging applications, etc.). It is used to

download the flash EPROMs of each of the systems boards. It permits connection of an external music

on-hold and a voice service and provides four V24 channels, an SCSI bus (step 2 only), an on-board

backplane Ethernet access and a direct 10base T access.

A second CPU3 board (optional) (same step) can be installed to back up the first board. A backplane

signal (depending on the position) specifies, on system power up, the master or slave function of each

CPU3 (step 2 or 3) board. Switch-over takes place in the event of faulty clock signals.

The following daughter boards (optionnal) can be installed on the CPU3 board (step 2 or 3):

- OBCA: 64kbit/s access (seemodule VMU-OBCA board - Operation ),

- VMU-OBCA: voice mail + 64kbit/s access (seemodule VMU-OBCA board - Operation ).

The CPU3 board (step 2 or 3) configuration is described in module CPU3 board (step2 - step3) Configuration .

The CPU3 board (step 2 or 3) connection is described in module CPU3 board (step2 - step3) - Connection .

2.

Environment

2.1.

Position in the rack

The CPU3 (step 2 or 3) is connected to the other system boards via the I/O controller which integrates

a C1 to establish the type 1 links wityh the 27 other system boards.

The CPU3 board (step 2 or 3) can be connected to the following, on the front side :

- the IO2 board, via ATB2 connection interface board,

- the IO2N board, via ISAB2 connection interface board.

The CPU3 (step 2 or 3) has a predefined position according to the type of ACT.

Ed.02

Ref.3BA19919ENAA

xx.3

A L C

T E L

Alcatel OmniPCX 4400

CPU3 board (step2 - step3)

Operation

2.2.

Section xx - CPU3 (step2-step3) board

Inputs/outputs

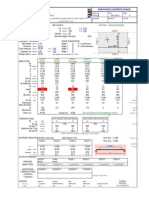

Figure 1 : CPU3 (step2-step3) board inputs/outputs diagram

10 base T port, AUI

Ethernet interface

Embedded Ethernet link

TYPE 1 links

T1 to T28

TYPE 1 links

R1 to R28

I/O controller

Master/slave

Alarm

Network line forwarding

External music on hold

Voice service

B bus

CPU

Floppy

SCSI bus (step 2)

Remote reset

4 V24 links

512kHz external

reference clock

256kHz converter

synchronisation

Rectifier alarm

DEM1 to 5

-48V

0V48

3.

System

clocks

Power supply

16MHz system clocks

8kHz frame synchronisation

On/Off

General operating principles

In case of failure of the main (master) CPU3 (Step 2 or 3) board, a backup (slave) CPU3 (same step)

board will take over. The backplane master/slave signal specifies to each CPU (according to its position) the master (-48V) or slave (0V48) function on initialisation. During normal operation, the master

CPU considers the slave CPU as an interface board. The CPUs communicate via the 256 kbit/s channel of the type 1 link. The CPU in stand-by monitors the backplane generated clocks of the active CPU.

In case of master CPU reset (resulting in loss of clocks) or clock failure, switch over will take place and

the slave CPU will become master CPU.

xx.4

Ref.3BA19919ENAA

Ed.02

A L C

T E L

Alcatel OmniPCX 4400

Section xx - CPU3 (step2-step3) board

4.

Functional blocks

4.1.

LIST

CPU3 board (step2 - step3)

Operation

The CPU3 (step 2 or 3) is made up of the following blocks:

- control unit,

- I/O controller integrating clock and tone generation,

- Ethernet, SCSI (step 2 only) and V24 interfaces,

- power supply block.

Ed.02

Ref.3BA19919ENAA

xx.5

A L C

T E L

Alcatel OmniPCX 4400

CPU3 board (step2 - step3)

Operation

Section xx - CPU3 (step2-step3) board

Figure 2 : CPU3 (step2 or step3) board functional summary diagram

Front

panel

Backplane

Ethernet LED

Processor

LED

2 asynchronous

V24 (A/B)

802.3 ports

80386EX

(10 base T)

ETHERNET

interface

Embedded

Ethernet link

DRAM

NAR6

Bus interface

2xV24

interfaces

2 asynchronous

Disk drive

controller

Disk drive

ISA

ATB2

SCSI bus

SCSI

Daughter

board

ISAB2

V24 (C/D)

(step 2 only)

EPROM

Bus inter

face

Bus interface

Protection key

Hard

disk

Music on

hold

External

music

on hold

C1

T1/ R1

to

T28/R28

B bus

B bus

Bus interface

Processor

IO2

IO2N

PCM E

Voice mail

interface

PCM R

HB, SYNC

Shared

RAM

512 kHz

8 kHz

256 kHz

16 MHZ

ASIC

VIVALDI

Shared

FLASH

EPROM flash

On/Off

xx.6

+5V

+12V

Ref.3BA19919ENAA

JTAG

CM2 converter

JTAG

256 kHz

-48V

Ed.02

A L C

T E L

Alcatel OmniPCX 4400

Section xx - CPU3 (step2-step3) board

4.2.

CPU3 board (step2 - step3)

Operation

Blocks description

4.2.1. Control unit

This is a PC-AT platform organized around an 80386 EX-33 microprocessor. It comprises the following

elements:

- microprocessor,

- dynamic memory,

- ASIC NAR6.

Microprocessor

The microprocessor is a 32-bit 80386 EX-33 de 32bits integrating a parallel bus controller, clock

controller, watchdog, serial asynchronous I/O unit (2 V24, COM A and COM B).

DRAM

The DRAM has a maximum capacity of 64 MB (memory modules).

ASIC NAR6

The NAR6 works directly on the picroprocessor bus. It supports the following system functions:

- DRAM controller,

- bus interface management (ISA, IDE, I/O),

- real time clock (calendar),

- JTAG functionality.

4.2.2. I/O controller

The I/O controller is made up of the following parts:

- C1 circuit,

- processor,

- clock and tone module,

- shared memory,

- voice service interface,

- external music interface.

C1 circuit

This component handles the I/Os for the CPU3 (Step 2 or 3) board. It is connected to the other system

boards via type 1 backplane links and carries out the following functions:

- distribution of music on hold and multi-frequencies to the interface boards,

- extraction of the four signalling TSs from each type 1 link and transmission to the control unit,

Ed.02

Ref.3BA19919ENAA

xx.7

A L C

T E L

Alcatel OmniPCX 4400

CPU3 board (step2 - step3)

Operation

Section xx - CPU3 (step2-step3) board

- exchange on type 1 links of voice channels with the other couplers,

- injection of the signalling from the CPU3 (Step 2 or 3) on the four type 1 link TSs destined for

an interface board.

Processor

This 80C188 type processor controls the C1 circuit, FLASH memory programming and activation of the

common part processor LED. In case of system failure (PSAL rectifier alarm or watch dog), it generates

two signals:

- the network line forwarding signal controls the forwarding relays installed on the MDF. This

forwards the network lines directly to the back-up telephone stations,

- the alarm signal informs the exterior that the system is no longer operational.

Clocks and tones module

Most peripherals are integrated in a VIVALDI ASIC. This carries out:

- clock generator.

Clock signals are generated for the whole system:

16 MHz system clocks (16M1 and 16M2),

8 KHz frame sync (8K1 and 8K2),

converter synchronisation (256 KHz).

Clocks 16M2 and 8K2 only service the lower shelf in the 28 position backplane.

This module can be synchronised by a 512 KHz reference clock signal from the public network via

a T2, PCM or T0 interface board or a DECT board.

The clocks sent on the system are generated from the external clock or else by a local oscillator

(16.384 MHz not slaved). VIVALDI ensures the selection.

- tone generator.

The frequencies are generated from samples stored in a FLASH EPROM, which is programmed via

the VIVALDI component. The tones and multi-frequencies used by the system interface boards are

MFQ23 type (16 frequencies), ringing frequency (50 Hz), TL frequency (50 Hz), modem frequency

(2100 Hz) as well as the tones specific to each country (Dial tone, send tone, etc.).

- watchdog function.

Voice mail interface (optional)

This module is an optional daughter board (MICROPAC interface). It interfaces with the Alcatel 4630

voice messaging system.

Shared memory

This 256 kB memory can be accessed for read/write by the 80C188 processor and 80386 EX platform

via the ISA bus. Memory access is controlled by an arbitrator.

Music on hold interface

xx.8

Ref.3BA19919ENAA

Ed.02

A L C

T E L

Alcatel OmniPCX 4400

Section xx - CPU3 (step2-step3) board

CPU3 board (step2 - step3)

Operation

This module interfaces with an external music on hold . This music is then distributed to the system

boards via type 1 links.

4.2.3. Interfaces

Ethernet interface

This interface is used for connection to an Ethernet network (connection to a server, etc.) via a connection box. The accesses available are:

- 802.3 link implemented in the circuit (on-board Ethernet link) which distributes to the ECX1 board,

- 10 Base T AUI type interface. When this interface is in service, the 10 Base T LED on the front

panel is on.

SCSI controller (step 2 only)

This interfaces with the ISA bus and offers an SCSI port for data transfer to the circuits on a parallel

I/O bus (SCSI peripheral installed on an MMS board, for example).

Floppy interface

The floppy controller is 82078 (step 2) or PC 8477B (step 3) type. The connection to the floppy is by

cable via the backplane.

V24 interfaces

Two V24 channels (COMC and COMD) are handled by a DUART (Dual Universal Asynchronous Receiver/Transmitter).

Hard disk

The IDE standard hard disk with integrated controller has a minimum capacity of 350 MB.

Protection key

A key, protecting the software is plugged into a support.

4.2.4. Power supply

This is controlled by a power switch. The CM2 converter supplies the +5V/5A and +12V/60mA voltages required for board operation. An alarm signal (rectifier alarm) informs the control unit of rectifier

failure, thus allowing hard disk update before cut-off.

The "On/Off" signal is used to simultaneously start-up/cut-off the power supply to the CPU board and

the other boards connected on the CPU bus so that the bus interface circuits are not damaged.

Ed.02

Ref.3BA19919ENAA

xx.9

A L C

T E L

Alcatel OmniPCX 4400

CPU3 board (step2 - step3)

Operation

xx.10

Section xx - CPU3 (step2-step3) board

Ref.3BA19919ENAA

Ed.02

A L C

T E L

Alcatel OmniPCX 4400

Section xx - CPU3 (step2-step3) board

CPU3 board (step2 - step3)

Configuration

44A03222123A020AAEN

CPU3 board (step2 - step3)

Configuration

Edition: 02

1.

CPU3 step 2 board

1.1.

Reference

CPU3 step 2 board: 3BA 57162 AB / 3BA 57162 BB (USA).

1.2.

Presentation

The diagram below gives the position and number for each strap present on the CPU3 step 2 board.

Ed.02

Ref.3BA19919ENAA

xx.11

A L C

T E L

Alcatel OmniPCX 4400

CPU3 board (step2 - step3)

Configuration

Section xx - CPU3 (step2-step3) board

Figure 3 : View of the CPU3 step 2 board

H1

X54

X55

X26

H2

X24

X25

connecteur

micropac

1.3.

Strappings

Ex-factory strappings are shown on a grey background.

xx.12

Ref.3BA19919ENAA

Ed.02

A L C

T E L

Alcatel OmniPCX 4400

Section xx - CPU3 (step2-step3) board

CPU3 board (step2 - step3)

Configuration

Loop closed

Alarm relay

X54

X54

X55

X55

X26

X26

33 KOhms in the loop

Alarm loop

2.

CPU3 step 3 board

2.1.

Reference

Loop open

X24

33 KOhms short-circuited

X25

X24

X25

CPU3 step 3 board: 3BA 57162 NA / 3BA 57162 MA (USA).

2.2.

Presentation

The diagram below gives the position and number for each strap present on the CPU3 step 3 board.

Ed.02

Ref.3BA19919ENAA

xx.13

A L C

T E L

Alcatel OmniPCX 4400

CPU3 board (step2 - step3)

Configuration

Section xx - CPU3 (step2-step3) board

Figure 4 : View of the CPU3 step 3 board

H1

H2

X25

X24

X26

connecteur

Micropac

2.3.

Strappings

Ex-factory strappings are shown on a grey background.

xx.14

Ref.3BA19919ENAA

Ed.02

A L C

T E L

Alcatel OmniPCX 4400

Section xx - CPU3 (step2-step3) board

CPU3 board (step2 - step3)

Configuration

Loop closed

Alarm relay

X25

X25

33 KOhms in loop

Alarm loop

Loop open

33 KOhms short-circuited

X24

X24

Music on hold

A law

Board: 3BA 57162 NA

Board: 3BA 57162 MA (USA)

3.

Meaning of the LED

3.1.

Display

law

X26

X26

X26

X26

The CPU3 (step 2 or step 3) board has 2 LED located on the front panel.

Ed.02

Ref.3BA19919ENAA

xx.15

A L C

T E L

Alcatel OmniPCX 4400

CPU3 board (step2 - step3)

Configuration

Section xx - CPU3 (step2-step3) board

Figure 5 : CPU3 (step 2 or step 3) board front panel

CPU3

CPU

ETH

3.2.

Meaning

Table 1 : Summary

LED

Meaning

CPU (Green LED)

CPU activity indicator

ETH (Orange LED)

Ethernet link activity indicator

3.3.

Cadencing

Table 2 : CPU LED

Cadencing

Meaning

ON fixed

Initialization in progress

100 ms (ON)/ 1s (OFF)

Loading in progress

10 ms (ON)/ 10 ms (OFF)

Re-flashing boot

300 ms (ON)/ 300 ms (OFF)

CPU wait

8 x (900 ms (ON)/ 600 ms (OFF))/1 s (OFF)

RAM Test error

8 x (300 ms (ON)/ 600 ms (OFF))/1 s (OFF)

Checksum error

xx.16

Ref.3BA19919ENAA

Ed.02

A L C

T E L

Alcatel OmniPCX 4400

Section xx - CPU3 (step2-step3) board

CPU3 board (step2 - step3)

Connection

44A03222123A030AAEN

CPU3 board (step2 - step3)

Connection

Edition: 02

1.

Connection

The CPU3 (step 2 or 3) board must be installed in a CPU slot of the main ACT.

The CPU positions depend on the type of ACT (see the related cabinet installation documentation).

Daughter boards connection to CPU3 step 2-3

Figure 6 : Connection diagram

Memory modules

Hard kee

CPU3 board

OBCA board

(option)

Hard disk

VMU-OBCA board

(option)

The CPU3 connection to external components depends on the type of ACT:

- M2 or M3 cabinet, see module M2/M3 cabinet - Internal connections ,

- VH rack, see module VH rack - Internal connections ,

- WM1 rack, see module WM1 Rack - Internal connections .

Ed.02

Ref.3BA19919ENAA

xx.17

A L C

T E L

Alcatel OmniPCX 4400

CPU3 board (step2 - step3)

Connection

2.

Output pins

2.1.

CPU3 step 2 board

Section xx - CPU3 (step2-step3) board

The output pins of the CPU3 board step 2 are shown below:

C

REMARKS

RXDA

RIA

TXDA

CTSA

GND

RTSA

TXDi, RXDi, RTSi,

CTSi, DTRi, DSRi,

DCDi, RIi = output

wires for the V24 A

and B

DSRA

DCDA

DTRA

RIB

DCDB

GND

RXDB

DSRB

GND

CTSB

DTRB

RTSB

TXDB

GND

GND

RESEXT1 = used to

reset by applying

12 V for 10 ms

GND

GND

(*)

(*)see CPU5

TR2

GND

TR1

CTSC, RTSC, RXDC,

TXDC = port C

(PIOC board)

10

CTSC

RESEXT1

RTSC

11

RXDC

RL1

TXDC

12

MICRN

RL2

MICRP

13

MICEN

AL1

MICEP

14

SYNCP

AL2

SYNCN

15

CLKP

GND

CLKN

16

SCSI_DPPN

GND

SCSI_D0N

xx.18

Ref.3BA19919ENAA

TR1, TR2 = wires for

the external music

on hold

MICEN, MICRN,

MICEP, MICRP,

SYNCN, SYNCP,

CLKN, CLKP =

wires for the 4630

voice service

RL1, RL2 =

command for

external line

forwarding

AL1, AL2 = alarm

wires

Ed.02

A L C

T E L

Alcatel OmniPCX 4400

Section xx - CPU3 (step2-step3) board

CPU3 board (step2 - step3)

Connection

17

TPI_RXP

SCSI_D7N

SCSI_D1N

18

TPI_RXN

SCSI_D6N

SCSI_D2N

19

SCSI_SELN

TPI_TXP

SCSI_D3N

20

GND (*)

TPI_TXN

SCSI_D4N

21

SCSI_ACKN

GND

SCSI_D5N

22

CTSD

RESEXT2

RTSD

23

RXDD

GND

TXDD

24

SCSI_BSYN

GND

SCSI_ATNN

25

INDX

GND

ME0

26

ME1

SCSI_RSTN

DS0

27

DS1

SCSI_CDN

DIR

28

STEP

SCSI_ION

WRDATA

29

WE

5V

TRK0

30

WP

GND

RDDATA

31

HDSEL

GND

DSKCHG

32

SCSI_REQN

GND

TERMPWR

2.2.

REMARKS

SCSI_xxx, TERMPWR

= for the SCSI

interface

TPI_RXP, TPI_RXN,

TPI_TXP, TPI_TXN =

for Ethernet in 10

baseT

RESEXT2 = Not

connected

CTSD, RTSD, RXDD,

TXDD = port D

(PIOC board)

INDX, ME0, ME1,

DS0, DS1, DIR,

STEP WRDATA,

WE, 5V, TRK0, WP,

RDDATA, HDSEL,

DSKCHG = wires

for the disk drive

CPU3 step 3 board

The output pins of the CPU3 board step 3 are shown below:

C

REMARQUES

RXDA

RIA

TXDA

CTSA

GND

RTSA

TXDi, RXDi, RTSi, CTSi, DTRi,

DSRi, DCDi, RIi = output

wires for the V24 A and B

DSRA

DCDA

DTRA

Ed.02

Ref.3BA19919ENAA

xx.19

A L C

T E L

Alcatel OmniPCX 4400

CPU3 board (step2 - step3)

Connection

Section xx - CPU3 (step2-step3) board

REMARQUES

RIB

DCDB

GND

TR1, TR2 =wires for the

external music on hold

RXDB

DSRB

GND

CTSB

DTRB

RTSB

TXDB

GND

GND

RESEXT1 = used to reset by

applying 12 V current for 10

ms

GND

GND

(*)

(*) see CPU5

TR2

GND

TR1

CTSC, RTSC, RXDC, TXDC =

port C (PIOC board)

10

CTSC

RESEXT1

RTSC

11

RXDC

RL1

TXDC

12

MICRN

RL2

MICRP

13

MICEN

AL1

MICEP

14

SYNCP

AL2

SYNCN

15

CLKP

GND

CLKN

16

GND

17

TPI_RXP

18

TPI_RXN

19

20

21

RL1, RL2 = command for

external line forwarding

AL1, AL2 = alarm wires

TPI_RXP, TPI_RXN, TPI_TXP,

TPI_TXN = for Ethernet in 10

baseT

TPI_TXP

GND (*)

MICEN, MICRN, MICEP,

MICRP, SYNCN, SYNCP,

CLKN, CLKP = wires for the

Alcatel 4630 voice services

TPI_TXN

GND

22

CTSD

RESEXT2

RTSD

23

RXDD

GND

TXDD

RESEXT2 = Not connected

ME0

CTSD, RTSD, RXDD, TXDD =

port D (PIOC board)

24

GND

25

INDX

26

ME1

DS0

27

DS1

DIR

xx.20

GND

Ref.3BA19919ENAA

Ed.02

A L C

T E L

Alcatel OmniPCX 4400

Section xx - CPU3 (step2-step3) board

CPU3 board (step2 - step3)

Connection

REMARQUES

WRDATA

INDX, ME0, ME1, DS0, DS1,

DIR, STEP WRDATA, WE, 5V,

TRK0, WP, RDDATA, HDSEL,

DSKCHG = wires for the disk

drive

28

STEP

29

WE

5V

TRK0

30

WP

GND

RDDATA

31

HDSEL

GND

DSKCHG

32

Ed.02

GND

Ref.3BA19919ENAA

xx.21

A L C

T E L

Alcatel OmniPCX 4400

CPU3 board (step2 - step3)

Connection

xx.22

Section xx - CPU3 (step2-step3) board

Ref.3BA19919ENAA

Ed.02

A L C

T E L

Alcatel OmniPCX 4400

Section xx - CPU3 (step2-step3) board

OBCA board

Operation

44A03222503A100AAEN

OBCA board

Operation

Edition: 01a

1.

Presentation

The OBCA (Optimised B-channel CPU Access) board is a daughter board supporting 3 B channels at

64 kbit/s.

It offers:

-

remote access to the system (management, download),

- access to terminals for internal applications.

OBCA board reference : 3BA 23099 AA .

The OBCA board is a board not requiring configuration.

It is installed on a CPU3 (step 2 or 3) board (see module CPU3 board (step2 - step3) - Connection ) or

CPU5 board (see module CPU5 step2 board - Connection or module CPU5 step3 board - Connection

).

Ed.02

Ref.3BA19919ENAA

xx.23

A L C

T E L

Alcatel OmniPCX 4400

OBCA board

Operation

Section xx - CPU3 (step2-step3) board

2.

Environment

2.1.

Functional environment

Figure 7 : Integration of the OBCA board in the ACT architecture.

CPU board

CPU

ISA bus

Appli

cations

Application

terminal

OBCA

IPCM2

C1

V24

TA

Terminal adapter

with protocol V120

UA

BPRA

T0/T2

Remote access

Network

2.2.

Position in the rack

The OBCA board, installed on a CPU motherboard, is connected to the IPCM2 of the board C1 component.

The exchanges between the two boards are carried out via the ISA (Industry Standard Architecture) bus.

xx.24

Ref.3BA19919ENAA

Ed.02

A L C

T E L

Alcatel OmniPCX 4400

Section xx - CPU3 (step2-step3) board

2.3.

OBCA board

Operation

Inputs/outputs

Figure 8 : OBCA board inputs/outputs diagram

CPU

IPCM2 input

Physical interface

IPCM2 output

Synchros

Communication

control

ISA interface

+5V

3.

ISA bus

Power supply

General principle of operation

The OBCA board is a daughter board for CPU3 and CPU5 boards. It offers connection oriented full

duplex links between the CPU and the external entities. These links allow dialogs with character or

packet mode applications. This board can handle up to three channels B in HDLC mode. The OBCA

board can handle the following proocols: Q922, LAPD, LAPB, V120 synchronous and asynchronous.

The OBCA board only provides Frame Relay operation (D overflow into B) on the end nodes.

The OBCA board can handle several data links multiplexed on one physical channel. It can therefore

process up to 30 concurrent data links. It is not equipped with any circuit C1,thus it cannot handle

packet switching nor frame relay.

OBCA and IO2 boards can be fitted together on the same CPU. In this way, the amount of channels

B which can be operated concurrently is 33. However, the max. amount of channels B which can be

operated in packet or character mode remains at 30.

Ed.02

Ref.3BA19919ENAA

xx.25

A L C

T E L

Alcatel OmniPCX 4400

OBCA board

Operation

4.

Functional blocks

4.1.

List

Section xx - CPU3 (step2-step3) board

The OBCA daughter board is made up of different blocks:

- CPU,

- physical interface,

- communication control,

- ISA interface,

- power supply.

xx.26

Ref.3BA19919ENAA

Ed.02

A L C

T E L

Alcatel OmniPCX 4400

Section xx - CPU3 (step2-step3) board

OBCA board

Operation

Figure 9 : OBCA board functional summary diagram

FRONT

PANEL

BACKPLANE

CPU motherboard

Physical

interface

IPCM2

TS

allocation

Synchros

CPU

Memory

Register

Arbitrator

ISA

interface

ISA bus

Shared

memory

+5V

OBCA board

256 kHz

+5V

Ed.02

Converter

Ref.3BA19919ENAA

-48V

xx.27

A L C

T E L

Alcatel OmniPCX 4400

OBCA board

Operation

4.2.

Section xx - CPU3 (step2-step3) board

Blocks description

4.2.1. CPU

The CPU part, with its architecture organised around a 68302 microcontroller, handles the following

functions:

- management of the OBCA board,

- management of the physical interface with the motherboard,

- management of communications control.

There is no manual reset on the OBCA board (this function is carried out by the CPU motherboard).

4.2.2. Physical interface

The physical interface is connected to the Internal 2 PCM of the mother CPU board. The synchronisations (4 MHz clock signal and 8 kHz frame sync signal) from the C1 component drive the OBCA board.

4.2.3. Communication control

The communications are carried out on 3 independent serial controllers. The 3 PCM channels of the

IPCM2 are assigned as follows: TS1 = channel 1, TS2 = channel 2 and TS3 = channel 3.

4.2.4. ISA interface

The ISA interface handles the exchanges between the OBCA board and the mother CPU board via the

ISA bus. It allows the motherboard to access the shared memory, board register and CPU memory

(download, maintenance functions).

The OBCA board is considered as an ISA bus peripheral.

4.2.5. Power supply

The board power supply is delivered from the converter located on the motherboard. Only the +5V is

required.

xx.28

Ref.3BA19919ENAA

Ed.02

A L C

T E L

Alcatel OmniPCX 4400

Section xx - CPU3 (step2-step3) board

VMU-OBCA board

Operation

44A03222513A100AAEN

VMU-OBCA board

Operation

Edition: 01a

1.

Presentation

The VMU-OBCA board is a daughter board which is composed of 2 parts:

- a VMU (Voice Mail Unit) voice mail part which has 4 accesses (Alcatel 4615 voice mail),

- an OBCA (Optimized B-channel CPU Access) part which supports 3 64 kbit/s B channels.

The VMU-OBCA is a board not requiring configuration.

VMU-OBCA board reference: 3BA 53176 AA .

It must be installed only on a CPU3 step 2 or 3 motherboard (see module CPU3 board (step2 - step3)

- Connection ).

Ed.02

Ref.3BA19919ENAA

xx.29

A L C

T E L

Alcatel OmniPCX 4400

VMU-OBCA board

Operation

Section xx - CPU3 (step2-step3) board

2.

Environment

2.1.

Functional environment

CPU

VMU/

OBCA

ISA bus

Mother board

Voice mail

management

terminal

C1

V24

Z

TA

UA

UA

Set with voice

mail system

BPRA

T0/T2

Remote access

Network

2.2.

Position in the rack

The VMU-OBCA board, installed on a CPU motherboard, is connected to the IPCM2 of the board C1

component.

The exchanges between the CPU3 and VMU-OBCA boards are conducted via the ISA bus.

xx.30

Ref.3BA19919ENAA

Ed.02

A L C

T E L

Alcatel OmniPCX 4400

Section xx - CPU3 (step2-step3) board

2.3.

VMU-OBCA board

Operation

Inputs/outputs

Figure 10 : VMU-OBCA board environment

OBCA

Communication

control

PCM2

ISA bus

System

interface

Synchros

VMU-OBCA

PCM2

CLK4M

System

interface

Physical interface

and ISA interface

FSY28

PCM0

PCM0

VMU

+5V

Power supply

The system interface is composed of PCM links and synchronisation signals.

3.

General principe of operation

The 2 VMU and OBCA parts integrate the following functions:

- ISA Bus Interface,

- shared FPGA (Field Programmable Gate Array) for the ISA (Industry Standard Architecture) Bus

interface command.

The VMU part has the following features:

- 2x64 Kwords DSP data memory,

- 512 Kwords of code memory,

Ed.02

Ref.3BA19919ENAA

xx.31

A L C

T E L

Alcatel OmniPCX 4400

VMU-OBCA board

Operation

Section xx - CPU3 (step2-step3) board

- 128 Mbits of FLASH NAND storage.

The OBCA part has the following features:

- MC68302 processor,

- 64 Kwords of code memory,

- 64 Kwords of shared memory.

4.

Functional blocks

4.1.

List

The VMU-OBCA daughter board is constitued of the following parts:

- OBCA module,

- VMU module,

- power supply.

xx.32

Ref.3BA19919ENAA

Ed.02

A L C

T E L

Alcatel OmniPCX 4400

Section xx - CPU3 (step2-step3) board

VMU-OBCA board

Operation

Figure 11 : VMU-OBCA board functional summary diagram

FRONT

PANEL

BACKPLANE

CPU mother board

VMU/OBCA daughter

board

Physical

interface

MICI2

CPU

Memory

TS assign

ment

Synchros

Register

Arbitra

tor

ISA

interface

Bus ISA

Shared

memory

OBCA part

VMU part

EPROM

Nand

Main DSP

SRAM

+5V

SRAM

Slave DSP

Logic

Reset

CPLD

256 kHz

-48V

Convertor

+5V

Ed.02

Ref.3BA19919ENAA

xx.33

A L C

T E L

Alcatel OmniPCX 4400

VMU-OBCA board

Operation

4.2.

Section xx - CPU3 (step2-step3) board

Blocks description

4.2.1. OBCA module

See OBCA board (voir module OBCA board - Operation ).

4.2.2. VMU module

The Voice mail module (VMU) has 4 voice accesses, up to 128 voice mailboxes and 340 minutes of

speech storage (maximum 4 minutes per message).

VMU interface

The host interface of the slave DSP is used for all the exchanges with the CPU, including the start-up of

each DSP. All the signalling messages are transferred from the slave DSP to the main DSP via the SSI

0 interface.

The host interface of the slave DSP is accessed via a logic applied to the CPLD (Complex Programmable

Logic Device).

The logic provides functional accesses, including the time conditions between the ISA-BUS interface

and the host interface of the slave DSP.

The quick interrupt of the slave DSP is used for both transfer directions between the CPU and the slave

DSP. The interrupt vector of the Host Receiver and the Host Emitter may be written as a move instruction

instead of a hop instruction. The DSP will insert this instruction in the normal execution of a waiting

queue without deleting this queue.

The slave DSP must never inhibit the interrrupts for a duration greater than a word read access cycle

or 2 bytes of the Host interface.

Reset circuit

After a CPU hardware reset, the VMU part must be reset. The reset may be removed from the VMU

part of the CPU software. The VMU part may be reset during a shutdown. The reset function applies

to the CPLDs OBCA part.

DSP LLP programming

The DSPs are controlled by the 4 MHz clock of the C1 link. The start-up program must have programming which is suitable for the PLL.

Features of the main DSP

- Start-up by SSI 0 synchronous serial interface,

- Reset and interrupt of the EPROM NAND,

- Communication interrupt,

- Access time request,

- Configuration of the B port bits to control the external hardware,

- Configuration of the C port bits as SSI 0 synchronous serial interface,

- Interface of the signals to the CPLD,

- Data bus connection,

xx.34

Ref.3BA19919ENAA

Ed.02

A L C

T E L

Alcatel OmniPCX 4400

Section xx - CPU3 (step2-step3) board

VMU-OBCA board

Operation

- Exchange of speech data on TSs 1,2,3 and 4 of PCMI 0 and PCMO 0,

- Use of the SSI 0 synchronous serial interface to transfer the boot codes to the main DSP and

exchange messages with the CPU.

Features of the slave DSP

- Communication interrupt to the main DSP,

- Access time request,

- Configuration of the B port bits to act as a host interface,

- Configuration of the C port bits as SSI 0 synchronous serial interface,

- Exchange of speech data on TSs 1,2,3 and 4 of PCMI 0 and PCMO 0,

- Use of the SSI 0 synchronous serial interface to transfer the boot codes to the main DSP and

exchange messages with the CPU.

4.2.3. Power supply

The converter located on the mother board supplies the board with power. Only +5V will be used.

Ed.02

Ref.3BA19919ENAA

xx.35

Anda mungkin juga menyukai

- Raft Slab DesignDokumen5 halamanRaft Slab DesignLekins Sefiu Yekini100% (2)

- ABB Motors for Hazardous AreasDokumen65 halamanABB Motors for Hazardous Areaslaem269Belum ada peringkat

- PVC Pipe Longevity ReportDokumen24 halamanPVC Pipe Longevity ReportUnibellBelum ada peringkat

- BGA ENG MATL TS 0006 Cathodic Protection Rev 02aDokumen26 halamanBGA ENG MATL TS 0006 Cathodic Protection Rev 02aGururaj P KundapurBelum ada peringkat

- Ua32 - 3ba53050Dokumen17 halamanUa32 - 3ba53050Edmundo Melchor GarcíaBelum ada peringkat

- MCQs DOMDokumen5 halamanMCQs DOMyuvraj PrajapatiBelum ada peringkat

- Inspection and Requalification of Flywheels Before Remounting - 09197Dokumen5 halamanInspection and Requalification of Flywheels Before Remounting - 09197Mark ChapmanBelum ada peringkat

- Assignment 3 CELTADokumen3 halamanAssignment 3 CELTAHam Naz80% (5)

- CPU7Dokumen16 halamanCPU7sunnymachoo100% (1)

- Omnipcx Enterprise Purple - PresalesDokumen149 halamanOmnipcx Enterprise Purple - PresalesDinusha BandaraBelum ada peringkat

- C - EWM - 90 - SAP Certified Application Associate - Extended Warehouse Management 9Dokumen4 halamanC - EWM - 90 - SAP Certified Application Associate - Extended Warehouse Management 9Padma Raju0% (1)

- SDH KLM MappingDokumen10 halamanSDH KLM MappingAntariksha SinghBelum ada peringkat

- AN5116-06B Hardware DescriptionDokumen76 halamanAN5116-06B Hardware DescriptionFlavio CRBelum ada peringkat

- Data Center Site Infrastructure Tier Standard: Topology: Uptime Institute, LLCDokumen0 halamanData Center Site Infrastructure Tier Standard: Topology: Uptime Institute, LLCOrlando Ramirez MedinaBelum ada peringkat

- 207.OTN 260SCX2 and 130SCX10 Cards V1 04 11feb16Dokumen24 halaman207.OTN 260SCX2 and 130SCX10 Cards V1 04 11feb16Ronald N Meza C100% (1)

- PM591 EthDokumen15 halamanPM591 EthIsaac Costa100% (1)

- Alcatel-Lucent Omnipcx Enterprise Communication ServerDokumen14 halamanAlcatel-Lucent Omnipcx Enterprise Communication ServerAnh Tuấn Trần100% (1)

- Alcatel-Lucent OmniPCX Enterprise DPT1Dokumen18 halamanAlcatel-Lucent OmniPCX Enterprise DPT1Hải Đàm100% (1)

- NPRAE-PEBX CardDokumen14 halamanNPRAE-PEBX CardSharn25100% (1)

- System Networking PDFDokumen432 halamanSystem Networking PDFEmmanuel Rodriguez100% (1)

- I2C PWM HardwareDokumen15 halamanI2C PWM HardwareNaveenkrishna Mohanasundaram100% (2)

- Alcatel 1641 SX OptinexDokumen6 halamanAlcatel 1641 SX OptinexCarlos Higa100% (1)

- 3AG24101BFAAFMZZA - V1 - 1678 MCC Release 04.05.x Product Release NoteDokumen33 halaman3AG24101BFAAFMZZA - V1 - 1678 MCC Release 04.05.x Product Release Notescribd01Belum ada peringkat

- 23 BDokumen16 halaman23 BEdmundo Melchor García100% (1)

- Overview - 1830PSS4 - 16 - 32Dokumen71 halamanOverview - 1830PSS4 - 16 - 32Jonatan SoaresBelum ada peringkat

- Alcatel 4635 PDFDokumen159 halamanAlcatel 4635 PDFEdmundo Melchor GarcíaBelum ada peringkat

- Alcatel 4635 PDFDokumen159 halamanAlcatel 4635 PDFEdmundo Melchor GarcíaBelum ada peringkat

- SIAE ALS PDH Radio Family Manual PDFDokumen324 halamanSIAE ALS PDH Radio Family Manual PDFbbzinhoalBelum ada peringkat

- Alcatel 4645 Con MGRDokumen16 halamanAlcatel 4645 Con MGREdmundo Melchor García100% (1)

- Alcatel 4645 Con MGRDokumen16 halamanAlcatel 4645 Con MGREdmundo Melchor García100% (1)

- Hit 7300 BENEFITS OF CORIANT'S Multi-Haul PDFDokumen3 halamanHit 7300 BENEFITS OF CORIANT'S Multi-Haul PDFTrương Thị LanBelum ada peringkat

- Conf 2Dokumen8 halamanConf 2Mohamed ShabanaBelum ada peringkat

- MOP# M-ALU-0007109 - 108-DWDMSS1-FTR7@15 SitesDokumen1 halamanMOP# M-ALU-0007109 - 108-DWDMSS1-FTR7@15 SitesEhtesham KhanBelum ada peringkat

- HiT Training Presentation-2Dokumen97 halamanHiT Training Presentation-2dogar99pk67% (3)

- Optimum Propeller Design Using Computerized MethodDokumen10 halamanOptimum Propeller Design Using Computerized MethodPavan KishoreBelum ada peringkat

- TL1 Reference Guide - 323-1059-190.1.r16Dokumen388 halamanTL1 Reference Guide - 323-1059-190.1.r16akrh125Belum ada peringkat

- 60-500 KV High Voltage-Gallery PDFDokumen33 halaman60-500 KV High Voltage-Gallery PDFuzakcilBelum ada peringkat

- Alcatel-Lucent PCX - OXE - BrochureDokumen12 halamanAlcatel-Lucent PCX - OXE - BrochureSharaf MkBelum ada peringkat

- DiagramDokumen2 halamanDiagramIT TelecomBelum ada peringkat

- TC2632en-Ed06 Release Note and Installation Procedure OmniPCX Enterprise R12.3.1 Version M4.501.14Dokumen143 halamanTC2632en-Ed06 Release Note and Installation Procedure OmniPCX Enterprise R12.3.1 Version M4.501.14locuras34100% (1)

- SDH BasicsDokumen46 halamanSDH BasicsmettlemasterBelum ada peringkat

- 03 Alcate 1660SM Sys DesDokumen107 halaman03 Alcate 1660SM Sys Desarranguezjr5991100% (2)

- PCM2 - 3ba23064Dokumen20 halamanPCM2 - 3ba23064Long Nguyen ThanhBelum ada peringkat

- Soft Download Ed02Dokumen5 halamanSoft Download Ed02OmarBelum ada peringkat

- Alcatel Lucent 4028/4029 User Guide ENT PHONES IPTouch-4028-4029Digital Guide 0907 enDokumen2 halamanAlcatel Lucent 4028/4029 User Guide ENT PHONES IPTouch-4028-4029Digital Guide 0907 enjhBelum ada peringkat

- 01-14-MMS CPU Master Cable-02Dokumen9 halaman01-14-MMS CPU Master Cable-02maverick11Belum ada peringkat

- Alcatel-Lucent Omnipcx Enterprise: NGP: New Generation PlatformDokumen11 halamanAlcatel-Lucent Omnipcx Enterprise: NGP: New Generation Platformissa galalBelum ada peringkat

- ALC-SDH Basics and Alcatel SDH System Training Presentation 46 SlideDokumen46 halamanALC-SDH Basics and Alcatel SDH System Training Presentation 46 SlideJesper Ebong75% (4)

- TAC03049-HO05-I2.0-7302 7330 5520 GPON Basic Configuration CEDokumen84 halamanTAC03049-HO05-I2.0-7302 7330 5520 GPON Basic Configuration CEWalid Abdullah MohammedBelum ada peringkat

- Ds 1664 SMDokumen4 halamanDs 1664 SMWumWendelin0% (1)

- SMA1 KDokumen12 halamanSMA1 Kusr1507Belum ada peringkat

- Installation Procedure For Version 4.2.12.00 - Release 4.2Dokumen54 halamanInstallation Procedure For Version 4.2.12.00 - Release 4.2Talhaoui ZakariaBelum ada peringkat

- GPON ONU Optical Transceiver SFF: RTXM167-407Dokumen12 halamanGPON ONU Optical Transceiver SFF: RTXM167-407Elaixa Samussone BiválioBelum ada peringkat

- MX960 RouterDokumen47 halamanMX960 RouterPha LetrungBelum ada peringkat

- 323-1051-190T TL1 Reference Iss 5Dokumen694 halaman323-1051-190T TL1 Reference Iss 5gglaze1Belum ada peringkat

- Tellabs 6300 Managed Transport SystemDokumen78 halamanTellabs 6300 Managed Transport SystemToanBelum ada peringkat

- ALU ManualDokumen886 halamanALU Manualdilligas1234Belum ada peringkat

- Path EthernetDokumen2 halamanPath EthernetGiorgio ValtolinaBelum ada peringkat

- Oxe12.4 DocumentationNote 8AL90920USAH 1 en PDFDokumen14 halamanOxe12.4 DocumentationNote 8AL90920USAH 1 en PDFK Mei.Belum ada peringkat

- OS6450 AOS 6.6.3 R01 Hardware GuideDokumen140 halamanOS6450 AOS 6.6.3 R01 Hardware GuideBesugoBelum ada peringkat

- Eci MSPP Optics ManagementDokumen38 halamanEci MSPP Optics ManagementJoãoLuisEspiritoSantoBelum ada peringkat

- Alcatel-Lucent Omnipcx Enterprise Communication Server: Abc-Ip Logical LinkDokumen46 halamanAlcatel-Lucent Omnipcx Enterprise Communication Server: Abc-Ip Logical Linkjuan50% (2)

- Symmetricom3100 Userguide PDFDokumen200 halamanSymmetricom3100 Userguide PDFX19_fredBelum ada peringkat

- OXO R9.1 Installation ManualDokumen238 halamanOXO R9.1 Installation ManualAlex Pineda0% (1)

- Manual 1662Dokumen123 halamanManual 1662Matt BubaBelum ada peringkat

- TCV039en Ed07Dokumen30 halamanTCV039en Ed07Dhexter VillaBelum ada peringkat

- Es Notes Unit 5Dokumen33 halamanEs Notes Unit 51balamanianBelum ada peringkat

- Tech. Specn. Annexure 2 PLCDokumen17 halamanTech. Specn. Annexure 2 PLCom007fireBelum ada peringkat

- TOYOPUC - Lineup - E - M2063-8E - Seleccion de Modulos + PLCDokumen64 halamanTOYOPUC - Lineup - E - M2063-8E - Seleccion de Modulos + PLCdimarclBelum ada peringkat

- 8011 Service ManualDokumen135 halaman8011 Service Manualserb_71Belum ada peringkat

- Users Manual Mcs-51Dokumen28 halamanUsers Manual Mcs-51Subkhan KholiqiBelum ada peringkat

- Sinclair QL Service Manual - Sinclair ResearchDokumen45 halamanSinclair QL Service Manual - Sinclair Researchabo alasrarBelum ada peringkat

- Solid State Interlocking: CAMTECH/S/2002/SSI/1.0 1Dokumen31 halamanSolid State Interlocking: CAMTECH/S/2002/SSI/1.0 1Vuppala SrinivasBelum ada peringkat

- WM1 Rack-Installation ProcedureDokumen42 halamanWM1 Rack-Installation ProcedureEdmundo Melchor GarcíaBelum ada peringkat

- Calisto 620Dokumen19 halamanCalisto 620Edmundo Melchor GarcíaBelum ada peringkat

- ICAM7000 Hardware Guide Ver1 1Dokumen16 halamanICAM7000 Hardware Guide Ver1 1Edmundo Melchor GarcíaBelum ada peringkat

- WM1 Rack-Installation ProcedureDokumen42 halamanWM1 Rack-Installation ProcedureEdmundo Melchor GarcíaBelum ada peringkat

- 1112 1112i SchematicsDokumen5 halaman1112 1112i SchematicsbansisutharBelum ada peringkat

- (eBook-PDF) - Hacking Cisco RoutersDokumen11 halaman(eBook-PDF) - Hacking Cisco RoutersilecBelum ada peringkat

- Versidrain 150: Green RoofDokumen2 halamanVersidrain 150: Green RoofMichael Tiu TorresBelum ada peringkat

- User Guide For Gateway NV57H / NV55SDokumen1.087 halamanUser Guide For Gateway NV57H / NV55SAudrey D. ChatmanBelum ada peringkat

- Caterpillar 307 CSB Technical SpecificationsDokumen3 halamanCaterpillar 307 CSB Technical Specificationsdale100% (22)

- Auto TurnDokumen156 halamanAuto TurnrrrraduBelum ada peringkat

- User Manual SR 9797HDDokumen47 halamanUser Manual SR 9797HDnavamivbBelum ada peringkat

- Cross Country Sheets1Dokumen2 halamanCross Country Sheets1Anonymous 10cG5eRp8Belum ada peringkat

- w13 - CRM How It Works and Help BusinessDokumen15 halamanw13 - CRM How It Works and Help BusinessYahya Vernanda RamadhaniBelum ada peringkat

- SwiggyDokumen5 halamanSwiggyAravind NarayanBelum ada peringkat

- CIS ch.5 NotesDokumen4 halamanCIS ch.5 NotesClarize R. MabiogBelum ada peringkat

- QMCS 16 - 2 Process CapabilityDokumen27 halamanQMCS 16 - 2 Process CapabilityalegabipachecoBelum ada peringkat

- CV Edin Fatic2Dokumen2 halamanCV Edin Fatic2yousab creator2Belum ada peringkat

- Cyberspace in National Perspective AbstractDokumen5 halamanCyberspace in National Perspective AbstractJiri HofmanBelum ada peringkat

- O & M Manual For JHVR 6000X PDFDokumen234 halamanO & M Manual For JHVR 6000X PDFvenkatesh100% (2)

- EPC Civil06Dokumen6 halamanEPC Civil06MHanif ARBelum ada peringkat

- Coatings For Wind Power - Uk - 010213Dokumen7 halamanCoatings For Wind Power - Uk - 010213King SabiBelum ada peringkat

- Staring Index PagesDokumen7 halamanStaring Index PagesKolte RushikeshBelum ada peringkat

- 01 Rude DoctypeDokumen215 halaman01 Rude DoctypeChristal Rae Tac-anBelum ada peringkat

- 0111 Tension Load Cell Datasheet enDokumen2 halaman0111 Tension Load Cell Datasheet enJosipaBelum ada peringkat

- TH3122 004 PDFDokumen14 halamanTH3122 004 PDFSasa MitrovicBelum ada peringkat