I2C

Diunggah oleh

Jesus Alejandro BastidasHak Cipta

Format Tersedia

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniHak Cipta:

Format Tersedia

I2C

Diunggah oleh

Jesus Alejandro BastidasHak Cipta:

Format Tersedia

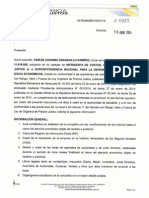

IC

Un ejemplo esquemtico con un maestro (unmicrocontrolador) y tres nodos

esclavos (un ADC, un DAC, y otro microcontrolador) con resistencias pull-up Rp.

IC es un bus de comunicaciones en serie. Su nombre viene de Inter-Integrated

Circuit (Inter-Circuitos Integrados). La versin 1.0 data del ao 1992 y la versin

2.1 del ao 2000, su diseador es Philips. La velocidad es de 100 kbit/s en el

modo estndar, aunque tambin permite velocidades de 3.4 Mbit/s. Es un bus muy

usado en la industria, principalmente para comunicar microcontroladores y

sus perifricosen sistemas integrados (Embedded Systems) y generalizando ms

para comunicar circuitos integrados entre si que normalmente residen en un

mismo circuito impreso.

La principal caracterstica de IC es que utiliza dos lneas para transmitir la

informacin: una para los datos y otra para la seal de reloj. Tambin es necesaria

una tercera lnea, pero esta slo es la referencia (masa). Como suelen

comunicarse circuitos en una misma placa que comparten una misma masa esta

tercera lnea no suele ser necesaria.

Las lneas se llaman:

SDA: datos

SCL: reloj

GND: tierra

Las dos primeras lneas son drenador abierto, por lo que necesitan resistencias

de pull-up.

Los dispositivos conectados al bus IC tienen una direccin nica para cada uno.

Tambin pueden ser maestros o esclavos. El dispositivo maestro inicia la

transferencia de datos y adems genera la seal de reloj, pero no es necesario

que el maestro sea siempre el mismo dispositivo, esta caracterstica se la pueden

ir pasando los dispositivos que tengan esa capacidad. Esta caracterstica hace

que al bus IC se le denomine bus multimaestro.

Las transacciones en el bus I2C tienen este formato:

| start | A7 A6 A5 A4 A3 A2 A1 R/W | ACK | ... DATA ... | ACK | stop | idle |

El bus esta libre cuando SDA y SCL estn en estado lgico alto.

En estado bus libre, cualquier dispositivo puede ocupar el bus IC como

maestro.

El maestro comienza la comunicacin enviando un patrn llamado "start

condition". Esto alerta a los dispositivos esclavos, ponindolos a la espera de

una transaccin.

El maestro se dirige al dispositivo con el que quiere hablar, enviando un

byte que contiene los siete bits (A7-A1) que componen la direccin del

dispositivo esclavo con el que se quiere comunicar, y el octavo bit (A0) de

menor peso se corresponde con la operacin deseada (L/E), lectura=1 (recibir

del esclavo) y escritura=0 (enviar al esclavo).

La direccin enviada es comparada por cada esclavo del bus con su propia

direccin, si ambas coinciden, el esclavo se considera direccionado como

esclavo-transmisor o esclavo-receptor dependiendo del bit R/W.

El esclavo responde enviando un bit de ACK que le indica al dispositivo

maestro que el esclavo reconoce la solicitud y est en condiciones de

comunicarse.

Seguidamente comienza el intercambio de informacin entre los

dispositivos.

El maestro enva la direccin del registro interno del dispositivo que se

desea leer o escribir.

El esclavo responde con otro bit de ACK

Ahora el maestro puede empezar a leer o escribir bytes de datos. Todos los

bytes de datos deben constar de 8 bits, el nmero mximo de bytes que

pueden ser enviados en una transmisin no est restringido, siendo el esclavo

quien fija esta cantidad de acuerdo a sus caractersticas.

Cada byte leido/escrito por el maestro debe ser obligatoriamente

reconocido por un bit de ACK por el dispositivo maestro/esclavo.

Se repiten los 2 pasos anteriores hasta finalizar la comunicacin entre

maestro y esclavo.

Aun cuando el maestro siempre controla el estado de la lnea del reloj, un

esclavo de baja velocidad o que deba detener la transferencia de datos

mientras efecta otra funcin, puede forzar la lnea SCL a nivel bajo. Esto hace

que el maestro entre en un estado de espera, durante el cual, no transmite

informacin esperando a que el esclavo est listo para continuar la

transferencia en el punto donde haba sido detenida.

Cuando la comunicacin finaliza, el maestro transmite una "stop condition"

para dejar libre el bus.

Despus de la "stop condition", es obligatorio para el bus estar idle durante

unos microsegundos.

El cdigo del kernel de Linux para el soporte I2C est separado en varias piezas

lgicas:

I2C chip driver (maneja uno de los chips conectados al bus I2C, tanto si se

comporta como maestro o como esclavo)

I2C bus driver

I2C algorithm driver

I2C core (la parte genrica del subsistema de I2C)

Anda mungkin juga menyukai

- Sca04 TareaDokumen4 halamanSca04 TareaDavid Hoyos100% (1)

- Diodo SnapDokumen3 halamanDiodo SnapMarin Gonthier100% (1)

- Check List - Cargador FrontalDokumen1 halamanCheck List - Cargador FrontalLuis Miguel Mamani Castro0% (1)

- Sistema de Control de Frenos: SectionDokumen178 halamanSistema de Control de Frenos: Sectionnilton villagaray huaranccaBelum ada peringkat

- Providencia 003-2014 Sundde - Criterios ContablesDokumen8 halamanProvidencia 003-2014 Sundde - Criterios ContablesDébora Esther Amado CortésBelum ada peringkat

- Indice DowDokumen15 halamanIndice DowJesus Alejandro BastidasBelum ada peringkat

- REQUISITOSd EPRECIOSJUSTOSDokumen6 halamanREQUISITOSd EPRECIOSJUSTOSJesus Alejandro BastidasBelum ada peringkat

- Ley Orgánica de Precios JustosDokumen8 halamanLey Orgánica de Precios JustosRenbel CelisBelum ada peringkat

- Norma Venezolana, Entorno Urbano y EdificacionesDokumen26 halamanNorma Venezolana, Entorno Urbano y Edificacionesamariandina100% (1)

- Criterios Fijacion de Precios SunnddeDokumen3 halamanCriterios Fijacion de Precios SunnddedavidcorreiaBelum ada peringkat

- Funcionamiento de La IncubadoraDokumen2 halamanFuncionamiento de La IncubadoraJesus Alejandro BastidasBelum ada peringkat

- Ley para Las Personas Con DiscapacidadDokumen2 halamanLey para Las Personas Con DiscapacidadJesus Alejandro BastidasBelum ada peringkat

- Comunicación I2CDokumen5 halamanComunicación I2CJesus Alejandro BastidasBelum ada peringkat

- Capitulo I Contextualizacion de La Tematica El CilantroDokumen8 halamanCapitulo I Contextualizacion de La Tematica El Cilantromaria_gabriela_2049Belum ada peringkat

- Compraventa UsufDokumen3 halamanCompraventa UsufJesus Alejandro BastidasBelum ada peringkat

- El DerechoDokumen41 halamanEl DerechoJesus Alejandro BastidasBelum ada peringkat

- Trabajo FinalDokumen5 halamanTrabajo Finallilia tinco valenzuelaBelum ada peringkat

- Nuevo ILO Mz. 43 Lote. 26 Pampa Inalámbrica ILO Telefono: (51) (053) - 792637 RPM: #953973720/ 0067349 E-Mail: WebDokumen7 halamanNuevo ILO Mz. 43 Lote. 26 Pampa Inalámbrica ILO Telefono: (51) (053) - 792637 RPM: #953973720/ 0067349 E-Mail: WebTonyRiverosBecerraBelum ada peringkat

- Historia de Las Redes en BoliviaDokumen2 halamanHistoria de Las Redes en BoliviaElvin Velasquez CareagaBelum ada peringkat

- Arduino Vs PicDokumen10 halamanArduino Vs PicClaudia Brandana100% (1)

- Kits MantenimientoDokumen28 halamanKits MantenimientoJean MoralesBelum ada peringkat

- MID 128 SID 232 5 V Alimentación para El SensorDokumen3 halamanMID 128 SID 232 5 V Alimentación para El SensoredwardBelum ada peringkat

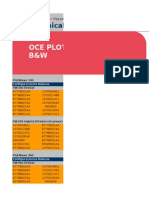

- Lista de Precios 2015-04 Oce 2Dokumen81 halamanLista de Precios 2015-04 Oce 2Marco Antonio Medina FigueroaBelum ada peringkat

- Dimensionamiento de Dispositivos II ParcialDokumen9 halamanDimensionamiento de Dispositivos II ParcialAlexander Valencia100% (2)

- Linea Del TiempoDokumen9 halamanLinea Del TiempoivancitoBelum ada peringkat

- Guia 18 - Configuración Red DeviceNet - ABDokumen12 halamanGuia 18 - Configuración Red DeviceNet - ABBenjamín LabbéBelum ada peringkat

- Lab 01elec IndDokumen12 halamanLab 01elec IndmanuelBelum ada peringkat

- Pinch Actuador NeumaticoDokumen1 halamanPinch Actuador NeumaticoDaniela CeciliaBelum ada peringkat

- Correctivo PLM-20220126-00000013 CAD0016 Dorada CentroDokumen9 halamanCorrectivo PLM-20220126-00000013 CAD0016 Dorada CentroLuswing Raul Rueda HernandezBelum ada peringkat

- Ficha Jac 2022 1083Dokumen1 halamanFicha Jac 2022 1083Elleo RoldanBelum ada peringkat

- Asintec HioposDokumen3 halamanAsintec HioposAlberto AvilaBelum ada peringkat

- Practica No 3 Motor CD DerivacionDokumen3 halamanPractica No 3 Motor CD DerivacionErickGarciaBelum ada peringkat

- Actas Er EmporioDokumen24 halamanActas Er EmporioMel GarcíaBelum ada peringkat

- Cuestiones Informatica 1º EsoDokumen3 halamanCuestiones Informatica 1º Esoperroviejo80Belum ada peringkat

- Brochure de Montacarga 5 A 10 Ton HeliDokumen4 halamanBrochure de Montacarga 5 A 10 Ton HeliAlonso Fernando Magallanes Palomino100% (2)

- Easy VarDokumen2 halamanEasy VarCharly SotoBelum ada peringkat

- Procedimiento para Operación de Perforación y VoladuraDokumen10 halamanProcedimiento para Operación de Perforación y VoladuraFreiser Ramos miñanoBelum ada peringkat

- Tipos de ComputadorasDokumen4 halamanTipos de ComputadorasCESAR HERNANDEZBelum ada peringkat

- Manual SmartTVDokumen48 halamanManual SmartTVLuis Torres100% (4)

- Recordelectric MotoresytablerosDokumen20 halamanRecordelectric MotoresytablerosLucho Fdo Casanova100% (1)

- Costos de Servicio de Mantto de Buses y CamionesDokumen23 halamanCostos de Servicio de Mantto de Buses y CamionesWaldir Rodriguez JuarezBelum ada peringkat

- Diagrama de Conexión UPS 9PX10KSP KVA 2021Dokumen2 halamanDiagrama de Conexión UPS 9PX10KSP KVA 2021BiomedicaBelum ada peringkat