Cascode Theory

Diunggah oleh

Giap LuongHak Cipta

Format Tersedia

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniHak Cipta:

Format Tersedia

Cascode Theory

Diunggah oleh

Giap LuongHak Cipta:

Format Tersedia

A 33-dBm 1.

9-GHz Silicon-on-Insulator CMOS Stacked-FET

Power Amplifier

Sataporn Pornpromlikit1, Jinho Jeong2, Calogero D. Presti1, Antonino Scuderi3, and Peter M. Asbeck1

1

University of California, San Diego, La Jolla, CA 92093, USA

2

Kwangwoon University, Seoul 139-701, Korea

STMicroelectronics s.r.l., Stradale Primasole 50, 95121 Catania, Italia

the drain of the top FET is used to allow voltage swings at the

gates of the stacked devices together with appropriate

capacitive loading of the gate nodes. Recently in [1], a 20dBm linear PA was designed in Silicon-on-Sapphire (SOS)

CMOS process using stacked-FET structure without a

feedback resistor.

Abstract A single-stage stacked-FET power amplifier (PA) is

demonstrated using a 0.28-m silicon-on-insulator (SOI) CMOS

technology. To overcome the low breakdown voltage limit of

MOSFETs, a stacked-FET structure is employed, where four

transistors are connected in series so that their output voltage

swings are added in phase. The stacked-FET PA has been

designed to withstand up to 9 V of supply voltage before reaching

its breakdown limit. The measurement results show that, with a

6.5-V supply, the PA achieves a small-signal gain of 13.2 dB, a

saturated output power of 33 dBm, and a maximum poweradded-efficiency (PAE) of 47% at 1.9 GHz. This is the first

reported stacked-FET PA in submicron SOI CMOS technology

that delivers multi-Watt output power in the GHz range. It also

maintains high power efficiency over a wide range of supply

voltages.

Index Terms Stacked-FET, stacked transistors, silicon-oninsulator, SOI, CMOS, RF power amplifier.

Vg4

C4

C3

I. INTRODUCTION

Due to its low cost and high-integration capability, CMOS has

become a technology of choice for research on single-chip

radio transceivers in recent years. Among other advantages,

CMOS PAs offer the potential of reducing complexity and

cost by enabling the combination of a complete transceiver

and digital baseband circuitry on the same chip. However,

designing a high-performance RF PA on CMOS remains a

challenging task, especially with the on-going technology

scaling to deep submicron dimensions [1]-[5].

The critical issues for CMOS PA design are the low

breakdown voltage and high knee voltage of the device, which

limit the drain voltage swing [5]. To obtain high output

power, a typical approach is to increase the device size for

higher drain current swing, resulting in lower input

impedance, and thus, more difficult input matching design.

More severely, the required output impedance transformation

ratio from the original load impedance to 50 becomes too

high, especially for Watt-level output power, resulting in high

loss in the output matching network, and thus, low efficiency.

Several approaches have been proposed to overcome these

limits of CMOS transistors, including cascode structures [2],

the distributed active transformer [5] and stacked-FET PAs

[1], [6], [7]. In [7], high-power/high-voltage PAs were

proposed, where several transistors are connected in series to

achieve high output voltage swing. A feedback resistor from

978-1-4244-2804-5/09/$25.00 2009 IEEE

C2

Vg3

Vg2

OUT

4Vm

3Vm

2Vm

Vm

4Ropt

Zs4= 3Ropt

Zs3= 2Ropt

Zs2= Ropt = Vm/Im

IN

Im

Fig. 1. Stacked-FET PA basic structure.

This paper reports a single-stage stacked-FET PA design in

a 0.28-m SOI CMOS technology, using an approach

extended from [1]. The PA has been designed to demonstrate

a reliable operation with the supply voltage as large as 9 V

while delivering multi-Watt output power with high power

efficiency (PAE > 40%). The SOI CMOS technology is

particularly attractive for the stacked-FET technique due to its

lack of body effect and relatively small parasitic junction

capacitance. By contrast, in conventional CMOS, source-body

capacitance and body effect progressively reduce gain of the

transistors in the upper sections of the stack.

533

IMS 2009

For a high-frequency design, however, the reactive

component of the load impedance (Zs2-Zs4) due to Cgs

becomes significant and the gain is degraded somewhat as

implied by (2). Also, the four transistors will see slightly

different drain currents due to currents leaking out through

Cgs, resulting in more difficult waveform shaping to achieve

high-efficiency operation on all transistors simultaneously.

The high-frequency performance of stacked-FET PAs clearly

improves with the advanced higher-Ft scaled-down CMOS

technology.

II. STACKED-FET DESIGN CONCEPT

The stacked-FET structure used in this work is shown in

Fig. 1. The circuit is composed of a common-source input

transistor and three common-gate stacked transistors

connected in series so that their output swings are added in

phase. Unlike in a cascode configuration where the gate of the

common-gate transistor is RF-grounded, a relatively small

external gate capacitance (C2, C3, and C4) is introduced to

allow an RF swing at the gate of each stacked transistor. The

external gate capacitance and the gate-to-source capacitance

(Cgs) of each stacked transistor form a capacitive voltage

divider to produce the proper in-phase voltage swing at the

gate and drain.

TL5

Rb4

Ci

Cgs

vgs

gmvgs

ro

VG4

RL

C4

it

vt

OUT

TL6

m4

Cm4

VG3

Zsi

C3

Rg3

Rb2

Cm5

Rg2

Cm1

Rb1

m2

Rf

RL

Cf

TL1

As shown in a simplified model in Fig. 2, assuming ro is

large, the source input impedance Zsi of a stacked transistor is

influenced by the value of the external gate capacitor relative

to its gate-source capacitance, according to:

TL2

Cm2

IN

m1

Rg1

VG1

C gs

Z si = 1 +

Ci

GND

= Bond pad

Fig. 3. Circuit schematic of the single-stage stacked-FET PA.

(1)

III. STACKED-FET PA DESIGN

A single-stage stacked-FET deep class-AB PA was

designed to operate at 1.9 GHz using STMicroelectronics

0.28-m SOI CMOS process. The overall circuit diagram is

shown in Fig. 3. Four transistors are stacked in series, based

on the design approach presented in the previous section. To

ensure a safe operation, the drain-to-source voltage of each

transistor is limited to 4.5 V (Vds-breakdown = 5 V), allowing a

maximum voltage swing of 18 V at the top drain node with a

9-V drain bias. The external gate capacitances (C2-C4) are 9

pF, 2.6 pF, and 2 pF, respectively. For flexibility, the gate bias

voltages of each stacked device are implemented by an offchip resistive voltage divider and applied through a 1-k onchip resistors.

Special consideration is needed when setting the gate bias

voltages of the stacked devices (VG2 VG4) for such a highvoltage design. The DC drain current is determined by the

bottom device (m1) and increases with the RF power level.

Since the gate bias voltages are fixed by the resistive voltage

divider, the source bias voltages of the stacked devices must

The small-signal voltage gain of the PA can be derived as:

sC gs 4

1 +

g m4

TL7

VG2

C2

g m1 R L

sC gs 2 sC gs 3

1 +

1 +

g m 2

g m3

g m1 R L for f o << Ft

TL8

m3

RF In

Fig. 2. Effect of an external gate capacitance on a stacked FETs

source input impedance.

Av =

TL4

TL3

Rg4

Rb3

1

1

g // sC

gs

m

C gs 1

1 +

for f o << Ft

C i g m

Cm3

VDD

(2)

For a low frequency design where the carrier frequency (fo)

is much lower than the cutoff frequency of the device (Ft), Zs2,

Zs3, and Zs4 are approximately purely-resistive and all four

devices in series share the same constant current swing (Im).

The values of external capacitors (C2-C4) should be set such

that Zs2, Zs3, and Zs4 are Ropt, 2Ropt, and 3Ropt, respectively,

and the optimum output load impedance is 4Ropt. This ensures

that each transistor has the same drain-source, drain-gate, and

gate-source voltage swings while the absolute voltage swings

with respect to ground increase as one moves up the ladder.

534

inductor (Qind = 12), the drain efficiency factor due to

matching network loss can be estimated as:

Drain Voltage (V)

decrease to accommodate higher DC current, resulting in an

early breakdown in the topmost device and an early

compression in the bottom device. A simple solution is to

offset the gate bias voltages of the stacked devices properly so

that all four devices have equal voltage headroom close to the

saturation point, thereby improving operation.

m =

Vd4

10

Vd3

Vd2

Vd1

0

0.0

0.2

0.4

0.6

0.8

1.0

1.2

Gate Voltage (V)

Time (nsec)

15

10

Vg4

Vg3

Body-Source

connection

G4

Vg2

G3

G2

0.0

0.2

0.4

0.6

GND Plane

G1

Top Drain

Vg1

-5

(3)

The on-chip output matching network for a conventional

common-source design delivering the same output power

level without device stacking (Qm = 8.28) would yield a drain

efficiency factor of only 59.2%.

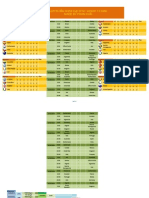

Fig. 4 shows the simulated drain, gate, drain-to-source,

drain-to-gate voltage waveforms and load lines of each FET at

the saturating output power under a 9-V supply, illustrating

that Vgs and Vds swings for the different devices are close to

one another and within the breakdown limit.

20

15

Qind

86.8%.

Qind + Qm

0.8

1.0

G1

G2

G3

G4

1.2

Time (nsec)

Top Drain

Unit cell

Voltage (V)

7

5

G1

G2

G3

G4

Vds

3

1

Top Drain

-1

Vdg

-3

0.0

0.2

0.4

0.6

0.8

1.0

1.2

Fig. 5. Layout diagram of stacked-FET unit cells and interconnects.

Drain Current

(A) (A)

Drain

Current

Time (nsec)

1.5

m1

The partial layout diagram of unit cells and interconnects is

illustrated in Fig. 5. One metal layer is dedicated as a ground

plane to minimize on-chip ground inductance. A unit cell is

composed of four gate fingers with a shared silicon active

area, thus effectively producing four stacked FETs. Each

finger has its body directly tied to its source. In this way, the

body terminals float in phase with the respective sources, thus

avoiding the breakdown of the drain junction as well. The

drain of the top finger is then connected to one of the large

drain lines, which flow from the input side to the output side

of the chip in parallel with the gate distribution lines. On the

other hand, the source of the bottom finger is connected

directly to the ground plane through multiple vias. This

distributed layout approach results in a highly compact layout

with improved on-chip heat distribution and minimized

parasitic components within the structure.

A microphotograph of the fabricated PA is shown in Fig. 6,

occupying an area of 0.43 mm x 1.56 mm. The chip is made

narrow to minimize drain line inductance and resistance, as

well as to minimize the phase difference between the unit

amplifier cells closer to the input side and the ones closer to

the output side.

m2

1.0

m3

0.5

m4

0.0

0

Drain-to-source Voltage

(V)

Drain-to-Source

Voltage

(V)

Fig. 4. Simulated drain, gate, drain-to-source, drain-to-gate voltage

waveforms and load lines of each FET at the saturating output power

and a supply voltage of 9 V.

Each transistor has the total gate width of 5 mm, so the total

gate width in the amplifier is 20 mm. The optimum output

load impedance (4Ropt in Fig. 1) is 11.5 , which lies in a

convenient range to match to 50 over broad bandwidth. The

input impedance is 17.5 , a comparatively large value

corresponding to that of a single 5-mm transistor. The input

and output matching circuits are implemented off-chip to

allow opportunities for investigation.

One of the main advantages in using the stack-FET

technique is the much lower impedance transformation ratio

relative to the conventional approach, which makes a low-loss

on-chip matching network possible. As an example, if the

output matching (Qm = 1.83) is done on-chip with an on-chip

535

In

GND

In

GND

GND

In

GND

In

Gate capacitors

VG2

VG3

Distributed stackedstacked-FET unit cells

VG4

Out

GND

Out

GND

GND

dB with a fairly flat gain roll-off. At the 1-dB compression

point, the output power is 31.8 dBm with 46.7% PAE. A

maximum PAE as high as 47% is achieved at a 32.1-dBm

output power, whereas the saturated output power reaches 33

dBm. High power efficiency (PAE > 40%) is also maintained

over a wide range of supply voltages (4.5 V - 9 V) as shown

in Fig. 9. To test its robustness under a high supply voltage as

designed, the PA was continuously operated at the peak

output power, under a 9-V supply. No performance

degradation was observed after 1 week.

GND

Out

GND

GND

Out

GND

Fig. 6. Microphotograph of the fabricated stacked-FET PA.

V. CONCLUSION

The test chip was mounted chip-on-board on a coplanar

waveguide PCB with substrate relative dielectric constant of

3.38. Eleven bond pads were used for wire-bonding to the

PCB ground. The on-board drain bias circuit included a

quarter-wave long line (TL4) with a 9.1-pF shunt capacitor

(Cm3) to ground, providing a 2nd harmonic termination. A

high-pass L-match section, consisted of a series capacitor

(Cm4) and a short stub (TL7), was used to transform the

external 50- load to the optimum load.

A single-stage stacked-FET class-AB PA has been

demonstrated at 1.9 GHz using a 0.28-m SOI CMOS

technology. To solve the low breakdown voltage problem, the

stacked-FET technique is employed to allow the use of higher

supply voltage, resulting in a much lower impedance

transformation ratio. The implemented PA achieves 47%

maximum PAE and delivers 33-dBm saturated output power

with a 6.5-V supply. In as much as its performance improves

with higher-Ft devices, the stacked-FET technique is clearly

an attractive solution for designing high-efficiency PAs in

advanced deep-submicron CMOS technology where the

breakdown limit is much lower than the standard supply

voltage.

50

45

40

35

30

25

20

15

10

5

0

0.6

PAE (%)

0.5

Gain (dB)

DC Current (A)

0.4

0.3

0.2

DC Current (A)

Gain (dB) and PAE (%)

IV. MEASUREMENTS

ACKNOWLEDGEMENT

The authors would like to thank STMicroelectronics for the

chip fabrication and support.

0.1

0

0

10

20

30

40

REFERENCES

Output power (dBm)

[1] J. Jeong, S. Pornpromlikit, P. M. Asbeck, and D. Kelly, A 20

dBm Linear RF Power Amplifier Using Stacked Silicon-onSapphire MOSFETs, IEEE Microwave and Wireless

Components Letters, vol. 16, no. 12, pp. 684-686, Dec. 2006.

[2] T. Sowlati, and D. M. W. Leenaerts, A 2.4-GHz 0.18-um

CMOS Self-Biased Cascode Power Amplifier, IEEE J. SolidState Circuits, vol. 38, no. 82, pp. 1318-1324, Aug. 2003.

[3] N. Srirattana, P. Sen, H. M. Park, C. H. Lee, P. E. Allen, and

J. Laskar, Linear RF CMOS Power Amplifier with Improved

Efficiency and Linearity in Wide Power Levels, in 2005 IEEE

RFIC Symp., pp. 251-254, June 2005.

[4] Y. Ding, and R. Harjani, A High-Efficiency CMOS +22-dBm

Linear Power Amplifier, IEEE J. Solid-State Circuits, vol. 40,

no. 9, pp. 1895-1900, Sep. 2005.

[5] I. Aoki, S. D. Kee, D. B. Rutledge, and A. Hajimiri, Fully

Integrated CMOS Power Amplifier Design Using the

Distributed Active-Transformer Architecture, IEEE J. SolidState Circuits, vol. 37, no. 3, pp. 371-383, Mar. 2002.

[6] J. G. McRory, G. G. Rabjohn, and R. H. Johnston, Transformer

Coupled Stacked FET Power Amplifiers, IEEE J. Solid-State

Circuits, vol. 34, no. 2, pp. 157-161, Feb. 1999.

[7] A. K. Ezzeddine, and H. C. Huang, The High Voltage/High

Power FET, in 2003 IEEE RFIC Symp, pp. 215-218, June

2003.

50

45

40

35

30

25

20

15

10

5

0

40

35

30

25

PAE (%)

Gain (dB)

20

Output Power (dBm)

15

10

5

Output Power (dBm)

Gain (dB) and PAE (%)

Fig. 8. Measured gain, PAE, and DC current as a function of output

power with a CW input at 1.9 GHz.

0

4

Supply Voltage (V)

Fig. 9. Measured gain, PAE, and output power as a function of

supply voltage with a 20.5-dBm CW input at 1.9 GHz.

The PA was tested under a continuous-wave (CW) input at

1.9 GHz and a supply voltage of 6.5 V. The measurement

results are illustrated in Fig. 8. The small-signal gain is 13.2

536

Anda mungkin juga menyukai

- Stmicroelectronics Deep Sub-Micron Processes 120Nm, 90Nm, 65 NM CmosDokumen37 halamanStmicroelectronics Deep Sub-Micron Processes 120Nm, 90Nm, 65 NM CmosGiap LuongBelum ada peringkat

- Impedance PsourceDokumen3 halamanImpedance PsourceGiap LuongBelum ada peringkat

- Activity 6. BJT Current MirrorDokumen6 halamanActivity 6. BJT Current MirrorGiap LuongBelum ada peringkat

- Switch Mode RF Amplifier 02Dokumen5 halamanSwitch Mode RF Amplifier 02Henry TseBelum ada peringkat

- 40901817Dokumen3 halaman40901817Giap LuongBelum ada peringkat

- Untitled 1Dokumen1 halamanUntitled 1Giap LuongBelum ada peringkat

- Lich Thi Dau WC2014 Ver 1.0 - Phan KhaiDokumen7 halamanLich Thi Dau WC2014 Ver 1.0 - Phan KhaiGiap LuongBelum ada peringkat

- Led Matrix 2Dokumen24 halamanLed Matrix 2Giap LuongBelum ada peringkat

- PSpice CaptureGuideOrCADDokumen374 halamanPSpice CaptureGuideOrCADVăn LinBelum ada peringkat

- Packet Tracer - RouterDokumen1 halamanPacket Tracer - RouterGiap LuongBelum ada peringkat

- Part 3 - Transport-LayerDokumen43 halamanPart 3 - Transport-LayerGiap LuongBelum ada peringkat

- ElectronicsDokumen2 halamanElectronicsGiap LuongBelum ada peringkat

- Mau CV Bang Tieng Anh CurDokumen8 halamanMau CV Bang Tieng Anh CurantiloveBelum ada peringkat

- Mpeg Audio Datafile Format SpecificationDokumen17 halamanMpeg Audio Datafile Format SpecificationGiap LuongBelum ada peringkat

- Optimal Image Feature Set For Detecting Lung Nodules On Chest X-Ray ImagesDokumen6 halamanOptimal Image Feature Set For Detecting Lung Nodules On Chest X-Ray ImagesGiap LuongBelum ada peringkat

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeDari EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifePenilaian: 4 dari 5 bintang4/5 (5794)

- Shoe Dog: A Memoir by the Creator of NikeDari EverandShoe Dog: A Memoir by the Creator of NikePenilaian: 4.5 dari 5 bintang4.5/5 (537)

- The Yellow House: A Memoir (2019 National Book Award Winner)Dari EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Penilaian: 4 dari 5 bintang4/5 (98)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceDari EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RacePenilaian: 4 dari 5 bintang4/5 (895)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersDari EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersPenilaian: 4.5 dari 5 bintang4.5/5 (344)

- The Little Book of Hygge: Danish Secrets to Happy LivingDari EverandThe Little Book of Hygge: Danish Secrets to Happy LivingPenilaian: 3.5 dari 5 bintang3.5/5 (399)

- Grit: The Power of Passion and PerseveranceDari EverandGrit: The Power of Passion and PerseverancePenilaian: 4 dari 5 bintang4/5 (588)

- The Emperor of All Maladies: A Biography of CancerDari EverandThe Emperor of All Maladies: A Biography of CancerPenilaian: 4.5 dari 5 bintang4.5/5 (271)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaDari EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaPenilaian: 4.5 dari 5 bintang4.5/5 (266)

- Never Split the Difference: Negotiating As If Your Life Depended On ItDari EverandNever Split the Difference: Negotiating As If Your Life Depended On ItPenilaian: 4.5 dari 5 bintang4.5/5 (838)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryDari EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryPenilaian: 3.5 dari 5 bintang3.5/5 (231)

- On Fire: The (Burning) Case for a Green New DealDari EverandOn Fire: The (Burning) Case for a Green New DealPenilaian: 4 dari 5 bintang4/5 (73)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureDari EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FuturePenilaian: 4.5 dari 5 bintang4.5/5 (474)

- Team of Rivals: The Political Genius of Abraham LincolnDari EverandTeam of Rivals: The Political Genius of Abraham LincolnPenilaian: 4.5 dari 5 bintang4.5/5 (234)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyDari EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyPenilaian: 3.5 dari 5 bintang3.5/5 (2259)

- Rise of ISIS: A Threat We Can't IgnoreDari EverandRise of ISIS: A Threat We Can't IgnorePenilaian: 3.5 dari 5 bintang3.5/5 (137)

- The Unwinding: An Inner History of the New AmericaDari EverandThe Unwinding: An Inner History of the New AmericaPenilaian: 4 dari 5 bintang4/5 (45)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreDari EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You ArePenilaian: 4 dari 5 bintang4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Dari EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Penilaian: 4.5 dari 5 bintang4.5/5 (120)

- Her Body and Other Parties: StoriesDari EverandHer Body and Other Parties: StoriesPenilaian: 4 dari 5 bintang4/5 (821)

- Key Issues in RF and RFIC Circuit Design PDFDokumen405 halamanKey Issues in RF and RFIC Circuit Design PDFDorothy KirbyBelum ada peringkat

- Pana USDokumen52 halamanPana USflorin100% (1)

- GSR III EmtlDokumen30 halamanGSR III EmtlkrishnaBelum ada peringkat

- Solid State Radio Engineering (Krauss 1980)Dokumen55 halamanSolid State Radio Engineering (Krauss 1980)sebastian nasiBelum ada peringkat

- A 13.56 MHZ Wireless Power Transfer System Without Impedance Matching NetworksDokumen4 halamanA 13.56 MHZ Wireless Power Transfer System Without Impedance Matching NetworksA.G. MonteroBelum ada peringkat

- CST Korean User meeting-KAIST-plasmaDokumen15 halamanCST Korean User meeting-KAIST-plasmashochstBelum ada peringkat

- ME450 Fall2008 Final Report - Team 23 - PECVD Desktop ReactorDokumen57 halamanME450 Fall2008 Final Report - Team 23 - PECVD Desktop ReactorAkhmad JailaniBelum ada peringkat

- Maximally-Flat Filters in Waveguide PDFDokumen30 halamanMaximally-Flat Filters in Waveguide PDFagmnm1962Belum ada peringkat

- RF - CH05 - Impedance - Matching - 2011-12 - HRC - EE - NCKU 0106 PDFDokumen25 halamanRF - CH05 - Impedance - Matching - 2011-12 - HRC - EE - NCKU 0106 PDFjgalindesBelum ada peringkat

- 2 Marks PDFDokumen5 halaman2 Marks PDFBala913Belum ada peringkat

- RF 2000Dokumen4 halamanRF 2000Sabri Yılmaz100% (1)

- Introduction and Historical Overview of Power Line Communications (PLC)Dokumen62 halamanIntroduction and Historical Overview of Power Line Communications (PLC)Younis FadlBelum ada peringkat

- Ec8651 TLRF Msajce QN BankDokumen12 halamanEc8651 TLRF Msajce QN BankPriyadharshini S VenkateshBelum ada peringkat

- ACOM 1000 Linear Amplifier Operating ManualDokumen26 halamanACOM 1000 Linear Amplifier Operating ManualPaul BryanBelum ada peringkat

- Master Saarinen Tapio 2019Dokumen67 halamanMaster Saarinen Tapio 2019suresh sangamBelum ada peringkat

- Solid State Guitar AmplifiersDokumen419 halamanSolid State Guitar AmplifiersRica TheSick100% (9)

- Optimal Operation of Paralleled Power Transformers: March 2008Dokumen6 halamanOptimal Operation of Paralleled Power Transformers: March 2008Akash VermaBelum ada peringkat

- TM 11 1520 221 20Dokumen162 halamanTM 11 1520 221 20Tod A. WulffBelum ada peringkat

- Doherty Power Amplifier For 5G SystemsDokumen25 halamanDoherty Power Amplifier For 5G SystemsАлексей КоротковBelum ada peringkat

- Reynolds03 JSSC Vol38no9 Pp1555-1560 ADirectConvReceiverICforWCDMAMobileSystemsDokumen6 halamanReynolds03 JSSC Vol38no9 Pp1555-1560 ADirectConvReceiverICforWCDMAMobileSystemsTom BlattnerBelum ada peringkat

- W2DU - Analisys Coaxial DipoleDokumen14 halamanW2DU - Analisys Coaxial DipolebyponsBelum ada peringkat

- Super Elex 4Dokumen10 halamanSuper Elex 4Charles Adrian CBelum ada peringkat

- Lab Manual AVSDokumen44 halamanLab Manual AVSKarishma Sav33% (3)

- Power Line Carrier Communication (PLCC) : Submitted By: Er. Vishwesh Kumar SharmaDokumen24 halamanPower Line Carrier Communication (PLCC) : Submitted By: Er. Vishwesh Kumar SharmaNeelakandan MasilamaniBelum ada peringkat

- Broadband Discone Antenna KIT: Ramsey Electronics Model No. DA25Dokumen20 halamanBroadband Discone Antenna KIT: Ramsey Electronics Model No. DA25Mitchell DanielsBelum ada peringkat

- The DBJ-2: A Portable VHF-UHF Roll-Up J-Pole Antenna For ARESDokumen3 halamanThe DBJ-2: A Portable VHF-UHF Roll-Up J-Pole Antenna For ARESIan AlvesBelum ada peringkat

- Microwave Amlifier Design Azrar PDFDokumen48 halamanMicrowave Amlifier Design Azrar PDFZakaria MounirBelum ada peringkat

- SWR Analyzer User Guide v4.00Dokumen47 halamanSWR Analyzer User Guide v4.00guevaragusBelum ada peringkat

- Antenna Tuning For WCDMA RF Front End: Reema SidhwaniDokumen70 halamanAntenna Tuning For WCDMA RF Front End: Reema SidhwaniRomualdo Begale PrudêncioBelum ada peringkat

- Design of A Low Noise Amplifier Using AWDokumen5 halamanDesign of A Low Noise Amplifier Using AWDũng ĐặngBelum ada peringkat