Methods For Implementation of Feedback Loops in High Speed FPGA Applications

Diunggah oleh

mmorsy1981Judul Asli

Hak Cipta

Format Tersedia

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniHak Cipta:

Format Tersedia

Methods For Implementation of Feedback Loops in High Speed FPGA Applications

Diunggah oleh

mmorsy1981Hak Cipta:

Format Tersedia

Methods for Implementation of Feedback Loops in

High Speed FPGA Applications

Nima Safari, Volker Mauer, Shahin Gheitanchi

Wireless SSE

Altera Corporation

High Wycombe, UK

nsafari@altera.com, vmauer@altera.com, sgheitan@altera.com

AbstractIn many Digital Signal Processing (DSP) modules,

increasing the number of pipelining stages to achieve higher

throughput may break the module functionality if a feedbackloop exists in the algorithm. This paper addresses a novel

algorithmic-level technique to modify implementation of

feedback loops to allow deeper pipelining while sustaining the

module functionality. An equivalent model for a first-order

Infinite Impulse Response (IIR) filter can be obtained by a

cascade model including a higher order repeated-pole IIR filter

followed by a Finite Impulse Response (FIR) filter. The order of

the repeated-pole IIR filters, and hence the number of pipelining

stages can be chosen to meet the Fmax requirements. The model

is further developed to include a class of mathematical recursive

functions to cover many different DSP applications.

KeywordsFPGA, Fmax , IIR filters, feedback loop, recursive

functions, Pipelining.

I. INTRODUCTION

FPGAs are required to provide higher throughput to

support high sampling rate applications. Digital Front End

(DFE) modules in the next generation of wireless/mobile

communication systems needs to support 100 MHz bandwidth

for multi-standard multi-carrier applications. This bandwidth

requirement obligates at least 5x sampling rate to be able to

run DFE modules such as Crest Factor Reduction (CFR),

and/or Digital Predistortion (DPD). Increasing the pipelining

stages is a common approach to meet the timing constraints

throughout the digital design in FPGAs. However, modules

containing feedback loops are particularly challenging. Since

in high bandwidth feedback loops, all the closed loop

calculations should be performed in a sample period,

increasing the number of pipelining stages in the loop to

achieve higher performance can lead to functionality failure.

Feedback loops are widely used in DSP applications such as

IIR filters, Phase-Locked Loops (PLLs), Proportional-Integral

(PI) controllers, carrier-phase trackers, Automatic Gain

Controllers (AGCs), Max and Min functions, etc. Therefore,

modifying the implementation of feedback-loops to insert

arbitrary pipeline registers while sustaining the loop

functionality, may lead to a significant breakthrough achieving

desired Fmax. Maximum throughput a device can run without

violating timing constraints is usually defined as Fmax.

One solution to resolve the problem stated above is to use

FIR approximation of the recursive function ([1]-[2]) to

remove the recursion and therefore pipelining the design. This

solution is an approximation and may lead to significant

resource usage increase.

The other alternative solution is signal decimation. This

solution is applicable if the sample rate is lower than the clock

rate, so that multi-cycles can be used to finish the feedback

chain computations [3].

In [4]-[5], a technique called Scattered-Lookahead was

presented for IIR filter pipelining by adding extra poles and

zeros to the original filter. However, the technique is only

limited to IIR filters.

In this paper, we propose a mathematically equivalent

system solution that the number of pipelining stages can be

arbitrarily chosen to meet the

requirement. The modified

structure preserves the stability conditions of the original IIR

filter, i.e. if the original IIR filter is stable the pipelined

structure will also be stable.

The method was originally developed to resolve the IIR

filters pipelining problems; however the algorithm is further

generalized to cover recursive functions satisfying associative,

distributive and commutative properties. This generalization is

particularly important as the method can further be deployed

for many math functions such as max, min, norm, multiply,

etc.

It should be pointed out that the great benefit of the new

structure is obtained at the expense of higher resource usage.

As discussed later, the logic usage increases linearly by the

number of pipelining stages required to hit the desired F

.

The increase in resource count is insignificant when compared

against overall design utilization.

The rest of the paper is organized as follows: section 2

states the problem of feedback loops in DSP applications. The

proposed solution to meet the timing constraints in IIR filters

and generalized recursive functions are presented in section 3.

In section 4, we give Crest Factor Reduction (CFR) example

to illustrate the benefit of using the proposed architecture for

high speed DSP applications in FPGAs. Finally, conclusions

are drawn in section 5.

II. FEEDBACK-LOOPS IN DSP APPLICATIONS

Single-cycle feedback loops are used in many DSP

applications. An accumulator or a single-pole IIR filter can be

represented by:

(1)

Z-transform of the system impulse response is then given by :

(2)

Running for the sample rate equal to the system clock, the

module should finish the closed-loop computations in one

clock cycle. In the accumulator with the transfer function given

above, the closed-loop computation includes one multiplication

and one addition (or subtraction). These operations typically

require several pipeline stages when implemented in high

applications. However, if the sample rate is the same as

the clock rate, only one register stage can be inserted without

breaking the functionality of this loop. Therefore it is highly

desirable to have a method to let designers insert pipelining

registers in single-cycle IIR filters to achieve the desired speed,

and at the same time sustain the loop functionality.

III.

higher

. It should be mentioned that the new structure

demands for more logic consumption. In fact the logic usage

increases linearly with the number of extra pipelining registers

inserted in the feedback loop. However, since the feedback

structures only account for a small portion of the overall

design, increasing the size of this structure does not have a

significant impact on the overall size.

Stability is always a concern when using IIR filters. It is worth

mentioning that the proposed model is stable if the original

IIR filter is stable, as no extra different poles are added in the

transfer function.

The other advantage of the proposed model is that it is

mathematically-equivalent to the original model and therefore,

the outputs of the original and the proposed models are

identical. This technique can be generalized to construct n-th

order IIR filters, as any IIR filter of order n can be

reconstructed using cascade/parallel realization of first order

IIR filters.

PIPELINED FEEDBACK-LOOPS

In this section, we first focus on IIR filters and modify the

transfer function of the filter to reach an equivalent

mathematical expression with more delays in the feedback

loop. Later we generalize the technique to cover more

operations inside the feedback loop to pipeline a number of

recursive functions.

A.

IIR Filters

The difference of two

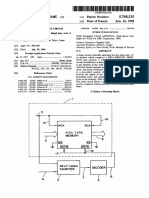

Figure 1 The equivalent IIR filter implementation for loop

pipelining.

power can be factorized as:

(3)

1,

Repeating the factorization for

1

, we have:

(4)

Thus, the transfer function of the single-cycle accumulator in

(2) can be rewritten as follows:

B.

Generalized Technique for Recursive

Functions

The technique proposed earlier for IIR filters is a special case

of a more generalized architecture. Here, we show that the

technique can be generalized to cover many different recursive

functions. In fact the summation operation used in

accumulators can be replaced by an operation .

Claim: If satisfies the following properties:

1.

2.

3.

Commutative :

Associative:

Factorization:

,

, /

(5)

The equivalent model is a higher order IIR filter that can be

implemented using a cascade of multi-cycle IIR filter followed

by a FIR filter. The multi-cycle IIR filter can now be

arbitrarily pipelined by selecting the K value. The FIR filter

contains no loop and hence it causes no limitation for the

pipelining.

Figure 1 shows the Direct-form II structure for a single-pole

IIR filter implementation. The equivalent model allows

pipelining in the feedback loop, and therefore can achieve

The single cycle recursive structure given by (please refer to

Figure 2 for notations)

,

(6)

can be represented by:

,

,

(7)

The proof of this claim is given in the Appendix. Figure 2

shows the equivalent model for more general operations

satisfying the mentioned properties. As the figure shows the

proposed model consists of a feedback structure with the

desired number of pipelining registers followed by a feedforward architecture that can be pipelined for desired

.

Besides the IIR filters, the generalized model can be used to

reconstruct pipelined loops with different operations and

hence for variety of applications.

Max/Min functions are the other set of useful operations that

satisfy all three properties, and thus the proposed structure can

be used to add pipelining registers in the feedback loop.

Figure 2 Equivalent model for loop-pipelining in recursive

structures.

Multiplication operation satisfies the first and second

properties, but not the last one; therefore the method may not

be applied. However if the constant gain is set to 1, g=1, the

technique can be applied for recursive multiplications as well.

This leads to applications such as Factorial and GeometricMean calculations.

It should be mentioned that subtraction operation can be

realized by the summation operation with a negative g, and

again the method can be properly applied for subtractions.

IV.

CFR EXAMPLE

Radio Digital Front End (DFE) supporting Long-Term

Evolution Advanced (LTE-A) is required to run at a sample

rate of 491 MHz to support bandwidths up to 100 MHz. One

of the most challenging algorithms to run at the sample rate is

crest factor reduction (CFR), as it contains a feedback loop.

CFR modules are used in DFEs to detect and cancel the peaks

in transmit modulated signal to mitigate the distortions when

using nonlinear power amplifiers.

Figure 3 shows the block diagram of peak searching submodule in CFR implementation. The peak searching module

needs to select the maximum value in a continuous stream of

samples. This is typically done by comparing the incoming

sample against the previously found maximum, and stores the

result as the new maximum.

Figure 3 The realization of Max(.) function in CFR.

As the figure shows the loop has only a single register,

therefore the closed loop calculations including a comparator

and a multiplexer should be carried out in a single clock cycle.

Increasing the number of registers will alter the algorithm and

therefore breaks the overall functionality.

Figure 4 Realization of Max(.) function with the proposed

technique. Two registers are added in the feedback loop to hit the

desired Fmax.

TABLE I.

FMAX ACHIEVEMENT IN QUARTUS, TOGETHER WITH LOGIC

USAGES.

Resource Usage

ALMs

Model

CFR IP Fmax, SV

Original

Model

396 MHz

4069

Proposed

Model

495 MHz

4267

Reg

Mux Cmp

The feedback loop including Max(.) function can be modified

according to the proposed structure to allow more pipelining

registers to be inserted in the loop. Figure 4 shows the

proposed structure with 2 delays (

2). The CFR module is

implemented using Alteras high level synthesis tool, DSP

builder Advanced (DSPBA) [6]. Table 1 shows the Fmax and

resource estimation results after the CFR modification

according to the proposed technique. For the resource

estimation we run both designs in 491 MHz system clock. As

the results show the module with three iteration CFR blocks

can reach 495 MHz Fmax, and hence an increase of around 100

MHz is achieved at the expense of around 5 % increase in

resource utilization. As CFR module is again a relatively small

portion of a full radio DFE, the overall resource utilization is

kept below 1 %, while meeting the desired Fmax requirements.

It should be pointed out here that 491 MHz requirement is met

by adding 2 registers in the feedback loop, whereas if higher

Fmax is required, more number of registers can be inserted

according to (7) to meet the requirement.

The second argument in the function can then be rewritten

using the property 2 as:

V. CONCLUSIONS

,

,

It works by increasing the pipeline stages while maintaining

the original functionality. This technique can be utilized by

engineers and also can be built into high level synthesis tools

(such as DSP Builder Advanced) to eliminate Fmax

bottlenecks in feedback loops and get close to maximum

silicon speed.

The authors would like to thank Alteras Wireless System

Solutions Group and DSP builder team for their kind support,

guidance and advices.

In this paper we presented a novel algorithmic-level

technique to significantly increase Fmax by modifying

feedback loops used in many DSP applications across FPGA

vertical markets. The proposed technique is flexible and the

closed-loop latency and hence the required stages for

pipelining is adjustable to achieve the desired Fmax to meet

various targets.

AKNOWLEDGMENT

(12)

APPENDIX

Please refer to Figure 2 for the notations.

Starting from the output of the multi-cycle equivalent

recursive model we have:

,

which is identical to the output of the single-cycle

recursive structure.

REFERENCES

(8)

(9)

[1] G. Bylkin, On Factored FIR Approximation of IIR Filters,

Applied and Computational Harmonic Analysis 2, pp. 293-298,

1995.

[2] Y. Yamamoto, B. D. O. Anderson, M. Nagahara, and Y.

Koyanagi, Optimizing FIR Approximation for Discrete--Time

IIR Filters, IEEE Signal Processing Letters, Vol. 10, No. 9,

September 2003.

[3] A. Krukowski and I. Kale, DSP system design: Complexity

reduced IIR filter implementation for practical applications,

Boston: Kluwer, Academic Publishers, 2003.

[4] Michael Francis, Infinite Impulse Response Filter Structures in

Xilinx FPGAs, White paper by XILINX, Aug. 2009.

(10)

[5] K.K. Parhi and D.G. Messerschmitt, Pipeline Interleaving and

Parallelism in Recursive Digital Filters Parts I and II, IEEE

Trans Acoustic Speech, Signal processing.

,

,

(11)

[6] "Altera

DSPBA,"

[Online].

Available:

http://www.altera.co.uk/technology/dsp/advanced-blockset/dspadvanced-blockset.html.

Anda mungkin juga menyukai

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceDari EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RacePenilaian: 4 dari 5 bintang4/5 (895)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeDari EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifePenilaian: 4 dari 5 bintang4/5 (5794)

- Intel 8086 Instruction FormatDokumen16 halamanIntel 8086 Instruction Formatmmorsy1981Belum ada peringkat

- Function Generator Using X86 MicroprocessorDokumen7 halamanFunction Generator Using X86 Microprocessormmorsy1981Belum ada peringkat

- ZTransformPairs PDFDokumen1 halamanZTransformPairs PDFmmorsy1981Belum ada peringkat

- Survey On Security in Internet of Things State of The Art and ChallengesDokumen8 halamanSurvey On Security in Internet of Things State of The Art and Challengesmmorsy1981Belum ada peringkat

- Internet of Things (IoT) A Vision, Architectural Elements, and Security IssuesDokumen5 halamanInternet of Things (IoT) A Vision, Architectural Elements, and Security Issuesmmorsy1981Belum ada peringkat

- Tutorial Design CompilerDokumen9 halamanTutorial Design Compilermmorsy1981Belum ada peringkat

- Nano Editor Keyboard ShortcutsDokumen1 halamanNano Editor Keyboard Shortcutsmmorsy1981Belum ada peringkat

- IDC Digital Ink InfoBrief - en-USDokumen20 halamanIDC Digital Ink InfoBrief - en-USmmorsy1981Belum ada peringkat

- Synopsys VCS Commands For Verilogn CompilationDokumen3 halamanSynopsys VCS Commands For Verilogn Compilationmmorsy1981Belum ada peringkat

- Lab 6 Introduction To VerilogDokumen7 halamanLab 6 Introduction To Verilogmmorsy1981Belum ada peringkat

- Foundational Proof-Carrying CodeDokumen10 halamanFoundational Proof-Carrying Codemmorsy1981Belum ada peringkat

- Time-Adjustable Delay Circuit PDFDokumen8 halamanTime-Adjustable Delay Circuit PDFmmorsy1981Belum ada peringkat

- Chapter 9 - Program Control InstructionsDokumen60 halamanChapter 9 - Program Control Instructionsmmorsy1981100% (4)

- Linear Temporal Logic Symbolic Model CheckingDokumen41 halamanLinear Temporal Logic Symbolic Model Checkingmmorsy1981100% (1)

- Formal Methods Roadmap PVS, ICS, and SALDokumen28 halamanFormal Methods Roadmap PVS, ICS, and SALmmorsy1981Belum ada peringkat

- Shoe Dog: A Memoir by the Creator of NikeDari EverandShoe Dog: A Memoir by the Creator of NikePenilaian: 4.5 dari 5 bintang4.5/5 (537)

- Grit: The Power of Passion and PerseveranceDari EverandGrit: The Power of Passion and PerseverancePenilaian: 4 dari 5 bintang4/5 (588)

- The Yellow House: A Memoir (2019 National Book Award Winner)Dari EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Penilaian: 4 dari 5 bintang4/5 (98)

- The Little Book of Hygge: Danish Secrets to Happy LivingDari EverandThe Little Book of Hygge: Danish Secrets to Happy LivingPenilaian: 3.5 dari 5 bintang3.5/5 (400)

- Never Split the Difference: Negotiating As If Your Life Depended On ItDari EverandNever Split the Difference: Negotiating As If Your Life Depended On ItPenilaian: 4.5 dari 5 bintang4.5/5 (838)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureDari EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FuturePenilaian: 4.5 dari 5 bintang4.5/5 (474)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryDari EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryPenilaian: 3.5 dari 5 bintang3.5/5 (231)

- Rise of ISIS: A Threat We Can't IgnoreDari EverandRise of ISIS: A Threat We Can't IgnorePenilaian: 3.5 dari 5 bintang3.5/5 (137)

- The Emperor of All Maladies: A Biography of CancerDari EverandThe Emperor of All Maladies: A Biography of CancerPenilaian: 4.5 dari 5 bintang4.5/5 (271)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaDari EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaPenilaian: 4.5 dari 5 bintang4.5/5 (266)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersDari EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersPenilaian: 4.5 dari 5 bintang4.5/5 (345)

- On Fire: The (Burning) Case for a Green New DealDari EverandOn Fire: The (Burning) Case for a Green New DealPenilaian: 4 dari 5 bintang4/5 (74)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyDari EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyPenilaian: 3.5 dari 5 bintang3.5/5 (2259)

- Team of Rivals: The Political Genius of Abraham LincolnDari EverandTeam of Rivals: The Political Genius of Abraham LincolnPenilaian: 4.5 dari 5 bintang4.5/5 (234)

- The Unwinding: An Inner History of the New AmericaDari EverandThe Unwinding: An Inner History of the New AmericaPenilaian: 4 dari 5 bintang4/5 (45)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreDari EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You ArePenilaian: 4 dari 5 bintang4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Dari EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Penilaian: 4.5 dari 5 bintang4.5/5 (121)

- Her Body and Other Parties: StoriesDari EverandHer Body and Other Parties: StoriesPenilaian: 4 dari 5 bintang4/5 (821)

- Heuristic SearchDokumen68 halamanHeuristic SearchRocky SinghBelum ada peringkat

- Mathcad - Postfilter-Feedback-Halfbridge-Single-Supply-170VDokumen6 halamanMathcad - Postfilter-Feedback-Halfbridge-Single-Supply-170Vfarid.mmdBelum ada peringkat

- FPGA Based Implementation of 2D Discrete Cosine Transform AlgorithmDokumen13 halamanFPGA Based Implementation of 2D Discrete Cosine Transform AlgorithmPragati PrajapatiBelum ada peringkat

- Seminar PresentationDokumen25 halamanSeminar PresentationPaDiNjArAnBelum ada peringkat

- Solved - The Fourth-Degree Polynomial F (X) 230x4 + 18x3 + 9x2...Dokumen7 halamanSolved - The Fourth-Degree Polynomial F (X) 230x4 + 18x3 + 9x2...Malik Ijaz Ali AwanBelum ada peringkat

- CSP 112 Assignment - Abhishek Kandel (2021826004)Dokumen16 halamanCSP 112 Assignment - Abhishek Kandel (2021826004)Abhishek KandelBelum ada peringkat

- Deep LearningDokumen39 halamanDeep LearningwilliamBelum ada peringkat

- Quality of Clustering: Clustering (K-Means Algorithm)Dokumen4 halamanQuality of Clustering: Clustering (K-Means Algorithm)Sk Arif AhmedBelum ada peringkat

- In Lecture SlidesDokumen137 halamanIn Lecture SlidesAlaa SaadBelum ada peringkat

- Lab 4Dokumen9 halamanLab 4shakaibBelum ada peringkat

- Lecture4 JavaDokumen46 halamanLecture4 JavaZerihun BekeleBelum ada peringkat

- Exercises III Integer Linear Programming and ModelingDokumen3 halamanExercises III Integer Linear Programming and ModelingVishnu T GopalBelum ada peringkat

- 4.3 Euler's Method: Linear ApproximationDokumen4 halaman4.3 Euler's Method: Linear ApproximationJaden MoniezBelum ada peringkat

- Equalizer Design and Performance Trade-Offs in ADC-Based Serial LinksDokumen12 halamanEqualizer Design and Performance Trade-Offs in ADC-Based Serial LinksModyKing99Belum ada peringkat

- 10 Bellmanford and SP in DAG - Algorithms (Series Lecture)Dokumen40 halaman10 Bellmanford and SP in DAG - Algorithms (Series Lecture)turjo987Belum ada peringkat

- Cnn-IDokumen32 halamanCnn-IJonathan PervaizBelum ada peringkat

- Assignment TechniqueDokumen16 halamanAssignment TechniqueRahul KhoslaBelum ada peringkat

- Sorting AlgorithmsDokumen2 halamanSorting AlgorithmsCristine Joy JemillaBelum ada peringkat

- Communication Systems Lab Lab 6: To Study The Sampling Theorem Using MatlabDokumen4 halamanCommunication Systems Lab Lab 6: To Study The Sampling Theorem Using MatlabAafaqIqbalBelum ada peringkat

- CS502 Finaltermsolved Mcqswithreferencesby MoaazDokumen43 halamanCS502 Finaltermsolved Mcqswithreferencesby MoaazZulqarnain GondalBelum ada peringkat

- Avl TreesDokumen11 halamanAvl Treesjesusmp97Belum ada peringkat

- How To Solve A Rubiks CubeDokumen5 halamanHow To Solve A Rubiks CubeLiezel SanchezBelum ada peringkat

- Finding The Roots of Polynomial Equations 1Dokumen2 halamanFinding The Roots of Polynomial Equations 1Dorinda F. Barredo100% (1)

- Sheet 1 Solution of Systems of Linear EquationsDokumen4 halamanSheet 1 Solution of Systems of Linear EquationsMohamed AlfarashBelum ada peringkat

- Engineering Science 204: Machine Problem No. 1Dokumen29 halamanEngineering Science 204: Machine Problem No. 1Regina LagaticBelum ada peringkat

- Advances in Signal Processing Technology For Electronic WarfareDokumen8 halamanAdvances in Signal Processing Technology For Electronic WarfareSalman AnwarBelum ada peringkat

- Assignment CaseDokumen6 halamanAssignment CaseMostafa SakrBelum ada peringkat

- HashingDokumen38 halamanHashingAdnan khanBelum ada peringkat

- Linear Algebra Cheat SheetDokumen2 halamanLinear Algebra Cheat SheettraponegroBelum ada peringkat

- COMP1942 Question PaperDokumen5 halamanCOMP1942 Question PaperpakaMuzikiBelum ada peringkat