Effect of Fin Shape On GIDL and Subthreshold Leakage Currents

Diunggah oleh

IJSTEJudul Asli

Hak Cipta

Format Tersedia

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniHak Cipta:

Format Tersedia

Effect of Fin Shape On GIDL and Subthreshold Leakage Currents

Diunggah oleh

IJSTEHak Cipta:

Format Tersedia

IJSTE - International Journal of Science Technology & Engineering | Volume 1 | Issue 10 | April 2015

ISSN (online): 2349-784X

Effect of Fin Shape on GIDL and Subthreshold

Leakage Currents

Daughty Abraham

PG Student

Department of Electronics & Communication Engineering

Saintgits College of Engineering

Abraham George

Assistant Professor

Department of Electronics & Communication Engineering

Saintgits College of Engineering

Deepa Gopinadh

PG Student

Department of Electronics & Communication Engineering

Saintgits College of Engineering

Abstract

FinFETs have emerged as the solution to short channel effects at the 22-nm technology node and beyond. Here, the effect of fin

shape on the leakage currents like Gate Induced Drain Leakage and subthreshold leakage is evaluated. The fin shape can be

changed by varying the top width of the fin. Hence, the leakage currents are verified using their expressions for both rectangular

and triangular FinFETs. The effects of oxide thickness, drain doping concentration and mobility on these leakage currents are

also studied.

Keywords: FinFETs, Gate Induced Drain Leakage, Subthreshold leakage

________________________________________________________________________________________________________

I. INTRODUCTION

As device feature sizes enter the nanometre regime, leakage power consumption in VLSI systems has become one of the main

barriers to technology scaling. Precise modeling of leakage current under process variations is crucial for the proper estimation

of leakage power consumption and the optimal design of leakage-sensitive circuits. Double-gate FinFET transistors are

recognized as one of the most promising successors of traditional planar bulk devices in the sub-50nm regime due to the

significantly reduced leakage current, excellent short channel behaviour, and a fabrication process which is compatible with

existing SOI or bulk technology processes. One of the major differences between a FinFET device and a planar device is the fact

that the FinFET device consists of multiple small unit fins.

Minimization of transistor off-state leakage current is an especially important issue for low-power circuit applications.

Leakage mechanisms include subthreshold leakage, gate oxide tunneling leakage, junction leakage, hot-carrier injection leakage,

gate-induced drain leakage, and punch-through leakage currents.

A large component of off-state leakage current is gate induced drain leakage (GIDL) current, caused by band-to band

tunneling in the drain region underneath the gate when there is a large gate-to-drain bias, there can be sufficient energy-band

bending near the interface between silicon and the gate dielectric for valence-band electrons to tunnel into the conduction band.

GIDL imposes a constraint for gate-oxide thickness scaling because the voltage required causing this band-to-band tunneling

leakage current decreases with decreasing gate oxide thickness, and GIDL can pose a lower limit for standby power in memory

devices. GIDL current becomes less significant for digital logic applications as the power-supply voltage is reduced to below

1.1V (corresponding to the energy band gap of silicon); however, it is still an important consideration for applications such as

dynamic random access memory (DRAM), for which data retention time is significantly degraded by GIDL current.

Subthreshold leakage current is the dominant mechanism in 90 nm and 65 nm technologies. It increases linearly as technology

scales down. Subthreshold current, also known as weak inversion conduction current, between source and drain in a MOS

transistor occurs when the gate voltage is below the transistor threshold voltage (Vth). The carriers move by diffusion along the

surface, and there is an exponential relation between driving voltage on the gate and the drain current.

In this paper, fin shape significantly impacts leakage in bulk tri-gate nFinFETs with thin fin widths when the fin body doping

is optimized to minimize leakage. Here, GIDL and subthreshold leakage current is observed when varying the fin shape. The

various parameters that these leakage currents are depending are also studied.

The detailed description of GIDL and subthreshold leakage currents are presented in the first part of Chapter 2, followed by

the description of processing of the fin-structures on bulk silicon wafers. Chapter 3 gives the analytical procedures of this

project. Simulation results are discussed in Chapter 4. Finally, Chapter 5 gives the conclusion.

All rights reserved by www.ijste.org

135

Effect of Fin Shape on GIDL and Subthreshold Leakage Currents

(IJSTE/ Volume 1 / Issue 10 / 027)

II. LITERATURE REVIEW

A.

Sources of Leakage Currents:

Different physical phenomena contribute to the leakage currents causing the static consumption when one or more transistors in

the Vdd to Gnd paths are in OFF- state. Figure 2.1 shows the contribution of different leakage currents in a transistor.

Fig. 2.1: Leakage components in a transistor (Farzan Fallah et al., 2010)

B. Gate Induced Drain Leakage (GIDL):

In some nanometric technologies, gate induced drain leakage current (IGIDL) may appear. The carriers responsible for GIDL

originate in the region of the drain that is overlapped by the gate. I GIDL is caused by the effects of high electric field in this region,

when the gate is grounded and the drain is at Vdd. IGIDL current of an nMOS transistor flows from drain to the substrate.

Fig. 2.2: Drain overlapped MOSFET: GIDL occurs in this region (FinFETs and Other Multi-Gate Transistors, by Jean Pierre Colinge)

Several possible mechanisms contribute to this current. These include thermal emission, trap-assisted tunneling and band-toband tunneling. It is the Band to Band Tunneling (BTBT) that has the MOSFET relevance at the voltages and structures of

modern devices.

Consider a MOS structure as shown in figure 2.2. In the structure gate overlaps the drain junction. As gate becomes more

negative or say drain becomes more positive at a fixed gate voltage then p-n+ junction become reverse biased. Due to reverse

biased p-n+ junction, a depletion region forms near the drain junctions. Since the drain is heavily doped, the depletion region

width formed inside the drain tends to be narrow, so band to band tunneling will start in this region, i.e. electrons tunnel from the

valence band of p region into conduction band of n+ region. The removal of electron from valence band produces a hole, which

creates electron-hole pairs. Hence, a significant current flow can occur, called GIDL current (Electronic Devices and Integrated

Circuits, by Singh).

Fig. 2.3: Energy band curvature in the depleted drain region and electron tunneling from the valence band to the conduction band (Physics of

Semiconductor Devices, by Jean Pierre Colinge and C. A. Colinge)

All rights reserved by www.ijste.org

136

Effect of Fin Shape on GIDL and Subthreshold Leakage Currents

(IJSTE/ Volume 1 / Issue 10 / 027)

This current may be further enhanced because the generated carriers are accelerated by the longitudinal electric field in the

drain substrate junction and this causes impact ionization. For direct-band gap materials, JGIDL can be modelled by equation 2.1

(FinFETs and Other Multi-Gate Transistors, by Jean Pierre Colinge).

(

(2.1)

Where, A is a pre-exponential parameter given by equation 2.2 and B is a physically-based exponential parameter given by

equation 2.3 (FinFETs and Other Multi-Gate Transistors, by Jean Pierre Colinge.). ETOT is the electrical field at point the

maximum band-to-band tunneling.

(2.2)

( )

( )

( )

(2.3)

Where, Eg is the energy band gap of the semiconductor channel and has a strong influence on the band-to-band tunneling

current, mr is 0.2 * mass of electron, q is the charge of electron, = h/2, h is the Plancks constant. A large component of the

ETOT is the surface electrical field ES. ES is defined by equation 2.4 (FinFETs and Other Multi-Gate Transistors, by Jean Pierre

Colinge.).

(2.4)

Where, VDG is the drain to gate bias, VFB is the flat-band voltage, Egap is the energy band gap of silicon, t ox is the thickness of

the oxide, Si is the permittivity of silicon and ox the permittivity of the oxide.

Fig. 2.4: Energy band curvature in the depleted drain region and electron tunneling from the valence band to the conduction band (Physics of

Semiconductor Devices, by Jean Pierre Colinge and C. A. Colinge)

C. Subthreshold Leakage Current:

In a MOS transistor, if the gate voltage with reference to the source voltage (V GS) is above the threshold voltage (Vth) then the

dominant mechanism of the drain current is primarily drift based. Drift current is proportional to (VGS Vth) where 1 < < 2.

When the gate voltage is lower than the threshold voltage and there is a voltage applied between drain and source of a MOS

transistor, the dominant mechanism of the drain current is primarily diffusion based. Diffusion current appears due to the

different carrier concentration at the inversion layer in source and drain terminals. Figure 2.5 shows the subthreshold leakage

current between drain and source. This current depends exponentially on gate-to-source voltage (VGS) and drain-to-source

voltage (VDS) through the carrier concentrations (Low Power CMOS Circuits and Technology, Logic Design and CAD Tools,

by Christian Piguet).

Fig. 2.5: Subthreshold leakage current in the MOSFET (Ashesh Rastogi et al., 2007)

In a long channel device, the depth of the depletion region in source and drain regions is relatively unimportant. As the

channel length is reduced, these depletion regions occupy more space of the channel region. The depletion region near the source

All rights reserved by www.ijste.org

137

Effect of Fin Shape on GIDL and Subthreshold Leakage Currents

(IJSTE/ Volume 1 / Issue 10 / 027)

and drain edges are shared with the channel. This effect produces a reduction of the threshold voltage when decreasing channel

length and therefore, increases the subthreshold current (Low Power CMOS Circuits and Technology, Logic Design and CAD

Tools, by Christian Piguet).

D.

Drain Induced Barrier Lowering (DIBL):

The Drain Induced Barrier Lowering effect consists of lowering the energy barrier between the source and the channel. This

causes excess injection of the charge barriers into the channel and gives rise to an increased subthreshold current. Figure 2.6

presents the band diagram at the interface of the channel, for short and long channel transistors. At the interface, the channel

consists of three regions: the source channel junction, the middle region, and the drain channel junction. For the long channel

transistor, the energy bands in the central part of the channel can be taken to be approximately constant because the voltage

almost drops at the drain channel junction. As the channel length is reduced, this situation is no longer true. Consequently, a

reduction in the interface energy barrier occurs at the source channel junction where the maximum of the barrier is reached. This

is the so-called DIBL effect. (T. A. Fjeldly et al., 1993).

Fig. 2.6: Physical origin of DIBL effect (Low Power CMOS Circuits and Technology, Logic Design and CAD Tools, by Christian Piguet)

The magnitude of the subthreshold current is a function of the temperature, supply voltage, device size and the process

parameters out of which the threshold voltage (Vth) plays a dominant role. For an nMOS transistor, the subthreshold current is

given by equation 2.5 (Low Power CMOS Circuits and Technology, Logic Design and CAD Tools, by Christian Piguet).

( )

)(

))

(2.5)

(2.6)

(2.7)

Where n is the electron carrier mobility, Cox is the oxide capacitance per unit area, W is the channel width, L is the channel

length, Vth is the threshold voltage, VGS is the gate to source voltage, VDS is the drain to source voltage, VT is the thermal voltage

given by the equation 2.6, T is the temperature in Kelvin, k is the Boltzmann constant, n is the inverse slope of the subthreshold

current given by the equation 2.7 and CD is the depletion channel region capacitance per unit area.

In short channel transistors, Vth is further modified as a function of the channel length and the drain-to-source bias and these

are the so called short channel and drain induced barrier lowering (DIBL) effects. Figure 2.7 shows the subthreshold leakage

current when VGS is less than Vth.

Fig. 2.7: Drain current showing the subthreshold leakage current (Physics of Semiconductor Devices, by Jean Pierre Colinge and C.

A. Colinge)

E.

FinFET:

The scaling of CMOS devices is moving towards the physical limits that can be achieved with the standard bulk technology. The

off-state current and standby powers are increasing with shorter channel lengths. Since, it is becoming more difficult to keep the

All rights reserved by www.ijste.org

138

Effect of Fin Shape on GIDL and Subthreshold Leakage Currents

(IJSTE/ Volume 1 / Issue 10 / 027)

electrostatic integrity of devices, channel doping needs to be increased and the source and drain junctions need to become

shallower. But these trends are offset by the increased junction leakage and higher series resistances. Fully-depleted devices,

double-gate devices in particular, offer significantly better electrostatic integrity and hence, better short-channel immunity.

FinFETs are seen as the most likely candidate for the successor of the bulk CMOS from the 22 nm node onwards, because of its

compatibility with the current CMOS technology. Many different ICs with FinFETs have already been demonstrated, ranging

from digital logic, SRAM, DRAM to flash memory (FinFETs and Other Multi-Gate Transistors, by Jean Pierre Colinge).

Figure 2.8 shows the FinFET structure. The distinguishing characteristic of the FinFET is that the conducting channel is

wrapped by a thin silicon "fin", which forms the body of the device. The thickness of the fin (measured in the direction from

source to drain) determines the effective channel length of the device. The Wrap-around gate structure provides a better electrical

control over the channel and thus helps in reducing the leakage current and overcoming other short-channel effects.

Fig. 2.8: FinFET structure (A. Dixit, A. Kottantharayil et al., 2005)

F. Current Drive:

In a multi-gate FET the current drive is essentially equal to the sum of the currents flowing along all the interfaces covered by

the gate electrode. It is, therefore, equal to the current in a single-gate device multiplied by the equivalent number of gates (a

square cross section is assumed) if carriers have the same mobility at each interfaces. For instance, the current drive of a doublegate device is double that of a single-gate transistor of equivalent gate length and width. In triple-gate and vertical double-gate

structures all individual fins have the same thickness and width. As a result, the current drive is fixed to a single, discrete value,

for a given gate length. To drive larger currents multi-fin devices are used. The current drive of a multi-fin MOSFET is equal to

the current of an individual fin multiplied by the number of fins (also sometimes referred to as fingers or legs) (FinFETs

and Other Multi-Gate Transistors, by Jean Pierre Colinge).

In the linear region, the current increases linearly with VDS, when VGS > Vth. To a first approximation, IDS in the linear region is

given by the equation 2.9 (M. Zakir Hossain et al., 2011).

(

)

In the saturation region, IDS no longer increases as VDS and is given by the equation 2.10 (M. Zakir Hossain et al., 2011).

(2.10)

(2.11)

Where is the effective mobility in the channel (inversion) region, C ox is the oxide capacitance per unit area, W is the

effective channel width, L is the effective channel length, Vth is the threshold voltage, xd is the depletion layer thickness and tox is

the oxide thickness.

III. ANALYTICAL PROCEDURES

In this project, the effect of fin shape on GIDL and subthreshold leakage currents has been studied. The fin shape normally in

rectangular shape has been changed to triangular for better reduction in leakage currents. To change the fin shape, the width of

the top of the fin has been changed while the bottom width remains unchanged.

A.

Effective Width Expression

To compare different fin shapes, all ION and IOFF values are normalized to the effective transistor width (Weff). Weff is the

component of the fin cross section perimeter adjacent to the gate oxide, calculated simply using the Pythagorean Theorem for the

fin sides and the area of the semicircle with corner radius set to Wtop/2 for the fin top and is given by the equation 3.1 (Brad D.

Gaynor et al., 2014).

All rights reserved by www.ijste.org

139

Effect of Fin Shape on GIDL and Subthreshold Leakage Currents

(IJSTE/ Volume 1 / Issue 10 / 027)

(3.1)

Where, Wbottom is w bottom width of the active fin, Wtop is top width of the active fin and H is the fin height.

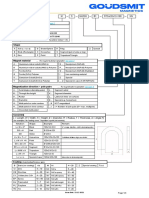

The key geometries shown in table 3.1 have been selected. The corner radius of the rounded fin is set to Wtop to minimize

corner effects.

Table -3.1:

nFinFET model geometry parameters

Parameter

Value

Wbottom

20nm

Wtop

20nm for rectangular, 1nm for triangular

H

30nm

L

30nm

B.

GIDL Current Expression:

The FinFET GIDL current can be expressed by the equation3.2 (Farkhanda Ana et al., 2012),

(

(3.2)

)

(3.3)

Where H is the parameter related to junction depth as,

(3.4)

VFB is the flat band voltage given by,

(3.5)

Where, ETOT is the total electric field, A and B given by the equation 2.2 and 2.3, L is the length of the fin, s is the potential

drop across silicon for band to band tunneling xj is the junction depth, m is the gate work function and Si is the silicon substrate

work function.

In case of GIDL current the values given to the different parameters are listed in the table 3.2. These values are given in the

equation 3.2 inorder to calculate the GIDL current for various negative values of gate to source voltage.

Table -3.2:

Parameters for GIDL current

Parameter

Value

VG

Negative values

VD

1V

tox

2 nm

A

Pre-exponential constant

B

21.3*10^8 V/m

xj

25 nm

Egap

1.11 eV

VFB

-.9 V

C.

Subthreshold Current Expression:

The FinFET subthreshold current can be expressed by the equation 3.6 (Giorgio Baccarani et al., 1999),

(

)(

))

(3.6)

(3.7)

(3.8)

(3.9)

Where, ox is the permittivity of the oxide, si is the permittivity of silicon and tfin is the thickness of fin.

All rights reserved by www.ijste.org

140

Effect of Fin Shape on GIDL and Subthreshold Leakage Currents

(IJSTE/ Volume 1 / Issue 10 / 027)

In case of subthreshold current the values given to the different parameters are listed in the table 3.3. These values are given in

the equation 3.6 inorder to calculate the subthreshold current for various positive values of gate to source voltage.

Table -3.3:

Parameters for subthreshold current

Parameter

Value

VGS

Positive values

VDS

1V

Tox

2 nm

ox

3.9

Si

11.68

tfin

5 nm

n

200 cm/Vs

These equations for GIDL and subthreshold currents are computed and obtained the results using MATLAB.

IV. RESULTS AND DISCUSSION

The parameter values mentioned in the previous chapter are given to the equations 3.1- 3.9 corresponding to the two leakage

currents GIDL and subthreshold current. The program is then run to obtain the 2D plots.

A.

Graphs for Drain Current in FinFET:

The output characteristics of rectangular and triangular FinFET is obtained as shown in the figure 4.1.

Fig. 4.1: Output characteristics of both rectangular and triangular FinFET

For rectangular fin shape, the current is 510 A/ m and for triangular fin shape, it is 570 A/m, when V GS is equal to 0.6

volts. Hence, there is 11% increase in drain current when compared with rectangular fin shape. Figure 4.1 indicates that the drain

current increases with increase in drain voltage and this condition is true up to pinch off voltage and beyond that there is no

effect of drain voltage over drain current.

B.

Graphs for GIDL Leakage Current:

GIDL current varying with negative values of gate voltage for both rectangular and triangular fin shape is obtained in the figure

4.2.

Fig. 4.2 GIDL characteristics of both rectangular and triangular FinFET

All rights reserved by www.ijste.org

141

Effect of Fin Shape on GIDL and Subthreshold Leakage Currents

(IJSTE/ Volume 1 / Issue 10 / 027)

For rectangular fin shape, the current is 31 A/ m and for triangular fin shape, it is 27 A/ m at -4 volts. Hence, there is 13%

decrease in leakage current when compared with rectangular fin shape.

The GIDL leakage current is compared by varying oxide thickness in both rectangular and triangular FinFET as shown in

figure 4.3. It is clear that by increasing the oxide thickness the current can be reduced in both rectangular and triangular FinFET.

Fig. 4.3: GIDL characteristics for varying oxide thickness

The GIDL leakage current is also compared by varying junction depth in both rectangular and triangular FinFET as shown in

figure 4.4. It is clear that by increasing the junction depth the current can be reduced in both rectangular and triangular FinFET.

Fig. 4.4: GIDL characteristics for varying junction depth

The comparison of GIDL current in both rectangular and triangular FinFET with different drain doping concentration has also

being compared and is shown in figure 4.5. From the graph we can infer that by decreasing drain doping concentration the

current can be reduced.

Fig. 4.5: GIDL characteristics for varying drain doping concentration

The results can be tabulated as in table 4.1.

Table 4.1

Results obtained for GIDL current

Parameters

Rectangular FinFET

2 nm

.035 nA

Oxide thickness

1.5 nm

.052 nA

30 nm

.016 nA

Junction depth

25 nm

.032 nA

5*10^30

.053 nA

Drain doping

concentration

5*10^20

.047 nA

Triangular FinFET

.03 nA

.047 nA

.014 nA

.028 nA

.046 nA

.042 nA

All rights reserved by www.ijste.org

142

Effect of Fin Shape on GIDL and Subthreshold Leakage Currents

(IJSTE/ Volume 1 / Issue 10 / 027)

So, the GIDL current can be reduced by decreasing the drain doping concentration, increasing the oxide thickness and also by

increasing the junction depth. These effects are also applicable to rectangular as well as triangular fins. i.e., by changing from

rectangular to triangular the leakage current is further lowered.

C.

Graphs for Subthreshold Leakage Current:

GIDL current varying with positive values of gate to source voltage for both rectangular and triangular fin shape is obtained in

the figure 4.6.

Fig. 4.6: Subthreshold characteristics of both rectangular and triangular FinFET

For rectangular fin shape, the current is 8.5 A/ m and for triangular fin shape, it is 7.5 A/ m at 0.4 volts. Hence, there is 12%

decrease in leakage current when compared with rectangular fin shape.

The subthreshold leakage current is compared by varying oxide thickness in both rectangular and triangular FinFET as shown

in figure 4.7. It is clear that by increasing the oxide thickness the current can be reduced in both rectangular and triangular

FinFET.

Fig. 4.7 Subthreshold characteristics for varying oxide thickness

The comparison of subthreshold current in both rectangular and triangular FinFET with different mobility has also being done

and is shown in figure 4.8. By decreasing mobility, the current can be reduced.

Fig. 4.8: Subthreshold characteristics for varying mobility

All rights reserved by www.ijste.org

143

Effect of Fin Shape on GIDL and Subthreshold Leakage Currents

(IJSTE/ Volume 1 / Issue 10 / 027)

The leakage current with respect to temperature is also plotted showing that the current is lower in triangular fin when

compared to rectangular fin. In case of rectangular fin, the current is 105A/m and for triangular fin it is 95A/m at 400K i.e.,

10% decrease in current.

The results can be tabulated as in table 4.2.

Table -4.2:

Results obtained for subthreshold leakage current

Parameters

Rectangular FinFET

Triangular FinFET

2 nm

.15 mA

.13 mA

Oxide thickness

1 nm

.29 mA

.26 mA

670 cm/Vs

.45 mA

.40 mA

Effective

mobility

220 cm/Vs

.15 mA

.12 mA

However, to reduce the subthreshold leakage current, the oxide thickness need to be increased and the effective mobility need

to be decreased. These effects are also applicable to rectangular as well as triangular fins. i.e., by changing from rectangular to

triangular the leakage current is further lowered.

V. CONCLUSION

Double-gate FinFET devices are considered as one of the most promising successors of conventional MOSFET devices. Due to

the physical fin structure, the width of a FinFET device can be changed. Here, the impact of fin cross-section shape on bulk trigate nFinFETs with thin fins is evaluated. It is clear that the fin shape has considerable impact on leakage performance. With

appropriate doping optimization, a 22-nm nFinFETs with triangular fin cross section results in more than 10% reduction in

leakage current over a rectangular fin with the same base fin width.

Here, the effect of fin shape on various device parameters like oxide thickness, drain doping concentration, effective mobility,

junction depth and temperature is also explored and showed that, all these parameters affects the leakage currents like GIDL and

subthreshold more in the case of triangular FinFET. MATLAB 8.3 has been used for the verification of the results. However,

future research is needed to further reduce the leakage current in bulk FinFETs.

VI. REFERENCES

[1]

[2]

[3]

[4]

[5]

[6]

[7]

[8]

[9]

[10]

[11]

[12]

[13]

[14]

[15]

[16]

[17]

[18]

[19]

[20]

[21]

[22]

[23]

[24]

[25]

A. Dixit, A. Kottantharayil, N. Collaert, M. Goodwin, M. Jurczak, K. De Meyer: Analysis of the Parasitic S/D Resistance in Multiple-Gate FETs. IEEE

Transactions on Electron Devices 52-6, 1132 (2005).

Ajay Kumar Singh, Electronic Devices and Integrated Circuits, Prentice Hall, pp 342-344, 2008.

Ashesh Rastogi, Comprehensive Analysis of Leakage Current in Ultra Deep Sub-micron (UDSM) CMOS Circuits, University of Massachusetts (2007).

Baozhen Yu, A Novel Dynamic Power Cut-off Technology (DPCT) for Active Leakage Reduction, University of New Jersey, 2009.

Brad D. Gaynor and Soha Hassoun, Fin Shape Impact on FinFET Leakage with Application to Multi-threshold and Ultralow-Leakage FinFET Design.

IEEE Transactions on Electron Devices. Vol.61 (2014).

B. Van Zeghbroeck, Principles of Semiconductor Devices, http://ecewww.colorado.edu/~bart/book/book/title.htm, ch.4.

Christian Piguet, Leakage in CMOS nanometric technologies, CRC Press, Taylor and Francis Group, pp 3.1-3.17, 2006.

C. Johnson, S. Ogura, J. Riseman, N. Rovedo, J. Shepard, Method for making submicron dimensions in structures using sidewall image transfer

techniques, IBM Technical Disclosure Bulletin 26, 4587 (1984).

C.T. Liu, Circuit requirement and integration challenges of thin gate dielectrics for ultra small MOSFETs, In IEDM Tech. Dig., pp 747-750, 1998.

Farkhanda Ana and Najeeb-ud-din, Suppression of Gate Induced Drain Leakage current (GIDL) by gate work function engineering: analysis and model.

Journal of Electron Devices, Vol. 13, 2012.

Farzan Fallah and Massoud Pedram Standby and Active Leakage Current Control and Minimization in CMOS VLSI Circuits, 2010.

Giorgio Baccarani, A Compact Double-Gate MOSFET Model Comprising Quantum-Mechanical and Nonstatic Effects, IEEE Transactions on Electron

Devices, Vol. 46 (1999).

H.-D. Lee and J.-M. Hwang, "Accurate extraction of reverse leakage current components of shallow silicided p+-n junction for quarter- and subquarter-micron MOSFETs. IEEE Trans. Electron. Devices, Vol.45, August 1998.

H-S. P. Wong et al., Nanoscale CMOS. Proc. IEEE, Vol.87, April 1999.

Jean Pierre Colinge and Cynthia A. Colinge. Physics of Semiconductor Devices, Kluwer Academic, pp 231-233, 2006.

Jean Pierre Colinge FinFETs and Other Multi-Gate Transistors, Springer, 2008.

J. Kedzierski, M. Ieong, E. Nowak, T. S. Kanarsky, Y. Zhang, R. Roy, D.Boyd, D. Fried, H.-S. Wong: Extension and source/drain design for high

performance FinFET devices. IEEE Transaction on Electron Devices, 50-4,952 (2003).

K-f. You and C-Y. Wu, A new quasi -2-D model for hot carrier band to band tunneling current, IEEE Electron Device Lett., vol. 46, June. 1999.

K. Cao, W.-C Lee, W. Liu, X. Jin, P. Su, S. Fung, J. An, B. Yu, and C. Hu, BSIM4 gate leakage model including source drain partition, in Tech. Dig. Int.

Electron Devices Meeting, 2000, pp. 815818.

MATLAB The Language of Technical Computing, the Math works Inc., 1999.

M. Chen, Back-gate bias enhanced band-to-band tunneling leakage in scaled MOSFET, IEEE Electron Device Lett., vol. 19, no. 4, pp. 134136, Apr.

1998.

M. Zakir Hossain, Md.Alamgir Hossain, Md.Saiful Islam, Md. Mijanur Rahman, Mahfuzul Haque Chowdhury , Electrical characteristics of a Trigate

FinFET. Global Journal of Researches in Engineering.Vol.11, 2011.

P.R. Van der Meer, Arthur H.M., Van Roermund, Low Power Deep Sub-micron CMOS Logic: Subthreshold Current Reduction, Springer, pp 83-88,

2004

Semiconductor Industry Association, International Technology Roadmap for Semiconductors, 2003 edition, http://public.itrs.net/.

S.M. Sze, Modern Semiconductor Device Physics, John Wiley & Sons, New York, 1998.

All rights reserved by www.ijste.org

144

Effect of Fin Shape on GIDL and Subthreshold Leakage Currents

(IJSTE/ Volume 1 / Issue 10 / 027)

[26]

T. A. Fjeldly and M. Shur, Threshold voltage modelling and the subthreshold regime of operation of short channel MOSFET's, IEEE

Trans. on Electron Devices, Vol. 40, January 1993.

[27] Vaidy Subramanian, Bertrand Parvais and Jonathan Borremans, Planar Bulk MOSFETS versus FinFETs: An Analog/RF Perspective. IEEE Transactions

on Electron Devices Vol.53 (2006).

[28] W. Xiong, G. Gebara, J. Zaman, M. Gostkowski, B. Nguyen, G. Smith, D. Lewis, C. R.Cleavelin, R. Wise, S.Yu, M. Pas, T.J. King, J.P. Colinge:

Improvement of FinFET electrical characteristics by hydrogen annealing. IEEE Electron Devices Letters 25-8, 541 (2004).

[29] Yang-Kyu Choi, Leland Chang, P. Ranade, Jeong-Soo Lee, Daewon Ha, S. Balasubramanian, A. Agarwal, M. Ameen, Tsu-Jae King, J. Bokor: FinFET

process refinements for improved mobility and gate work function engineering. Technical Digest of the IEDM, 259 (2002).

[30] Y.-K. Choi, T.-J. King, C. Hu: Nanoscale CMOS spacer FinFET for the terabit era. IEEE Electron Device Letters 23-1, 25 (2002).

All rights reserved by www.ijste.org

145

Anda mungkin juga menyukai

- Leakage in Nanometer Scale CMOSDokumen8 halamanLeakage in Nanometer Scale CMOSJimit GadaBelum ada peringkat

- Leakage Power Optimization Using Gate Length Biasing and Multiple VTDokumen13 halamanLeakage Power Optimization Using Gate Length Biasing and Multiple VTSanupKumarSinghBelum ada peringkat

- Research PaperDokumen13 halamanResearch PaperYawar KhurshidBelum ada peringkat

- FinFET Inverter Anlaysis PDFDokumen14 halamanFinFET Inverter Anlaysis PDFRakeshBelum ada peringkat

- FinfetsDokumen27 halamanFinfetsAjay JoshyBelum ada peringkat

- Leakage Control For Deep-Submicron Circuits: Kaushik Roy, Hamid Mahmoodi-Meimand, and Saibal MukhopadhyayDokumen12 halamanLeakage Control For Deep-Submicron Circuits: Kaushik Roy, Hamid Mahmoodi-Meimand, and Saibal MukhopadhyayDebbrat GhoshBelum ada peringkat

- Performance Improvement of FinFET Using Nitride SpacerDokumen3 halamanPerformance Improvement of FinFET Using Nitride SpacerseventhsensegroupBelum ada peringkat

- A Study On Multi Material Gate All Around SOI MOSFETDokumen5 halamanA Study On Multi Material Gate All Around SOI MOSFETeditor_ijtelBelum ada peringkat

- GIDLDokumen4 halamanGIDLTnSharmaBelum ada peringkat

- Review of Junctionless Transistors and Their ClassificationDokumen22 halamanReview of Junctionless Transistors and Their Classificationmanurudin2Belum ada peringkat

- Leakage Current PaperDokumen23 halamanLeakage Current Paperkeshav rocksBelum ada peringkat

- 10 1016@j Aeue 2019 06 017Dokumen9 halaman10 1016@j Aeue 2019 06 017riya pc02Belum ada peringkat

- Double Gate MosDokumen21 halamanDouble Gate MosdayaBelum ada peringkat

- Finfet: Soi and The Non-Planar Finfet DeviceDokumen34 halamanFinfet: Soi and The Non-Planar Finfet Devicesandeeppareek926100% (1)

- Punch ThroughDokumen2 halamanPunch ThroughmodivivekBelum ada peringkat

- Transistor Staking EffectDokumen6 halamanTransistor Staking Effectpramod_scribdBelum ada peringkat

- AN211 FET Teory and PracticeDokumen12 halamanAN211 FET Teory and PracticefabirznBelum ada peringkat

- Variations Gobal LoacalDokumen11 halamanVariations Gobal LoacalPullareddy AvulaBelum ada peringkat

- Review of Modern Field Effect Transistor Technologie1Dokumen8 halamanReview of Modern Field Effect Transistor Technologie1G ManBelum ada peringkat

- Scaling of MOSFETs and Short Channel EffectsDokumen35 halamanScaling of MOSFETs and Short Channel EffectsAnonymous zn5X2z0% (1)

- Chap6-Very Fast TransientsDokumen24 halamanChap6-Very Fast TransientshhipowerBelum ada peringkat

- Junctionless TransistorsDokumen2 halamanJunctionless TransistorslutfiBelum ada peringkat

- Manuscript 167 OldDokumen6 halamanManuscript 167 Oldsudipta2580Belum ada peringkat

- Design and Implementation of 4-Bit Alu Using Finfet TechnologyDokumen12 halamanDesign and Implementation of 4-Bit Alu Using Finfet TechnologyDinesh Kumar J RBelum ada peringkat

- Researsh ProposalDokumen2 halamanResearsh ProposalEr Paramjit SinghBelum ada peringkat

- (SOI) Technology Have Emerged As An Efective Means of ExtendingDokumen38 halaman(SOI) Technology Have Emerged As An Efective Means of ExtendingShwetaAgarwalBelum ada peringkat

- Seminar Report On FinFETDokumen25 halamanSeminar Report On FinFETaajsaj60% (5)

- Threshold Voltage Control Schemes in FinfetsDokumen17 halamanThreshold Voltage Control Schemes in FinfetsAnonymous e4UpOQEPBelum ada peringkat

- Trends in IC TechnologyDokumen26 halamanTrends in IC Technologyhale_209031335Belum ada peringkat

- Ece-Research Work 1Dokumen10 halamanEce-Research Work 1Peale ObiedoBelum ada peringkat

- 1.1 Scaling of Bulk CmosDokumen16 halaman1.1 Scaling of Bulk CmosVineetha UmeshBelum ada peringkat

- Subthreshold Condition in Mosfet: EPRA International Journal of Research and Development (IJRD)Dokumen7 halamanSubthreshold Condition in Mosfet: EPRA International Journal of Research and Development (IJRD)electro maniaBelum ada peringkat

- Mesfet 1Dokumen25 halamanMesfet 1Kiran KirruBelum ada peringkat

- Impact of Process Variation On Electrical Characteristics of 22Nm FinfetDokumen7 halamanImpact of Process Variation On Electrical Characteristics of 22Nm FinfetDamodar SurisettyBelum ada peringkat

- EI2301-IE - Unit 1 - Part A and Part B - With Answers PDFDokumen21 halamanEI2301-IE - Unit 1 - Part A and Part B - With Answers PDFsartpgitBelum ada peringkat

- Aip Adv TfetDokumen10 halamanAip Adv TfetAnik PaulBelum ada peringkat

- Workfunction, Hfin, L, Wfin, Tox, Temperature 20nm IonDokumen5 halamanWorkfunction, Hfin, L, Wfin, Tox, Temperature 20nm IonAnala MBelum ada peringkat

- Lec14 DTMOSDokumen88 halamanLec14 DTMOSSalim SanBelum ada peringkat

- Superlattices and Microstructures 77 (2015) 209-218Dokumen10 halamanSuperlattices and Microstructures 77 (2015) 209-218Avi JainBelum ada peringkat

- Advantages of near-threshold computingDokumen1 halamanAdvantages of near-threshold computingMuhammad FaisalBelum ada peringkat

- Malvika2022 Article AReviewOnANegativeCapacitanceFDokumen15 halamanMalvika2022 Article AReviewOnANegativeCapacitanceFMD Salim EqubalBelum ada peringkat

- Ijest12 04 05 285Dokumen7 halamanIjest12 04 05 285Vijay Kumar PulluriBelum ada peringkat

- Leakage Minimization Technique For Nanoscale Cmos Vlsi: Ecause of TheDokumen9 halamanLeakage Minimization Technique For Nanoscale Cmos Vlsi: Ecause of TheSdBelum ada peringkat

- Fermi FET Technology Seminar ReportDokumen21 halamanFermi FET Technology Seminar Reportimcoolsha999Belum ada peringkat

- Metal Semiconductor FET MESFETDokumen26 halamanMetal Semiconductor FET MESFETsrinathBelum ada peringkat

- Module-2 Fets:: Importance of Fets (Motivation)Dokumen22 halamanModule-2 Fets:: Importance of Fets (Motivation)rajuBelum ada peringkat

- GIS Vs AISDokumen6 halamanGIS Vs AISabhi_akBelum ada peringkat

- Effect of Thickness Variation On Electrical Characteristics of Single & Dual Gate Organic Thin Film TransistorsDokumen5 halamanEffect of Thickness Variation On Electrical Characteristics of Single & Dual Gate Organic Thin Film TransistorsIRJIEBelum ada peringkat

- 1 s2.0 S2589208821000132 MainDokumen8 halaman1 s2.0 S2589208821000132 MainEvent DecemberBelum ada peringkat

- New Reliability Issues of CMOS Transistors With 1.3nm Thick Gate OxideDokumen1 halamanNew Reliability Issues of CMOS Transistors With 1.3nm Thick Gate OxideRamprasad PoluruBelum ada peringkat

- Dančak2018 Chapter TheFinFETATutorialDokumen33 halamanDančak2018 Chapter TheFinFETATutorialAhmed KamalBelum ada peringkat

- 279 E317 PDFDokumen6 halaman279 E317 PDFJubin JainBelum ada peringkat

- Low Power Design and Simulation of 7T SRAM Cell Using Various Circuit TechniquesDokumen6 halamanLow Power Design and Simulation of 7T SRAM Cell Using Various Circuit TechniquesseventhsensegroupBelum ada peringkat

- Transformable Junctionless Transistor (T-JLT)Dokumen6 halamanTransformable Junctionless Transistor (T-JLT)Rakesh KumarBelum ada peringkat

- California Eastern Laboratories: Application of Microwave Gaas FetsDokumen27 halamanCalifornia Eastern Laboratories: Application of Microwave Gaas FetsJ Jesús Villanueva GarcíaBelum ada peringkat

- Chapter 5-Metal Semiconductor FET (MESFET)Dokumen26 halamanChapter 5-Metal Semiconductor FET (MESFET)mdhuBelum ada peringkat

- Impact of ProcessDokumen8 halamanImpact of ProcesseleenaamohapatraBelum ada peringkat

- MOS Integrated Circuit DesignDari EverandMOS Integrated Circuit DesignE. WolfendaleBelum ada peringkat

- Signal Integrity: From High-Speed to Radiofrequency ApplicationsDari EverandSignal Integrity: From High-Speed to Radiofrequency ApplicationsBelum ada peringkat

- Optimization of Overall Efficiency Using Facilities Planning in Ropp Cap Making IndustryDokumen8 halamanOptimization of Overall Efficiency Using Facilities Planning in Ropp Cap Making IndustryIJSTEBelum ada peringkat

- Design and Analysis of Magneto Repulsive Wind TurbineDokumen7 halamanDesign and Analysis of Magneto Repulsive Wind TurbineIJSTEBelum ada peringkat

- FPGA Implementation of High Speed Floating Point Mutliplier Using Log Based DesignDokumen4 halamanFPGA Implementation of High Speed Floating Point Mutliplier Using Log Based DesignIJSTEBelum ada peringkat

- Development of Relationship Between Saturation Flow and Capacity of Mid Block Section of Urban Road - A Case Study of Ahmedabad CityDokumen6 halamanDevelopment of Relationship Between Saturation Flow and Capacity of Mid Block Section of Urban Road - A Case Study of Ahmedabad CityIJSTEBelum ada peringkat

- A Cloud Based Healthcare Services For Remote PlacesDokumen4 halamanA Cloud Based Healthcare Services For Remote PlacesIJSTEBelum ada peringkat

- Automatic Generation Control in Three-Area Power System Operation by Using "Particle Swarm Optimization Technique"Dokumen8 halamanAutomatic Generation Control in Three-Area Power System Operation by Using "Particle Swarm Optimization Technique"IJSTEBelum ada peringkat

- Partial Replacement of Fine Aggregate With Iron Ore Tailings and Glass PowderDokumen7 halamanPartial Replacement of Fine Aggregate With Iron Ore Tailings and Glass PowderIJSTEBelum ada peringkat

- Effect of RIB Orientation in Isogrid Structures: Aerospace ApplicationsDokumen9 halamanEffect of RIB Orientation in Isogrid Structures: Aerospace ApplicationsIJSTEBelum ada peringkat

- Multipurpose Scheme of Workshop Exhaust System For Ventilation and Electrical Power GenerationDokumen9 halamanMultipurpose Scheme of Workshop Exhaust System For Ventilation and Electrical Power GenerationIJSTEBelum ada peringkat

- RFID Based Toll Gate AccessDokumen5 halamanRFID Based Toll Gate AccessIJSTEBelum ada peringkat

- Optimization of Treatability by FACCO For Treatment of Chemical Industry EffluentDokumen9 halamanOptimization of Treatability by FACCO For Treatment of Chemical Industry EffluentIJSTEBelum ada peringkat

- A Mixture of Experts Model For ExtubationDokumen4 halamanA Mixture of Experts Model For ExtubationIJSTEBelum ada peringkat

- Comparative Study and Analysis of PCC Beam and Reinforced Concrete Beam Using GeogridDokumen7 halamanComparative Study and Analysis of PCC Beam and Reinforced Concrete Beam Using GeogridIJSTEBelum ada peringkat

- Enriching Gum Disease Prediction Using Machine LearningDokumen6 halamanEnriching Gum Disease Prediction Using Machine LearningIJSTEBelum ada peringkat

- A Comprehensive Survey of Techniques/Methods For Content Based Image Retrieval SystemDokumen6 halamanA Comprehensive Survey of Techniques/Methods For Content Based Image Retrieval SystemIJSTEBelum ada peringkat

- Optimizing Turning Process For EN43 by Taguchi Method Under Various Machining ParametersDokumen4 halamanOptimizing Turning Process For EN43 by Taguchi Method Under Various Machining ParametersIJSTEBelum ada peringkat

- The Bicycle As A Mode Choice - A Gendered ApproachDokumen4 halamanThe Bicycle As A Mode Choice - A Gendered ApproachIJSTEBelum ada peringkat

- Optimum Placement of DG Units Using CPF MethodDokumen6 halamanOptimum Placement of DG Units Using CPF MethodIJSTEBelum ada peringkat

- Interstage Construction Techniques For Mass Gain: An OverviewDokumen5 halamanInterstage Construction Techniques For Mass Gain: An OverviewIJSTEBelum ada peringkat

- An Implementation and Design A Customized Advanced Image Editor Using Image Processing in MatlabDokumen5 halamanAn Implementation and Design A Customized Advanced Image Editor Using Image Processing in MatlabIJSTEBelum ada peringkat

- Onerider The Bike TaxiDokumen3 halamanOnerider The Bike TaxiIJSTEBelum ada peringkat

- A Radar Target Generator For Airborne TargetsDokumen8 halamanA Radar Target Generator For Airborne TargetsIJSTEBelum ada peringkat

- App-Based Water Tanker Booking, Monitoring & Controlling SystemDokumen6 halamanApp-Based Water Tanker Booking, Monitoring & Controlling SystemIJSTEBelum ada peringkat

- Using The Touch-Screen Images For Password-Based Authentication of IlliteratesDokumen6 halamanUsing The Touch-Screen Images For Password-Based Authentication of IlliteratesIJSTEBelum ada peringkat

- Research On Storage Privacy Via Black Box and Sanitizable SignatureDokumen6 halamanResearch On Storage Privacy Via Black Box and Sanitizable SignatureIJSTEBelum ada peringkat

- Wireless Information Process and Power Transfer in Single-User OFDM SystemDokumen6 halamanWireless Information Process and Power Transfer in Single-User OFDM SystemIJSTEBelum ada peringkat

- Duplicate Detection Using AlgorithmsDokumen3 halamanDuplicate Detection Using AlgorithmsIJSTEBelum ada peringkat

- Technology Advancement For Abled PersonDokumen9 halamanTechnology Advancement For Abled PersonIJSTEBelum ada peringkat

- An Implementation of Maximum Power Point Tracking Algorithms For Photovoltaic Systems Using Matlab and Arduino Based RTOS SystemDokumen5 halamanAn Implementation of Maximum Power Point Tracking Algorithms For Photovoltaic Systems Using Matlab and Arduino Based RTOS SystemIJSTEBelum ada peringkat

- Plinth Beams DesignDokumen24 halamanPlinth Beams DesignRathinavel VenkateshwaranBelum ada peringkat

- Grade Markings For Steel Bolts and ScrewsDokumen3 halamanGrade Markings For Steel Bolts and Screwsrexie2canos8964Belum ada peringkat

- Steam TableDokumen1 halamanSteam TableKrismawan Saptya YudhaBelum ada peringkat

- Reinforcing Method of Rock Slope Using FRP PipeDokumen8 halamanReinforcing Method of Rock Slope Using FRP PipeA.Subin DasBelum ada peringkat

- Product Key MX - Magnet PermanentDokumen4 halamanProduct Key MX - Magnet PermanentFooBelum ada peringkat

- Advance StructuresDokumen6 halamanAdvance StructuresManju NishaBelum ada peringkat

- Flexural beam design calculationDokumen17 halamanFlexural beam design calculationReceb AgaBelum ada peringkat

- Insulators, Conductors and Semiconductors (With Band Diagram) - StudyElectrical - Online Electrical Engineering Study Site PDFDokumen3 halamanInsulators, Conductors and Semiconductors (With Band Diagram) - StudyElectrical - Online Electrical Engineering Study Site PDFGoutham DevisettyBelum ada peringkat

- Agitation and Mixing of Fluids: Dr. Vimal Gandhi Department of Chemical Engineering, D.D.University, NadiadDokumen112 halamanAgitation and Mixing of Fluids: Dr. Vimal Gandhi Department of Chemical Engineering, D.D.University, NadiadmanankBelum ada peringkat

- Thermodynamics Lab Report - Application of The Perfect Gas Laws in The Determination of Adiabatic Index of AirDokumen9 halamanThermodynamics Lab Report - Application of The Perfect Gas Laws in The Determination of Adiabatic Index of Airqiaunus69% (13)

- Shell Thickness Calculation ..: MAWP Design PressureDokumen6 halamanShell Thickness Calculation ..: MAWP Design PressureSatish ShindeBelum ada peringkat

- Lect 3 Forging PDFDokumen21 halamanLect 3 Forging PDFأحمد قطيمBelum ada peringkat

- Som Unit - 1.2.1 Stepped Bar 3 Regions ProblemDokumen2 halamanSom Unit - 1.2.1 Stepped Bar 3 Regions ProblemNagamani ArumugamBelum ada peringkat

- Sifat KoligatifDokumen12 halamanSifat Koligatiflilik supriantiBelum ada peringkat

- Difference Between NM3 and M3 UnitsDokumen2 halamanDifference Between NM3 and M3 UnitsBkhari HaranBelum ada peringkat

- 6 Unrestrained Beams - 2011 (Compatibility Mode)Dokumen21 halaman6 Unrestrained Beams - 2011 (Compatibility Mode)susan87Belum ada peringkat

- PHASE-EQUILIBRIUM-CORROSIONDokumen5 halamanPHASE-EQUILIBRIUM-CORROSIONPrabhanshu PareBelum ada peringkat

- Mechanical Strength AgaroseDokumen9 halamanMechanical Strength AgaroseHyunjung KimBelum ada peringkat

- Chapter 4 Optical ReceiversDokumen49 halamanChapter 4 Optical ReceiversNguyễnMinhTháiBelum ada peringkat

- Concrete Slab Load Calculation PDFDokumen54 halamanConcrete Slab Load Calculation PDFEddie TaiBelum ada peringkat

- 20 Things You Can Do With Graphene: ApplicationsDokumen4 halaman20 Things You Can Do With Graphene: ApplicationsEmilio Lecaros BustamanteBelum ada peringkat

- Time Table Spring 2024Dokumen7 halamanTime Table Spring 2024Dev JariwalaBelum ada peringkat

- CH 206 Tutorial 7 SolutionsDokumen14 halamanCH 206 Tutorial 7 SolutionspushkalBelum ada peringkat

- Energy Dissipation Capacity of Flexure-Dominated Reinforced Concrete MembersDokumen12 halamanEnergy Dissipation Capacity of Flexure-Dominated Reinforced Concrete Members01010Belum ada peringkat

- Janssens BCC09 PaperDokumen11 halamanJanssens BCC09 PaperVyto BabrauskasBelum ada peringkat

- The Influence of Grain Size On The Tensile and Fatigue Behavior of 7075 t6 Aluminum SheetDokumen8 halamanThe Influence of Grain Size On The Tensile and Fatigue Behavior of 7075 t6 Aluminum SheetHoai Anh VuBelum ada peringkat

- Soil Lab CBRDokumen24 halamanSoil Lab CBRObey mubonderiBelum ada peringkat

- Ray Optics - DPP 10 (Of Lec 14) - (Lakshya JEE 2023)Dokumen3 halamanRay Optics - DPP 10 (Of Lec 14) - (Lakshya JEE 2023)rambhaiya888Belum ada peringkat

- Table List of Tests Correlations of Soil and Rock Properties in Geotechnical EngineeringDokumen1 halamanTable List of Tests Correlations of Soil and Rock Properties in Geotechnical EngineeringTomasz CzBelum ada peringkat

- The Performance Pipe Engineering ManualDokumen208 halamanThe Performance Pipe Engineering Manualpca97100% (2)