MOSFET Amplificadores

Diunggah oleh

David Santiago Daza QuirogaDeskripsi Asli:

Judul Asli

Hak Cipta

Format Tersedia

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniHak Cipta:

Format Tersedia

MOSFET Amplificadores

Diunggah oleh

David Santiago Daza QuirogaHak Cipta:

Format Tersedia

UNIVERSIDAD NACIONAL DE COLOMBIA, BOGOT D.C.

Prctica 8: Transistor MOSFET en circuitos

amplificadores

David Santiago Daza Quiroga dsdazaq@unal.edu.co, Fabian Hernan Villegas Manrique

fahvillegasm@unal.edu.co, Nicolas Moreno Franco jnmorenofr@unal.edu.co

AbstractSignal amplifiers are the basic applications we

have for a MOSFET transistor, thus the need to analyze and

understand how it works as they are critical in more complex

structures. A study conducted in this laboratory report.

Index TermsMOSFET, Zone of saturation, Amplifier, Common source, Common drain, Source follower.

I. INTRODUCCIN

N el presente informe se muestran los resultados

obtenidos durante la prctica de laboratorio en la cual se

realiz la verificacin del comportamiento de algunos tipos

de amplificadores, y el anlisis de los mismos, tambin se

comprueba el comportamiento de una fuente de corriente de

espejo sometido a distintas cargas.

En concreto se estudiar el amplificador de fuente comn y

de drenaje comn, as como la resultante de su combinacin

en serie.

II. MARCO TERICO

Entre los tipos de amplificadores bsicos que tenemos para

dispositivos MOSFET, tenemos el fuente comn y el drenaje

comn o seguidor de fuente.

Figura 2.1.2. Modelo de pequea seal amplificador fuente

comn [2].

De donde tenemos las relaciones:

Av =

Ai =

vout

= gm(go1 ||RD ||RL )

vin

(R1||R2)

Zin

Iout

Av =

gm(go1 ||RD ||RL )

=

Iin

RL

RL

Para esta configuracin se obtienen valores altos de ganancia

(mayor a 1) para la seal de entrada, ya sea de tensin o de

corriente.

B. Amplificador de Drenaje Comn o Seguidor de Voltaje

El esquema general puede verse en la figura 2.2.1.

A. Amplificador de Fuente Comn

Figura 2.2.1. Amplificador seguidor de voltaje [3].

Figura 2.1.1. Amplificador fuente comn [1].

Su modelo de pequea seal puede verse en la figura 2.1.2.

El correspondiente modelo de pequea seal puede verse

en la figura 2.2.2.

UNIVERSIDAD NACIONAL DE COLOMBIA, BOGOT D.C.

Figura 3.2. Circuito 1, Fuente de corriente espejo [5].

Figura 2.2.2. Modelo de pequea seal amplificador seguidor

de voltaje [4].

Posteriormente se realiz el montaje del circuito 2 con

valores para R1 = 12.5M, R2 = 3.7M, RD = 10.2 k,

RS = 600, C1= C2 = CS = 1 F, RL = 10 k, Vipp = 200

mV a una frecuencia de 10 kHz y VDD = 20 V.

III. PROCEDIMIENTO

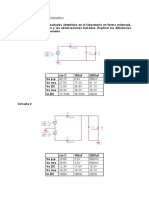

De acuerdo a clculos previos, para la fuente de corriente

del esquema del circuito 1, se us una resistencia de referencia

de 6.12 k, un valor para VDD = 10V usando del chip

CD4007CN nicamente las compuertas NMOS.

Variando RL desde 0 hasta 10 k, se obtuvo la siguiente

tabla de datos.

TABLA I

IQ2 VS RL CIRCUITO 1

RL[k]

IQ1 [mA] IQ2 [mA]

10

1.05

0.872

9

1.05

0.934

8

1.05

0.988

7

1.05

1.02

6

1.05

1.06

5

1.05

1.1

4

1.05

1.14

3

1.05

1.18

2

1.05

1.23

1

1.05

1.28

0.1

1.05

1.34

Tabla 3.1. Toma de datos.

Y la correspondiente grfica.

Figura 3.1. Variacin de la corriente respecto a RL en el

circuito 1.

Figura 3.3. Circuito 2, Amplificador de fuente comn [6].

Bajo los valores iniciales encontramos una salida V0pp =

1 V, obteniendo una ganancia aproximada Av = 5. Luego

variamos la frecuencia para la seal de entrada con lo cual

obtuvimos la siguiente tabla.

TABLA II

AV VARIANDO FRECUENCIA DE VI

f[KHz]

0,1

1

10

100

500

1000

V0 [mVp] 321.5

479

500

500

500

489,03

V

AV [ V

3,21

4,79

5

5

5

4,93

]

Tabla 3.2. Toma de datos.

Figura 3.4. Circuito 2, Amplificacin de fuente comn.

UNIVERSIDAD NACIONAL DE COLOMBIA, BOGOT D.C.

Los valores medidos de este circuito son V0pp = 787 mV

con una ganancia de Av = 3.93 V/V.

Igual que en el caso anterior, variamos la frecuencia de la

seal de entrada, cuyos resultados estn consignados en la

siguiente tabla.

Figura 3.5. Transferencia de tensiones.

Inmediatamente se procedi a hacer el montaje del circuito

3 mostrado en la figura 8, con los valores para los componentes

iguales a los del circuito 2 de fuente comn.

f[KHz]

V0 [mV]

AV [ V

]

V

TABLA III

AV VARIANDO FRECUENCIA DE VI

0,1

1

10

100

500

391,02

395

392.55

372.74

329,65

3.91

3,95

3,92

3,72

3,21

Tabla 3.3. Toma de datos.

1000

329,45

3,21

Finalmente para el montaje del circuito 4 con valores de C1

= C2 = C3 = 1 F, R1 =1k, RD = RS = RL = 220 , R2 =

3 k, VDD = 20 V y Vipp = 400 mV a una frecuencia de 10

kHz se obtuvo una salida V0pp = 162 mV con una ganancia

de Av = 0,405 V/V.

Figura 3.6. Circuito 3, Amplificador de fuente comn

Degenerado [7].

Figura 3.9. Circuito 4, Amplificador de Drenaje comn [8].

Variando la frecuencia en la seal de entrada obtenemos los

valores de la siguiente tabla.

Figura 3.7. Circuito 3, Amplificacin de fuente comn

degenerado.

Figura 3.8. Transferencia de tensiones.

TABLA IV

AV VARIANDO FRECUENCIA DE VI

f[KHz]

0,1

1

10

100

500

V0 [mVp]

6.7

70.9

79.9

81

81

V

]

AV [ V

0,033

0,355

0,399

0,405

0,405

Tabla 3.4. Toma de datos.

1000

81

0,405

Figura 3.10. Circuito 4, Amplificacin drenaje comn.

UNIVERSIDAD NACIONAL DE COLOMBIA, BOGOT D.C.

V. PREGUNTAS

A. A qu se debe el hecho de que la resistencia de carga de

las fuentes de corriente deba estar en un rango determinado de

valores, o de lo contrario no se garantizar el funcionamiento

como espejo de corriente?

Figura 3.11. Transferencia de tensiones.

Finalmente, uniendo los circuitos de fuente comn y drenaje

comn como lo ilustra el esquema del circuito 5, y con los

valores para los elementos ya utilizados, tenemos V0pp = 70

mV con una ganancia de Av = 0,35 V/V.

Al aumentar el valor de la resistencia de carga con valores

muy altos respecto al valor de referencia, la corriente a travs

del transistor disminuye drsticamente afectando la eficiencia

de la fuente de corriente para el valor calculado.

Dado que la resistencia de referencia no es alterada, se

garantiza que los transistores siempre estn en saturacin, por

tanto el aumento de la resistencia de carga hace que la fuente

que alimenta la configuracin no posea la suficiente potencia

para suplir los requerimientos cada vez mayores de corriente

que exige la carga.

Por lo anterior se puede considerar una fuente de corriente

ideal para valores de carga menores a 8 k, en donde la

corriente es constante de 1 mA.

B. Describa la transicin del transistor Q1 (fuentes de corriente en espejo) a travs de las regiones de operacin del

Mosfet, conforme la resistencia RL aumenta desde RL = 0

hasta RL

Figura 3.12. Circuito 5, Amplificacin en cascada.

IV. ANLISIS

El circuito 1, la fuente de corriente, al variar RL como

lo muestra la TABLA 3.1 y la grfica correspondiente, se

deduce que dicha corriente disminuye para valores superiores

para RL a los 8 k, alejndose del valor ideal de 1 mA. Por

tanto RL no debe superar los 8 k.

En el circuito 2 tenemos Zi = R1 || R2, Zi = 2.85 M, Zo

= RL || RD, Zo = 5.05 k.

La tabla de variacin de frecuencias de entrada para el

circuito 3.2 devela que no incide en la ganancia de respuesta

del circuito ya que se mantiene en valores muy estables y

cercanos entre s.

Para el circuito 3 tenemos Zi = R1 || R2, Zi = 2,85 M,

Zo = RL || RD, Zo = 5.05 k.

Los transistores siempre estarn en saturacin por tanto

tendr un comportamiento constante de 1 mA hasta la carga

mxima soportada, en donde empezar a decaer la corriente

con el aumento de la carga.

Lo anterior implica la determinacin previa de valores y

seleccin del transistor en funcin de la corriente esperada y

la carga mxima a soportar.

C. Describa el comportamiento real de los circuitos amplificadores en funcin de la frecuencia de trabajo y explique en

sus propias palabras a que se puede deber este fenmeno

Dada la evidencia encontrada, no podemos inferir variaciones importantes en relacin a la ganancia de los distintos

amplificadores dado por la variacin de la frecuencia de la

seal.

En el circuito 4 tenemos Zi = R1 || R2, Zi = 750 , Zo =

RL || RS, Zo = 110 .

D. Basado en la teora y en los diseos realizados, realice

una breve descripcin de las ventajas, desventajas y posibles

escenarios de aplicacin, para cada una de las cuatro configuraciones de amplificadores trabajadas. Tenga en cuenta

aspectos como ganancia, frecuencia de trabajo y limitaciones

de pequea seal, impedancias de entrada y salida, entre

otros.

Al variar la frecuencia de entrada no se evidencia variacin

en la relacin de ganancia del circuito.

La configuracin de fuente comn ofrece impedancias de

entradas altas y de salidas bajas, y una ganancia alta aunque

la salida est invertida respecto a la seal de entrada.

Finalmente con el circuito 5, como la unin de los circuitos

2 y 4, se encontr que su ganancia de 0,35 V/V.

Los amplificadores de drenaje comn tambin llamados

seguidor de tensin se utilizan generalmente para acoples de

Al variar la frecuencia, de forma semejante al caso

anterior, no se devela incidencia en la variacin de la

ganancia, permaneciendo constante dentro de la gama de

frecuencias.

UNIVERSIDAD NACIONAL DE COLOMBIA, BOGOT D.C.

impedancias.

El circuito combinado ltimo en su fase inicial amplifica

una seal de tensin que en su segunda parte procurar

entregar de la forma ms limpia a travs del drenaje comn.

VI. CONCLUSIONES

La potencialidad de un elemento no radica necesariamente en la complejidad de su funcionalidad, puede ser

una cualidad que logre emerger gracias al ingenio de

quien cree sus posibilidades. Ejemplos claros son la rueda

y los semiconductores; en su sencillez se fundamenta

nuestro pasado, presente y futuro.

En el anlisis de circuitos es prctico y eficiente recurrir

a modelos ideales de comportamiento para los distintos

elementos, sin embargo no hay que olvidar que para

su implementacin real es necesario nuevamente realizar

dichos anlisis con parmetros reales.

Analizar un elemento de un circuito con modelos

matemticos ms precisos (como el diodo) puede ser

complejo, an ms si se combinan varios elementos en

distintas configuraciones, por ello, el uso de un buen

software de simulacin puede ser de gran utilidad, ahorrando esfuerzo, tiempo y evitando el error humano en la

ejecucin lineal de clculos.

VII. REFERENCIAS

[1] Francisco J. Franco P. AMPLIFICADORES DE

ENTRADA SIMPLE [Online]. Pgina: 17. Tomada de:

https://cv3.sim.ucm.es/access/content/group/portal-uatducma43/webs/material_original/apuntes/PDF/04_amplificadores_ent

rada_simple.pdf

[2] Francisco J. Franco P. AMPLIFICADORES DE

ENTRADA SIMPLE [Online]. Pgina: 16. Tomada de:

https://cv3.sim.ucm.es/access/content/group/portal-uatducma43/webs/material_original/apuntes/PDF/04_amplificadores_ent

rada_simple.pdf

[3] Francisco J. Franco P. AMPLIFICADORES DE

ENTRADA SIMPLE [Online]. Pgina: 37. Tomada de:

https://cv3.sim.ucm.es/access/content/group/portal-uatducma43/webs/material_original/apuntes/PDF/04_amplificadores_ent

rada_simple.pdf

[4] Francisco J. Franco P. AMPLIFICADORES DE

ENTRADA SIMPLE [Online]. Pgina: 39. Tomada de:

https://cv3.sim.ucm.es/access/content/group/portal-uatducma43/webs/material_original/apuntes/PDF/04_amplificadores_en

trada_simple.pdf

[5] Jair F. Ladino M. Transistor MOSFET en

circuitos amplificadores [online]. Pgina: 2. Tomada de:

https://drive.google.com/viewerng/viewer?a=v&pid=sites&srci

d=ZGVmYXVsdGRvbWFpbnxlbGVjdHJvbmljYWFuYWx

vZ2F1bmFsfGd4OjE0YmE1NGRhMDYzNDljYjI&u=0

[6] Jair F. Ladino M. Transistor MOSFET en

circuitos amplificadores [online]. Pgina: 3. Tomada de:

https://drive.google.com/viewerng/viewer?a=v&pid=sites&srci

d=ZGVmYXVsdGRvbWFpbnxlbGVjdHJvbmljYWFuYWx

vZ2F1bmFsfGd4OjE0YmE1NGRhMDYzNDljYjI&u=0

[7] Jair F. Ladino M. Transistor MOSFET en

circuitos amplificadores [online]. Pgina: 3. Tomada de:

https://drive.google.com/viewerng/viewer?a=v&pid=sites&srci

d=ZGVmYXVsdGRvbWFpbnxlbGVjdHJvbmljYWFuYWx

vZ2F1bmFsfGd4OjE0YmE1NGRhMDYzNDljYjI&u=0

[8] Jair F. Ladino M. Transistor MOSFET en

circuitos amplificadores [online]. Pgina: 4. Tomada de:

https://drive.google.com/viewerng/viewer?a=v&pid=sites&srci

d=ZGVmYXVsdGRvbWFpbnxlbGVjdHJvbmljYWFuYWx

vZ2F1bmFsfGd4OjE0YmE1NGRhMDYzNDljYjI&u=0

Anda mungkin juga menyukai

- Armónicas en Sistemas Eléctricos IndustrialesDari EverandArmónicas en Sistemas Eléctricos IndustrialesPenilaian: 4.5 dari 5 bintang4.5/5 (12)

- Rectificador trifásico onda completaDokumen6 halamanRectificador trifásico onda completaIsaac MedinaBelum ada peringkat

- Montaje y mantenimiento de transformadores. ELEE0109Dari EverandMontaje y mantenimiento de transformadores. ELEE0109Belum ada peringkat

- Informe Practica 2 Electronica Analoga 2Dokumen7 halamanInforme Practica 2 Electronica Analoga 2Marco Hernandez GomezBelum ada peringkat

- Informe 6 Mosfet IntDokumen4 halamanInforme 6 Mosfet Intwsosornoz100% (1)

- Informe8 - Amplificador Con Transistores en CascadaDokumen3 halamanInforme8 - Amplificador Con Transistores en CascadajulalbrinconBelum ada peringkat

- Práctica 5 Colector ComunDokumen14 halamanPráctica 5 Colector ComunRamiro Avalos VegaBelum ada peringkat

- Informe de Laboratorio de Circuitos DobladoresDokumen9 halamanInforme de Laboratorio de Circuitos Dobladoressagallardo9Belum ada peringkat

- LABORATORIO 3 AnalogaDokumen6 halamanLABORATORIO 3 AnalogaEsteban MaldonadoBelum ada peringkat

- Semiconductores Laboratorio NDokumen8 halamanSemiconductores Laboratorio NJackCastroBelum ada peringkat

- Rectificadores de Media Onda y Onda CompletaDokumen12 halamanRectificadores de Media Onda y Onda CompletaGabriel Barreda Zegarra93% (28)

- 3ER FinalDokumen8 halaman3ER FinalJhon Alex López SotoBelum ada peringkat

- Lab. Circuitos Electronicos I - 4. - Rectificadores y FiltrosDokumen26 halamanLab. Circuitos Electronicos I - 4. - Rectificadores y FiltrosChristiam Paul Ramírez80% (5)

- Amp Con Opreracional y Salida CuasicomplementarioDokumen79 halamanAmp Con Opreracional y Salida CuasicomplementarioFabio LopezBelum ada peringkat

- Informe Previo Laboratorio NDokumen5 halamanInforme Previo Laboratorio Npagedpiero100% (1)

- Lab2 Is411Dokumen13 halamanLab2 Is411wilhen umañaBelum ada peringkat

- Lab 3Dokumen11 halamanLab 3ROSAS MONTALVO JESUSBelum ada peringkat

- Informe de Laboratorio Electronica Analoga 2Dokumen6 halamanInforme de Laboratorio Electronica Analoga 2Älvärö ÄndrësBelum ada peringkat

- Practica No.4 Base ComúnDokumen5 halamanPractica No.4 Base ComúnTania TorresBelum ada peringkat

- Informe Fuente de Corriente Transistores Mosfet (Tipo P)Dokumen3 halamanInforme Fuente de Corriente Transistores Mosfet (Tipo P)Juan Antonio BarraganBelum ada peringkat

- Laboratorio 03Dokumen11 halamanLaboratorio 03Pool Nolasco RamirezBelum ada peringkat

- Electronica AnalogicaDokumen14 halamanElectronica AnalogicamarcocapitanoBelum ada peringkat

- Rectificadores de Media Onda y Onda CompletaDokumen13 halamanRectificadores de Media Onda y Onda CompletajohnBelum ada peringkat

- Rectificador Onda Completa TrifásicoDokumen13 halamanRectificador Onda Completa TrifásicopprootsBelum ada peringkat

- 8 Caracteristicas Circuito Integrador y DiferenciadorDokumen16 halaman8 Caracteristicas Circuito Integrador y DiferenciadorRicardo Alcántara CamposBelum ada peringkat

- Informe Final Laboratorio #7 Circuito RLCDokumen15 halamanInforme Final Laboratorio #7 Circuito RLCMaerElectronicaBelum ada peringkat

- Final Lab 7 - C.EDokumen10 halamanFinal Lab 7 - C.EJesus QVasquezBelum ada peringkat

- Laboratorio Amplificador Con BJTDokumen14 halamanLaboratorio Amplificador Con BJTTextos de Ingenieria100% (6)

- Practica - 6 Mosfet Como InterruptorDokumen4 halamanPractica - 6 Mosfet Como InterruptorAlejandro Marin100% (1)

- Electronica R3Dokumen24 halamanElectronica R3ASEGRE S.A de C.V.Belum ada peringkat

- Electronicos 2 Laboratorio 3Dokumen8 halamanElectronicos 2 Laboratorio 3Tumblin OrangeBelum ada peringkat

- Transistores BJT Con MatlabDokumen26 halamanTransistores BJT Con MatlabJesus Vargas AguilarBelum ada peringkat

- Lab 8 RLC Resonancia en ParaleloDokumen7 halamanLab 8 RLC Resonancia en ParaleloKenny H G JiménezBelum ada peringkat

- Lab E.A.3Dokumen21 halamanLab E.A.3AndyEshinoBelum ada peringkat

- Circuitos con diodos (recortadoresDokumen12 halamanCircuitos con diodos (recortadoresparfreeBelum ada peringkat

- Informe de Laboratorio: Aplicacion DiodosDokumen5 halamanInforme de Laboratorio: Aplicacion DiodosLaura Lorena LugoBelum ada peringkat

- Informe MosfetDokumen12 halamanInforme Mosfetmayra alejandta villamil barbosaBelum ada peringkat

- PRACTICA 5 y 6Dokumen27 halamanPRACTICA 5 y 6CRISTIAN QUIROZ SANCHEZBelum ada peringkat

- Informe 7Dokumen8 halamanInforme 7Camilo SarmientoBelum ada peringkat

- 3er Laboratorio Electronica Filtro LCDokumen10 halaman3er Laboratorio Electronica Filtro LCJhon Alex López SotoBelum ada peringkat

- Amplificador Emisor Comun PDFDokumen5 halamanAmplificador Emisor Comun PDFKevin Esleiter LeónBelum ada peringkat

- Laboratorio 5 Aplicaciones Del Amplificador OperacionalDokumen13 halamanLaboratorio 5 Aplicaciones Del Amplificador OperacionalAndres SanchezBelum ada peringkat

- Practica No.4 Circuitos RectificadoresDokumen9 halamanPractica No.4 Circuitos Rectificadoresoscar espinalBelum ada peringkat

- Circuito Am A Traves de Un DiodoDokumen12 halamanCircuito Am A Traves de Un DiodoRai PardoBelum ada peringkat

- Transmisor FMDokumen9 halamanTransmisor FMleonelBelum ada peringkat

- Circuitos electrónicos analógicosDokumen10 halamanCircuitos electrónicos analógicosRucko KrytiicontyBelum ada peringkat

- Lab5 C15 3 D VargasDokumen15 halamanLab5 C15 3 D VargasAlvaro Vargas GonzalesBelum ada peringkat

- Laboratorio Nº2 Pedro AlvaradoDokumen16 halamanLaboratorio Nº2 Pedro Alvaradopedro alvarado mayorgaBelum ada peringkat

- Fuente regulada de voltaje DC 5V - Experimento No10Dokumen12 halamanFuente regulada de voltaje DC 5V - Experimento No10Joel RiveraBelum ada peringkat

- Informe Previo 1 y 2 - Electronicos 2Dokumen8 halamanInforme Previo 1 y 2 - Electronicos 2Natalia PilarBelum ada peringkat

- Practica 4 Rectificador de Onda Completa Tipo PuenteDokumen7 halamanPractica 4 Rectificador de Onda Completa Tipo PuenteVictor Manuel Martinez GonzalezBelum ada peringkat

- Final FiltrosDokumen6 halamanFinal FiltrosPeter Ponce MontenegroBelum ada peringkat

- Proyecto de AnalogicaDokumen10 halamanProyecto de Analogicajuancarlosarano31Belum ada peringkat

- Practicas El Diodo RectificadorDokumen12 halamanPracticas El Diodo RectificadorJose GarciaBelum ada peringkat

- Lab 3 SCRDokumen5 halamanLab 3 SCRAlexCristanchoBelum ada peringkat

- Amp Dif y Fuentes de Corriente MosfetDokumen4 halamanAmp Dif y Fuentes de Corriente MosfetMarie DovaleBelum ada peringkat

- Tema 8Dokumen37 halamanTema 8Federico100% (1)

- Reporte de Práctica 9Dokumen13 halamanReporte de Práctica 9Ulises GarcíaBelum ada peringkat

- Realimentación paralelo-serie en amplificador operacionalDokumen7 halamanRealimentación paralelo-serie en amplificador operacionalSilva Minutti RomanBelum ada peringkat

- Informe Final 7 Ee131Dokumen14 halamanInforme Final 7 Ee131Bernick Lincoln Salvador RosasBelum ada peringkat

- Transformador de DistribucionDokumen27 halamanTransformador de DistribucionAlonzo AlvaradoBelum ada peringkat

- Análisis transitorios usando Bergerón y DommelDokumen8 halamanAnálisis transitorios usando Bergerón y DommelDavid Santiago Daza QuirogaBelum ada peringkat

- Ntc2050 Sec 318 Bandeja PortacablesDokumen2 halamanNtc2050 Sec 318 Bandeja PortacablesDavid Santiago Daza QuirogaBelum ada peringkat

- PedestalDokumen19 halamanPedestalAndres AlonsoBelum ada peringkat

- Arranque Motores SincronosDokumen7 halamanArranque Motores SincronosTropa Fiee UncpBelum ada peringkat

- Interventoría Segundo Apartamento PDFDokumen2 halamanInterventoría Segundo Apartamento PDFDavid Santiago Daza QuirogaBelum ada peringkat

- Constantes 2017Dokumen10 halamanConstantes 2017gercubBelum ada peringkat

- Litestar10 ES PDFDokumen136 halamanLitestar10 ES PDFEmilio TamayoBelum ada peringkat

- Ap 330Dokumen2 halamanAp 330David Santiago Daza QuirogaBelum ada peringkat

- Agpe 20180411 BquillaDokumen41 halamanAgpe 20180411 BquillaDavid Santiago Daza QuirogaBelum ada peringkat

- Selección de Calibre en Cables para Construcción PDFDokumen7 halamanSelección de Calibre en Cables para Construcción PDFFrancisco GalleguillosBelum ada peringkat

- Rectificador de Onda Completa A 300WDokumen2 halamanRectificador de Onda Completa A 300WDavid Santiago Daza QuirogaBelum ada peringkat

- Seleccion de Calibre en Cables para ConstruccionDokumen94 halamanSeleccion de Calibre en Cables para ConstruccionDavid Santiago Daza QuirogaBelum ada peringkat

- Interventoría Segundo Apartamento PDFDokumen2 halamanInterventoría Segundo Apartamento PDFDavid Santiago Daza QuirogaBelum ada peringkat

- Documento CREGDokumen24 halamanDocumento CREGDavid Santiago Daza QuirogaBelum ada peringkat

- John Von NeumannDokumen17 halamanJohn Von Neumannjhony alejandro salazar grajalesBelum ada peringkat

- Cargos Regulados para La Actividad de GeneraciónDokumen3 halamanCargos Regulados para La Actividad de GeneraciónDavid Santiago Daza QuirogaBelum ada peringkat

- 1MRB520308-Bes-REB500-REB500sys Datasheet PDFDokumen48 halaman1MRB520308-Bes-REB500-REB500sys Datasheet PDFkensoiBelum ada peringkat

- Efectos de Los Campos Electromagneticos en Los Seres VivosDokumen3 halamanEfectos de Los Campos Electromagneticos en Los Seres VivosDavid Santiago Daza QuirogaBelum ada peringkat

- Un Norte para Los Sistemas de Transporte MasivoDokumen4 halamanUn Norte para Los Sistemas de Transporte MasivoDavid Santiago Daza QuirogaBelum ada peringkat

- Pre Informe Transformador Monofasico Bajo CargaDokumen3 halamanPre Informe Transformador Monofasico Bajo CargaDavid Santiago Daza QuirogaBelum ada peringkat

- Cargos Regulados para La Actividad de GeneraciónDokumen3 halamanCargos Regulados para La Actividad de GeneraciónDavid Santiago Daza QuirogaBelum ada peringkat

- Informe Del Analizador de RedesDokumen3 halamanInforme Del Analizador de RedesDavid Santiago Daza QuirogaBelum ada peringkat

- Fibrilación Ventricular Primera Causante de Muerte Por Corriente EléctricaDokumen2 halamanFibrilación Ventricular Primera Causante de Muerte Por Corriente EléctricaDavid Santiago Daza QuirogaBelum ada peringkat

- Doing Business Colombia 2016Dokumen104 halamanDoing Business Colombia 2016David Santiago Daza QuirogaBelum ada peringkat

- Archivo Nuevo38Dokumen4 halamanArchivo Nuevo38David Santiago Daza QuirogaBelum ada peringkat

- Control PI: acción proporcional e integralDokumen9 halamanControl PI: acción proporcional e integralturrubiateBelum ada peringkat

- Efectos de los campos electromagnéticos y límites de exposiciónDokumen3 halamanEfectos de los campos electromagnéticos y límites de exposiciónDavid Santiago Daza QuirogaBelum ada peringkat

- Doing Business Colombia 2016Dokumen104 halamanDoing Business Colombia 2016David Santiago Daza QuirogaBelum ada peringkat

- Control PWMDokumen2 halamanControl PWMDavid Santiago Daza QuirogaBelum ada peringkat

- InglesDokumen7 halamanInglesKarina Silva50% (4)

- Empresa Gran Akí-CarapungoDokumen32 halamanEmpresa Gran Akí-CarapungoDANILOJITALABelum ada peringkat

- Constancia de Aval y Letras de CambioDokumen14 halamanConstancia de Aval y Letras de CambioESTELA MORANBelum ada peringkat

- Usuario Altamente Exportador y Usuario Aduanero PermanenteDokumen9 halamanUsuario Altamente Exportador y Usuario Aduanero PermanenteKaren RomeroBelum ada peringkat

- Modelo de Informe de Estafa Conserva.Dokumen2 halamanModelo de Informe de Estafa Conserva.Charito Raza QuirozBelum ada peringkat

- Comparación Ciclos de VidaDokumen22 halamanComparación Ciclos de VidaLuismarcallaBelum ada peringkat

- 00 Soñar o No Soñar - DR Peter y Eva Muller MeerkatzDokumen264 halaman00 Soñar o No Soñar - DR Peter y Eva Muller MeerkatzCarlos Hernandez Hernandez67% (3)

- Propuesta de Contrato de ConcesiónDokumen2 halamanPropuesta de Contrato de ConcesiónFrank Cuao SánchezBelum ada peringkat

- Redactar Una Buena PublicidadDokumen15 halamanRedactar Una Buena PublicidadJJND88Belum ada peringkat

- Recetario Navidad 2Dokumen152 halamanRecetario Navidad 2Jose Manuel Macías100% (1)

- PHAYAWISDokumen52 halamanPHAYAWISdiegonauthaBelum ada peringkat

- Cómo redactar una receta de cocina paso a pasoDokumen13 halamanCómo redactar una receta de cocina paso a pasomarysolBelum ada peringkat

- Pestiños Con MielDokumen9 halamanPestiños Con MielJuan Manuel Rodríguez MarcosBelum ada peringkat

- FDHB725ES - Soluciones de FiltraciónDokumen40 halamanFDHB725ES - Soluciones de FiltraciónJulio Cesar Moreno AriasBelum ada peringkat

- Formato Acta de Compromiso de Corresponsabilidad Proyectos SocialesDokumen2 halamanFormato Acta de Compromiso de Corresponsabilidad Proyectos SocialesDiego JarrinBelum ada peringkat

- Plan de Operaciones para La Creacion de Una EmpresaDokumen9 halamanPlan de Operaciones para La Creacion de Una EmpresaJames Huaman Guzman100% (1)

- Rastrojos y Algo Mas - Historia - Alapin, Helena PDFDokumen123 halamanRastrojos y Algo Mas - Historia - Alapin, Helena PDFAlejandroOrozcoAlvarezBelum ada peringkat

- DiaposDokumen8 halamanDiaposLuis Velarde DezaBelum ada peringkat

- Estado de Origen y Aplicacion de FondosDokumen26 halamanEstado de Origen y Aplicacion de Fondosabel aramis machado rodriguezBelum ada peringkat

- MRODokumen6 halamanMROErnestoPierdant100% (1)

- Zingueria RD Factura: OriginalDokumen3 halamanZingueria RD Factura: Originalbrutal6589Belum ada peringkat

- Mapa Conceptual NIA 220Dokumen4 halamanMapa Conceptual NIA 220Max ReinerBelum ada peringkat

- Trabajo DoveDokumen3 halamanTrabajo DoveblobofstuffandthingsBelum ada peringkat

- El desarrollo del capitalismo en América Latina y la formación de los estados nacionalesDokumen5 halamanEl desarrollo del capitalismo en América Latina y la formación de los estados nacionalesNahuelBelum ada peringkat

- Canta PalabrasDokumen36 halamanCanta PalabrasTatiana AcelasBelum ada peringkat

- Baño de RodioDokumen3 halamanBaño de Rodiocarlos753Belum ada peringkat

- Administracion de Operaciones Chase 2009 WordDokumen44 halamanAdministracion de Operaciones Chase 2009 WordLuci CastroBelum ada peringkat

- S4A9 MartinezM LuisAngelDokumen4 halamanS4A9 MartinezM LuisAngelLuisilloBelum ada peringkat

- Unidad 5 SQL Del MySQLDokumen15 halamanUnidad 5 SQL Del MySQLClaudia GonzalesBelum ada peringkat

- Ciudades MedievalesDokumen54 halamanCiudades MedievalesLupittaa Montes Soto100% (2)