Ch12 Memory Organization

Diunggah oleh

Murali KrishnaHak Cipta

Format Tersedia

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniHak Cipta:

Format Tersedia

Ch12 Memory Organization

Diunggah oleh

Murali KrishnaHak Cipta:

Format Tersedia

Memory Organization

MEMORY ORGANIZATION

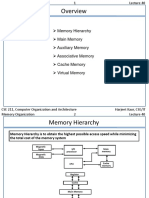

Memory Hierarchy

Main Memory

Auxiliary Memory

Associative Memory

Cache Memory

Virtual Memory

Memory Management Hardware

Computer Organization

Computer Architectures Lab

Memory Organization

Memory Hierarchy

MEMORY HIERARCHY

Memory Hierarchy is to obtain the highest possible

access speed while minimizing the total cost of the memory system

Auxiliary memory

Magnetic

tapes

I/O

processor

Main

memory

CPU

Cache

memory

Magnetic

disks

Register

Cache

Main Memory

Magnetic Disk

Magnetic Tape

Computer Organization

Computer Architectures Lab

Memory Organization

Main Memory

MAIN MEMORY

RAM and ROM Chips

Typical RAM chip

Chip select 1

Chip select 2

Read

Write

7-bit address

CS1 CS2

0

0

0

1

1

0

1

0

1

0

1

1

CS1

CS2

RD

WR

AD 7

RD

x

x

0

0

1

x

WR

x

x

0

1

x

x

128 x 8

RAM

8-bit data bus

Memory function

Inhibit

Inhibit

Inhibit

Write

Read

Inhibit

State of data bus

High-impedence

High-impedence

High-impedence

Input data to RAM

Output data from RAM

High-impedence

Typical ROM chip

Chip select 1

Chip select 2

CS1

CS2

512 x 8

ROM

9-bit address

Computer Organization

8-bit data bus

AD 9

Computer Architectures Lab

Memory Organization

Main Memory

MEMORY ADDRESS MAP

Address space assignment to each memory chip

Example: 512 bytes RAM and 512 bytes ROM

Component

RAM

RAM

RAM

RAM

ROM

1

2

3

4

Hexa

address

0000 - 007F

0080 - 00FF

0100 - 017F

0180 - 01FF

0200 - 03FF

Address bus

10 9

0

0

0

0

1

0

0

1

1

x

8 7 6 5

4 3 2 1

0

1

0

1

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

x

Memory Connection to CPU

- RAM and ROM chips are connected to a CPU

through the data and address buses

- The low-order lines in the address bus select

the byte within the chips and other lines in the

address bus select a particular chip through

its chip select inputs

Computer Organization

Computer Architectures Lab

Memory Organization

Main Memory

CONNECTION OF MEMORY TO CPU

Address bus

16-11 10 9 8

CPU

7-1

RD WR

Data bus

CS1

CS2

RD 128 x 8

RAM 4

WR

AD7

1- 7

8

9

Computer Organization

CS1

CS2

512 x 8

AD9 ROM

Data

Data

CS1

CS2

RD 128 x 8

RAM 3

WR

AD7

Data

CS1

CS2

RD 128 x 8

RAM 2

WR

AD7

Data

CS1

CS2

RD 128 x 8

RAM 1

WR

AD7

Data

Decoder

3 2 1 0

Computer Architectures Lab

Memory Organization

Auxiliary Memory

AUXILIARY MEMORY

Information Organization on Magnetic Tapes

file i

block 1

R1

block 2

block 3

R2

R3

R4

EOF

R5

R6

block 3 IRG

R1

EOF

R5

R4

R3 R2

block 1

block 2

Organization of Disk Hardware

Moving Head Disk

Fixed Head Disk

Track

Computer Organization

Computer Architectures Lab

Memory Organization

Associative Memory

ASSOCIATIVE MEMORY

- Accessed by the content of the data rather than by an address

- Also called Content Addressable Memory (CAM)

Hardware Organization

Argument register(A)

Key register (K)

Match

register

Input

Associative memory

array and logic

M

Read

Write

m words

n bits per word

- Compare each word in CAM in parallel with the

content of A(Argument Register)

- If CAM Word[i] = A, M(i) = 1

- Read sequentially accessing CAM for CAM Word(i) for M(i) = 1

- K(Key Register) provides a mask for choosing a

particular field or key in the argument in A

(only those bits in the argument that have 1s in

their corresponding position of K are compared)

Computer Organization

Computer Architectures Lab

Memory Organization

Associative Memory

ORGANIZATION OF CAM

A1

Aj

An

K1

Kj

Kn

Word 1

C11

C1j

C1n

M1

Word i

Ci1

Cij

Cin

Mi

Word m

Cm1

Cmj

Cmn

Mm

Bit 1

Bit j

Bit n

Internal organization of a typical cell Cij

Aj

Input

Kj

Write

S

F ij

Read

Match

logic

To M i

Output

Computer Organization

Computer Architectures Lab

Memory Organization

Associative Memory

MATCH LOGIC

K1

A1

F'i1

F i1

K2

A2

F'i2

F i2

Kn

....

F'in

An

F in

Mi

Computer Organization

Computer Architectures Lab

Memory Organization

10

Cache Memory

CACHE MEMORY

Locality of Reference

- The references to memory at any given time

interval tend to be confined within a localized areas

- This area contains a set of information and

the membership changes gradually as time goes by

- Temporal Locality

The information which will be used in near future

is likely to be in use already( e.g. Reuse of information in loops)

- Spatial Locality

If a word is accessed, adjacent(near) words are likely accessed soon

(e.g. Related data items (arrays) are usually stored together;

instructions are executed sequentially)

Cache

- The property of Locality of Reference makes the

Cache memory systems work

- Cache is a fast small capacity memory that should hold those information

which are most likely to be accessed

Main memory

CPU

Cache memory

Computer Organization

Computer Architectures Lab

Memory Organization

11

Cache Memory

PERFORMANCE OF CACHE

Memory Access

All the memory accesses are directed first to Cache

If the word is in Cache; Access cache to provide it to CPU

If the word is not in Cache; Bring a block (or a line) including

that word to replace a block now in Cache

- How can we know if the word that is required

is there ?

- If a new block is to replace one of the old blocks,

which one should we choose ?

Performance of Cache Memory System

Hit Ratio - % of memory accesses satisfied by Cache memory system

Te: Effective memory access time in Cache memory system

Tc: Cache access time

Tm: Main memory access time

Te = Tc + (1 - h) Tm

Example: Tc = 0.4 s, Tm = 1.2s, h = 0.85%

Te = 0.4 + (1 - 0.85) * 1.2 = 0.58s

Computer Organization

Computer Architectures Lab

Memory Organization

12

Cache Memory

MEMORY AND CACHE MAPPING - ASSOCIATIVE MAPPLING Mapping Function

Specification of correspondence between main

memory blocks and cache blocks

Associative mapping

Direct mapping

Set-associative mapping

Associative Mapping

- Any block location in Cache can store any block in memory

-> Most flexible

- Mapping Table is implemented in an associative memory

-> Fast, very Expensive

- Mapping Table

Stores both address and the content of the memory word

address (15 bits)

Argument register

CAM

Computer Organization

Address

Data

01000

02777

22235

3450

6710

1234

Computer Architectures Lab

Memory Organization

13

Cache Memory

MEMORY AND CACHE MAPPING - DIRECT MAPPING - Each memory block has only one place to load in Cache

- Mapping Table is made of RAM instead of CAM

- n-bit memory address consists of 2 parts; k bits of Index field and

n-k bits of Tag field

- n-bit addresses are used to access main memory

and k-bit Index is used to access the Cache

Addressing Relationships

Tag(6)

Index(9)

00 000

32K x 12

000

Main memory

Address = 15 bits

Data = 12 bits

777

77 777

512 x 12

Cache memory

Address = 9 bits

Data = 12 bits

Direct Mapping Cache Organization

Memory

address

00000

Memory data

1220

00777

01000

2340

3450

01777

02000

4560

5670

02777

6710

Computer Organization

Index

address

000

777

Cache memory

Tag

00

Data

1220

02

6710

Computer Architectures Lab

Memory Organization

14

Cache Memory

DIRECT MAPPING

Operation

- CPU generates a memory request with (TAG;INDEX)

- Access Cache using INDEX ; (tag; data)

Compare TAG and tag

- If matches -> Hit

Provide Cache[INDEX](data) to CPU

- If not match -> Miss

M[tag;INDEX] <- Cache[INDEX](data)

Cache[INDEX] <- (TAG;M[TAG; INDEX])

CPU <- Cache[INDEX](data)

Direct Mapping with block size of 8 words

Index

tag

000

007

010

017

01

01

Block 63 770

777

02

02

Block 0

Block 1

Computer Organization

data

3450

6578

6

Tag

6

Block

3

Word

INDEX

6710

Computer Architectures Lab

Memory Organization

15

Cache Memory

MEMORY AND CACHE MAPPING - SET ASSOCIATIVE MAPPING - Each memory block has a set of locations in the Cache to load

Set Associative Mapping Cache with set size of two

Index

Tag

Data

Tag

Data

000

01

3450

02

5670

777

02

6710

00

2340

Operation

- CPU generates a memory address(TAG; INDEX)

- Access Cache with INDEX, (Cache word = (tag 0, data 0); (tag 1, data 1))

- Compare TAG and tag 0 and then tag 1

- If tag i = TAG -> Hit, CPU <- data i

- If tag i TAG -> Miss,

Replace either (tag 0, data 0) or (tag 1, data 1),

Assume (tag 0, data 0) is selected for replacement,

(Why (tag 0, data 0) instead of (tag 1, data 1) ?)

M[tag 0, INDEX] <- Cache[INDEX](data 0)

Cache[INDEX](tag 0, data 0) <- (TAG, M[TAG,INDEX]),

CPU <- Cache[INDEX](data 0)

Computer Organization

Computer Architectures Lab

Memory Organization

16

Cache Memory

BLOCK REPLACEMENT POLICY

Many different block replacement policies are available

LRU(Least Recently Used) is most easy to implement

Cache word = (tag 0, data 0, U0);(tag 1, data 1, U1), Ui = 0 or 1(binary)

Implementation of LRU in the Set Associative Mapping with set size = 2

Modifications

Initially all U0 = U1 = 1

When Hit to (tag 0, data 0, U0), U1 <- 1(least recently used)

(When Hit to (tag 1, data 1, U1), U0 <- 1(least recently used))

When Miss, find the least recently used one(Ui=1)

If U0 = 1, and U1 = 0, then replace (tag 0, data 0)

M[tag 0, INDEX] <- Cache[INDEX](data 0)

Cache[INDEX](tag 0, data 0, U0) <- (TAG,M[TAG,INDEX], 0); U1 <- 1

If U0 = 0, and U1 = 1, then replace (tag 1, data 1)

Similar to above; U0 <- 1

If U0 = U1 = 0, this condition does not exist

If U0 = U1 = 1, Both of them are candidates,

Take arbitrary selection

Computer Organization

Computer Architectures Lab

Memory Organization

17

Cache Memory

CACHE WRITE

Write Through

When writing into memory

If Hit, both Cache and memory is written in parallel

If Miss, Memory is written

For a read miss, missing block may be

overloaded onto a cache block

Memory is always updated

-> Important when CPU and DMA I/O are both executing

Slow, due to the memory access time

Write-Back (Copy-Back)

When writing into memory

If Hit, only Cache is written

If Miss, missing block is brought to Cache and write into Cache

For a read miss, candidate block must be

written back to the memory

Memory is not up-to-date, i.e., the same item in

Cache and memory may have different value

Computer Organization

Computer Architectures Lab

Memory Organization

18

Virtual Memory

VIRTUAL MEMORY

Give the programmer the illusion that the system has a very large memory,

even though the computer actually has a relatively small main memory

Address Space(Logical) and Memory Space(Physical)

address space

virtual address

(logical address)

memory space

Mapping

address generated by programs

physical address

actual main memory address

Address Mapping

Memory Mapping Table for Virtual Address -> Physical Address

Virtual address

Virtual

address

register

Memory

mapping

table

Main memory

address

register

Main

memory

Physical

Address

Memory table

buffer register

Computer Organization

Main memory

buffer register

Computer Architectures Lab

Memory Organization

19

Virtual Memory

ADDRESS MAPPING

Address Space and Memory Space are each divided

into fixed size group of words called blocks or pages

1K words group

Address space

N = 8K = 213

Page 0

Page 1

Page 2

Page 3

Page 4

Page 5

Page 6

Page 7

Memory space

M = 4K = 212

Block 0

Block 1

Block 2

Block 3

Organization of memory Mapping Table in a paged system

Page no.

1 0 1

Table

address

Memory page table

Virtual address

Presence

bit

000

001

010

011

100

101

110

111

11

00

01

10

01

Computer Organization

Line number

0 1 0 1 0 1 0 0 1 1

0

1

1

0

0

1

1

0

01

0101010011

Main memory

address register

Main memory

Block 0

Block 1

Block 2

Block 3

MBR

Computer Architectures Lab

Memory Organization

20

Virtual Memory

ASSOCIATIVE MEMORY PAGE TABLE

Assume that

Number of Blocks in memory = m

Number of Pages in Virtual Address Space = n

Page Table

- Straight forward design -> n entry table in memory

Inefficient storage space utilization

<- n-m entries of the table is empty

- More efficient method is m-entry Page Table

Page Table made of an Associative Memory

m words; (Page Number:Block Number)

Virtual address

Page no.

1 0 1

Line number

Argument register

1 0 1

0 0

Key register

0

0

1

1

1

0

0

1

Associative memory

0

1

0

1

1

0

1

0

1

0

1

0

Page no.Block no.

Page Fault

Page number cannot be found in the Page Table

Computer Organization

Computer Architectures Lab

Memory Organization

21

Virtual Memory

PAGE FAULT

1. Trap to the OS

Page is on backing store

trap

OS

2. Save the user registers and program state

3. Determine that the interrupt was a page fault

4. Check that the page reference was legal and

determine the location of the page on the

backing store(disk)

5. Issue a read from the backing store to a free

Reference

LOAD M

0

frame

a. Wait in a queue for this device until serviced

restart

instruction

b. Wait for the device seek and/or latency time

c. Begin the transfer of the page to a free frame

6. While waiting, the CPU may be allocated to

some other process

free frame

reset

page

table

bring in

missing

page

7. Interrupt from the backing store (I/O completed)

8. Save the registers and program state for the other user

main memory

9. Determine that the interrupt was from the backing store

10. Correct the page tables (the desired page is now in memory)

11. Wait for the CPU to be allocated to this process again

12. Restore the user registers, program state, and new page table, then

resume the interrupted instruction.

Processor architecture should provide the ability

to restart any instruction after a page fault.

Computer Organization

Computer Architectures Lab

Memory Organization

22

Virtual Memory

PAGE REPLACEMENT

Decision on which page to displace to make room for

an incoming page when no free frame is available

Modified page fault service routine

1. Find the location of the desired page on the backing store

2. Find a free frame

- If there is a free frame, use it

- Otherwise, use a page-replacement algorithm to select a victim frame

- Write the victim page to the backing store

3. Read the desired page into the (newly) free frame

4. Restart the user process

valid/

frame invalid bit

2 change to

f 0 v i

invalid

4

v

f

reset page

table for

new page

page table

swap

out

1 victim

page

victim

3

swap

desired

page in

backing store

physical memory

Computer Organization

Computer Architectures Lab

Memory Organization

23

Virtual Memory

PAGE REPLACEMENT ALGORITHMS

FIFO

Reference string

7

7

0

2

0

1

7

0

1

2

3

1

2

3

0

4

3

0

4

2

3

4

2

0

0

1

3

0

2

3

0

1

2

7

1

2

7

0

2

7

0

1

Page frames

FIFO algorithm selects the page that has been in memory the longest time

Using a queue - every time a page is loaded, its

identification is inserted in the queue

Easy to implement

May result in a frequent page fault

Optimal Replacement (OPT) - Lowest page fault rate of all algorithms

Replace that page which will not be used for the longest period of time

Reference string

7

0

7

1

7

0

2

7

0

1

0

2

0

1

0

2

0

3

2

2

4

3

2

0

3

2

2

0

1

7

0

1

Page frames

Computer Organization

Computer Architectures Lab

Memory Organization

24

Virtual Memory

PAGE REPLACEMENT ALGORITHMS

LRU

- OPT is difficult to implement since it requires future knowledge

- LRU uses the recent past as an approximation of near future.

Replace that page which has not been

used for the longest period of time

Reference string

7

0

1

2

7

7

0

7

0

1

0

2

0

1

0

2

0

3

2

4

0

3

3

4

0

2

0

4

3

2

0

3

2

2

1

3

2

1

0

2

1

0

7

Page frames

- LRU may require substantial hardware assistance

- The problem is to determine an order for the frames

defined by the time of last use

Computer Organization

Computer Architectures Lab

Memory Organization

25

Virtual Memory

PAGE REPLACEMENT ALGORITHMS

LRU Implementation Methods

Counters

- For each page table entry - time-of-use register

- Incremented for every memory reference

- Page with the smallest value in time-of-use register is replaced

Stack

- Stack of page numbers

- Whenever a page is referenced its page number is

removed from the stack and pushed on top

- Least recently used page number is at the bottom

Reference string

4

7

0

7

1

2

1

0

7

4

7

2

1

0

4

LRU Approximation

- Reference (or use) bit is used to approximate the LRU

- Turned on when the corresponding page is

referenced after its initial loading

- Additional reference bits may be used

Computer Organization

Computer Architectures Lab

Memory Organization

26

Memory Management Hardware

MEMORY MANAGEMENT HARDWARE

Basic Functions of MM

- Dynamic Storage Relocation - mapping logical

memory references to physical memory references

- Provision for Sharing common information stored

in memory by different users

- Protection of information against unauthorized access

Segmentation

- A segment is a set of logically related instructions

or data elements associated with a given name

- Variable size

User's view of memory

Stack

Subroutine

Symbol

Table

SQRT

Main

Program

The user does not think of

memory as a linear array

of words. Rather the user

prefers to view memory as

a collection of variable

sized segments, with no

necessary ordering among

segments.

User's view of a program

Computer Organization

Computer Architectures Lab

Memory Organization

27

Memory Management Hardware

SEGMENTATION

- A memory management scheme which supports

user's view of memory

- A logical address space is a collection of segments

- Each segment has a name and a length

- Address specify both the segment name and the

offset within the segment.

- For simplicity of implementations, segments are numbered.

Segmentation Hardware

Segment Table

s

limit

CPU

base

(s,d)

Memory

<

n

error

Computer Organization

Computer Architectures Lab

Memory Organization

28

Memory Management Hardware

SEGMENTATION EXAMPLE

Subroutine

Stack

Segment 3

1400

Segment 0

2400

Segment 0

Symbol

Table

SQRT

Segment 1

Segment 4

Main

Program

3200

Segment 3

Segment 2

Segment 2

Logical Address Space

4300

4700

Segment 4

5700

Segment 1

Segment Table

limit base

0 1000 1400

1 400 6300

2 400 4300

3 1100 3200

4 1000 4700

Computer Organization

6300

6700

Computer Architectures Lab

Memory Organization

29

Memory Management Hardware

SHARING OF SEGMENTS

Editor

limit

Segment 0

Data 1

base

0 25286 43062

1 4425 68348

43062

Editor

Segment Table

(User 1)

Data 1

Segment 1

68348

72773

Logical Memory

(User 1)

90003

Data 2

98556

Editor

Segment 0

Data 2

limit base

0 25286 43062

1 8550 90003

Physical Memory

Segment Table

(User 2)

Segment 1

Logical Memory

(User 2)

Computer Organization

Computer Architectures Lab

Memory Organization

30

Memory Management Hardware

SEGMENTED PAGE SYSTEM

Logical address

Segment

Page

Segment table

Word

Page table

Block

Word

Physical address

Computer Organization

Computer Architectures Lab

Memory Organization

31

Memory Management Hardware

IMPLEMENTATION OF PAGE AND SEGMENT TABLES

Implementation of the Page Table

- Hardware registers (if the page table is reasonably small)

- Main memory

- Page Table Base Register(PTBR) points to PT

- Two memory accesses are needed to access

a word; one for the page table, one for the word

- Cache memory (TLB: Translation Lookaside Buffer)

- To speedup the effective memory access time,

a special small memory called associative

memory, or cache is used

Implementation of the Segment Table

Similar to the case of the page table

Computer Organization

Computer Architectures Lab

Memory Organization

32

Memory Management Hardware

EXAMPLE

Logical and Physical Addresses

Logical address format: 16 segments of 256 pages

each, each page has 256words

4

8

Page

Segment

8

Word

20

2 x 32

Physical

memory

Physical address format: 4096 blocks of 256 words

each, each word has 32bits

12

Block

8

Word

Logical and Physical Memory Address Assignment

Hexa

address

Page number

60000

Page 0

60100

Page 1

60200

Page 2

60300

60400

604FF

Page 3

Page

00

01

02

03

04

Block

012

000

019

053

A61

Page 4

(a) Logical address assignment

Computer Organization

Segment

6

6

6

6

6

(b) Segment-page versus

memory block assignment

Computer Architectures Lab

Memory Organization

33

Memory Management Hardware

LOGICAL TO PHYSICAL MEMORY MAPPING

Segment and page table mapping

Logical address (in hexadecimal)

02

Segment table

Page table

00

7E

Physical memory

00000

000FF

35

35

36

37

38

39

A3

A3

012

000

019

053

A61

012

Block 0

01200

012FF

01900

0197E

019FF

Block 12

32-bit word

Associative memory mapping

Segment

6

6

Computer Organization

Page

02

04

Block

019

A61

Computer Architectures Lab

Memory Organization

34

Memory Management Hardware

MEMORY PROTECTION

Protection information can be included in the

segment table or segment register of the memory

management hardware

- Format of a typical segment descriptor

Base address

Length

Protection

- The protection field in a segment descriptor specifies

the Access Rights to the particular segment

- In a segmented-page organization, each entry in the

page table may have its own protection field to

describe the Access Rights of each page

- Access Rights:

Computer Organization

Full read and write privileges.

Read only (write protection)

Execute only (program protection)

System only (O.S. Protection)

Computer Architectures Lab

Memory Organization

35

A Typical Cache and TLB Design

From translator

Virtual

Real

Address Address

CPU

Virtual Address

Page

Line

Word in

Number

Number

Line

To translator

A

CPU Memory

Hash

Function

Real Address Data

TLB

Cache

A

Real

Compare Virtual

Address

Addresses

Compare Addresses

& Select Data

Data

Word Select & Align

To Main Memory

S = Select

Computer Organization

Data Out

Computer Architectures Lab

Memory Organization

36

Structure of Cache Entry and Cache Set

Real Address Tag

Data

Valid

Cache Entry

Entry 1

Entry 2

Entry E

Replacement status

Cache Set

Computer Organization

Computer Architectures Lab

Memory Organization

37

Cache Operation Flow Chart

Receive Virtual Address

Use Line Number

to Select Set

Hash Page Number

Search TLB

Read Out Address Tags

A

In TLB ?

yes

Compare Addresses

no

Send Virtual Address

to Translator

yes

Update Replacement

Status in TLB

Use Page & Segment tables

to Translate Address

Update Replacement

Status

Select

Correct

Line

Match ?

no

Send Real Address

to Main Memory

Receive Line from

Main Memory

Store Line

in Cache

Put in TLB

Select Correct

Word from Line

Read Out

Computer Organization

Computer Architectures Lab

Memory Organization

38

Virtual Address Format - Example

Page number

Byte within page

Byte within line

31

21

Map through

page directory

20

17

12

Select set

in TLB

Map through

page table

11

10

Select set

in cache

Line number

Byte within

word

Word within

line

Virtual Address of Fairchild Clipper

Computer Organization

Computer Architectures Lab

Anda mungkin juga menyukai

- Nintendo DS Architecture: Architecture of Consoles: A Practical Analysis, #14Dari EverandNintendo DS Architecture: Architecture of Consoles: A Practical Analysis, #14Belum ada peringkat

- Nintendo 64 Architecture: Architecture of Consoles: A Practical Analysis, #8Dari EverandNintendo 64 Architecture: Architecture of Consoles: A Practical Analysis, #8Belum ada peringkat

- Memory OrganizationDokumen22 halamanMemory OrganizationsivaBelum ada peringkat

- Memory HierarchyDokumen4 halamanMemory Hierarchynancy_01Belum ada peringkat

- Unit 5Dokumen42 halamanUnit 5godifab162Belum ada peringkat

- Memory Hierarchy Main Memory Auxiliary Memory Associative Memory Cache Memory Virtual MemoryDokumen23 halamanMemory Hierarchy Main Memory Auxiliary Memory Associative Memory Cache Memory Virtual Memoryayush ajayBelum ada peringkat

- Memory Hierarchy Main Memory Auxiliary Memory Associative Memory Cache Memory Virtual MemoryDokumen22 halamanMemory Hierarchy Main Memory Auxiliary Memory Associative Memory Cache Memory Virtual MemoryADITYA KUMAR SINGHBelum ada peringkat

- MemoryDokumen38 halamanMemoryRohit PaulBelum ada peringkat

- Memory Hierarchy Main Memory Auxiliary Memory Associative Memory Cache Memory Virtual MemoryDokumen6 halamanMemory Hierarchy Main Memory Auxiliary Memory Associative Memory Cache Memory Virtual MemoryShaik ShariefBelum ada peringkat

- CH-3.Memory OrganizationDokumen35 halamanCH-3.Memory OrganizationDevanshi GudsariyaBelum ada peringkat

- CH12Dokumen6 halamanCH12sara_lolo100% (1)

- Unit 5Dokumen21 halamanUnit 5optics opticsBelum ada peringkat

- Memory OrganisationDokumen44 halamanMemory OrganisationHerambh DubeyBelum ada peringkat

- Lect 22-Memory HierarchyDokumen16 halamanLect 22-Memory HierarchyjyotiranjanBelum ada peringkat

- 4 RR Unit-4 NotesDokumen96 halaman4 RR Unit-4 Notesdevillucifer9889Belum ada peringkat

- Memory Memory Organization OrganizationDokumen43 halamanMemory Memory Organization OrganizationAnonymous AFFiZnBelum ada peringkat

- 0memory HierarchyDokumen20 halaman0memory HierarchyOm PrakashBelum ada peringkat

- 6-Module 4-11-03-2024Dokumen77 halaman6-Module 4-11-03-2024bk8507091Belum ada peringkat

- DRAM and Other 3 BDokumen34 halamanDRAM and Other 3 BSumit GuptaBelum ada peringkat

- The Memory Hierarchy: CS 105 Tour of The Black Holes of ComputingDokumen39 halamanThe Memory Hierarchy: CS 105 Tour of The Black Holes of ComputinggaurabBelum ada peringkat

- CH 12Dokumen5 halamanCH 12Shivani GargBelum ada peringkat

- Virtual MemoryDokumen68 halamanVirtual MemoryMULLAIVANESH A VBelum ada peringkat

- Basics of Computer Theory Part-1Dokumen33 halamanBasics of Computer Theory Part-1uic.16bca1524Belum ada peringkat

- 21-Problems On Memory Design-28!02!2024Dokumen38 halaman21-Problems On Memory Design-28!02!2024suhas kodakandlaBelum ada peringkat

- 33-Design of Scalable Memory Using RAM's - ROM's Chips - Construction of Larger Size Memories-16-03-2024Dokumen32 halaman33-Design of Scalable Memory Using RAM's - ROM's Chips - Construction of Larger Size Memories-16-03-2024KBS SrikarBelum ada peringkat

- Memory OrganisationDokumen37 halamanMemory OrganisationRAJITHA RAMACHANDRANBelum ada peringkat

- Memory Organization and Interfacing EEE-3131Dokumen13 halamanMemory Organization and Interfacing EEE-3131ShazidBelum ada peringkat

- Sesion 6 - Memorias Ram Y Optane: Inst. Rafael G. Ticona CarbajalDokumen16 halamanSesion 6 - Memorias Ram Y Optane: Inst. Rafael G. Ticona CarbajalAngela Correa C.Belum ada peringkat

- Mem CacheDokumen23 halamanMem CacheJitendra PatelBelum ada peringkat

- IKI10230 Pengantar Organisasi Komputer Bab 5.1: MemoriDokumen31 halamanIKI10230 Pengantar Organisasi Komputer Bab 5.1: MemoriandinatapompiBelum ada peringkat

- 7 Mem CacheDokumen23 halaman7 Mem CacheSamuel GetachewBelum ada peringkat

- Memory Hierarchy: Sabina BatyrkhanovnaDokumen27 halamanMemory Hierarchy: Sabina BatyrkhanovnaNaski KuafniBelum ada peringkat

- Unit8 MemoryOrganizationDokumen10 halamanUnit8 MemoryOrganizationlovi bahunBelum ada peringkat

- Memory HierarchyDokumen43 halamanMemory Hierarchydress dressBelum ada peringkat

- Computer Architecture Notes VIIIDokumen10 halamanComputer Architecture Notes VIIIUnisa SakhaBelum ada peringkat

- 10 MemInterfaceDokumen16 halaman10 MemInterfaceanniyan_xBelum ada peringkat

- 512mb Ddrii Sdram A3r12e30cbf-ZentelDokumen74 halaman512mb Ddrii Sdram A3r12e30cbf-ZentelYonathan CoronaBelum ada peringkat

- 6.1 Memory & Programmable Logic Device DefinitionsDokumen40 halaman6.1 Memory & Programmable Logic Device Definitionsjeroro6730Belum ada peringkat

- Ov 4Dokumen99 halamanOv 4marwen hassenBelum ada peringkat

- Memory Devices, Circuits, and Subsystem DesignDokumen38 halamanMemory Devices, Circuits, and Subsystem Designلطيف احمد حسنBelum ada peringkat

- EE6304 Lecture8 Mem HierarchyDokumen54 halamanEE6304 Lecture8 Mem HierarchyAshish SoniBelum ada peringkat

- Super ComputerDokumen45 halamanSuper ComputerBook ThanayongBelum ada peringkat

- DLCA Unit 5-MemoryorganizationDokumen58 halamanDLCA Unit 5-MemoryorganizationJayendra SriBelum ada peringkat

- Unit 4 Memory HeirarchyDokumen16 halamanUnit 4 Memory Heirarchyvivek kumarBelum ada peringkat

- Hardware Components - Memory: M1: Introduction To Embedded SystemsDokumen12 halamanHardware Components - Memory: M1: Introduction To Embedded SystemsvithyaBelum ada peringkat

- CP SirDokumen238 halamanCP SirKaran SharmaBelum ada peringkat

- 217 Lec6Dokumen23 halaman217 Lec6palashBelum ada peringkat

- Memory OrganizationDokumen36 halamanMemory OrganizationjenyrennyBelum ada peringkat

- Evoltion&Future - Memory TechnologyDokumen37 halamanEvoltion&Future - Memory Technology16117 GOURAB SAHABelum ada peringkat

- Lec9-10 MemoryDokumen37 halamanLec9-10 MemoryvgodavarthyBelum ada peringkat

- Memory Part-IDokumen28 halamanMemory Part-IIRYA JAINBelum ada peringkat

- IT Workshop Lab Manual PDFDokumen166 halamanIT Workshop Lab Manual PDFAnusha KakumanuBelum ada peringkat

- 5 - Internal MemoryDokumen22 halaman5 - Internal Memoryerdvk100% (1)

- Super ComputerDokumen45 halamanSuper ComputerBook ThanayongBelum ada peringkat

- 06 MemoryDokumen37 halaman06 MemoryuabdulgwadBelum ada peringkat

- Memory Scaling Is Dead, Long Live Memory Scaling: Le Memoire Scaling Est Mort, Vive Le Memoire Scaling!Dokumen23 halamanMemory Scaling Is Dead, Long Live Memory Scaling: Le Memoire Scaling Est Mort, Vive Le Memoire Scaling!Soumyadeep DuttaBelum ada peringkat

- Virtual MemoryDokumen35 halamanVirtual MemoryAnikBelum ada peringkat

- Webinar stm32 20170511 PDFDokumen141 halamanWebinar stm32 20170511 PDFsushisenseiBelum ada peringkat

- G6 SupercomputerDokumen45 halamanG6 SupercomputerBook ThanayongBelum ada peringkat

- Game Boy Advance Architecture: Architecture of Consoles: A Practical Analysis, #7Dari EverandGame Boy Advance Architecture: Architecture of Consoles: A Practical Analysis, #7Belum ada peringkat

- Dell Emc Poweredge T640: Installation and Service ManualDokumen128 halamanDell Emc Poweredge T640: Installation and Service ManualNguyen Xuan MaoBelum ada peringkat

- 2.3.4 LAB Complete Dis AssemblyDokumen4 halaman2.3.4 LAB Complete Dis AssemblyHarleyBelum ada peringkat

- Ibm Infoprint 1570 DatasheetDokumen3 halamanIbm Infoprint 1570 DatasheetxyzBelum ada peringkat

- QuizDokumen5 halamanQuizfakenews1945Belum ada peringkat

- IoregDokumen310 halamanIoregPFEBelum ada peringkat

- Assembly 9618Dokumen5 halamanAssembly 9618raidenBelum ada peringkat

- Turn A Commodore 64 Into An IOS Bluetooth KeyboardDokumen21 halamanTurn A Commodore 64 Into An IOS Bluetooth KeyboardpolikarpaBelum ada peringkat

- Pascal ' S Calculator: Machine To The Public in 1645Dokumen3 halamanPascal ' S Calculator: Machine To The Public in 1645Frank Jomari MurilloBelum ada peringkat

- SPC 2306 Systems Programming Year III Semester IIDokumen3 halamanSPC 2306 Systems Programming Year III Semester IIhassan adamBelum ada peringkat

- RAD750 SpaceVPX - DsDokumen2 halamanRAD750 SpaceVPX - DsHugo MartínsBelum ada peringkat

- Why EMC Open Storage?: Symmetrix 3000 vs. Conventional DiskDokumen5 halamanWhy EMC Open Storage?: Symmetrix 3000 vs. Conventional Disknino7879Belum ada peringkat

- Microprocessors LabDokumen20 halamanMicroprocessors LabSwarnim ShuklaBelum ada peringkat

- AC-0085 Digital Assessment Accreditation GuidanceDokumen13 halamanAC-0085 Digital Assessment Accreditation GuidanceairlinemembershipBelum ada peringkat

- Hardware ComponentsDokumen18 halamanHardware Componentsapi-299006363Belum ada peringkat

- Unit 4 NotesDokumen13 halamanUnit 4 Notesselvapriya biherBelum ada peringkat

- Best 59 Hardware Interview QuestionsDokumen2 halamanBest 59 Hardware Interview QuestionsKhogen MairembamBelum ada peringkat

- c02 En4442en00enDokumen14 halamanc02 En4442en00enAgnes EcsekiBelum ada peringkat

- Harga CasingDokumen6 halamanHarga CasingAnonymous sGUFj93Belum ada peringkat

- Micro Propre Senex Er 2Dokumen15 halamanMicro Propre Senex Er 2bernie gumapacBelum ada peringkat

- E. B. Magalona National High School Summative Test in CSS 10 Quarter 1 Week 1 Multiple Choice. Choose The Letter of The Correct AnswerDokumen2 halamanE. B. Magalona National High School Summative Test in CSS 10 Quarter 1 Week 1 Multiple Choice. Choose The Letter of The Correct Answerric jason pedralBelum ada peringkat

- Chapter 01Dokumen51 halamanChapter 01Larson RogersBelum ada peringkat

- Problem - Write An Assembly Language Program To Add Two 8 Bit Numbers Stored at Address 2050 and Address 2051 in 8085Dokumen16 halamanProblem - Write An Assembly Language Program To Add Two 8 Bit Numbers Stored at Address 2050 and Address 2051 in 8085Robert LionBelum ada peringkat

- Voyager™ 1452g Series: Quick Start GuideDokumen16 halamanVoyager™ 1452g Series: Quick Start Guidevijay_sudhaBelum ada peringkat

- Supermicro C2SBX, C2SBX+ (User Manual)Dokumen92 halamanSupermicro C2SBX, C2SBX+ (User Manual)MechDRBelum ada peringkat

- MiraScreen 5G V1.20Dokumen10 halamanMiraScreen 5G V1.20Irfandi Al WhbBelum ada peringkat

- Computer Requirements: La NWM InstallationDokumen8 halamanComputer Requirements: La NWM InstallationJorge EstradaBelum ada peringkat

- Parul University: Pin Diagram of 8086Dokumen14 halamanParul University: Pin Diagram of 8086Lakshmi KumariBelum ada peringkat

- Chapter 3 - Hardware Basics - PeripheralsDokumen4 halamanChapter 3 - Hardware Basics - PeripheralsSasurika UchihaBelum ada peringkat

- SmartFlash HelpDokumen9 halamanSmartFlash HelpRoger Danilo FiglieBelum ada peringkat

- BIOS Update Compute Stick PDFDokumen9 halamanBIOS Update Compute Stick PDFZook ZTEBelum ada peringkat