HM6264

Diunggah oleh

Kaustuv MishraDeskripsi Asli:

Hak Cipta

Format Tersedia

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniHak Cipta:

Format Tersedia

HM6264

Diunggah oleh

Kaustuv MishraHak Cipta:

Format Tersedia

HM6264A Series

8192-word 8-bit High Speed CMOS Static RAM

Features

Low-power standby

0.1 mW (typ)

10 W (typ) L-/LL-version

Low power operation

15 mW/MHz (typ)

Fast access time

l00/120/150 ns (max)

Single +5 V supply

Completely static memory

No clock or timing strobe required

Equal access and cycle time

Common data input and output, three-state

output

Directly TTL compatible

All inputs and outputs

Battery back up operation capability

(L-/LL-version)

Ordering Information

Type No.

Access

time

HM6264AP-10

100 ns

HM6264AP-12

120 ns

HM6264AP-15

150 ns

HM6264ALP-10

100 ns

HM6264ALP-12

120 ns

HM6264ALP-15

150 ns

Type No.

Access

time

HM6264ASP-10

100 ns

HM6264ASP-12

120 ns

HM6264ASP-15

150 ns

Package

300-mil, 28-pin

plastic DIP

(DP-28N)

HM6264ALSP-10 100 ns

HM6264ALSP-12 120 ns

HM6264ALSP-15 150 ns

HM6264ALSP-10L 100 ns

HM6264ALSP-12L 120 ns

HM6264ALSP-15L 150 ns

HM6264AFP-10

100 ns

HM6264AFP-12

120 ns

HM6264AFP-15

150 ns

28-pin plastic

SOP *1

(FP-28D/DA)

Package

HM6264ALFP-10 100 ns

600-mil, 28-pin

plastic DIP

(DP-28)

HM6264ALFP-12 120 ns

HM6264ALFP-15 150 ns

HM6264ALFP-10L 100 ns

HM6264ALFP-12L 120 ns

HM6264ALFP-15L 150 ns

HM6264ALP-10L 100 ns

Note: 1. T is added to the end of the type number

for a SOP of 3.00 mm (max) thickness.

HM6264ALP-12L 120 ns

HM6264ALP-15L 150 ns

HM6264A Series

HM6264A Series

Pin Arrangement

NC

A12

A7

A6

A5

A4

A3

1

2

A2

A1

A0

8

9

10

11

12

21

20

19

18

17

VCC

WE

CS2

A8

A9

A11

OE

A10

CS1

I/O8

I/O7

I/O6

13

14

16

15

I/O5

I/O4

I/O1

I/O2

I/O3

VSS

28

27

26

25

24

3

4

5

6

7

23

22

(Top view)

Block Diagram

A11

A8

A9

A7

A12

A5

A6

A4

Row

decoder

I/O1

Column I/O

Input

data

control

I/O8

CS2

CS1

WE

OE

Memory array

256 256

Column decoder

A1 A2 A0 A10 A3

Timing pulse generator

VCC

VSS

HM6264A Series

HM6264A Series

Truth Table

WE

CS1

CS2

OE

Mode

I/O pin

VCC current

Not selected

(power down)

High Z

ISB, ISB1

High Z

ISB, ISB1

Output disabled

High Z

ICC

Read

Dout

ICC

Read cycle

Write

Din

ICC

Write cycle 1

Write

Din

ICC

Write cycle 2

Note:

: Dont care.

Note

Absolute Maximum Ratings

Parameter

Symbol

Rating

Unit

Terminal voltage *1

VT

0.5 *2 to +7.0

Power dissipation

PT

1.0

Operating temperature

Topr

0 to +70

Storage temperature

Tstg

55 to +125

Storage temperature (under bias)

Tbias

10 to +85

Notes: 1. With respect to VSS.

2. 3.0 V for pulse width 50 ns

Recommended DC Operating Conditions (Ta = 0 to +70C)

Parameter

Symbol

Min

Typ

Max

Unit

Supply voltage

VCC

4.5

5.0

5.5

VSS

VIH

2.2

6.0

VIL

0.3 *1

0.8

Input voltage

Note:

1. 3.0 V for pulse width 50 ns

HM6264A Series

HM6264A Series

DC and Operating Characteristics (VCC = 5 V 10%,VSS = 0 V, Ta = 0 to +70C)

Parameter

Symbol

Min

Typ

Max

Unit

Test condition

Input leakage current

|ILI|

Vin = VSS to VCC

Output leakage current |ILO|

CS1 = VIH or CS2 = VIL or OE = VIH or

WE = VIL, VI/O = VSS to VCC

Operating power

supply current

ICCDC

15

mA

CS1 = VIL, CS2 = VIH, II/O = 0 mA

Average operating

current

ICC1

30

30

45*5

55*6

mA

Min. cycle, duty = 100%,

CS1 = VIL, CS2 = VIH, II/O = 0 mA

ICC2

mA

Cycle time = 1 s, duty = 100%,

II/O = 0 mA, CS1 0.2 V,

CS2 VCC 0.2 V, VIH VCC 0.2 V,

VIL 0.2 V

mA

CS1 = VIH or CS2 = VIL

Standby power supply ISB

current

ISB1 *2

Output voltage

Notes: 1.

2.

3.

4.

5.

6.

0.02 2

mA

CS1 VCC 0.2 V, CS2 VCC 0.2 V or

2*3

100*3 A

0 V CS2 0.2 V, 0 V Vin

2*4

50*4

VOL

0.4

IOL = 2.1 mA

VOH

2.4

IOH = 1.0 mA

Typical values are at VCC = 5.0 V, Ta = 25C and not guaranteed.

VIL min = 0.3 V

These characteristics are guaranteed only for the L-version.

These characteristics are guaranteed only for the LL-version.

For 120 ns/150 ns version.

For 100 ns version.

Capacitance (f = 1 MHz, Ta = 25C)*1

Parameter

Symbol

Typ

Max

Unit

Test condition

Input capacitance

Cin

pF

Vin = 0 V

Input/output capacitance

CI/O

pF

VI/O = 0 V

Note:

1. This parameter is sampled and is not 100% tested.

HM6264A Series

HM6264A Series

AC Characteristics (VCC = 5 V 10%, Ta = 0 to +70C)

AC Test Conditions:

Input pulse levels: 0.8 V/2.4 V

Input rise and fall time: 10 ns

Input timing reference level: 1.5 V

Output timing reference level

HM6264A-10: 1.5 V

HM6264A-12/15: 0.8 V/2.0 V

Output load: 1 TTL gate and CL (100 pF) (including scope and jig)

Read Cycle

Parameter

Symbol

HM6264A-10

Min

Max

Read cycle time

tRC

100

120

150

ns

Address access time

tAA

100

120

150

ns

CS1

tCO1

100

120

150

ns

CS2

tCO2

100

120

150

ns

tOE

50

60

70

ns

CS1

tLZ1

10

10

15

ns

CS2

tLZ2

10

10

15

ns

Output enable to output in low Z

tOLZ

ns

CS1

tHZ1

35

40

50

ns

CS2

tHZ2

35

40

50

ns

Output disable to output in high Z

35

40

50

ns

Output hold from address change

10

10

10

ns

Chip selection to output

Output enable to output valid

Chip selection to output

in low Z

Chip deselection to

output in high Z

Notes

OHZ

OH

HM6264A-12

Min

Max

HM6264A-15

Min

Max

Unit

1. tHZ and tOHZ are defined as the time at which the outputs to achieve the open circuit

condition and are not referred to output voltage levels.

2. At any given temperature and voltage condition, tHZ maximum is less than tLZ minimum both for

a given device and from device to device.

HM6264A Series

HM6264A Series

Read Timing Waveform

tRC

Address

tAA

tCO1

CS1

tLZ1

tCO2

CS2

tHZ1

tLZ2

tOE

tHZ2

tOLZ

OE

tOHZ

Dout

Valid Data

tOH

Note: WE is high for read cycle.

Write Cycle

Parameter

Symbol

HM6264A-10

Min

Max

Write cycle time

tWC

100

120

150

ns

Chip selection to end of write

tCW

80

85

100

ns

Address setup time

tAS

ns

Address valid to end of write

tAW

80

85

100

ns

Write pulse width

tWP

60

70

90

ns

Write recovery time

tWR

ns

Write to output in high Z

tWHZ

35

40

50

ns

Data to write time overlap

tDW

40

40

50

ns

Data hold from write time

tDH

ns

Output enable to output in high Z

tOHZ

35

40

50

ns

Output active from end of write

tOW

ns

HM6264A-12

Min

Max

HM6264A-15

Min

Max

Unit

HM6264A Series

HM6264A Series

Write Timing Waveform (1) (OE Clock)

tWC

Address

OE

tCW *2

tWR *4

CS1

*6

CS2

WE

tAW

tAS *3

tWP *1

tOHZ *5

Dout

Din

tDW

tDH

Valid Data

HM6264A Series

HM6264A Series

Write Timing Waveform (2) (OE Low Fix)

tWC

Address

tAW

tWR *4

tCW

*2

*6

CS1

tCW *2

CS2

WE

tWP *1

tAS *3

*5

tOH

tOW

tWHZ

*7

Dout

tDW

*8

tDH

*9

Din

Valid Data

Notes: 1. A write occurs during the overlap of a low CS1, a high CS2, and a low WE. A write begins

at the latest transition among CS1 going low, CS2 going high and WE going low. A write

ends at the earliest transition among CS1 going high, CS2 going low and WE going high.

Time tWP is measured from the beginning of write to the end of write.

2. tCW is measured from the later of CS1 going low or CS2 going high to the end of write.

3. tAS is measured from the address valid to the beginning of write.

4. tWR is measured from the earliest of CS1 or WE going high or CS2 going low to the end

of the write cycle.

5. During this period, I/O pins are in the output state, therefore the input signals of opposite

phase to the outputs must not be applied.

6. If CS1 goes low simultaneously with WE going low or after WE goes low, the outputs

remain in high impedance state.

7. Dout is the same phase of the latest written data in this write cycle.

8. Dout is the read data of the next address.

9. If CS1 is low and CS2 is high during this period, I/O pins are in the output state. Input signals

of opposite phase to the outputs must not be applied to I/O pins

HM6264A Series

HM6264A Series

Low VCC Data Retention

In data retention mode, CS2 controls the address,

WE, CS1, OE, and the Din buffer. If CS2 controls

data retention mode, Vin (for these inputs) can be

in the high impedance state. If CS1 controls the

data retention mode, CS2 must satisfy either

CS2 VCC 0.2 V or CS2 0.2 V. The other

input levels (address, WE, OE, I/O) can be in the

high impedance state.

Low VCC Data Retention Characteristics (Ta = 0 to +70C)

This characteristics is guaranteed only L/LL-version.

Parameter

Symbol

Min

Typ

Max

Unit

Test Condition

VCC for data retention

VDR

2.0

CS1 VCC 0.2 V,

CS2 VCC 0.2 V, or

CS2 0.2 V

Data retention current

ICCDR

1*1

50*1

1*2

25*2

VCC = 3.0 V,

CS1 VCC 0.2 V,

CS2 VCC 0.2 V, or

0 V CS2 0.2 V, 0 V Vin

ns

See retention waveform

ns

See retention waveform

Chip deselect to data

retention time

Operation recovery time

tR

CDR

*3

RC

Notes: 1. VIL min = 0.3 V, 20 A max at Ta = 0 to 40C. These characteristics are guaranteed only for

the L-version.

2. VIL min = 0.3 V, 10 A max at Ta = 0 to 40C. These characteristics are guaranteed only for

the LL-version.

3. tRC = Read cycle time.

Low VCC Data Retention Waveform (1) (CS1 Controlled)

tCDR

Data retention mode

tR

VCC

4.5 V

2.2 V

VDR

CS1

0V

CS1 VCC 0.2 V

HM6264A Series

HM6264A Series

Low VCC Data Retention Waveform (2) (CS2 Controlled)

Data retention mode

VCC

4.5 V

tCDR

tR

CS2

VDR

0.4 V

0V

10

CS2 0.2 V

Anda mungkin juga menyukai

- HM6264B Series: 64 K SRAM (8-Kword 8-Bit)Dokumen16 halamanHM6264B Series: 64 K SRAM (8-Kword 8-Bit)Nguyen Hai Tran SonBelum ada peringkat

- 6264 DatasheetDokumen15 halaman6264 DatasheetjlfmotaBelum ada peringkat

- 4Mb-SRAM 512Kx1BDokumen18 halaman4Mb-SRAM 512Kx1BserjaniBelum ada peringkat

- 24LC02BDokumen26 halaman24LC02Bjab_arx1Belum ada peringkat

- HM62256B Series: 32,768-Word 8-Bit High Speed CMOS Static RAMDokumen15 halamanHM62256B Series: 32,768-Word 8-Bit High Speed CMOS Static RAMJose LopezBelum ada peringkat

- HY6264A - (I) Series: 8kx8bit CMOS SRAMDokumen9 halamanHY6264A - (I) Series: 8kx8bit CMOS SRAMLexuanhoa ProBelum ada peringkat

- 128mbit SDRAM: 2M X 16bit X 4 Banks Synchronous DRAM LVTTLDokumen11 halaman128mbit SDRAM: 2M X 16bit X 4 Banks Synchronous DRAM LVTTLThiago Cristiano TavaresBelum ada peringkat

- Hanbit Hmn1288D: Non-Volatile Sram Module 1mbit (128K X 8-Bit), 32Pin-Dip, 5V Part No. Hmn1288DDokumen9 halamanHanbit Hmn1288D: Non-Volatile Sram Module 1mbit (128K X 8-Bit), 32Pin-Dip, 5V Part No. Hmn1288DDeepa DevarajBelum ada peringkat

- 000 0 Hy628100bllg 70Dokumen9 halaman000 0 Hy628100bllg 70Deepa DevarajBelum ada peringkat

- 2114 SramDokumen4 halaman2114 SramKarloz IbarraBelum ada peringkat

- 24 LC 2561Dokumen12 halaman24 LC 2561ricardo_MassisBelum ada peringkat

- 32kx8bit CMOS SRAM: HY62256B SeriesDokumen9 halaman32kx8bit CMOS SRAM: HY62256B SeriesShiwam IsrieBelum ada peringkat

- 24AA00/24LC00/24C00: 128 Bit I C Bus Serial EEPROMDokumen18 halaman24AA00/24LC00/24C00: 128 Bit I C Bus Serial EEPROMJuliano GriguloBelum ada peringkat

- OpAmp - MCP6241Dokumen28 halamanOpAmp - MCP6241Ludwig SchmidtBelum ada peringkat

- Cmos 24aa256 & 24LC256Dokumen12 halamanCmos 24aa256 & 24LC256Someguy123551234512Belum ada peringkat

- MemoriaDokumen7 halamanMemoriaEduardo TaglialavoreBelum ada peringkat

- Hanbit Hmn328D: Non-Volatile Sram Module 256kbit (32K X 8-Bit), 28pin Dip, 5V Part No. Hmn328DDokumen9 halamanHanbit Hmn328D: Non-Volatile Sram Module 256kbit (32K X 8-Bit), 28pin Dip, 5V Part No. Hmn328DDeepa DevarajBelum ada peringkat

- ¡ Semiconductor: MSM80C88A-10RS/GS/JSDokumen37 halaman¡ Semiconductor: MSM80C88A-10RS/GS/JSZarate BismkBelum ada peringkat

- 24 LC 16Dokumen32 halaman24 LC 16Jos RoBelum ada peringkat

- Max3160 Max3162Dokumen23 halamanMax3160 Max3162jb2015831Belum ada peringkat

- 24LC04BDokumen22 halaman24LC04BcarlosBelum ada peringkat

- 450 Μa, 5 Mhz Rail-To-Rail Op Amp: Features DescriptionDokumen32 halaman450 Μa, 5 Mhz Rail-To-Rail Op Amp: Features DescriptionYusuf UçkunBelum ada peringkat

- CD4553 Datasheet OKDokumen13 halamanCD4553 Datasheet OKCong ThoBelum ada peringkat

- THC63LVDM83R/THC63LVDM63R: General Description FeaturesDokumen13 halamanTHC63LVDM83R/THC63LVDM63R: General Description Featureshenry96sBelum ada peringkat

- Cmos Sram K6F2016U4E Family: Document TitleDokumen9 halamanCmos Sram K6F2016U4E Family: Document TitleSash BremecBelum ada peringkat

- IC-ON-LINE - CN In74hc164a 4331941Dokumen6 halamanIC-ON-LINE - CN In74hc164a 4331941enriquevagoBelum ada peringkat

- MC 14521Dokumen12 halamanMC 14521rrebollarBelum ada peringkat

- Tle 6220 PDFDokumen17 halamanTle 6220 PDFFabio JuniorBelum ada peringkat

- 24 LC 64Dokumen12 halaman24 LC 64achuthkumarBelum ada peringkat

- MC6821PDokumen10 halamanMC6821Pbobyof91Belum ada peringkat

- 8K X 8 Bit Fast Static RAM MCM6264C: MotorolaDokumen8 halaman8K X 8 Bit Fast Static RAM MCM6264C: Motorolajackiie16Belum ada peringkat

- Dual Retriggerable Monostable Multivibrator: Order CodesDokumen12 halamanDual Retriggerable Monostable Multivibrator: Order Codeswrite2skBelum ada peringkat

- 7214Dokumen12 halaman7214Dan EsentherBelum ada peringkat

- Memoria Ram 6264Dokumen14 halamanMemoria Ram 6264DOMINGOS ALADIRBelum ada peringkat

- 2M X 32 Sdram: 512K X 32bit X 4 Banks Synchronous DRAM LVTTL (3.3V)Dokumen12 halaman2M X 32 Sdram: 512K X 32bit X 4 Banks Synchronous DRAM LVTTL (3.3V)vsc2012Belum ada peringkat

- LTC2440 PDFDokumen28 halamanLTC2440 PDFyusufwpBelum ada peringkat

- 24lc08 EepromDokumen27 halaman24lc08 EepromIsmael Minchola CarhuasBelum ada peringkat

- 25LC160Dokumen21 halaman25LC160João JoséBelum ada peringkat

- 24 LC 32Dokumen14 halaman24 LC 32Shuchi Raju AgrawalBelum ada peringkat

- 1K 2.5V Dual Mode I C Serial EEPROMDokumen26 halaman1K 2.5V Dual Mode I C Serial EEPROMbalck_virusBelum ada peringkat

- Max7490 Max7491Dokumen18 halamanMax7490 Max7491xo9o6Belum ada peringkat

- LTC4151 I2C Current and Voltage MonitorDokumen18 halamanLTC4151 I2C Current and Voltage MonitorNegru P. PlantatieBelum ada peringkat

- 24AA00/24LC00/24C00: 128-Bit I C Bus Serial EEPROMDokumen4 halaman24AA00/24LC00/24C00: 128-Bit I C Bus Serial EEPROMcabalaestebanBelum ada peringkat

- 7473Dokumen8 halaman7473Merényi OszkárBelum ada peringkat

- SN754410 Quadruple Half-H Driver: 1,2EN 1A 1Y V 4A 4Y Heat Sink and Ground 3Y 3A 3,4EN Heat Sink and GroundDokumen10 halamanSN754410 Quadruple Half-H Driver: 1,2EN 1A 1Y V 4A 4Y Heat Sink and Ground 3Y 3A 3,4EN Heat Sink and GroundFrankin Esteban Carmona AguilarBelum ada peringkat

- Cmos Sram K6T1008C2E Family: Document TitleDokumen11 halamanCmos Sram K6T1008C2E Family: Document TitleOmar LeonBelum ada peringkat

- Description Features: CMOS Low-Power Monostable/Astable MultivibratorDokumen15 halamanDescription Features: CMOS Low-Power Monostable/Astable Multivibratorதினேஷ் குமார்Belum ada peringkat

- CD54HC14, CD74HC14, CD54HCT14, CD74HCT14: Features DescriptionDokumen16 halamanCD54HC14, CD74HC14, CD54HCT14, CD74HCT14: Features DescriptionAndrea DispoBelum ada peringkat

- D D D D D D D D D D D D: CD4066B Cmos Quad Bilateral SwitchDokumen20 halamanD D D D D D D D D D D D: CD4066B Cmos Quad Bilateral SwitchAnna Kaye Sapanhila AninBelum ada peringkat

- Dual Quick-PWM Step-Down Controller With Low-Power LDO and RTC Regulator For MAIN SuppliesDokumen24 halamanDual Quick-PWM Step-Down Controller With Low-Power LDO and RTC Regulator For MAIN SuppliesReklama BielskoBelum ada peringkat

- 4536BDokumen17 halaman4536BpandaypiraBelum ada peringkat

- CD40160BMS, CD40161BMS, CD40162BMS, CD40163BMS: CMOS Synchronous Programmable 4-Bit Counters FeaturesDokumen13 halamanCD40160BMS, CD40161BMS, CD40162BMS, CD40163BMS: CMOS Synchronous Programmable 4-Bit Counters FeaturesIonut TomaBelum ada peringkat

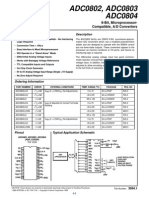

- ADC0802, ADC0803 ADC0804: Features DescriptionDokumen17 halamanADC0802, ADC0803 ADC0804: Features DescriptionSuryananda PadmadinataBelum ada peringkat

- 2.5V To 6.0V Micropower CMOS Op Amp: FeaturesDokumen42 halaman2.5V To 6.0V Micropower CMOS Op Amp: Featuresinside121Belum ada peringkat

- 32x8 SRAM DatasheetDokumen12 halaman32x8 SRAM DatasheetAhmet AyanBelum ada peringkat

- Max232 Maxim IC DatasheetDokumen7 halamanMax232 Maxim IC Datasheetcyanide0007Belum ada peringkat

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Dari EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Belum ada peringkat

- Ad 5933Dokumen2 halamanAd 5933Kaustuv MishraBelum ada peringkat

- How To Make A Powerpoint Presentation and How Not To: Amit Patra Department of Electrical Engineering IIT KharagpurDokumen4 halamanHow To Make A Powerpoint Presentation and How Not To: Amit Patra Department of Electrical Engineering IIT KharagpurKaustuv MishraBelum ada peringkat

- Embedded Sytem RoutroyDokumen16 halamanEmbedded Sytem RoutroyKaustuv MishraBelum ada peringkat

- Optimal Reception of Digital SignalsDokumen40 halamanOptimal Reception of Digital SignalsKaustuv Mishra100% (1)

- 1998-09 The Computer Paper - Ontario EditionDokumen165 halaman1998-09 The Computer Paper - Ontario EditionthecomputerpaperBelum ada peringkat

- Operating System AssignmentDokumen13 halamanOperating System AssignmentMarc AndalloBelum ada peringkat

- IT Support Technician PDFDokumen2 halamanIT Support Technician PDFAndres MauricioBelum ada peringkat

- Docu31714 EMC VNX5100 and VNX5300 Series Storage Systems Disk and OE MatrixDokumen7 halamanDocu31714 EMC VNX5100 and VNX5300 Series Storage Systems Disk and OE MatrixMariappan KalaivananBelum ada peringkat

- Bpo QuestionerDokumen4 halamanBpo QuestionerRose Marie D TupasBelum ada peringkat

- SIMCom 3G MQTT Application Note V1.00Dokumen18 halamanSIMCom 3G MQTT Application Note V1.00Sijeo PhilipBelum ada peringkat

- IQVIA Partnerships Agency Program - Mobile Intelligence (MI)Dokumen13 halamanIQVIA Partnerships Agency Program - Mobile Intelligence (MI)ybsmeBelum ada peringkat

- MVC - Entity Framework - SQL Server-1Dokumen56 halamanMVC - Entity Framework - SQL Server-1Mohan RaviBelum ada peringkat

- Allen Bradley Controllogix ManualDokumen40 halamanAllen Bradley Controllogix ManualkjfensBelum ada peringkat

- Ankon Gopal Banik: According To The Syllabus of Department of CSE, Gono BishwabidiyalayDokumen36 halamanAnkon Gopal Banik: According To The Syllabus of Department of CSE, Gono BishwabidiyalayAnkon Gopal BanikBelum ada peringkat

- DEFCON25Dokumen251 halamanDEFCON25宛俊Belum ada peringkat

- Photopea TutorialDokumen4 halamanPhotopea Tutorialapi-533357373Belum ada peringkat

- SCSR 1013 Digital Logic 2017/2018 Test 1Dokumen8 halamanSCSR 1013 Digital Logic 2017/2018 Test 1dad sadBelum ada peringkat

- ABEM Terraloc Pro User ManualDokumen101 halamanABEM Terraloc Pro User ManualMichael KazindaBelum ada peringkat

- The Book of Good CounselsDokumen184 halamanThe Book of Good CounselsJothiBelum ada peringkat

- 10 File Formats: 10.1 ATS HeaderDokumen6 halaman10 File Formats: 10.1 ATS HeaderMilenko MarkovicBelum ada peringkat

- LRMDS HandbookDokumen14 halamanLRMDS HandbookJerry G. GabacBelum ada peringkat

- C/c++questions With AnswersDokumen14 halamanC/c++questions With AnswersBunny ChughBelum ada peringkat

- Stephen Kasina CVDokumen4 halamanStephen Kasina CVStephen KasinaBelum ada peringkat

- Data Science Course Syllabus 01Dokumen20 halamanData Science Course Syllabus 01Ram Mohan Reddy Putta100% (1)

- Manual en Español Kip 3000Dokumen2 halamanManual en Español Kip 3000Ja De OstiaBelum ada peringkat

- FLIP - FLOPS Lab-Sheet-Digital-ElectronicsDokumen5 halamanFLIP - FLOPS Lab-Sheet-Digital-Electronicswakala manaseBelum ada peringkat

- How To Import Device Type in SAPDokumen4 halamanHow To Import Device Type in SAPMuhammad ShoaibBelum ada peringkat

- Computer Graphics 3Dokumen21 halamanComputer Graphics 3IFTHIQUAR AHAMED26Belum ada peringkat

- Curious Freaks Coding SheetDokumen6 halamanCurious Freaks Coding Sheetacknowledgeme1717Belum ada peringkat

- Live Hacking CD 1.1 Final-On A USB Thumb Drive-How To Make-Tutorial GuideDokumen10 halamanLive Hacking CD 1.1 Final-On A USB Thumb Drive-How To Make-Tutorial GuidePhil PhilatelyBelum ada peringkat

- Cisco Security Licensing and Software Access 20210511Dokumen81 halamanCisco Security Licensing and Software Access 20210511trustseepBelum ada peringkat

- Rpa - SMP V 0.1Dokumen18 halamanRpa - SMP V 0.1Srinivas KannanBelum ada peringkat

- Mokerlink Outdoor Wirelss - AP - User - ManualDokumen11 halamanMokerlink Outdoor Wirelss - AP - User - ManualJai Sri HariBelum ada peringkat

- Computer System: Classification of Computers by SizeDokumen25 halamanComputer System: Classification of Computers by SizeIndu ThottathilBelum ada peringkat