Art3 - (S1), Florian Ion, 17-22

Diunggah oleh

camiloHak Cipta

Format Tersedia

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniHak Cipta:

Format Tersedia

Art3 - (S1), Florian Ion, 17-22

Diunggah oleh

camiloHak Cipta:

Format Tersedia

Scientific Bulletin of the Electrical Engineering Faculty 2008

A COMPARATIVE STUDY OF SEPIC, CUK AND ZETA CONVERTERS

Florian ION 1 , Gabriel PREDUSCA

2.1. OPERATING PRINCIPLES

Abstract: In this paper a comparative study of DC-DC

converters is presented. The SEPIC, Cuk and ZETA

converters in applications are detailed. Also are presented

the operating simulation for these converters. The results

of simulations are compared with the measurements done

for a ZETA converter with an output of 3.3V and different

output currents.

2.1 Fundamental DC-DC Converters

From the viewpoint of input and output voltages V1

and Vo, the fundamental converters are: (1) step-down or

buck converters, (2) step-up or boost converters, (3) step

down/up or buck-boost converters. Figure 1 shows the

principle diagrams of these topologies.

Keywords: DC-DC converters, SEPIC converter, Cuk

converter, ZETA converter

1. INTRODUCTION

L1

Its well known that to have the maximum efficiency

of the solar panels, the load must be connected to the

solar panel through a DC-DC converter. The topologies

and the operation of these converters are very well

described in the literature. A classification of these

converters is presented in [1]. The authors of [1]

consider the DC-DC converters in six decades: (1)

classical/traditional converters, (2) multiple-quadrant

converters, (3) switched component converters, (4) softswitching converters, (5) synchronous rectifier

converters, (6) multiple energy-storage elements

resonant converters. The classical/traditional converters

are divided in five categories: (1) fundamental

converters, (2) transformer-type converters, (3)

developed converters, (4) voltage-lift converters, and (5)

super-lift converters.

The converters studied in this paper are classical

developed converters well known in literature like

converters in SEPIC (Single Ended Primary Inductance

Converter) topology, Cuk and ZETA (Positive Output

Luo Converter). The developed-type converters derived

from fundamental converters by addition of a low-pass

filter. In [2] these converters are considered like a

MASTER converter switched by a PWM signal, and a

SLAVE converter achieved with passive components.

Because the great usage of converters in the

topologies mentioned above in applications, we found

opportunity for a short presentation of operating

principles, simulations and some experimental results

in this work. The equations of main operating

parameters, advantages and disadvantages of each

topology are presented in chapter 2 of this paper. The

simulations and the measurements are presented in

chapter 3, and the final conclusions in chapter 4.

1

2

L2

V1

C1

Co

Rs

Co

Rs

Co

Rs

a)

D

L1

L2

V1

S

C1

b)

S

L1

V1

L1

C1

c)

Figure 1. Fundamental DC-DC Converters: a) buck

converter, b) boost converter, c) buck-boost converter.

In ideal operating conditions (no voltage loss on the

switch S, the average voltage across inductors L at

steady state zero, no current loss on capacitors C, and

no voltage loss on diode at forward conduction) the

equations of ratio Vo/V1 are:

for the buck converter (1):

Vo

=D

(1)

V1

where D is the duty cycle of PWM signal of switch S,

with the meaning from equation (2),

t

(2)

D = ON

T

Valahia University/Electronic Department, Targoviste, Romania, e-mail: flion@valahia.ro

Valahia University/Electronic Department, Targoviste, Romania, e-mail: gpredusca@valahia.ro

17

Scientific Bulletin of the Electrical Engineering Faculty 2008

where tON is the conduction time of switch S and T is

the period of PWM signal.

for the boost converter (3):

Vo

1

=

(3)

V1 1 D

for the buck-boost converter (4):

Vo

D

=

(4)

V1 1 D

In all these equations the internal resistance of

power supply V1 was considered zero [3].

L1

V1

L2

S

Co

Rs

Co

Rs

Co

Rs

a)

L1

L2

V1

S

2.2. Developed DC-DC converters

b)

S

Figure 2 shows the topologies of developed DC-DC

converters.

These topologies have few similitudes:

The equation of the transfer function of these

converters is (4), the same with that one of buck-boost

converter, if the conditions of Continuous Conduction

Mode CCM are assured.

These converters are used in different

applications, such as with solar panels, in systems

supplied with electrical energy where the output

voltage Vo of converter can be superior or inferior of

the input voltage V1 of converter. The fundamental

converters dont accept this situation. These converters

are integrated in the MPPT of solar panels.

The capacitor C assures the galvanic insulation

between input and output. The short-circuits or others

breakdown of the load dont affect the power supply

solar panels.

The output voltage becomes zero if the PWM

control signal of switch S is missing.

The diode D can be replaced by a transistor

switched synchronal with the main switch in the

synchronous converters.

The differences between these topologies are:

SEPIC and Cuk converters became from the boost

converter, and ZETA converter from the buck-boost

converter.

The ripple current in the load is greater for Cuk

and ZETA converters than SEPIC, because the SEPIC

converter has an inductor L2 that smooth the current

spikes.

The switch S of SEPIC ad Cuk converters is a N

channel MOS transistor that needs a Low Side driver,

when the ZETA converter has a P channel MOS

transistor that needs a High Side driver.

Because, these three topologies have many

advantages mentioned above, these things make

enable their integration in applications with a great

efficiency of using the solar energy in solar panels

with MPP trackers.

V1

L2

L1

D

c)

Figure 2. Developed DC-DC Converters: a) SEPIC

converter, b) Cuk converter, c) ZETA converter

2.3 Integration of convertors in MPPT systems

The perturb-andobserve (PAO) method for the

MPPT is an iterative approach. The MPP is obtained

by making the derivate of power equal with zero in the

feedback circuit that commands the duty cycle of

switch S. This is very useful because doesnt need the

disconnection of panels from the load. Through this

method can be reached good results if it is compared the

instantaneous conductance of panel with the incremental

conductance of panel the method is known as

Incremental Conductance Technique (ICT) [4].

If it is considered the equivalent circuit of the solar

panel like in Fig. 3, with vi the input voltage of panel

and ri the equivalent input resistance of panel, Pi the

input power, Po the output power (5), the

P = 0 means (6).

Pi = Po =

v i2

ri

(5)

v i

V

= i

(6)

ri

2 Ri

The method proposed in [4] resides in the

connection of a SEPIC or Cuk converter between the

solar panel and load. The converter works in

continuous current mode (CCM) through inductor L1

Figure 2 a), but with discontinuous voltage (DCV) on

the capacitor C. The duty cycle of PWM signal of

switch is adjusted in a proper way to achieve the input

resistance of converter equal with the output resistance

of solar panel. Figure 3 shows the equivalent circuit of

solar panel and converter.

18

Scientific Bulletin of the Electrical Engineering Faculty 2008

Figure 3. Equivalent circuit of a solar panel and

converter [4]

The operating equations of SEPIC converter in

DCV mode are the next: (7a) the voltage on

capacitor C, (7b) the voltage on diode D.

I

I 1 (1 d )TS

Vo 2 t , 0 < t < d 1TS

C

C

v C (t ) = Vo ,

d 1TS < t < dTS (7a)

I

1 (t dTS ) Vo,

dTS < t < TS

C

Vo + v C (t ), 0 < t < d 1TS

v D (t ) =

d1TS < t < TS

0,

(7b)

where I1 and I2 are the inductor currents - assumed to

be constant, dTS is the conduction time of switch, d1TS

is the conduction time of diode D, and TS is the period

1

of PWM signal of switch - TS =

, fS frequency of

fS

PWM signal.

The three sequences in one switching cycle are

shown in Figure 4.

Because the voltage of capacitor C at d1TS

I

is v C (d 1TS ) = Vo , the duty cycle is d 1 = 1 (1 d ) .

I2

In the steady state the voltage on the inductor L2 is

zero. From this moment the output voltage Vo is equal

with the average voltage of diode D (8).

Figure 4. Operating principle of the SEPIC converter.

a) equivalent circuits, b) theoretical waveforms [4]

3. Simulations

In this chapter it will be presented few

representative waveforms of each topology. The

simulations were done in OrCAD, in the next

conditions:

d

T

T

1 1S

Vo =

v D (t )dt = S I 1 (1 d )d 1

(8)

input voltage V1=12V,

TS 0

2C

output voltage Vo=3.3V,

Moreover, the voltage stress on the switch S is

load resistance RS=3.3,

given by (9).

duty cycle D=0.22,

In the same way can be determined the operating

switching frequency fS=500kHz,

equations of Cuk and ZETA topologies. This is

coupling capacitor C=47F,

shown in [4].

output capacitor Co=100F,

I1

inductors L1=L2=6.2H.

v stres = v C (TS ) + Vo = (1 d )TS

(9)

C

3.1 The SEPIC converter

To simulate the operation of SEPIC converters it

was used the diagram from Figure 2 a). In Figure 5 a),

b), and c), is shown the output voltage Vo, the ripple of

19

Scientific Bulletin of the Electrical Engineering Faculty 2008

output voltage Vo, and the voltage stress Vstress of

switch S.

At steady state after 1.5ms, these values are:

V0=3.5V, Vo=6mVpp, and Vstress=16V.

0V

-2.0V

6.0V

-4.0V

4.0V

-6.0V

0s

0.5ms

1.0ms

1.5ms

2.0ms

2.5ms

3.0ms

3.5ms

4.0ms

V(R4:2)

Time

2.0V

a) Vo output voltage

0V

-3.60V

-2.0V

0s

0.5ms

1.0ms

1.5ms

2.0ms

2.5ms

3.0ms

3.5ms

4.0ms

-3.65V

V(R4:2)

Time

Vo output voltage

a)

-3.70V

3.7200V

-3.75V

-3.80V

0.8773ms 0.9000ms

V(R4:2)

3.7150V

0.9500ms

1.0000ms

1.0500ms

1.1000ms

Time

b) Vo output ripple

3.7100V

20V

3.7056V

2.960ms

2.962ms

V(R4:2)

2.964ms

2.966ms

2.968ms

2.970ms

2.972ms

2.974ms

2.976ms

15V

2.978ms

Time

b)

Vo output ripple

10V

20V

5V

15V

0V

877.34us

878.00us

V(M2:d)

879.00us

880.00us

881.00us

882.00us

883.00us

884.00us

Time

c) Vstress voltage stress on switch

10V

5V

Figure 6. Simulated waveforms of Cuk converter: a)

output voltage, b) output ripple, c) voltage stress of switch

0V

2.96000ms

V(M2:d)

2.96400ms

2.96800ms

2.97200ms

2.97600ms

2.97897ms

Time

c)

Conclusions on simulations are in Table 1.

Vstress voltage stress on switch

Table 1. Simulation Results

Figure 5. Simulated waveforms of SEPIC converter: a)

output voltage, b) output ripple, c) voltage stress of switch

SEPIC

Topology

Cuk

ZETA

Vo [V]

3.51

3.51

3.41

Vo [mVpp]

28

26

Vstress [V]

16

16

16

Voltage

3.2. The Cuk conveter

To simulate the operation of Cuk converter it was

used the diagram from Figure 2 b). Figure 6 a), b) and

c) shows the waveforms of output voltage, output

ripple and voltage stress of switch in the same

conditions.

At steady state after 0.5ms, these values are:

V0=3.51V, Vo=28mVpp, and Vstress=16V.

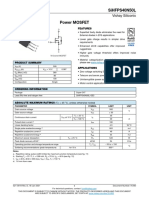

3.4. Experimental verifications

An experiment has been performed using a ZETA

topology on a LTC1622 a Current Mode Step-Down

DC/DC converter of Linear Technology [5]. The

schematic diagram is the typical application proposed

by the producer and is shown in Figure 8 [6].

In Figure 9 are the waveforms in the next

conditions: V1=8.3V, Vo=3.3V, RS=20 (Io=165mA).

The channels of oscilloscope represent: CH1 VG

PWM signal on the gate of MOS transistor, CH2 VD

drain voltage of MOS transistor, CH3 VC voltage

3.3. The ZETA converter

To simulate the operation of ZETA converter it was

used the diagram from Figure 2 c). Figure 7 a), b) and c)

shows the waveforms of output voltage, output ripple

and voltage stress of switch in the same conditions.

At steady state after 0.5ms, these values are:

V0=3.41V, Vo=26mVpp, and Vstress=16V.

20

Scientific Bulletin of the Electrical Engineering Faculty 2008

on positive pin of capacitor C, CH4 Vo output

voltage ripple.

In Figure 10 are the waveforms in these conditions:

V1=4.9V, Vo=3.4V, RS=10 (Io=340mA). It can be

observed other values for switching frequency and

duty cycle of PWM signal.

systems where these conditions are reached very often

like solar panels in different levels of solar radiation.

The results of measurements are in Table 2.

The circuit LTC1622 changes the switching

frequency Figure 9, 10, 11, in a wide range from

265 kHz to 1024 kHz. Also, the duty cycle D of PWM

signal in the gate of the MOS transistor is changed

according with the work conditions input and output

voltage, and the output current, to insure a constant

value of output voltage.

The ripple of output voltage measured in real

conditions is few times greater than that one obtained

in ideal conditions of simulations.

6.0V

4.0V

2.0V

0V

0s

0.5ms

1.0ms

1.5ms

2.0ms

2.5ms

3.0ms

3.5ms

4.0ms

V(R8:2)

Time

a) Vo output voltage

3.62V

3.61V

3.60V

3.59V

4.65ms

V(R8:2)

4.70ms

4.75ms

4.80ms

4.85ms

4.90ms

4.95ms

5.00ms

Time

b) Vo output ripple

20V

15V

Figure 9. Waveforms of VG, VD, VC, Vo in conditions:

V1=8.3V, Vo=3.3V, RS=20

10V

5V

0V

4.650ms

4.652ms

V(M1:s)- V(M1:d)

4.654ms

4.656ms

4.658ms

4.660ms

Time

c) Vstress voltage stress on switch

Figure 7. Simulated waveforms of ZETA converter: a)

output voltage, b) output ripple, c) voltage stress of switch

Figure 8. ZETA converter with LTC1622 [9]

Figure 10. Waveforms of VG, VD, VC, Vo in conditions:

V1=4.9V, Vo=3.4V, RS=10

The experimental waveforms in the conditions:

V1=7.1V, Vo=3.4V, RS=5 (Io=680mA) are shown in

Figure 11.

It can be seen that the ZETA converter build with the

LTC1622 integrated circuit works well with input

voltages less than output voltage and at an input voltage

over the output voltage. This advantage can be used in

21

Scientific Bulletin of the Electrical Engineering Faculty 2008

REFERENCES

[1]

F. L. Luo, H. Ye, Advanced DC/DC Converters,

CRC Press, 2004.

[2] S. Maniktala, Slave Converters Power Auxiliary

Outputs, EDN Magazine, Elsevier, 2002.

[3] P. Constantin, et al., Electronic industrial, Editura

Didactic i Pedagogic, Bucureti, 1983.

[4] H. S-H. Chung, et al., A Novel Maximum Power

Point Tracking Technique for Solar Panels Using a

SEPIC or Cuk Converter, IEEE Transaction on Power

Electronics, Vol. 18, No. 3, May 2003.

[5] M. Dobre, F. Ion - supervisor, Corecia factorului de

putere n convertoarele n comutaie cu reele de

comutare de ordin zero, Proiect de diplom,

Universitatea Valahia, Trgovite, iulie 2007.

***, LTC1622 Low Voltage Input Current Mode StepDown DC/DC Controller, Data Sheet, Linear

Technology, 1998.

Figure 11. Waveforms of VG, VD, VC, Vo in conditions:

V1=7,1V, Vo=3,4V, RS=5

Table 2. Measurement results

ZETA converter with LTC1622

with output voltage 3.3V

Voltage

V1=8.3V, V1=4.8V, V1=3.2V,

Io=165mA Io=165mA Io=165mA

Vo [Vpp] 1.37

0.82

0.60

fS [kHz]

265

524

504

Voltage

V1=8.3V, V1=4.9V, V1=8.3V, V1=7.1V,

Io=340mA Io=340mA Io=680mA Io=680mA

Vo [Vpp] 1.25

0.83

1.45

1.12

fS [kHz]

759

1024

562

913

4. CONCLUSIONS

In this paper was presented a comparative study of

DC-DC converters in SEPIC, Cuk and ZETA

topologies.

It was studied the fundamental converters and

developed converters in the topologies mentioned

above. The operation equations of main parameters

were presented.

Moreover, it was presented the simulations of these

converters in the same work conditions.

The waveforms that have seen on a ZETA

converter with a constant output voltage and variable

input voltage and load confirmed the simulations

results of that converter.

22

Anda mungkin juga menyukai

- Investigation of the Usefulness of the PowerWorld Simulator Program: Developed by "Glover, Overbye & Sarma" in the Solution of Power System ProblemsDari EverandInvestigation of the Usefulness of the PowerWorld Simulator Program: Developed by "Glover, Overbye & Sarma" in the Solution of Power System ProblemsBelum ada peringkat

- Lecture 1Dokumen93 halamanLecture 1ClasesBelum ada peringkat

- Boost DC-DC Converter Analysis and DesignDokumen13 halamanBoost DC-DC Converter Analysis and DesignKarthickBelum ada peringkat

- What Are The Advantages and Disadvantages of A Bi-Directional DC To A DC Converter?Dokumen14 halamanWhat Are The Advantages and Disadvantages of A Bi-Directional DC To A DC Converter?BALAJIBelum ada peringkat

- Design Calculations For Buck-Boost Converters: Michael Green Advanced Low Power SolutionsDokumen12 halamanDesign Calculations For Buck-Boost Converters: Michael Green Advanced Low Power SolutionsnandhakumarmeBelum ada peringkat

- Buck Boost ProjectDokumen24 halamanBuck Boost ProjectRonald LugwireBelum ada peringkat

- Line Commutated Converters ExplainedDokumen10 halamanLine Commutated Converters ExplainedJay Romar PabianiaBelum ada peringkat

- CUK CONVERTER: A Versatile DC-DC Converter TopologyDokumen13 halamanCUK CONVERTER: A Versatile DC-DC Converter TopologypakalagopalBelum ada peringkat

- Double Frequency Buck ConverterDokumen36 halamanDouble Frequency Buck ConverterSanthosh Guduru100% (1)

- Bi-Directional DC-to-DC Converter For Solar Applications With Battery BackupDokumen5 halamanBi-Directional DC-to-DC Converter For Solar Applications With Battery BackupPaulius BruneikaBelum ada peringkat

- Boost DesignDokumen4 halamanBoost DesignmuthukumartharaniBelum ada peringkat

- Boost ConverterDokumen8 halamanBoost Converterhamza abdo mohamoudBelum ada peringkat

- Exp 8 Buck ConverterDokumen7 halamanExp 8 Buck Converterusmpowerlab50% (2)

- Double Frequency Buck ConverterDokumen68 halamanDouble Frequency Buck ConverterSanthosh GuduruBelum ada peringkat

- Study and Design, Simulation of PWM Based Buck Converter For Low Power ApplicationDokumen17 halamanStudy and Design, Simulation of PWM Based Buck Converter For Low Power ApplicationIOSRjournalBelum ada peringkat

- PV BoostDokumen6 halamanPV BoostlestherroqueBelum ada peringkat

- TP 1800 DC-DC Converter For Hybrid Electric Vehicle and EV ArrowTimesDokumen7 halamanTP 1800 DC-DC Converter For Hybrid Electric Vehicle and EV ArrowTimespapipapii100% (1)

- Chap4-Buck Boost and FlybackDokumen29 halamanChap4-Buck Boost and FlybackArchit BaglaBelum ada peringkat

- Push-Pull ConverterDokumen3 halamanPush-Pull ConverterBill YoungBelum ada peringkat

- Buck ConvertorDokumen10 halamanBuck ConvertorGirish MohantyBelum ada peringkat

- Flyback Converter: J. FisherDokumen16 halamanFlyback Converter: J. FisherDaniel NimabwayaBelum ada peringkat

- Buck ConverterDokumen31 halamanBuck Converterbalak144Belum ada peringkat

- DC Link CurrentDokumen8 halamanDC Link CurrentsubbannaBelum ada peringkat

- Buck-boost converter project reportDokumen3 halamanBuck-boost converter project reportArnoldo ZereceroBelum ada peringkat

- Analyze Buck-Boost Converter Lab Using Power MOSEFTDokumen6 halamanAnalyze Buck-Boost Converter Lab Using Power MOSEFTFALSERBelum ada peringkat

- Unsymmetrical Fault AnalysisDokumen49 halamanUnsymmetrical Fault AnalysisabdulbabulBelum ada peringkat

- DC - Ac Inv.Dokumen82 halamanDC - Ac Inv.Jegadeeswari GBelum ada peringkat

- DC-DC ConverterDokumen24 halamanDC-DC ConverterkandularanjithBelum ada peringkat

- Buck ConvertersDokumen15 halamanBuck Convertersmuddassir07100% (2)

- Lab ReportDokumen15 halamanLab Reportaeoliano0% (1)

- DC-DC ConvertersDokumen8 halamanDC-DC ConvertersNuruddin MuktaruddinBelum ada peringkat

- Diff BTWN MOSFET and BJTDokumen2 halamanDiff BTWN MOSFET and BJTMadan R HonnalagereBelum ada peringkat

- Design and Control of A Buck-Boost DC-DC Power ConverterDokumen65 halamanDesign and Control of A Buck-Boost DC-DC Power ConverterMurad Lansa Abdul Khader100% (1)

- Generating 50Hz PWM Using PIC16F877ADokumen2 halamanGenerating 50Hz PWM Using PIC16F877AZarko DacevicBelum ada peringkat

- Chapter 3 MSDokumen42 halamanChapter 3 MSRounak ChoudhuryBelum ada peringkat

- Operation of DC/DC Converter For Hybrid Electric Vehicle: Atul Kumar and Prerna GaurDokumen6 halamanOperation of DC/DC Converter For Hybrid Electric Vehicle: Atul Kumar and Prerna GaurAhana MalhotraBelum ada peringkat

- DC-DC Converter FundamentalsDokumen63 halamanDC-DC Converter FundamentalsFaida HamidBelum ada peringkat

- Z Source InverterDokumen16 halamanZ Source InverterpradeepagrahariBelum ada peringkat

- EMT 369 Wk2 Power Semiconductor Devices (GC)Dokumen53 halamanEMT 369 Wk2 Power Semiconductor Devices (GC)Ashraf YusofBelum ada peringkat

- Push Pull ConvertersDokumen44 halamanPush Pull ConvertersRaminBelum ada peringkat

- Theory:: Experiment 3 Buck ConverterDokumen3 halamanTheory:: Experiment 3 Buck ConverterRAVI DUTTBelum ada peringkat

- BLDC Sinusoidal ControlDokumen6 halamanBLDC Sinusoidal ControlOctavian MîrţiBelum ada peringkat

- L14 Three Phase Half Controlled ConverterDokumen18 halamanL14 Three Phase Half Controlled Converterapi-19951707Belum ada peringkat

- ARDUINO SPWM SINE INVERTER PROJECT GUIDEDokumen5 halamanARDUINO SPWM SINE INVERTER PROJECT GUIDEmaurilioctbaBelum ada peringkat

- PE Lecture 1Dokumen31 halamanPE Lecture 1AhmedSeragBelum ada peringkat

- 1.single Phase AC To DC Fully Controlled Converter PDFDokumen10 halaman1.single Phase AC To DC Fully Controlled Converter PDFAshwin RaghavanBelum ada peringkat

- Chopper DC To DC ConverterDokumen37 halamanChopper DC To DC ConverterGautam Kumar100% (1)

- Magnetics Design: 11/21/21 Dept. of Electrical & Electronics Engg., MIT - Manipal 1Dokumen107 halamanMagnetics Design: 11/21/21 Dept. of Electrical & Electronics Engg., MIT - Manipal 1timothybijuvBelum ada peringkat

- Thyristor Characteristics AnalysisDokumen15 halamanThyristor Characteristics AnalysisRoy Jonathan Adorna AvilaBelum ada peringkat

- Buck - Boost ConverterDokumen9 halamanBuck - Boost Converterhamza abdo mohamoud100% (1)

- EE309 Notes 07 PDFDokumen4 halamanEE309 Notes 07 PDFbals123456100% (1)

- Electromagnetic Foundations of Electrical EngineeringDari EverandElectromagnetic Foundations of Electrical EngineeringBelum ada peringkat

- Multilevel Inverters: Introduction and Emergent TopologiesDari EverandMultilevel Inverters: Introduction and Emergent TopologiesBelum ada peringkat

- AC Circuit Modeling of Switching Power ConvertersDokumen65 halamanAC Circuit Modeling of Switching Power Convertershey_gluppyBelum ada peringkat

- Buck, Boost and Buck-Boost Inverter ComparisonDokumen6 halamanBuck, Boost and Buck-Boost Inverter ComparisonIndra PratamaBelum ada peringkat

- Analysis of SEPIC for PV using PI and Current Mode ControlDokumen4 halamanAnalysis of SEPIC for PV using PI and Current Mode ControlSindhujaSindhuBelum ada peringkat

- Presentation Paper On DGDokumen5 halamanPresentation Paper On DGAlok Bikash SadangiBelum ada peringkat

- Transformer Less DC - DC Converter With High Step Up Voltage Gain MethodDokumen6 halamanTransformer Less DC - DC Converter With High Step Up Voltage Gain Methodsurendiran123Belum ada peringkat

- PMP Exam Prep Study Group: Project Management ProfessionalDokumen59 halamanPMP Exam Prep Study Group: Project Management ProfessionalcamiloBelum ada peringkat

- PMP Exam Prep Study Group: Project Management ProfessionalDokumen52 halamanPMP Exam Prep Study Group: Project Management ProfessionalcamiloBelum ada peringkat

- PMP Exam Prep Study Group: Project Management ProfessionalDokumen29 halamanPMP Exam Prep Study Group: Project Management ProfessionalcamiloBelum ada peringkat

- NOD Breathing Normally WorkbookDokumen4 halamanNOD Breathing Normally WorkbookcamiloBelum ada peringkat

- Helixii1 61Dokumen104 halamanHelixii1 61camiloBelum ada peringkat

- PMP Exam Prep Study Group: Project Management ProfessionalDokumen37 halamanPMP Exam Prep Study Group: Project Management ProfessionalcamiloBelum ada peringkat

- PMP Exam Prep Study Group: Project Management ProfessionalDokumen29 halamanPMP Exam Prep Study Group: Project Management ProfessionalcamiloBelum ada peringkat

- PMO Setup Chapter 3Dokumen36 halamanPMO Setup Chapter 3camiloBelum ada peringkat

- Assignments Module 2Dokumen1 halamanAssignments Module 2camiloBelum ada peringkat

- Eg 3170 NotesDokumen38 halamanEg 3170 NotesAnonymous WkbmWCa8MBelum ada peringkat

- BPI1 BDokumen16 halamanBPI1 BcamiloBelum ada peringkat

- A Quadruple Tank Process Control ExperimentDokumen26 halamanA Quadruple Tank Process Control ExperimentcamiloBelum ada peringkat

- Universities of USADokumen19 halamanUniversities of USAcamiloBelum ada peringkat

- Tips For Taking The PMP ExamDokumen1 halamanTips For Taking The PMP ExamcamiloBelum ada peringkat

- Solución Tarea N°2: Parte A Modelo de Paneles PV Con Convertidor DC/AC MonofásicoDokumen13 halamanSolución Tarea N°2: Parte A Modelo de Paneles PV Con Convertidor DC/AC MonofásicocamiloBelum ada peringkat

- Rev IsarDokumen5 halamanRev IsarcamiloBelum ada peringkat

- Solución Tarea N°2: Ki KiDokumen26 halamanSolución Tarea N°2: Ki KicamiloBelum ada peringkat

- Top 50 Most Common Irregular Verbs in EnglishDokumen2 halamanTop 50 Most Common Irregular Verbs in EnglishFranz AioláBelum ada peringkat

- Chapter 9Dokumen22 halamanChapter 9camiloBelum ada peringkat

- Horario M2 Tutor and Native Speaker (Completo)Dokumen2 halamanHorario M2 Tutor and Native Speaker (Completo)camiloBelum ada peringkat

- ANP-29 ZetaConverterBasics 071107Dokumen9 halamanANP-29 ZetaConverterBasics 071107ngayhevuiBelum ada peringkat

- Zeta Converter Applied in Power Factor CorrectionDokumen14 halamanZeta Converter Applied in Power Factor CorrectioncamiloBelum ada peringkat

- Transfer Function to State Space FormDokumen15 halamanTransfer Function to State Space FormcamiloBelum ada peringkat

- Ejemplo Amathcad Buck BoostDokumen5 halamanEjemplo Amathcad Buck BoostcamiloBelum ada peringkat

- 55 RuselerDokumen8 halaman55 RuselercamiloBelum ada peringkat

- Power Quality Improvement in Switched Reluctance Motor Drive Using Zeta ConverterDokumen5 halamanPower Quality Improvement in Switched Reluctance Motor Drive Using Zeta ConvertercamiloBelum ada peringkat

- May 201413Dokumen3 halamanMay 201413camiloBelum ada peringkat

- Conf TenDokumen6 halamanConf TencamiloBelum ada peringkat

- SEPIC Converter: A Modified Boost-Buck DC-DC ConverterDokumen15 halamanSEPIC Converter: A Modified Boost-Buck DC-DC ConverterAbhi NáyBelum ada peringkat

- AF291 Chilling Unit Hiver QAP.Dokumen4 halamanAF291 Chilling Unit Hiver QAP.Deepak UpadhyayBelum ada peringkat

- Basic Troubleshooting StepsDokumen7 halamanBasic Troubleshooting Stepsगणेश पराजुलीBelum ada peringkat

- Monovolt pk30 pk60 pk120 pk240Dokumen9 halamanMonovolt pk30 pk60 pk120 pk240yang yangBelum ada peringkat

- Linear Opto IsolatorsDokumen105 halamanLinear Opto Isolatorszawmintun1Belum ada peringkat

- PWM 2 Level and 3 LevelDokumen7 halamanPWM 2 Level and 3 LevelnewrajasinghBelum ada peringkat

- EEVblog Electronics Community Forum - SMPS Repair: Name the Controller ICDokumen19 halamanEEVblog Electronics Community Forum - SMPS Repair: Name the Controller ICRICHARDBelum ada peringkat

- Sihfps 40 N 50 LDokumen10 halamanSihfps 40 N 50 LRAMESH JUNJUBelum ada peringkat

- CPCL Transformer Rectifier Brochure 2022 1Dokumen6 halamanCPCL Transformer Rectifier Brochure 2022 1Taiwo AdenipekunBelum ada peringkat

- Solar Powered BLDC Motor Drive Using CUK Converter: Dr.M.Gopila, Mr. S. Madhubalan, M.BaluDokumen6 halamanSolar Powered BLDC Motor Drive Using CUK Converter: Dr.M.Gopila, Mr. S. Madhubalan, M.BaluGangadhar AkkiBelum ada peringkat

- Design and Implementation of Asymmetric Half-Bridge Flyback Converter For USB Power Delivery ApplicationsDokumen8 halamanDesign and Implementation of Asymmetric Half-Bridge Flyback Converter For USB Power Delivery Applicationsfunnylearn08Belum ada peringkat

- LG 42PQ30 Plasma TV Single Scan Troubleshooting Training Manual 1 PDFDokumen123 halamanLG 42PQ30 Plasma TV Single Scan Troubleshooting Training Manual 1 PDFJim FordBelum ada peringkat

- ICIEAPaper Voltage Sags PsimDokumen8 halamanICIEAPaper Voltage Sags Psimjefao_MMABelum ada peringkat

- SMPSDokumen8 halamanSMPSnishant thakreBelum ada peringkat

- TP03AL220S03LSW 2W 85-265VAC Input 3.3VDC OutputDokumen3 halamanTP03AL220S03LSW 2W 85-265VAC Input 3.3VDC OutputtoppowerBelum ada peringkat

- Samsung 2011 & 2013 LCD-LED TV Training GuideDokumen366 halamanSamsung 2011 & 2013 LCD-LED TV Training GuideGeert GeensBelum ada peringkat

- TIDA-010054 Design GuideDokumen81 halamanTIDA-010054 Design GuidebocarocaBelum ada peringkat

- Design Method of 6-Element Boundary Gain For LLC Resonant Converter of Electric VehicleDokumen11 halamanDesign Method of 6-Element Boundary Gain For LLC Resonant Converter of Electric VehicleSh M AaqibBelum ada peringkat

- B Tech-EXTCDokumen164 halamanB Tech-EXTCANGEL 69Belum ada peringkat

- KST 01Dokumen1 halamanKST 01sanjeevBelum ada peringkat

- Rectify Faulty Switchmode Power Supply ComponentsDokumen14 halamanRectify Faulty Switchmode Power Supply ComponentsVasilis ChrimatopoulosBelum ada peringkat

- SMPS ComponentsDokumen2 halamanSMPS Componentsaloksxn.careerBelum ada peringkat

- PFC Design PDFDokumen35 halamanPFC Design PDFAnil SharmaBelum ada peringkat

- DPG30I300PADokumen5 halamanDPG30I300PAedgar_dauzonBelum ada peringkat

- Applied Energy: Luigi Rubino, Clemente Capasso, Ottorino VeneriDokumen27 halamanApplied Energy: Luigi Rubino, Clemente Capasso, Ottorino VeneriDiego CamachoBelum ada peringkat

- 3BR4765JZ 104 PDFDokumen32 halaman3BR4765JZ 104 PDFJose Barroso GuerraBelum ada peringkat

- bd93941xx e PDFDokumen30 halamanbd93941xx e PDFLeonardo GpontoBelum ada peringkat

- 150KHz 3A PWM Buck DC/DC Converter ModuleDokumen11 halaman150KHz 3A PWM Buck DC/DC Converter Modulebibib bibibBelum ada peringkat

- Philips Chasis Cts-Aa Service ManualDokumen25 halamanPhilips Chasis Cts-Aa Service ManualveronrazvyBelum ada peringkat

- Mouseen Iti Report 333Dokumen39 halamanMouseen Iti Report 333Akshay powar100% (1)