36 Clock

Diunggah oleh

lizhaohuiJudul Asli

Hak Cipta

Format Tersedia

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniHak Cipta:

Format Tersedia

36 Clock

Diunggah oleh

lizhaohuiHak Cipta:

Format Tersedia

RAN Feature Description

Table of Contents

Table of Contents

Chapter 36 Clock........................................................................................................................ 36-1

36.1 Introduction................................................................................................................... 36-1

36.1.1 Definition............................................................................................................. 36-1

36.1.2 Purposes............................................................................................................ 36-1

36.1.3 Terms and Abbreviations....................................................................................36-2

36.2 Availability..................................................................................................................... 36-5

36.2.1 Involved Network Element..................................................................................36-5

36.2.2 Software Release............................................................................................... 36-5

36.2.3 Miscellaneous..................................................................................................... 36-5

36.3 Impact........................................................................................................................... 36-5

36.3.1 On System Performance....................................................................................36-5

36.3.2 On Other Features.............................................................................................. 36-6

36.4 Restrictions................................................................................................................... 36-6

36.5 Technical Description.................................................................................................... 36-6

36.5.1 Clock Systems Configuration Model...................................................................36-6

36.5.2 NodeB Clock System.......................................................................................... 36-6

36.5.3 RNC Clock System........................................................................................... 36-11

36.6 Capabilities................................................................................................................. 36-17

36.7 Implementation........................................................................................................... 36-17

36.7.1 Enabling the Clock Feature..............................................................................36-17

36.7.2 Reconfiguring Clock Parameters......................................................................36-20

36.7.3 Disabling the Clock Feature..............................................................................36-22

36.8 Maintenance Information.............................................................................................36-23

36.8.1 Alarms............................................................................................................... 36-23

36.8.2 Counters........................................................................................................... 36-24

36.9 References.................................................................................................................. 36-24

Huawei Technologies Proprietary

i

RAN Feature Description

List of Figures

List of Figures

Figure 36-1 Synchronization model....................................................................................36-2

Figure 36-2 Clock system configuration model...................................................................36-6

Figure 36-3 Synchronization with Iub clock signals.............................................................36-8

Figure 36-4 Synchronization with GPS clock signals..........................................................36-9

Figure 36-5 Synchronization with GPS clock signals........................................................36-10

Figure 36-6 Synchronization with external reference clock signals...................................36-10

Figure 36-7 Structure of the RNC clock system................................................................36-13

Huawei Technologies Proprietary

ii

RAN Feature Description

List of Tables

List of Tables

Table 36-1 NEs required for the clock feature.....................................................................36-5

Table 36-2 RAN product and related versions.....................................................................36-5

Table 36-3 Clock sources.................................................................................................. 36-11

Table 36-4 Processing of a system timing signal inside the RNC......................................36-14

Table 36-5 Commands to enable the feature on the NodeB side......................................36-17

Table 36-6 Commands to enable the feature on RNC side...............................................36-19

Table 36-7 Commands to reconfigure clock parameters on the NodeB side.....................36-20

Table 36-8 Commands to reconfigure clock parameters on the RNC side........................36-21

Huawei Technologies Proprietary

iii

RAN Feature Description

Chapter 36 Clock

Chapter 36 Clock

36.1 Introduction

36.1.1 Definition

The clock feature involves some basic concepts such as clock source, reference

clock source, and clock working mode.

GPS reference source

The built-in GPS receiver of the RNC output signals to the precision of second.

Network Elements (NEs) such as NodeB track this clock source through Phaselocked Loop (PLL) and use it as the primary reference clock.

Iub/Iu reference clock source

The clock source of NEs such as NodeB can be synchronized with the line clock

sources of its upper-level NE such as RNC. The NodeB selects the reference

clock source from one line for the NMPT, a main control and timing unit.

BITS clock source

BITS clock sources are of three types: BITS1 2 MHz, BITS1 2 Mbps, and 8

kHz.

36.1.2 Purposes

Network synchronization relates to the distribution of synchronization references to

UTRAN nodes and the stability of the clocks in the UTRAN (and performance

requirements on UTRAN internal interfaces).

Huawei Technologies Proprietary

1

RAN Feature Description

Chapter 36 Clock

Vocoder

CN

Time

Alignment

Handling

RNS

RNC

RNC

Transport

Channel

Synchronisation

Node

B

Node

B

Radio

Interface

Synchronisation

Node

B

Node

B

Node

B

UTRAN

UE1

[TDD] Cell

Sync.

UE2

Optional TDD only input &

output sync ports

Figure 1.1 Synchronization model

The distribution of an accurate frequency reference to the network elements in the

UTRAN is related to several aspects. One main issue is the possibility to provide a

synchronization reference with a frequency whose accuracy is better than 0.05 ppm

at the NodeB in order to properly generate signals on the radio interface. Therefore,

when the NodeB extracts reference clock signals from a line to the RNC, the longterm stability of the RNC clock must be higher than 0.05 ppm.

Clock sources and working modes of various NEs are important issues. This chapter

mainly describes RAN clocks.

RAN clocks must provide reliable clock sources for the NEs in the RAN system; thus

meeting the specifications for clock accuracy stated in protocols and avoiding

asynchronization between NEs.

When exceptions occur to clock sources, the RNC and the NodeB must report related

alarms and start the backup scheme to ensure that the system is not affected.

36.1.3 Terms and Abbreviations

I. Terms

Term

Description

Free-run

A mode in which the crystal oscillator of the NMPT in the NodeB

mode

keeps working without being affected by the change of its external

reference clock source.

Huawei Technologies Proprietary

2

RAN Feature Description

Chapter 36 Clock

Term

Description

Fast pull-in

When the external reference clock source is operational, the

mode

system adjusts its local oscillator by a large step size, depending

on the reference clock source. The adjustment aims to enable the

system to work in slow pull-in mode as soon as possible

In fast pull-in mode, the frequency offset is compensated with a

single step as required to get the system to work in slow pull-in

mode or locked mode as soon as possible.

Slow pull-in

When the external reference clock source is operational and the

mode

offset between the source and the center frequency saved on the

system is within 0.4 Hz, the system adjusts the local oscillator with

a smaller step size to smoothly switch the system to locked mode.

During the slow pull-in phase, the frequency offset is also

compensated as required.

Locked

When the external reference clock source is operational and the

mode

offset between the source and the center frequency saved on the

system is within 0.2 Hz, the system begins to work in locked

mode.

In this mode, the system does not adjust the local oscillator, which

helps to ensure that the synchronization error between the local

oscillator and the upper-level clock source is smaller than 0.05

ppm, as specified by 3GPP protocols.

Hold mode

If the reference clock source is faulty (loss or unreasonable offset)

during locking, the system starts to work in hold mode.

In this mode:

The system works at the frequency (usually the center

frequency) before the hold mode is started. The system works

in pull-in mode after the reference clock source comes back to

normal.

The system starts to work in fast pull-in mode to avoid abrupt

frequency change if the source is recovered in a few days.

Huawei Technologies Proprietary

3

RAN Feature Description

Chapter 36 Clock

Term

Description

Current

A dynamic value written into the DAC by software.

(frequency)

During phase locking, the system can adjust the value according to

DA value

frequency offset until the clock works in locked mode. This value

changes with the changes of the signals of the clock source, and it

is not stored on a static storage. This instant value is lost after the

power-off.

Center

A DA value to the precision of 0.05 ppm that is stored on a static

(frequency)

storage and enables the OCXO to work at 10 MHz within a short

DA value

period, for example, one month. Each time when the clock module

is initialized, the module uses the center DA value as the current

DA value before phase-locking and as a criterion for large

frequency offset. When exceptions occur to the clock source, the

clock module works in free-run mode with the center DA value.

After the clock works in locked mode for a period, for example, 7

consecutive days, a new center DA value calculated by weighting

the current DA value within this period is written into the storage.

Initial DA

The initial DA value is the calibrated center frequency DA value

value

preset in a board before its delivery. It is stored on the static

storage. When the system is started for the first time, the center

frequency DA value is written into the configuration file as the initial

DA value.

Term

Description

Clock source

The loss of clock source occurs when the clock module does not

loss

detect any pulses of the clock source for a specified interval, for

example, 30 seconds.

Clock source

Jitter of clock source occurs when the clock module detects large

jitter

frequency offsets continuously for many times.

Large

Large frequency offset of clock source occurs when the clock

frequency

module detects that the offset between the frequency of the clock

offset

source and the center frequency of the local clock exceeds the

specified value, for example, 1 Hz.

Normal clock

The clock source is normal when no loss, jitter, or large frequency

source

offset occurs.

Huawei Technologies Proprietary

4

RAN Feature Description

Chapter 36 Clock

II. Abbreviations

Abbreviation

Full Spelling

3GPP

3rd Generation Partnership Project

BITS

Building Integrated Timing Supply System

DAC

Digit-Analog Converter

DDS

Direct Digital Synthesis

GPS

Global Positioning System

LMT

Local Maintenance Terminal

MML

Man-Machine Language

OCXO

Oven Controlled Crystal Oscillator

PLL

Phase-locked Loop

RAN

Radio Access Network

RNC

Radio Network Controller

RFN

RNC Frame Number

RNC

Radio Network Controller

WCDMA

Wideband CDMA

WRBS

WCDMA RNC Business Subrackv

WRSS

WCDMA RNC Switch Subrack

36.2 Availability

36.2.1 Involved Network Element

Table 1.1 shows the Network Elements (NEs) required for the clock feature.

Table 1.1 NEs required for the clock feature.

UE

NodeB

RNC

MSC Server

MGW

Huawei Technologies Proprietary

5

SGSN

GGSN

HLR

RAN Feature Description

Chapter 36 Clock

Note:

= not required

= required

36.2.2 Software Release

Table 1.1 describes the versions of the RAN products that support the clock feature.

Table 1.1 RAN product and related versions

Product

Version

RNC

BSC6800

V100R002 and later releases

NodeB

DBS3800

V100R006 and later releases

BTS3812A

V100R005 and later releases

BTS3812E

V100R005 and later releases

36.2.3 Miscellaneous

None.

36.3 Impact

36.3.1 On System Performance

RAN clocks must provide reliable clock sources for the NEs in the RAN system; thus

meeting the specifications for clock accuracy stated in protocols and avoiding

asynchronization between NEs.

36.3.2 On Other Features

None.

36.4 Restrictions

None.

36.5 Technical Description

The description of clocks in this section is based on NodeB and RNC.

Huawei Technologies Proprietary

6

RAN Feature Description

Chapter 36 Clock

36.5.1 Clock Systems Configuration Model

The configuration model for clock systems is show in Figure 1.1.

NodeB

RNC

EquimentClass

EquimentClass

CLKSRC.Class

CLKMODE.Class

System Clock Working Mode

Clock Source Type

Clock source priority

Figure 1.1 Clock system configuration model

36.5.2 NodeB Clock System

In compliance with 3GPP protocols, the NodeB clock must have a higher clock

precision. The frequency stability of the 10 MHz master of the NodeB is lower than

0.05 ppm.

The NodeB can work in multiple clock synchronization modes to suit different clock

topologies:

Synchronization with the Iub clock (default mode)

Synchronization with GPS

Synchronization with the BITS

The clock module of the NodeB performs frequency or phase discrimination of the

selected clock source, controls the input voltage of the local OCXO/TXCO that can

provide 10 MHz signals for the baseband boards and RF modules of the NodeB.

The description below is based on BTS3812E and BTS3812A.

You can enable or disable the clock synchronization modes of the NodeB by setting

the parameters System Clock Working Mode and CLKSRC. For example, to enable

the synchronization with the Iub clock, set the System Clock Working Mode

parameter to MANUAL, and the Clock Source Type parameter to LINE. To disable

the synchronization with the Iub clock, change any value of the System Clock

Working Mode or Clock Source Type parameter.

Huawei Technologies Proprietary

7

RAN Feature Description

Chapter 36 Clock

Parameter Name

Parameter ID

GUI Range

Physical Range & Unit

System Clock Working Mode

MODE

MANUAL, FREE

None

Default Value

MANUAL

Optional/Mandatory

Mandatory

MML Command

SET CLKMODE

Description:

Use this command to change NodeB clock working mode as MANUAL or FREE.

Parameter Name

Parameter ID

GUI Range

Clock Source Type

CLKSRC

GPS (GPS clock source), BITS (BITS clock

source (for indoor BBU), LINE (line clock

source)

Physical Range & Unit

None

Default Value

LINE

Optional/Mandatory

MML Command

Mandatory

SET CLKMODE

Description:

Use this command to modify the reference clock source of the NodeB. It is valid

only when the System Clock Working Mode parameter is set to MANUAL.

When NodeB is operational, it is necessary for it to trace an external clock to

correct its clock frequency. That clock is referred to as the reference clock source.

The reference clock source can be GPS, line clock, or external clock.

Configuration Rule and Restriction:

The parameter Clock Source Type is valid only when the parameter System

Clock Working Mode is set to MANUAL.

Huawei Technologies Proprietary

8

RAN Feature Description

Chapter 36 Clock

I. Synchronization with the Iub Clock Signals

Figure 1.1 shows the synchronization with Iub clock signals.

NMON

HULP

NMPT

F_CLK

Iub clock

signals

NDTI/

NAOI

8k

Clock

module

F_CLK BFN

HDLP

CLK-4x

BFN

CLK-4x

F_CLK

HBBI

CLK-4x

MTRU

BFN

Figure 1.1 Synchronization with Iub clock signals

The clock signals are processed and synchronized as follows:

1)

The NodeB extracts 8 kHz clock signals from Iub transmission lines.

2)

The NDTI or NAOI transmits the clock signals to the clock module in the NMPT.

3)

Through phase locking and frequency dividing, the clock module converts the

clock signals into various clock signals required by the NodeB, for example,

frame clock (F_CLK), clock at 4x chip rate (CLK_4X), and NodeB frame number

(BFN).

4)

The NMPT transmits the clock signals to boards such as HDLP, HULP, HBBI,

and NMON.

5)

The NMPT transmit the clock signals to the MTRU through the HBBI.

Synchronization with Iub clock signals ensures that the NodeB clock precision is

higher than 0.05 ppm. This satisfies the clock precision requirements for long-term

stable operation of the NodeB.

II. Synchronization with GPS Clock Signals

The GPS card is optional unless the NodeB uses a GPS clock as its clock source.

Figure 5.1 shows the synchronization with GPS clock signals.

Huawei Technologies Proprietary

9

RAN Feature Description

Chapter 36 Clock

NMON

HULP

NMPT

F_CLK

GPS antenna

GPS

card

Clock

module

F_CLK BFN

HDLP

CLK-4x

BFN

CLK-4x

F_CLK

HBBI

CLK-4x

MTRU

BFN

Figure 1.1 Synchronization with GPS clock signals

The clock signals are processed and synchronized as follows:

1)

The GSP antenna and feeder system receives GPS signals at 1575.42 MHz, and

then transmits the signals to the GPS card in the NMPT. The system can trace

up to eight (normally three or four) satellites simultaneously.

2)

The GPS card processes the signals and transmits them to the clock module.

3)

Through phase locking and frequency dividing, the clock module converts the

clock signals into various clock signals required by the NodeB, for example,

F_CLK, CLK_4X, and BFN.

4)

The NMPT transmits the clock signals to such boards as HDLP, HULP, HBBI,

and NMON.

5)

The NMPT transmits the clock signals to the MTRU through the HBBI.

With a frequency stability of 0.0001 ppm, the GPS card provides long-term stable

clock signals for the NodeB.

Huawei Technologies Proprietary

10

RAN Feature Description

Chapter 36 Clock

NMON

NMPT

GPS antenna

GPS

card

HULP

F_CLK

F_CLK BFN

HDLP

CLK-4X

Clock

module

BFN

CLK-4X

F_CLK

CLK-4X

NBBI

MTRU

BFN

Figure 5.1 Synchronization with GPS clock signals

III. Synchronization with External Reference Clock Signals

The BTS3812E and BTS3812A can synchronize its clocks with the 2 MHz clock

signals from an external reference clock. The reference clock can be a BITS or a 2

MHz clock from the transmission equipment. The precision of the reference clock

must be better than 0.05 ppm.

Figure 1.1 shows the synchronization with external reference clock signals.

NMON

HULP

NMPT

F_CLK

External reference

clock signals

Clock

module

F_CLK BFN

HDLP

CLK-4x

BFN

CLK-4x

F_CLK

CLK-4x

HBBI

MTRU

BFN

Figure 1.1 Synchronization with external reference clock signals

The clock signals are processed and synchronized as follows:

Huawei Technologies Proprietary

11

RAN Feature Description

Chapter 36 Clock

1)

The NMPT clock module receives external reference clock signals.

2)

Through phase locking and frequency dividing, the clock module converts the

clock signals into various clock signals for the NodeB, for example, F_CLK,

CLK_4X and BFN.

3)

The NMPT transmits the clock signals to such boards as HDLP, HULP, HBBI,

and NMON.

4)

The NMPT transmits the clock signals to the MTRU through the HBBI.

IV. Internal Clock in Free-Run Mode

In addition to the three synchronization modes above, the BTS3812E and BTS3812A

internal clock can work in free-run mode to keep the NodeB running.

The enhanced stratum 3 OCXO with a high precision works as the master clock of the

NodeB. The OCXO can keep the NodeB in normal service for up to 90 days.

36.5.3 RNC Clock System

I. Clock Sources Provided by the RNC

The RNC extracts timing signals from:

GPS

Iu interface

BITS

Table 1.1 describes the clock sources that are described in the MML command ADD

CLKSRC.

Table 1.1 Clock sources

Type

Description

GPS clock (GPS0 and

It provides 1PPS pulse.

GPS1)

Line clock (LINE0,

interface and locked at the WLPU.

LINE1, LINE2, and

LINE3)

It provides timing signals that are extracted from the Iu

During configuration, slot number and port number of

the WLPU must be specified.

The WLPU selects one line clock at a time.

Different clock priorities correspond to different WLPU

slots.

BITS (BITS0)

It provides 2 MHz, 2 Mbit/s, and 8 kHz timing signals.

The anti-interference capability of 2 Mbit/s timing

signal is higher than that of 2 MHz timing signal.

Huawei Technologies Proprietary

12

RAN Feature Description

Chapter 36 Clock

Type

BITS (BITS1)

Description

It provides 2 MHz and 2 Mbit/s timing signals.

The anti-interference capability of 2 Mbit/s timing

signal is higher than that of 2 MHz timing signal.

Note:

The RNC supports active/standby clock sources.

If the active port is configured with a clock source, the board where the standby

port resides cannot be configured with any clock source.

If the active port is not configured with a clock source, the board where the active

port resides must be configured with a clock source.

II. Clock System Structure

Figure 1.1 shows the structure of the RNC clock system.

The clock module of the system is located on the clock sub-board of the

WNET/WNETc. It receives timing signals from:

GPS

Iu interface

BITS

Huawei Technologies Proprietary

13

RAN Feature Description

Chapter 36 Clock

BITS

GPS

CN

WNETc

M

P

Clock mode

8 kHz

WRSS

WRBS

WRBS

W

To NodeB B

E

b

U

b

R

b

X

b

X

b

U

b

R

b

E

b

8 kHz 32 MHz

8 kHz 32 MHz

Figure 1.1 Structure of the RNC clock system

Huawei Technologies Proprietary

14

To NodeB

RAN Feature Description

Chapter 36 Clock

Table 1.1 describes the processing of a system timing signal inside the RNC.

Table 1.1 Processing of a system timing signal inside the RNC

Step

Internal Processing

The clock module receives a timing signal.

After phase locking, the clock module obtains the 8 kHz system timing

signals.

The clock module sends the 8 kHz system timing signals to other boards in

the WRSS through the backplane of the WRSS.

All optical ports on the WLPUs synchronize their line clocks with the timing

signals.

The WMUX/WMUXb in each WRBS extracts the 8 kHz system timing

signals as its clock source.

After phase lock, each WRBS obtains its own timing signals at 8 kHz or 32

MHz.

The WBIE/WBIEb or WOSE/WOSEb/WOSEc extracts the 8 kHz system

timing signals from the backplane of the WRBS and provides them to lowerlevel NodeBs.

Note:

For different interface boards connecting the RNC to the CN, the methods of

extracting timing signal from the Iu interface are different.

If the WLPU serves as the interface board, the timing signals are directly sent to

the clock module of the WNET/WNETc through the backplane, as shown in Figure

1.1.

If another board serves as the interface board, the timing signals are extracted

from the panel of this board and they are then sent to the clock module through

the external clock cable.

For the subsequent processing, refer to Table 1.1.

The WLPU is commonly used. Unless otherwise stated, the following takes the

WLPU as an example.

Huawei Technologies Proprietary

15

RAN Feature Description

Chapter 36 Clock

III. Current Clock Source and Handover Strategy

You can configure multiple clock sources. The system, however, needs only one at a

time. Therefore, you need specify the current clock source and its handover strategy

used when the current clock source fails.

Through SET CLKMODE, you can set the handover strategy to one of the following:

MANUAL

In MANUAL mode, a clock source is specified as the current clock source. The

system cannot use another clock source even when this clock source fails.

AUTO

In AUTO mode, you do not need to specify a clock source as the current clock

source. The system automatically selects a clock source with the highest priority.

If the current clock source with the priority of PRI3 is faulty, the system selects a

clock source with the priority of PRI4. If the faulty clock source recovers, the

system switches the clock source to it.

If all the clock sources are faulty, the system switches to the free-run mode.

When one or more clock sources recover, the system selects a clock source

automatically.

FREE

The FREE mode is the default clock working mode of the system.

You can enable or disable the clock synchronization modes of the RNC by setting the

parameters System Clock Working Mode and CLKSRC. For example, to enable the

synchronization with the Iub clock, set the System Clock Working Mode parameter

to MANUAL, and the Clock Source Type parameter to LINE. To disable the

synchronization with the Iub clock, change the value of the Clock Source Type

parameter to any value except LINE0LINE3.

Huawei Technologies Proprietary

16

RAN Feature Description

Chapter 36 Clock

Parameter Name

Parameter ID

GUI Range

System Clock Working Mode

CLKWMODE

MANUAL, AUTO, FREE

Physical Range & Unit

None

Default Value

None

Optional/Mandatory

MML Command

Mandatory

SET CLKMODE

Description:

The clock sources are classified as current clock source and non-current clock

source. According to a certain handover strategy, the system clock can be fixed to

the current clock source or handed over between the current and the non-current

clock sources.

System clock working mode has three types:

Manual: The user specifies a clock source and inhibits it from automatically be

handed over to other sources.

Auto: The user need not to specify a clock source and the system is able to

select the clock source with the highest priority automatically.

Free: Free can not be the source clock, only a working mode

Parameter Name

Parameter ID

GUI Range

Clock Source Type

SRCT

GPS0, GPS1, BITS0, BITS1, LINE0, LINE1,

LINE2, LINE3

Physical Range & Unit

None

Default Value

None

Optional/Mandatory

MML Command

Mandatory

SET CLKMODE

ADD CLKSRC

RMV CLKSRC

Description:

This parameter defines the type of the reference clock source of the RNC.

Huawei Technologies Proprietary

17

RAN Feature Description

Chapter 36 Clock

Configuration Rule and Restriction:

The parameter Clock Source Type is valid only when the parameter System

Clock Working Mode is set to MANUAL.

IV. Configuration Strategy of Clock Source Priorities

The RNC provides up to four clock source priorities: PRI1PRI4, from the highest to

the lowest.

During clock source configuration, pay attention to the following:

Clock source and clock source priority has a 1-to-1 relationship.

If the timing signals are extracted from a line clock and the WLPU serves as the

interface board, then the port must be the WLPU physical port from which the Iu

interface goes out but not the one connected to the WRBS.

Multiple timing signals can be extracted from the Iu interface. However, one

WLPU can provide only one timing signal. Therefore, different WLPUs must be

used for different priorities of timing signals.

The RNC usually uses line clocks. The system can also use the BITS or GPS clock in

the equipment room if they are available.

Parameter Name

Parameter ID

GUI Range

Clock source priority

SRCPRI

PRI1 (highest priority), PRI2 (higher priority),

PRI3 (lower priority), PRI4 (lowest priority)

Physical Range & Unit

None

Default Value

None

Optional/Mandatory

MML Command

Mandatory

ADD CLKSRC

Description:

A clock source can only correspond to one priority, and a priority can only

correspond to one clock source.

The LINE0 and LINE1 clock source is extracted from the WLPU. Only one clock

input can be selected for one WLPU at a time. Therefore, clock sources at different

stratums can correspond to different WLPUs.

Huawei Technologies Proprietary

18

RAN Feature Description

Chapter 36 Clock

36.6 Capabilities

None.

36.7 Implementation

36.7.1 Enabling the Clock Feature

I. On the NodeB Side

Table 1.1 describes the commands used to enable the feature on the NodeB side.

Table 1.1 Commands to enable the feature on the NodeB side

Function

Clock working mode

Use this command to modify the

and the reference

reference clock source of the NodeB.

clock source

When the NodeB is operational, it is

Command

SET CLKMODE

necessary for it to trace an external

clock to correct its clock frequency.

That clock is referred to as reference

clock source. The reference clock

source can be GPS clock, line clock,

or external clock.

Use this command to set the NodeB

clock working mode as MANUAL or

FREE.

Line clock source

Use this command to set the line

ADD LNKSRC

clock reported by the NDTI, NAOI or

NUTI to the NMPT.

Setting the GPS

Use this command to set the GPS

cable delay

cable delay.

Caution:

To enable the feature, note that:

Huawei Technologies Proprietary

19

SET GPSDELAY

RAN Feature Description

Chapter 36 Clock

If there is a clock source and the clock mode is set to FREE, the clock source is

not useful and the clock is working in the free-run mode.

If the system uses the LINE clock source, the system clock works in the free-run

state when the LINE clock is faulty. After the reference clock source is restored,

NodeB clock will resume tracing it.

Ensure that the clock source is available before executing the command, or else

the execution will fail.

Note:

If the system returns the Clock source is unavailable message after the execution of

the command, do as follows:

For LINE clock, check whether the LINE clock is configured through DSP

LNKSRC. If not, add it through ADD LNKSRC.

For GPS clock, check whether the GPS is configured through DSP GPS. If no

information returned, it indicates the NodeB doesn't support GPS. Or else, there

may be something wrong with GPS. Handle the faults firstly.

For BITS clock, it indicates the clock source is unavailable. Check the clock source

firstly.

II. On the RNC Side

Table 1.1 describes the commands to enable the feature on the RNC side.

Table 1.1 Commands to enable the feature on RNC side

Function

Clock source

Add a system clock source. Clocks in

Command

ADD CLKSRC

the board are selected or traced

according to handover strategy of the

clock source.

Cock working mode

The clock sources are classified as

current clock source and non-current

clock source. According to a certain

handover strategy, the system clock

can be fixed to the current clock source

or handed over between the current

and the non-current clock sources.

Huawei Technologies Proprietary

20

SET CLKMODE

RAN Feature Description

Chapter 36 Clock

Note:

A clock source can only correspond to one priority, and a priority can only

correspond to one clock source.

The LINE0 and LINE1 clock source is extracted from the WLPU. Only one clock

input can be selected for one WLPU every time, and therefore, clock sources of

different stratums can only correspond to different WLPUs.

III. Examples on the NodeB side

Task

Set the line clock reported to the NMPT by No. 0 E1/T1 of the NDTI in slot 12 of

the basic cabinet.

Command:

SET CLKMODE: MODE=MANUAL, CLKSRC=LINE;

ADD LNKSRC: CN=MASTER, SRN=0, SN=12, PT=IUBE1T1, PN=0;

IV. Examples on the RNC side

Task

Add an LINE0 clock source with stratum of 2, which is extracted from port 8 of

the WLPU in slot 5, and set the clock working mode to manual.

Command

ADD CLKSRC: SRCT=LINE0, SRCPRI=PRI2, WLPUSN=5, WLPUPN=8;

SET CLKMODE: CLKWMODE=MANUAL, SRCT=LINE0;

36.7.2 Reconfiguring Clock Parameters

I. Parameter Reconfiguration on the NodeB Side

Table 1.1 describes the commands to reconfigure clock parameters on the NodeB

side.

Huawei Technologies Proprietary

21

RAN Feature Description

Chapter 36 Clock

Table 1.1 Commands to reconfigure clock parameters on the NodeB side

Function

Clock working mode

Use this command to modify the

and the reference

reference clock source of NodeB.

clock source

When NodeB is in normal operation, it

Command

SET CLKMODE

is necessary for it to trace an external

clock to correct the NodeB clock

frequency. That clock is referred to as

reference clock source. The reference

clock source can be GPS clock

source, line clock source, or external

clock source.

Use this command to modify NodeB

clock working mode as MANUAL or

FREE.

Line clock source

Use this command to set the line clock

ADD LNKSRC

reported by the NDTI, NAOI, or NUTI

to the NMPT.

Use this command to remove a line

RMV LNKSRC

clock source reported to the NMPT by

the NDTI, NAOI, or NUTI.

Use this command to display the

DSP LNKSRC

information of the trunk link used to

extract the line clock.

GPS information

Use this command to display the

DSP GPS

information of the GPS.

Use this command to set the GPS

SET GPSDELAY

cable delay.

Use this command to list GPS cable

delay.

Huawei Technologies Proprietary

22

LST GPSDELAY

RAN Feature Description

Chapter 36 Clock

Note:

The MML command ADD LNKSRC or RMV LNKSRC are used as follows:

The corresponding NDTI or NAOI or NUTI must work well.

You can carry out this command RMV LNKSRC only after adding the line clock to

the system.

If the current system uses the line clock source, the system clock works in the

free-run state after the line clock source is deleted from the system. If the system

uses another clock source, deleting the line clock source has no impact on the

system clock.

II. Parameter Reconfiguration on the RNC Side

Table 1.1 describes the commands to reconfigure clock parameters on the RNC side.

Table 1.1 Commands to reconfigure clock parameters on the RNC side

Function

Current working state

Query the current working state of a

Command

DSP CLKSTAT

board clock. For the WRBS, the

working state of the clock of each board

can be queried. For the WRSS, the

information such as the working state of

the clock in the WNET board as well as

current clock source stratum of the

system clock, working mode of the

system clock, working mode of the

WNET board and current state of phase

lock loop can be queried.

System clock source

Add a system clock source. Clocks in

ADD CLKSRC

the board are selected or traced

according to handover strategy of the

clock source.

Remove the clock source of a specified

RMV CLKSRC

type.

List the configuration information of

clock sources.

Huawei Technologies Proprietary

23

LST CLKSRC

RAN Feature Description

Chapter 36 Clock

Function

Clock mode

The clock sources are classified as

Command

SET CLKMODE

current clock source and non-current

clock source. According to a certain

handover strategy, the system clock

can be fixed to the current clock source

or handed over between the current

and the non-current clock sources.

List the configuration information of the

LST CLKMODE

system clock.

Board-level clock

Set the WRBS interface board clock

source

source.

List board clock source configuration.

SET CLK

LST CLK

III. Examples on the NodeB side

1)

Example 1

Task

Reconfigure the line clock reported to the NMPT from E1/T1 No. 0 to No. 1

of the NUTI in slot 12 of the basic cabinet.

Command

RMV LNKSRC: CN=MASTER, SRN=0, SN=12, PT=IUBE1T1;

ADD LNKSRC: CN=MASTER, SRN=0, SN=12, PT=IUBE1T1, PN=1;

2)

Example 2

Task

The existing link clock source is configured to the board in slot 12.

Reconfigure the clock source to GPS and set the line delay of the GPS to

38 ns.

Command

RMV LNKSRC: CN=MASTER, SRN=0, SN=12, PT=IUBE1T1;

SET CLKMODE: MODE=MANUAL, CLKSRC=GPS;

SET GPSDELAY: GPSCD=38;

IV. Examples on the RNC side

1)

Example 1

Task

Huawei Technologies Proprietary

24

RAN Feature Description

Chapter 36 Clock

The existing clock source is configured to LINE0. Reconfigure the clock

source by setting the Clock source priority parameter to PRI3, and the

Clock source type parameter to BITS0 at 2 Mbps.

Command

RMV CLKSRC: SRCT=LINE0;

SET CLKMODE: CLKWMODE=MANUAL, SRCT=BITS0;

ADD CLKSRC: SRCT=BITS0, SRCPRI=PRI3, BITS1TYPE=2Mbps;

36.7.3 Disabling the Clock Feature

The clock feature is a basic one. Therefore, it can only be adjusted instead of being

disabled.

36.8 Maintenance Information

36.8.1 Alarms

I. Alarms on the NodeB Side

Alarm for BTS3812E/BTS3812A

ALM-1008 Board Clock Abnormal

ALM-1020 NodeB Clock Source Abnormal

ALM-1021 GPS Abnormal

ALM-1032 NMPT-to-Board Clock Abnormal

ALM-1036 NMPT 10M Clock Abnormal

ALM-1037 NMPT 4x Clock Abnormal

ALM-1038 NMPT Secondary PLL Out of Lock

ALM-1106 MTRU Clock Abnormal

ALM-1400 GPS Receiver Hardware Error

ALM-1401 GPS Receiver Antenna Not Powered

ALM-1402 GPS Receiver LNA Abnormal

ALM-1403 GPS Receiver Antenna Open

ALM-1404 GPS Receiver Antenna Shorted

ALM-1405 GPS Receiver Almanac Invalid

ALM-1406 GPS Receiver Position Solution Invalid

ALM-1407 GPS Receiver Position Not Locked

ALM-1408 GPS Receiver Clock Steering Disabled

ALM-1409 GPS Receiver Clock Model Invalid

ALM-1410 GPS Receiver Communication Abnormal

ALM-1411 GPS Receiver Initialization Configuration Failure

Alarm for DBS3800

ALM-1007 BBU Clock Abnormal

ALM-1008 NodeB Clock Source Abnormal

Huawei Technologies Proprietary

25

RAN Feature Description

Chapter 36 Clock

ALM-1021 GPS Abnormal

ALM-1312 RRU Clock Abnormal

II. Alarms on the RNC Side

ALM-202 Backplane 8K Synchronization Signal Abnormity

ALM-203 Backplane 32M Clock Abnormity

ALM-205 WMUX/WMUXb Clock Phase-locked Loop Failure

ALM-553 GPS Card Antenna not powered

ALM-554 LNA of GPS Card abnormal

ALM-562 Clock model invalid

ALM-561 Clock steering disabled

ALM-2402 Locked Satellite Number Abnormality

ALM-9030 Clock Source Unavailable

ALM-9032 Clock Source Handover

ALM-9033 Clock State Change

ALM-9035 Loss of GPS Signal

ALM-9037 Crystal Oscillator Faulty

ALM-9187 GPS Card Faulty

ALM-9188 Loss of Satellite

ALM-9189 Unavailable Communication Port on GPS Card

36.8.2 Counters

None.

36.9 References

3GPP TS 25.402 Synchronization in UTRAN Stage 2

3GPP TS 25.104 "UTRA (BS) FDD; Radio transmission and Reception".

3GPP TS 25.105 "UTRA (BS) TDD, Radio transmission and Reception".

Huawei Technologies Proprietary

26

Anda mungkin juga menyukai

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Dari EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Belum ada peringkat

- Ef4202 7Dokumen1 halamanEf4202 7SON100% (2)

- ABB HighPowerSemiconductorsProductCatalogue2013 PDFDokumen36 halamanABB HighPowerSemiconductorsProductCatalogue2013 PDFPopovici Paul100% (1)

- Introduction to 6800/6802 Microprocessor Systems: Hardware, Software and ExperimentationDari EverandIntroduction to 6800/6802 Microprocessor Systems: Hardware, Software and ExperimentationBelum ada peringkat

- Synchronization in UTRANDokumen36 halamanSynchronization in UTRANMarjoryWangareWanjohi100% (1)

- Vacon NXP Lift APFIFF33 Application Manual UD01041Dokumen76 halamanVacon NXP Lift APFIFF33 Application Manual UD01041TanuTiganuBelum ada peringkat

- Practical Machinery Vibration Analysis and Predictive MaintenanceDari EverandPractical Machinery Vibration Analysis and Predictive MaintenancePenilaian: 4.5 dari 5 bintang4.5/5 (10)

- RPM IndicatorDokumen39 halamanRPM IndicatorAnkur PatelBelum ada peringkat

- 11 November 1998Dokumen108 halaman11 November 1998Monitoring Times100% (1)

- CTS SignoffsemiconductorsDokumen7 halamanCTS SignoffsemiconductorsAgnathavasiBelum ada peringkat

- Preliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960Dari EverandPreliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960Belum ada peringkat

- Ericsson RBS 6000 Sync AlarmDokumen4 halamanEricsson RBS 6000 Sync AlarmMinto Issac100% (1)

- NOJA-5002-08 OSM15 310, OSM27 310, OSM38 300 and RC10 Controller User Manual - Print (Adobe) PDFDokumen208 halamanNOJA-5002-08 OSM15 310, OSM27 310, OSM38 300 and RC10 Controller User Manual - Print (Adobe) PDFNhat Nguyen Van100% (1)

- Draft Format - Method Statement of Commissioning NURSE CALLDokumen12 halamanDraft Format - Method Statement of Commissioning NURSE CALLmohammed naseer uddinBelum ada peringkat

- PMI Online Setup and CommisioningDokumen25 halamanPMI Online Setup and Commisioning_commandos_Belum ada peringkat

- 35 TX RX DiversityDokumen36 halaman35 TX RX DiversitylizhaohuiBelum ada peringkat

- Fast Radio Bearer SetupDokumen5 halamanFast Radio Bearer SetupVictor Perez JimenezBelum ada peringkat

- Local Cell RadiusDokumen1 halamanLocal Cell RadiuslizhaohuiBelum ada peringkat

- Local Cell RadiusDokumen1 halamanLocal Cell RadiuslizhaohuiBelum ada peringkat

- 25-Ip RanDokumen65 halaman25-Ip RanlizhaohuiBelum ada peringkat

- WCDMA Synchronization SimplifiedDokumen18 halamanWCDMA Synchronization Simplifiedmola argawBelum ada peringkat

- BSC/RNC Clock Feature Parameter DescriptionDokumen21 halamanBSC/RNC Clock Feature Parameter DescriptionSam FicherBelum ada peringkat

- AN5300 - Using and Synchronizing The KEA's Internal Clock For LIN Follower Implementations - Application NoteDokumen13 halamanAN5300 - Using and Synchronizing The KEA's Internal Clock For LIN Follower Implementations - Application NoteArun KumarBelum ada peringkat

- 8.chapter-2 Literature SurveyDokumen3 halaman8.chapter-2 Literature Surveycr9_sriniBelum ada peringkat

- En - stm32l4 WDG Timers RTCDokumen22 halamanEn - stm32l4 WDG Timers RTCThế PhươngBelum ada peringkat

- Syn470R Datasheet: (300-450Mhz Ask Receiver)Dokumen21 halamanSyn470R Datasheet: (300-450Mhz Ask Receiver)mariachi1980Belum ada peringkat

- 04 Delays, Counters, and TimersDokumen47 halaman04 Delays, Counters, and TimersFatimaAlarconBlancoBelum ada peringkat

- CDMA Performance Parameters (1x) V3.0 PDFDokumen326 halamanCDMA Performance Parameters (1x) V3.0 PDFابراهيم معوضةBelum ada peringkat

- CDMA Performance Parameters (1x) V3.0Dokumen326 halamanCDMA Performance Parameters (1x) V3.0ابراهيم معوضةBelum ada peringkat

- Document Version: 1.0 Image Version: V1.3: Lgt-92 Lorawan Gps Tracker User ManualDokumen32 halamanDocument Version: 1.0 Image Version: V1.3: Lgt-92 Lorawan Gps Tracker User ManualSilver ProBelum ada peringkat

- C Homework #11Dokumen3 halamanC Homework #11Saurabh GuptaBelum ada peringkat

- Ohmega 311Dokumen3 halamanOhmega 311tonytomsonBelum ada peringkat

- AD9548 GPS Disciplined Stratum 2 ClockDokumen16 halamanAD9548 GPS Disciplined Stratum 2 Clockmarktheman4uBelum ada peringkat

- Unit 3 McuDokumen23 halamanUnit 3 McuatulBelum ada peringkat

- Revision RCC Reset Clock Control 06 - 2022 - FinalDokumen16 halamanRevision RCC Reset Clock Control 06 - 2022 - Finalservice informatiqueBelum ada peringkat

- 5-En - stm32l4 System RCCDokumen25 halaman5-En - stm32l4 System RCCYohanes ErwinBelum ada peringkat

- Inrush3 Three-Phase Transformer Inrush and Motor Start-Up Current DetectorDokumen15 halamanInrush3 Three-Phase Transformer Inrush and Motor Start-Up Current DetectorrajeshBelum ada peringkat

- Sine Wave GeneratorDokumen12 halamanSine Wave GeneratortranvandoanhBelum ada peringkat

- Clocks and Timers-Sources & Controls-IDokumen10 halamanClocks and Timers-Sources & Controls-ISUNOJ RAICARBelum ada peringkat

- Microcontrollers ApNote AP163703Dokumen24 halamanMicrocontrollers ApNote AP163703djkruggerBelum ada peringkat

- DOC6 - Three-Phase Directional Overcurrent Protection Low-Set Stage (DOC6Low) High-Set Stage (DOC6High) Instantaneous Stage (DOC6Inst)Dokumen35 halamanDOC6 - Three-Phase Directional Overcurrent Protection Low-Set Stage (DOC6Low) High-Set Stage (DOC6High) Instantaneous Stage (DOC6Inst)rajeshBelum ada peringkat

- JHBLH Ko: Where We Can Attaach Our Crystal Oscillator ThereDokumen3 halamanJHBLH Ko: Where We Can Attaach Our Crystal Oscillator ThereNelson Javines QuiritBelum ada peringkat

- Atmega328Pb DatasheetDokumen406 halamanAtmega328Pb DatasheetNenad PetrovicBelum ada peringkat

- Application Note 504: Design Considerations For Dallas Real-Time ClocksDokumen8 halamanApplication Note 504: Design Considerations For Dallas Real-Time ClocksAyadBelum ada peringkat

- Microcontroller Based Radar SystemDokumen19 halamanMicrocontroller Based Radar SystemMeet MakwanaBelum ada peringkat

- KFlopManual PDFDokumen306 halamanKFlopManual PDFandrea772Belum ada peringkat

- LTE RRC Succ Rate OptimizationDokumen4 halamanLTE RRC Succ Rate OptimizationApollo Spaceship11Belum ada peringkat

- Mg86fel508 Datasheet A1-2Dokumen202 halamanMg86fel508 Datasheet A1-2ravikant.shreeji20068681Belum ada peringkat

- 1C108 0e Bluetooth BR EDR AFHDokumen19 halaman1C108 0e Bluetooth BR EDR AFHAA ccBelum ada peringkat

- Real-Time-Clock Selection and Optimization: System ConsiderationsDokumen7 halamanReal-Time-Clock Selection and Optimization: System ConsiderationsmadhuvariarBelum ada peringkat

- AN2669 Application Note: How To Configure The STM8A Microcontroller ClocksDokumen8 halamanAN2669 Application Note: How To Configure The STM8A Microcontroller ClocksVladBelum ada peringkat

- Transmission SynchDokumen47 halamanTransmission SynchMakarand DereBelum ada peringkat

- Implementing A Real-Time Clock On The MSP430: Mike Mitchell Mixed Signal ProductsDokumen12 halamanImplementing A Real-Time Clock On The MSP430: Mike Mitchell Mixed Signal ProductssadeqBelum ada peringkat

- Project Report KanojDokumen17 halamanProject Report KanojKanoj Bsn100% (3)

- Chuan Kangliang2008Dokumen9 halamanChuan Kangliang2008Huy VươngBelum ada peringkat

- Y25-029-0 Training For O&M Manual For Excitaion SystemDokumen32 halamanY25-029-0 Training For O&M Manual For Excitaion SystemLiixoo Rojas100% (1)

- 3-Phase Switched Reluctance Motor Control With Encoder Using DSP56F80xDokumen56 halaman3-Phase Switched Reluctance Motor Control With Encoder Using DSP56F80xYusuf Ilker öztürkBelum ada peringkat

- Serial UART Communication Using MicrocontrollerDokumen12 halamanSerial UART Communication Using MicrocontrollerGaurav Gupta100% (1)

- RE - 5 - Three-Phase Directional Overcurrent Protection Low-Set Stage (DOC6Low) High-Set Stage (DOC6High) Instantaneous Stage (DOC6Inst)Dokumen34 halamanRE - 5 - Three-Phase Directional Overcurrent Protection Low-Set Stage (DOC6Low) High-Set Stage (DOC6High) Instantaneous Stage (DOC6Inst)rajeshBelum ada peringkat

- Microchip Technology Inc.: Digital Signal ControllerDokumen17 halamanMicrochip Technology Inc.: Digital Signal Controllerjnax101Belum ada peringkat

- 06 Tr3272eu00tr 0501 SynchronizationDokumen44 halaman06 Tr3272eu00tr 0501 SynchronizationwahbaabassBelum ada peringkat

- Configuring The FlexTimer For Position and Speed Measurement With An EncoderDokumen10 halamanConfiguring The FlexTimer For Position and Speed Measurement With An EncoderSumeet TrivediBelum ada peringkat

- Clock Tree Design ConsiderationsDokumen4 halamanClock Tree Design Considerationscontscribd11Belum ada peringkat

- Sine Wave GenerationDokumen18 halamanSine Wave GenerationIfedayo OladapoBelum ada peringkat

- Chapter Error: Reference Source Not FoundDokumen3 halamanChapter Error: Reference Source Not FoundKàrthîkéyàn PérîyàsàmyBelum ada peringkat

- TRACT System CalibrationDokumen38 halamanTRACT System Calibrationneseg61034Belum ada peringkat

- LSN50v2 S31 LoRaWAN Temperature Manual v1.2Dokumen22 halamanLSN50v2 S31 LoRaWAN Temperature Manual v1.2Andrés Felipe Matamala QuezadaBelum ada peringkat

- Transistor Electronics: Use of Semiconductor Components in Switching OperationsDari EverandTransistor Electronics: Use of Semiconductor Components in Switching OperationsPenilaian: 1 dari 5 bintang1/5 (1)

- Optimizer-refarming-training-Day4 12Dokumen1 halamanOptimizer-refarming-training-Day4 12lizhaohuiBelum ada peringkat

- Optimizer-refarming-training-Day4 4Dokumen1 halamanOptimizer-refarming-training-Day4 4lizhaohuiBelum ada peringkat

- Plan Provisioning: 10 © Nokia Solutions and Networks 2014Dokumen1 halamanPlan Provisioning: 10 © Nokia Solutions and Networks 2014lizhaohuiBelum ada peringkat

- Plan Transfer From Optimizer: 8 © Nokia Solutions and Networks 2014Dokumen1 halamanPlan Transfer From Optimizer: 8 © Nokia Solutions and Networks 2014lizhaohuiBelum ada peringkat

- Optimizer-refarming-training-Day4 6Dokumen1 halamanOptimizer-refarming-training-Day4 6lizhaohuiBelum ada peringkat

- Plan in CM Operations Manager: 9 © Nokia Solutions and Networks 2014Dokumen1 halamanPlan in CM Operations Manager: 9 © Nokia Solutions and Networks 2014lizhaohuiBelum ada peringkat

- Optimizer-refarming-training-Day4 11Dokumen1 halamanOptimizer-refarming-training-Day4 11lizhaohuiBelum ada peringkat

- Optimizer-refarming-training-Day4 5Dokumen1 halamanOptimizer-refarming-training-Day4 5lizhaohuiBelum ada peringkat

- RRM FunctionsDokumen38 halamanRRM FunctionsSahil KalaBelum ada peringkat

- 3511 - HSUPAOverview Dec14 07Dokumen52 halaman3511 - HSUPAOverview Dec14 07Ashok Kumar S CBelum ada peringkat

- 2G CSV Format - ModifiedDokumen86 halaman2G CSV Format - ModifiedlizhaohuiBelum ada peringkat

- Optimizer-refarming-training-Day4 3Dokumen1 halamanOptimizer-refarming-training-Day4 3lizhaohuiBelum ada peringkat

- LDM & CacDokumen1 halamanLDM & CaclizhaohuiBelum ada peringkat

- LDM & CacDokumen10 halamanLDM & CaclizhaohuiBelum ada peringkat

- Levenshtein PLDokumen1 halamanLevenshtein PLlizhaohuiBelum ada peringkat

- Query 1Dokumen43 halamanQuery 1lizhaohuiBelum ada peringkat

- Nemo QueriesDokumen6 halamanNemo QuerieslizhaohuiBelum ada peringkat

- Script BCC NCC TRX MalDokumen1 halamanScript BCC NCC TRX MallizhaohuiBelum ada peringkat

- Impact of Sib Scheduling On The Standby Battery Life of Mobile Devices in UmtsDokumen5 halamanImpact of Sib Scheduling On The Standby Battery Life of Mobile Devices in UmtsavonsusBelum ada peringkat

- Excel ShortcutsDokumen3 halamanExcel ShortcutslizhaohuiBelum ada peringkat

- ISHO Competitor CapabilitiesDokumen2 halamanISHO Competitor CapabilitieslizhaohuiBelum ada peringkat

- 24-NodeB Reparent ToolDokumen24 halaman24-NodeB Reparent ToollizhaohuiBelum ada peringkat

- 30 IMSI Based HandoverDokumen16 halaman30 IMSI Based HandoverlizhaohuiBelum ada peringkat

- 28 Tracing FunctionDokumen29 halaman28 Tracing FunctionWalid BensaidBelum ada peringkat

- JQuery CheatSheetDokumen1 halamanJQuery CheatSheetlizhaohuiBelum ada peringkat

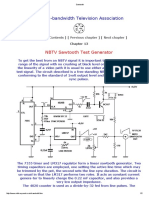

- Narrow Bandwidth Television Association: NBTV Sawtooth Test GeneratorDokumen2 halamanNarrow Bandwidth Television Association: NBTV Sawtooth Test GeneratorSebastian CostaBelum ada peringkat

- Ec1008 QBDokumen3 halamanEc1008 QBSomasundaram RamuBelum ada peringkat

- 3HEA802920-001 - Programing Fronius PS - RW5Dokumen48 halaman3HEA802920-001 - Programing Fronius PS - RW5samac1411Belum ada peringkat

- Lession-35 - 3-Phase Voltage Source Inverter With Square Wave OutputDokumen11 halamanLession-35 - 3-Phase Voltage Source Inverter With Square Wave OutputSangeetha DurairajuBelum ada peringkat

- FLIR T640 IR CameraDokumen5 halamanFLIR T640 IR CameraaspenspencerwrmBelum ada peringkat

- A - Introduction B - Organisation C - Championships Program D - Technical E - Awards F - Matters Not Covered by These Rules AppendixDokumen12 halamanA - Introduction B - Organisation C - Championships Program D - Technical E - Awards F - Matters Not Covered by These Rules AppendixAlex BerezinBelum ada peringkat

- EziweighDokumen4 halamanEziweighBerney RyxlerBelum ada peringkat

- Microwave Engineering - Cavity Klystron PDFDokumen6 halamanMicrowave Engineering - Cavity Klystron PDFHero RameshBelum ada peringkat

- Accessory Cable GuideDokumen9 halamanAccessory Cable GuideCarmelo BayonBelum ada peringkat

- DIP New Guidelines 4th EditionDokumen3 halamanDIP New Guidelines 4th EditionSHOBHIT KUMAR SONI cs200% (1)

- 4128Dokumen6 halaman4128L BBelum ada peringkat

- Jimma ThesisDokumen65 halamanJimma ThesisMintesnot AlemuBelum ada peringkat

- Rn5Rf Series: OutlineDokumen14 halamanRn5Rf Series: OutlineVlady Lopez CastroBelum ada peringkat

- Furman AR1215 Power Conditioning (120vac)Dokumen18 halamanFurman AR1215 Power Conditioning (120vac)Bob FarlowBelum ada peringkat

- A G.709 Optical Transport Network Tutorial: White PaperDokumen12 halamanA G.709 Optical Transport Network Tutorial: White PapersumitBelum ada peringkat

- Construction and Woking of BJTDokumen3 halamanConstruction and Woking of BJTGowtham100% (1)

- 6es7153 2ba02 0XB0Dokumen3 halaman6es7153 2ba02 0XB0HarunBelum ada peringkat

- Simulation of Negotiation-Based Data Dissemination Protocol in Wireless Sensor Networks With Omnet++Dokumen13 halamanSimulation of Negotiation-Based Data Dissemination Protocol in Wireless Sensor Networks With Omnet++pigeonrainBelum ada peringkat

- 8-Port Gpon Olt: Compact High Performance GPON OLT For Medium and Small OperatorDokumen5 halaman8-Port Gpon Olt: Compact High Performance GPON OLT For Medium and Small Operatordevsa ityBelum ada peringkat

- Te 18Dokumen75 halamanTe 18Ritika BakshiBelum ada peringkat

- RLFDokumen5 halamanRLFPritam ModakBelum ada peringkat

- SCS SpecsDokumen92 halamanSCS Specstamheed4uBelum ada peringkat

- XR2000 IP-PBX Data Sheet: FeaturesDokumen3 halamanXR2000 IP-PBX Data Sheet: FeaturesC3RE4LBelum ada peringkat

- Gigabyte GA-890FXA-UD7 Motherboard Product GuideDokumen51 halamanGigabyte GA-890FXA-UD7 Motherboard Product GuideGIGABYTE UKBelum ada peringkat

- JBL Quantum Duo QSG MultilingualDokumen20 halamanJBL Quantum Duo QSG MultilingualzooooooreBelum ada peringkat

- Arduino Irf520 Mosfet Driver ModuleDokumen11 halamanArduino Irf520 Mosfet Driver ModuleSisil BandaraBelum ada peringkat