DLD Lab Manual 2014 - Latest

Diunggah oleh

Nabeel ZahurJudul Asli

Hak Cipta

Format Tersedia

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniHak Cipta:

Format Tersedia

DLD Lab Manual 2014 - Latest

Diunggah oleh

Nabeel ZahurHak Cipta:

Format Tersedia

University of Sharjah

Computer Engineering

Digital Logic Design Laboratory Manual

0403202

Spring 2013-2014

University of Sharjah

Computer Engineering

Experiment No. 1

Introduction to Hardware Description Language and

Synthesis

Objectives

Implementation of Simple Digital Gates with Verilog using Altera DE2 board and

Quartus II 6.1 Software

Introduction

The aim of this experiment is to implement simple digital gates (INV, BUFFER, AND,

OR, NAND, NOR, XOR, and XNOR) on Altera's DE2 board using Verilog description

languages and Quartus II 6.1

Content

Verilog Structural Models

QuartusII 6.1

Compilation

Simulation

Programming

1. Quartus II Project Setup

Create a new project called Basic_Gates using the following steps:

1. Create a directory called "DLD_Basics" in your Desktop.

2. Start Quartus II 6.1. The main Quartus II display is shown in Figure 1.

Figure 1. The main Quartus display

Spring 2013-2014

University of Sharjah

Computer Engineering

3. Go to "File" a pop-up window will appear as shown in Figure 2. "Select New

Project Wizard"

4. Hit Next on the first pop-up window shown in Figure 3.

Figure 2. An example of File menu

Figure 3. New Project Wizard Introduction

Spring 2013-2014

University of Sharjah

Computer Engineering

5. A pop-up window will appear as shown in Figure 4. Select a folder for the

project, "DLD_BASICS".

Figure 4. Name of project

6. Type Basic_Gates in the name of the project field and hit Next.

7. A pop-up window shown in Figure 5.

8. Hit Next on the Add Files popup window.

Figure 5. Add files to a project if any.

Spring 2013-2014

University of Sharjah

Computer Engineering

Figure 6. Select family and device package

9. The next popup window will be Family & Device Settings window shown in

Figure 6. Choose the following

a. For the family select Cyclone II

b. For the Package select FBGA

c. For the Pin count select 672

d. For the Speed Grade select 6

e. For the Target Device select Specify Devices Selected in Available

Device List

f. In the Available Devices Select EP2C35F672C6

g. Hit Next to continue.

h. Check the setting and hit Finish

10. Hit "Next" on the pop-up window shown in Figure 7.

11. Hit "Finish" on Figure 8.

Spring 2013-2014

University of Sharjah

Computer Engineering

Figure 7. Additional EDA tools

Figure

8.

Final

Project

Summary

Spring 2013-2014

showing

Device

selection

University of Sharjah

Computer Engineering

2. Design basic gates

In this section, we will design the basic digital gates given in Chapter 2 of your Text

Book. The gates are INV, BUF, AND, NAND, OR, NOR, XOR, and XNOR as show in

Figure 9. Table 1 describes the output signal.

A

B

AB_AND

AB_OR

AB_NAND

AB_NOR

AB_XOR

AB_XNOR

A_INV

B_BUF

Figure 9. Top-level entity

TABLE 1: Verilog module signal description of Basic_Gates

Signal Name

Type

Description

A

Input

One bit

B

Input

One bit

AB_AND

Output

A and B

AB_OR

Output

A or B

AB_NAND

Output

A nand B

AB_NOR

Output

A nor B

AB_XOR

Output

A xor B

AB_XNOR

Output

A xnor B

A_INV

Output

A'

B_BUFF

Output

B

Spring 2013-2014

University of Sharjah

Computer Engineering

1. Go to File New and choose Verilog on the Device Design Type as shown in

Figure 10.

Figure 10. Choosing Verilog HDL File.

2. Type in the Verilog module shown in Figure 11. Note that the name of the

module must be the Project Name.

3. Note that you can replace the XOR function by the module given in Figure 12.

4. To insert a gate from a template. Go to Edit Insert Template

5. Save the file as shown in Figure 13. Note that the file name needs to be the same

as the Project Name.

Spring 2013-2014

University of Sharjah

Computer Engineering

module Basic_Gates (

A,

B,

AB_AND,

AB_OR,

AB_NAND,

AB_NOR,

AB_XOR,

AB_XNOR,

A_INV,

B_BUFF

);

// List all the inputs

input A;

input B;

// List all outputs

output AB_AND;

output AB_OR;

output AB_NAND;

output AB_NOR;

output AB_XOR;

output AB_XNOR;

output A_INV;

output B_BUFF;

// Structural Module

and (AB_AND, A, B);

or (AB_OR, A, B);

nand (AB_NAND, A, B);

nor (AB_NOR, A, B);

xor (AB_XOR, A, B);

xnor (AB_XNOR, A, B);

not (A_INV, A);

buf (B_BUFF, B);

endmodule

Figure 11. Verilog module of Basics Gates

Spring 2013-2014

10

University of Sharjah

Computer Engineering

wire w0, w1;

wire A_, B_;

not (A_, A);

not (B_, B);

and (w0, A_, B);

and (w1, A, B_);

or (AB_XOR, w0, w1);

Figure 12. Another alternative for XOR

Figure 13. Save your file.

3. Compiling the design

1. Go to Processing Start Compilation

2. The compilation should be successful with three warnings only as shown in

Figure 14. Ignore these warnings and go to the next step.

Spring 2013-2014

11

University of Sharjah

Computer Engineering

Figure 14. Compilation Report

4. Simulating the design

1. Go to File New

2. Select "Other Files" and select "Vector Waveform File" as shown in Figure 15.

3. A new waveform file will be opened as show in Figure 16.

Figure 15. Choosing Vector Waveform File

Spring 2013-2014

12

University of Sharjah

Computer Engineering

Figure 16. Waveform File.

4. Right Click on Name bar and select Insert Insert Node or Bus as shown in

Figure 17.

5. In the Insert Node or Bus popup window choose Node Finder as shown in

Figure 18.

Figure 17. Selecting Nodes

Spring 2013-2014

13

University of Sharjah

Computer Engineering

Figure 18. Insert Node or Bus

6. Select List on the right hand side. All the Inputs/Outputs will appear on the left

hand side of the pop-up window. Select all signals (ONE-BY-ONE) and transfer

them to the right hand side of the pop-up screen using the right arrow in the

middle. As shown in Figure 19. Hit "OK" and go to next step.

Figure 19. List of all inputs and outputs

Spring 2013-2014

14

University of Sharjah

Computer Engineering

Figure 20. Waveform file

7. Hit Ctrl+W to see the whole file as shown in Figure 20.

8. With the mouse button highlight a section of the signal and double click on it as

shown in Figure 21.

Figure 21: assigning values to a signal

9. Assign all four different combinations to signal A and B, and save the file as

"Basic_Gates.wvf".

Spring 2013-2014

15

University of Sharjah

Computer Engineering

10. Go to Processing Start Simulation

11. Simulation should be successful with no warnings. The waveform file should be

similar to Figure 22.

12. Look into the file to verify the outputs. Fill in the table the values of the

following outputs.

TABLE 2: Simulation Results

A B AB_ AB_ AB_N

AB_

AND OR

AND

NOR

0 0

0 1

1 0

1 1

AB_

XOR

AB_X

NOR

A_I

NV

B_B

UFF

Figure 22. Simulation waveform of Basic_Gates

Spring 2013-2014

16

University of Sharjah

Computer Engineering

5. Pin Assignments

In this section we will use only the switches and the Red Light Emitting Diodes (LEDs)

to assign the inputs and outputs of the function.

1. Go to Assignment Assignment Editor as shown in Figure 23.

Figure 23. Pin Assignment

2. In the "Category:" option select "Pin"

3. Double click with your mouse button on line#1, and select pin "A" as shown in

Figure 24.

Figure 24. Choosing pins

4. In the location space type "PIN_N25" this is SW[0] in the DE2 Board.

5. Fill the assignments according to Table 3. For more information, look in the

Appendix (or Altera DE2 Manual) for a complete list of Switches, LEDs, and

Pushbuttons assignment.

Spring 2013-2014

17

University of Sharjah

Computer Engineering

6. Save your design and recompile it. You should get 2 warnings only. Ignore these

warnings and go to next step.

Table 3: Pin Assignments

A

PIN_N25

B

PIN_N26

AB_AND

PIN_AE23

AB_OR

PIN_AF23

AB_NAND

PIN_AB21

AB_NOR

PIN_AC22

AB_XOR

PIN_AD22

AB_XNOR

PIN_AD23

A_INV

PIN_AD21

B_BUFF

PIN_AC21

6. Programming to Traffic_Sys Design

In this section you will program the DE2 FPGA CycloneII and test your design.

1. Connect the USB-Blaster cable to your computer and turn on the board by

pushing the red button on the board. Make sure that the board is in RUN

mode not programmer mode (This is a switch on the left hand side of the

board). For more details, please refer to the Altera DE2 manual.

2. Go to Tools Programmer or push the programmer button located in the

top right corner.

3. Select Basic_Gates.sof as shown in Figure 24.

Figure 24. Basic_Gates Programming Tools

4.

5.

6.

7.

Select Program/Configure

Make sure the Hardware Setup USB-Blaster[USB0] is selected.

Push the Start Button to start programming the board.

The lights on the board will indicate the chip is configured. Test the chip

with the same test as the input.

Spring 2013-2014

18

University of Sharjah

Computer Engineering

8. Fill in Table 3 and make sure it matches your simulation in Table 2.

TABLE 3: DE2 Board Test

A B AB_ AB_ AB_N

AND OR

AND

0 0

0 1

1 0

1 1

AB_

NOR

AB_

XOR

AB_X

NOR

A_I

NV

B_B

UFF

9. Go to File Close Project and exit Quartus II.

Assignment: Write a Verilog program to implement a Full adder.

Sum = A xor B xor Cin

Cout = A B + A Cin + B Cin

A

0

0

0

0

1

1

1

1

B

0

0

1

1

0

0

1

1

Cin

0

1

0

1

0

1

0

1

Sum

0

1

1

0

1

0

0

1

Cout

0

0

0

1

0

1

1

1

Cin

Full Adder

Cout

Sum

Spring 2013-2014

19

University of Sharjah

Computer Engineering

Appendix

Spring 2013-2014

20

University of Sharjah

Computer Engineering

Spring 2013-2014

21

University of Sharjah

Computer Engineering

Experiment No. 2

Implementation in Verilog (Part I)

Objectives

In this lab, you have to solve the following problems during lab time as a group work and

submit your solution at the end of the lab session. For each problem, you have to write

the verilog code using Quartus software and show your output on waveforms and altera

boards.

Problems:

Problem 1: Design a 4-bit comparator ( X>Y, X=Y, X<Y)

The comparator should have two 4-bt inputs for x and y, and three outputs E, G and L.

When X= Y, E=1

When X>Y, G=1

When X< Y, L=1

Display the output of your program on:

a) Waveform

b) Digital LEDs

Problem 2: Design a 2*1 multiplexer

Hint: The input (x and y) are 4-bit width.

When selector = 0 , the output F= X

When selector = 1, F= Y

X

Y

Selector

Spring 2013-2014

22

University of Sharjah

Computer Engineering

Problem 3: The following code represent a 4-bit binary counter. Simulate the below

code using Quartus Software. Download the program on the Altera board and show

the output on:

a) Waveform

b) Digital LEDs

module problem3 (count, clock);

input clock;

output reg [3:0] count;

count=0;

always@(posedge clock(

begin

count=count+1;

end

endmodule

Problem 4: You need now to display the output of the above counter on a 7-segment

display, using the following code:

module problem4 (count,hex0,clock);

input clock;

output reg [3:0] count;

output reg [6:0] hex0;

count=0;

always@(posedge clock(

begin

count=count+1;

case(count(

4'b0000:hex0=7'b1000000;

4'b0001:hex0=7'b1111001;

4'b0010:hex0=7'b0100100;

4'b0011:hex0=7'b0110000;

4'b0100:hex0=7'b0011001;

4'b0101:hex0=7'b0010010;

4'b0110:hex0=7'b0000010;

4'b0111:hex0=7'b1111000;

4'b1000:hex0=7'b0000000;

4'b1001:hex0=7'b0011000;

default: hex0=7'b1000000;

endcase

end

endmodule

Spring 2013-2014

23

University of Sharjah

Computer Engineering

Assignment 1: Design an even counter that counts from 0, 2, 4, 6, 8 and then back to

0. Display your output on 7-Segment display

Assignment 2: Design an 2-bit up/down counter.

Hint: You have one input (1 bit) x, and (2-bits) for output y.

When x = 1, it performs an up counter and counts {0, 1 , 2,3}

When x =0, it backwards one step and counts down {3, 2 ,1,0}

Your initial start should be 00.

a. Draw the state diagram of your design.

b. Writing your Verilog code.

c. Show your output on waveform and altera board.

Spring 2013-2014

24

University of Sharjah

Computer Engineering

Experiment No. 3

Basic Gates Implementation in Verilog and

Configuration

Objectives:

Implementation of Simple FSM with Verilog using Altera DE2 board and Quartus II 6.1

Software

Introduction

The aim of this lab is to implement simple FSM (sequential circuit) on Altera's DE2

board using Verilog description languages and Quartus II 6.1

Content

Verilog Behavioral Models

QuartusII 6.1

Compilation

Simulation

Programming

1. Quartus II Project Setup

Create a new project called Simple_FSM using the following steps:

1. Create a directory called "Simple_FSM" in your Desktop.

2. Start Quartus II 6.1.

3. Go to FileSelect New Project Wizard.

4. Hit Next on the "New Project Wizard: Introduction" window.

5. In the "New Project Wizard: Directory, Name, Top Level-Entity" window. Select a

folder for the project, "Simple_FSM".

6. Type Count_Four in What is the name of the project? field and hit Next.

7. Hit Next on the Add Files popup window.

8. The next popup window will be Family & Device Settings window shown in

Figure 1. Choose the following

a. For the Family select Cyclone II

b. For the Package select FBGA

c. For the Pin count select 672

d. For the Speed Grade select 6

e. For the Target Device select Specify Devices Selected in Available Device List

f. In the Available Devices Select EP2C35F672C6

Spring 2013-2014

25

University of Sharjah

Computer Engineering

g. Hit Next to continue.

h. Check the setting and hit Finish

9. Hit "Next" on the next

10. Hit "Finish" and go to next step.

Figure 1. Select family and device package

2. Simple FSM design

Design a sequential machine that detects four consecutive ones on input "x" anytime it

occurs and produce and output F. For example, if the input is 0101010101111111 the

output would be 0000000000001111

x

Reset

CLK

F

Counter Four

FSM

Figure 2. Top-level entity

Signal Name

x

F

Type

Input

Output

Description

One bit

One Bit

TABLE 1: Signal Description

Spring 2013-2014

26

University of Sharjah

Computer Engineering

Figure 3. State Diagram of FSM

Go to File New and choose Verilog on the Device Design Type.

1. Type in the Verilog module shown in Figure 4. Note that the name of the

module must be the Project Name.

2. To insert a gate from a template. Go to Edit Insert Template.

3. Save the file. Note that the file name needs to be the same as the Project

Name.

Spring 2013-2014

27

University of Sharjah

Computer Engineering

module Count_Four (CLOCK, RST, x, F);

// Input and Output declaration

input x;

input RST;

input CLOCK;

output F;

reg [2:0] State;

always@(posedge CLOCK)

begin

if

(RST == 1'b1)

State = 3'b000;

// Reset state

else

begin

case (State)

3'b000:begin

if (x == 1'b1)

begin

State = 3'b001;

F=0;

end

else

begin

State = 3'b000;

F=0;

end

end

3'b001:begin

if (x == 1'b1)

begin

State = 3'b010;

F=0;

end

else

begin

State = 3'b000;

F=0;

end

end

Figure 4-a. Verilog module of Count_Four

Spring 2013-2014

28

University of Sharjah

Computer Engineering

3'b010:begin

if (x == 1'b1)

begin

State = 3'b011;

F=0;

end

else

begin

State = 3'b000;

F=0;

end

end

3'b011:begin

if (x == 1'b1)

begin

State = 3'b100;

F=0;

end

else

begin

State = 3'b000;

F=0;

end

end

3'b100:begin

if (x == 1'b1)

begin

State = 3'b100;

F=1;

end

else

begin

State = 3'b000;

F=0;

end

end

default :begin

State = 3'b000;

F=0;

end

endcase

end

//end case-statement

end //end if-else statement

//end always statement

endmodule

Figure 4-b. Verilog module of Count_Four

Spring 2013-2014

29

University of Sharjah

Computer Engineering

3. Compiling the design

3. Go to Processing Start Compilation

4. The compilation should be successful with 4 warnings. Ignore these warnings

and go to the next step.

4. Simulating the design

5. Go to File New

6. Select "Other Files" and select "Vector Waveform File".

7. A new waveform file will be opened.

8. Right Click on Name bar and select Insert Insert Node or Bus.

9. In the Insert Node or Bus popup window choose Node Finder.

10. Select List on the right hand side. All the Inputs/Outputs will appear on the left

hand side of the pop-up window. Select all signals (ONE-BY-ONE) and transfer

them to the right hand side of the pop-up screen using the right arrow in the

middle. Hit "OK" and go to next step.

11. Hit Ctrl+W to see the whole file.

12. Assign the value of the clock by right clicking with the mouse button and go to

Value Clock... as shown in Figure 5. A popup window shown in Figure 6 will

appear. Choose a reasonable clock for this design. A 50ns clock period is sufficient as

shown in Figure6. Make sure that the Duty Cycle of the clock is 50%.

13. Assign several sequences to input "x", and save the file as "Count_Four.wvf".

14. Go to Processing Start Simulation

15. Simulation should be successful with no warnings.

16. Look into the file to verify the outputs.

Figure 5: Assigning Value to "CLOCK" signal

Spring 2013-2014

30

University of Sharjah

Computer Engineering

Figure 6: Clock Assignment

5. Pin Assignments

In this section we will use only the External Clock, Switches, Push Buttons, and the

Green Light Emitting Diodes (LEDs) to assign the inputs and outputs of the function.

7. Go to Assignment Assignment Editor.

8. In the "Category:" option select "Pin"

9. Double click with your mouse button on line#1, and type in TABLE 2. For more

information, look in the Appendix (or Altera DE2 Manual) for a complete list of

Switches, LEDs, and Pushbuttons assignment.

10. Save your design and recompile it. You should get 3 warnings only. Ignore these

warnings and go to next step.

Table 2: Pin Assignments

CLOCK

PIN_P26

RST

PIN_N25

x

PIN_N26

F

PIN_AE22

Spring 2013-2014

31

University of Sharjah

Computer Engineering

5. Programming to Traffic_Sys Design

In this section you will program the DE2 FPGA CycloneII and test your design.

10. Connect the USB-Blaster cable to your computer and turn on the board by

pushing the red button on the board. Make sure that the board is in RUN

mode not programmer mode (This is a switch on the left hand side of the

board). For more details, please refer to the Altera DE2 manual.

11. Go to Tools Programmer or push the programmer button located in the

top right corner.

12. Select Count_Four.sof.

13. Select Program/Configure

14. Make sure the Hardware Setup USB-Blaster[USB0] is selected.

15. Push the Start Button to start programming the board.

16. The lights on the board will indicate the chip is configured.

17. Use a 1 HZ clock from your DLD Trainer. Test the chip with the same test

as the input.

18. Go to File Close Project and exit Quartus II.

Assignment:

Q1: Design a sequential machine that counts the number of one's when input x

is equal to one and display the count number on LEDs.

Hint use only a register of four bits width.

Q2: Implement a 5-Bit Binary Counter.

Hint use only a register of 5 bits width.

RST

5-Bit Counter

Output:

5 Bits

Binary

Counter

Clock

Spring 2013-2014

32

University of Sharjah

Computer Engineering

Appendix

Spring 2013-2014

33

University of Sharjah

Computer Engineering

Spring 2013-2014

34

University of Sharjah

Computer Engineering

Experiment No. 4

Implementation in Verilog (Part 2)

Objectives:

In this lab you will practice on verilog programming.

Problems:

You have to solve the following problems using Altera DE2 board and

Quartus II 6.1 during lab

time as an individual work and submit your solution at the end of the lab

session.

For each problem, you have to write a program using verilog code and

Quartus software. Show

your outputs on waveforms and altera board.

Problem 1: Design 2*4 decoder: Using two methods: a) if-else statement

b) case statement

The following is the truth table for 2x4 Decoder:

Truth table for 2x4 Decoder

A B | D3 D2 D1 D0

---------+----------------0 0 | 0 0 0 1

0 1 | 0 0 1 0

1 0 | 0 1 0 0

1 1 | 1 0 0 0

Problem 2: Compare between three numbers and display the maximum

number of them on a 7-segment display of altera board.

Problem 3: Design a multiplexer 2*1, the inputs of the multiplex (x and y)

is a 4-bit width. If selector is one, then it will pass an output from a 3-bit

even counter. If selector is zero, then it will pass the output from a 3-bit odd

counter.

Problem 4: Design an even counter that counts from zero to 18 and then go

back to zero. Display the output on two segment displays of the altera board.

Spring 2013-2014

35

University of Sharjah

Computer Engineering

Appendix

Spring 2013-2014

36

University of Sharjah

Computer Engineering

Spring 2013-2014

37

University of Sharjah

Computer Engineering

Experiment No. 5

Introduction to Digital Logic Design Lab using Basic

Logic Gates

Objectives

To study the operation of basic logic gates

To investigate the behavior of simple logic circuits

Introduction

Components

The components mainly used in this lab are various types of digital

integrated circuits (Digital ICs or chips). These digital ICs are classified not

only by their logic operation, but also the specific logic-circuit family to

which they belong. Each logic family has its own basic electronic circuit

upon which more complex digital circuits and functions are developed. The

most frequently used logic families are TTL (Transistor-Transistor Logic)

and CMOS (Complementary metal-oxide semiconductor). TTL has a well

established popularity among Logic families and are used in this lab. CMOS

is widely used in large scale integrated circuits because of their high

component density and relatively low power consumption.

TTL ICs are usually distinguished by numerical designation 5400 and 7400

series and the power supply for TTL ICs usually is 5V. The common CMOS

type ICs are in the 4000 series and the power supply for CMOS ICs ranges

from 3V to 15V. Table below shows the standard logic levels for TTL gates

Logic Level

LOW (0)

Undefined

HIGH (1)

TTL Volts

0.0 to 0.8 V

0.8 to 2V

2.2 to 5V

The most popular package style of a TTL IC is Dual in line package

(DIP). An IC has many pins (input/output pins and power supply pins)

and in DIP these pins are arranged equally on either side as shown in

Spring 2013-2014

38

University of Sharjah

Computer Engineering

figure 1.1. You will have to read the datasheet of each IC before using it

in your circuits to know the function of each pin. The pin numbers of an

IC can be identified easily by a notch or dot. The pin on the top left side

of the notch/dot is always pin number 1 and pin on the top right side is

always the last pin as shown in fig 1.1

Figure 1.1 Standard DIP package

You will read some numbers and letters on the IC's such as:

74H00: which means this chip contains four two inputs NAND gates.

H means high speed.

74L00: which means this chip contains four two inputs NAND gates.

L means low power.

74LS: L means low power; S means Schottky.

74AS: A means advanced; S means Schottky.

Spring 2013-2014

39

University of Sharjah

Computer Engineering

74ALS: A means advanced; L means low power; S means Schottky.

Note: the 74S series is twice faster than the 74H series. ;

Following Digital ICs are required for the experiments in this manual:

7400 Quad 2-Input NAND

7402 Quad 2-Input NOR

7404 Hex INVERTER

7408 Quad 2-Input AND

7410 Triple 3-Input NAND

7411 Triple 3-Input AND

7420 Dual 4-Input NAND

7421 Dual 4-Input AND

7427 Triple 3-Input NOR

7432 Quad 2-Input OR

7447 BCD To 7-Segment Display Driver

7474 Dual D FLOP-FLOP

7476 Dual J-K FLOP-FLOP

7483 4-Bit Binary Adder

7486 Quad 2-Input EX-OR

7493 4-Bit (0-15) Ripple Counter

74147 Decimal To BCD Priority Encoder

74154 4 To 16 Decoder

74194 Universal Shift Register

In addition to the above digital ICs other components such as SPST

switches, 7-segment displays, resistors etc are also needed.

The basic gates are the building blocks of more complex logic circuits.

These gates perform the basic Boolean functions, such as AND, OR and

NOT. All logic circuits are made up of combinations of the electronic

equivalent of simple series and parallel connected switches. At the end of

this introductory laboratory section the students will be familiar with basic

logic gate ICs and their equivalent switching circuits. Also they will learn

how to implement simple logic circuits.

Following are the tools and equipment using the Digital Logic Design Lab:

Spring 2013-2014

40

University of Sharjah

Computer Engineering

Tools & Equipment

Circuit Maker

Circuit Maker is a powerful, user-friendly, circuit simulation program that

allows you to easily draw and modify digital circuits. Its powerful built-in

digital and analog simulation capability can save your time and money by

allowing you to check your designs before you build them. A simple tutorial

on circuit maker is given in Appendix A.

Digital Trainer (ETS-7000)

ETS -7000 (Figure 1.2) combines a multitude of features and all essential

functions of digital experiments in one compact unit.

Figure 1.2

Spring 2013-2014

41

University of Sharjah

Computer Engineering

The unit mainly contains:

1. DC power Supply

Fixed DC Output:

Variable DC output:

+5V, 1 Amp and -5V, 300mAmp

0 to +15 V, 500mA and 0 to -15V, 500mA

2. Potentiometers: Variable resistor VR1 = 1k and VR2 = 100k

3. Function Generator: Operate in five variable range frequencies from

1KHz to 100KHz to Provide sine wave (0 to 8 V pp), Triangular wave (o

to 6 V pp) Square wave (0 to 8 V pp) and TTL output 5 Vp.

4. Eight toggle switches and corresponding output point: When the

switch is set at down position, the output is LOW (logic 0) and at UP

position, the output is HIGH (logic 1). Used to input 0 or 1 to logic

circuits.

5. Two Pulse Switches (push buttons) with two sets of outputs A, A, B

and B) to provide High to Low and Low to High clock pulses.

6. Speaker: To produce sound.

7. Adapter: Used to connect peripherals to the digital trainer

8. Two 7-segment Displays with decoder to display decimal numbers.

9. Eight LED displays with separate input terminals. The LED will light up

when input is at HIGH level and it will be turned off when it is at Low

level. Used for checking the output of logic circuits.

10. Solderless Breadboard

The large solderless breadboard is used for mounting components and

ICs (constructing the circuits)- This removal breadboard has many strips

of metal (nickel plated contact), which run underneath the board. These

metal strips are laid out horizontally and vertically as shown in figure 1.3.

Spring 2013-2014

42

University of Sharjah

Computer Engineering

Figure 1.3

To use the breadboard, the legs of component are placed in the holes. The

holes are made so that they will hold the components in place. Each hole is

connected to one of the metal strips running underneath the board. The long

top, middle and bottom rows are usually used for power supply connections.

The circuit is built by placing components and connecting them together with

jumper wires. The ICs should be placed on the board in such a way that the

pins of the ICs are electrically isolated (no connection between pins).

The correct (and wrong) way of placing ICs on the bread board is shown in

figure 1.4.

Spring 2013-2014

43

University of Sharjah

Computer Engineering

Figure 1.4

Logic Probes

Logic probe is a useful device to detect the logic state of an IC and provides

a quick, inexpensive way for you to locate the fault. The Logic probes can

show you immediately whether a specific point in the circuit is low, high,

open, or pulsing. These probes are usually connected directly to the power

supply of the device being tested. A logic probe has three visible indicators Red, Green and Yellow LEDs.

Red LED (HI) The voltage is a valid HIGH (logic 1)

Green LED (LO) The voltage is a valid LOW (Logic 0)

Spring 2013-2014

44

University of Sharjah

Computer Engineering

Yellow LED (Pulse): The yellow or pulse LED comes on for approximately

200 ms to indicate a pulse without regards to its width. This feature enables

one to observe a short duration pulse that would otherwise not be seen on the

red and green LEDs. The brightness of the HIGH and LOW LEDs are an

indication of the duty cycle.

Multi-meter

Used for measuring voltage, current and resistance

Building the Circuit

The steps for wiring a circuit should be completed in the order described

below:

1. Make sure the power is off before building your circuits

2. Connect the +5V and ground (GND) leads of the trainer to the power

and ground bus strips on your breadboard (long connections on the

bread board)

3. Plug the chips you will be using into the breadboard properly. Point

all the chips in the same direction.

4. Connect +5V and GND pins of each chip to the power and ground bus

strips on the breadboard

5. Select a connection on your schematic and place a piece of hook-up

wire between corresponding pins of the chips on your breadboard. It is

better to make the short connections before the longer ones. Mark

each connection on your schematic as you go, so as not to try to make

the same connection again at a later stage.

6. Get one of your group members to check the connections, before you

turn the power on

7. If an error is made and is not spotted before you turn the power on,

turn the power off immediately before you begin to rewire the circuit.

8. At the end of the laboratory session, collect your hook-up wires,

components and all equipment and leave it in the same condition as it

was before you started.

Spring 2013-2014

45

University of Sharjah

Computer Engineering

Equipment & Components Required for this experiment

DIGITAL TRAINER

LOGIC PROBE

1 IC of 7404 NOT

1 IC of 7408 AND

1 IC of 7432 OR

Procedure

Part 1: 2-InputAND Gate

1. Insert AND gate IC (74LS08) on the breadboard properly and connect its

power supply pins (Vcc & Ground) to +5V and GND on the trainer

(Refer datasheet for the pin layout of 74LS08)

2. Select any one gate (out of four) from the 7408 IC, label its input as A &

B and connect these inputs to any two toggle switches and output (F) to

an LED on the trainer as in fig 1.5.

3. Note the output F for all possible combinations of inputs A and B and

complete the truth table 1.1 (the ON/OFF condition of LED indicates the

logic level 1/0).

Figure 1.5

Inputs

A

B

0

0

1

1

Logical Output F

Expected

Experimental

0

1

0

1

Table 1.1

Spring 2013-2014

46

University of Sharjah

Computer Engineering

Part 2: 2-input OR Gate

1. Repeat steps 1 to 3 in part 1 for figure 1.6 (with OR Gate IC 74LS32)

and complete table 1.2.

Inputs

A

Logical Level of F

Expected

0

1

2

Figure 1.6

Experimental

0

0

Table 1.2

Part 3: Not Gate

1. Repeat steps 1 to 3 in part 1 for figure 1.7 (with NOT gate IC 74LS04)

and complete table 1.3. (IC 74LS04 has six gates inside, each gate has

only one input. Select any of them and connect its input to a toggle

switch and output to an LED) as in figure 1.7.

Inputs

A

0

1

Figure 1.7

Logical Level of F

Expected Experimental

Table 1.3

Part 4: Implementation of simple Logic circuits

1. For the logic circuit of fig 1.8 write the Boolean expression for F.

Simulate the circuit using circuit maker and complete the output column

(F1) of table 1.4.

2. Obtain the simplified expression for F using Boolean algebra and draw

the simplified logic diagram (Using only three gates AND, OR and

NOT - 1 each)

Spring 2013-2014

47

University of Sharjah

Computer Engineering

3. Construct the simplified logic circuit, note the output F for each

combination of input and complete the output column (F2) of table 1.4

4. Compare the outputs obtained in steps 1 & 3 above and write your

comments.

Figure 1.8

A

0

0

0

0

1

1

1

1

Inputs

B

0

0

1

1

1

0

1

1

F1

F2

C Step 1 Step 3

0

1

0

1

0

1

0

1

Table 1.4

Spring 2013-2014

48

University of Sharjah

Computer Engineering

Experiment No. 6

Combinational Circuits Design Using Utilizing Basic

TTL Gates

Objectives:

To design and implement combinational circuits with different logics from a

set of statements which describe the circuits behavior.

Introduction

Figure 4.1 shows the block diagram of a combinational logic circuit. It

consists of input variables, logic circuit (Combination of logic gates) and

output variables. The logic circuit accepts signals from the inputs and

generates signals to the outputs. The operation of a combinational logic

circuit can be specified with a truth table that lists the output values for each

combination of input variables. Also, it can be described by m Boolean

functions, one for each output variable. Each output function is expressed in

terms of n input variables.

n inputs

Combinational

Logic Circuits

m outputs

Figure 4.1

A combinational logic circuit can be implemented in many different logics

such as AND-OR, OR-AND, NAND-NAND (NAND logic), NOR-NOR

(NOR logic) etc. Since NAND and NOR gates are easier to fabricate with

electronic components and are the basic gates used in all IC digital families,

NAND or NOR logic are extensively used for implementing combinational

logic circuits. In this experiment students will learn how to design and

implement logic circuit using different logics.

Equipment & Components Required

DIGITAL TRAINER

LOGIC PROBE

2 ICs of 7400 QUAD 2-I/P'S NAND GATE

Spring 2013-2014

49

University of Sharjah

1

3

1

1

1

ICs of

ICs of

ICs of

ICs of

ICs of

Computer Engineering

7404 HEX INVERTERS

7402 QUAD 2-I/P'S NOR GATE

7486 QUAD 2-I/P'S XOR GATE

7410 QUAD 3-I/P'S NAND GATE

7411 QUAD 3-I/P'S AND GATE

Procedure

Part 1

For each of the design problem stated below:

1. Obtain the Truth Table from the problem statement.

2. Using K Map, obtain simplified Boolean expressions for each of the

output variable and draw the logic diagram using the gates specified

in the design constraints.

3. Using circuit maker simulate the circuit and verify the truth table.

Part 2

Construct the circuit for problem 3 and experimentally verify the truth table.

Problem 1

Design a combinational circuit with three inputs, A, B and C, and two

outputs, X and Y. The output X becomes 1 when the binary input,

ABC (taking A as MSB), is a multiple of 3. The output Y becomes 1

when the binary input, ABC, is a multiple of 2 and 3 both. Do not

consider 0 as a multiple of any number.

Design Constraint: 3-input AND gates and Inverters ONLY.

Problem 2

Design a 3-bit majority circuit. A majority circuit is a combinational

circuit whose output is equal to 1 if the input variable has more 1's

than 0's. The output is 0 otherwise.

Design Constraint: 2-input and 3-input NAND gates ONLY.

Spring 2013-2014

50

University of Sharjah

Computer Engineering

Problem 3

Design a combinational circuit to count the number of 1's in a 3-bit

input. The output represents the number of 1's in binary i.e. if the

input is '101' then the output will be '10' representing two 1's in the

input.

Design Constraint: 2-input and 3-input NAND gates and 2-input

XOR gates ONLY.

Problem 4

A combinational switching network has three inputs (A, B, and C) and

two outputs X, Y. The output X is 1 if the input number is a prime

number. Y is 1 if the decimal value of its inputs is not a multiple of

three.

Note: The two input combinations 001 & 100 are forbidden.

Design constraint: 2-input NAND, Inverter, & 3-input NAND gates

ONLY.

Problem 5

Design an error detection circuit for 3-bit input. The circuit must have

two outputs X and Y. The output X becomes 1 when there are two

consecutive 1's in the binary input. Similarly, the output Y becomes 1

when there are two consecutive 0's in the binary input. In all other

cases the outputs should be 0.

Design Constraint: 2-input NOR gates ONLY.

Spring 2013-2014

51

University of Sharjah

Computer Engineering

Experiment No. 7

Arithmetic Logic Unit and Datapath Utilizing Decoders

and Encoders

Objectives:

To implement and investigate the operation of 4-bit binary addersubtractor and magnitude comparator circuits.

To study the operation of decoders/encoders and their applications in

digital systems.

Introduction

One of the primary functions any calculator or digital computer must

perform is binary addition. A combinational logic circuit that performs the

addition of two bits and produces the sum and carry is called a half adder

(fig 5.1a)

b

Figure 5.1

The circuit that performs addition of three bits (two significant bits and a

previous carry) and produces the sum and carry is called a full adder (figure

5.1b). The names of the circuit derived from the fact that a full adder can be

implemented with two half adders.

An n-bit binary adder can be constructed with n-full adders connected in

cascade, with the output carry from each full adder connected to the input

carry of the next full adder connected in chain. Such binary adders are

available in IC form. Figure 5.2 shows the block diagram of 4-bit binary

adder IC (74LS83). It can add two 4-bit numbers, say A (= A4 A3 A2 A1) and

B (= B4 B3 B2 B1) and produce sum output S (= S4 S3 S2 S1). C0 is the initial

carry input and C4 is the final carry output.

Spring 2013-2014

52

University of Sharjah

Computer Engineering

Figure 5.2 - Block diagram of 7483 IC

The 7483 IC can be used as a 4-bit binary adder-subtractor with some

modifications as shown in figure 5.3. It can be seen that the 7483 receives

Figure 5.3

the first operand A directly and other operand B through XOR gates. Each

XOR gates receives mode input M and one of the inputs of B. When M=0

the circuit is an adder and when M=1 it becomes subtractor as explained

below.

When M = 0, the initial carry C0 = 0, one of the input of each XOR gates is 0

and each XOR gate passes the other input to its output (because X0 = X).

Spring 2013-2014

53

University of Sharjah

Computer Engineering

Thus the second input to 7483

as follows

First operand

Second operand

Sum output

is B and the circuit perform normal addition

C4 C3 C2 C1 0 +

A=

A4 A3 A2 A1 +

B=

B4 B3 B2 B1

S = C4 S4 S3 S2 S1

When M = 1, the initial carry C0 = 1, one of the input of each XOR gates is 1

and each XOR gate produces the complement of its other input (because

X1 = X). Thus the second input to 7483 is 1s complement of B. This 1s

complement plus C0 (1) becomes 2s complement of B. Thus circuit adds 2s

complement of B to A (i.e. subtraction by 2s complement).

C4 C3 C2 C1 1 +

First operand

A=

A4 A3 A2 A1 +

Second operand (1s complement of B) =

B4 B3 B2 B1

Sum output

S=

C4 S4 S3 S2 S1

The circuit of figure 4.3 in subtractor mode can be used as a 4-bit magnitude

comparator for checking the conditions A = B, A < B and A > B. For this

you will have to design a combinational logic circuit with C4, S4, S3, S2, S1, as

inputs and E, L and G as outputs.

Output E= 1 if A = B (When A = B, S = 0000)

Output L= 1 if A < B (When A < B, carry out put C4= 0)

Output G= 1 if A > B (When A > B, C4 = 1 and S 0000)

Decoders & Encoders:

Digital systems contain binary-coded data and information. Decoder and

encoder circuits are used in digital system for changing data from one type

of code to another. Since this is a common operation in digital systems these

circuits are available in IC forms. In this experiment we will concentrate on

BCD to 7-segment decoder and a Decimal to BCD encoder.

The 7-segment display, used for displaying decimal numbers (0 to 9)

consists of 7 segments a, b, c, d, e, f, g and seven inputs as shown in figure

5.4 (a). Each segment is a Light emitting Diode LED (figure 5.4 (b)) that

emits lights when current passes through it. There are two types of displays

1) Common anode and 2) Common Cathode. A common anode type ties all

of the + voltage sides (Anode) of the LEDs together to a common point and

this common point must be connected to +5V as shown in figure 5.4 (c). In

Spring 2013-2014

54

University of Sharjah

Computer Engineering

order to turn on a specific segment in a common anode type display, you

must supply a low voltage (logic 0) at that segment. In other words, when

you apply logic 0 to a, b, c, d and g input lines, these segments will be ON

and you will get a display 3. In common cathode type display, the cathode

of all LEDs is connected together to ground and a logic 1 must be applied to

enable a segment.

In order to display a BCD number on a seven segment display, a BCD to

seven segment decoder is needed to translate the 4-bit BCD number into

seven segments (7-bits). Since this is a common operation in digital systems

such decoders are available in IC forms. For example 74LS 47 (for common

anode display) and 74LS48 (for common cathode display).

(a)

(b)

(c)

Figure 5.4

Equipment & Components Required

DIGITAL TRAINER , LOGIC PROBE

2 IC of 7483 4-BIT BINARY ADDER

1 IC of 7421 4-input AND GATE

2 IC of 7404 INVERTERS

1 ICs of 7486 QUAD 2-I/P'S XOR GATE

1 IC of 74147 ENCODER

1 IC of 7447 BCD TO 7-SEGMENT DECODER/DRIVER

1 IC of 74154 4-to-16 DECODER

1 IC of 7432 2-INPUT OR GATE

2 IC of 7420 4-INPUT NAND GATE

1 Resistor pack (contains 8 resistors) of 270 ohms

1 Seven Segment display Common anode type.

Spring 2013-2014

55

University of Sharjah

Computer Engineering

Procedure

Part 1: Parallel Adder-Subtractor:

1. Using circuit maker simulate the operation of circuit in figure 5.3 with

three different inputs of your choice (with M=0 and M=1) using ICs

7483 and 7486. Show clearly the inputs and outputs in table 5.1

2. Construct the circuit in figure 5.3 by connecting the inputs A (A1

through A4) and B (B1 through B4) to the toggle switches and the sum

output S (S1 through S4) and carry output C4 to the LEDs on the

trainer. You may connect the mode control input M to GND to set

M=0 and to Vcc to set M = 1.

3. Experimentally verify the results obtained in step 1 and write your

comments.

M=0

M=1

Inputs

Outputs

Inputs

Outputs

A4A3A2A1

B4B3 B2B1

C4 S4S3S2 S1

A4A3A2A1

B4B3 B2B1

C4 S4S3S2 S1

Table 5.1

4. Keep the connection of this circuit, dont disconnect it, you will use it

for the next part.

Part 2: Decoder:

1. Refer the datasheet of 7447, 7-segment display and construct the circuit

in Fig 5.5.

2. Experimentally verify your results and fill it in table 5.2.

Spring 2013-2014

56

University of Sharjah

Computer Engineering

Figure 5.5

Note: Seven resistors are used to guarantee that the same current flows through all

segments that are currently on (keeping all segments at a uniform brightness).

BCD inputs

0 0 0 0

Decimal display

0 0 0 1

0 0 1 1

0 1 0 0

0 1 0 1

0 1 1 0

0 1 1 1

1 0 0 0

1 0 0 1

Table 5.2

3. Now, go back to the previous part, disconnect the inputs from the

switches.

4. Connect the output of the adder to the input of the decoder and display

the output result.

5. Experimentally verify the results obtained in the previous part.

Spring 2013-2014

57

University of Sharjah

Computer Engineering

Part 3: Magnitude Comparator:

1. Design a 4-bit magnitude comparator with 4-bit adder-subtractor

circuits and other logic gates.

2. Using circuit maker verify the operation of the circuits with three

different sets of inputs. Show clearly the inputs and outputs in table 5.3

Inputs

A4 A3 A2 A1

Outputs

B4 B3 B2 B1

Table 5.3

Part 5: Encoder:/

1. Simulate the operation of circuit shown in figure 5.6 using circuit maker.

2. Construct the circuit in figure 5.6 and experimentally verify the results

obtained in step 1.

Figure 5.6

3. Verify your result using the 7-segment display.

Spring 2013-2014

58

University of Sharjah

Computer Engineering

Experiment No. 8

Sequential Circuits Design

Objectives:

To investigate the operation of various types of Flip-flops.

To design, build and test sequential circuit from a state diagram.

Introduction:

In the previous experiments, the logic circuits introduced were combinational.

The output of these circuits depends on the present combination of the inputs

and these circuits do not have any memory cells. Memory cells are very

important in digital systems and are used for temporary storage of the outputs

produced by a combinational logic circuit for use at a later time in the operation

of a digital system. Logic circuits that incorporate memory cells are called

sequential logic circuits; their output depends not only upon the present value

(state) of the input but also upon the previous values (state). Usually a

sequential logic circuit requires timing signal or clock signal for their operation.

A clock pulse is a signal that has two different voltage levels as shown in figure

6.1. It remains at the high level for a time called the pulse width (t w), and then

returns to the low level. A periodic pulse train repeats itself in a regular

manner. The time for one complete cycle in a periodic signal is called period

(T). The reciprocal of the period is the frequency (f), which is the number of

cycles per second. A second characteristic of a periodic pulse is the duty cycle.

The duty cycle is the pulse width (tw) divided by the period (T) and it is usually

given as a percentage. These definitions are shown in figure 6.1.

Figure 6.1 Definitions for a periodic pulse

Spring 2013-2014

59

University of Sharjah

Computer Engineering

The flip-flop (also called latch) is a basic bi-stable memory cell widely used

in sequential logic circuits. Usually there are two outputs, Q and its

complement Q. They are called state variables. State variables which

change only between logic 1 and logic 0 are called binary state variables.

There are various types of flip-flops such as Basic R-S Flip-flop, Clocked RS flip-flops, D-Flip-flops, J-K Flip-flop etc. Flip-flops are seem to be

everywhere in digital systems such as counters, memories, registers,

arithmetic circuits, timing and control circuits, frequency dividers etc. These

flip-flops can be implemented with logic gates. Since flip-flops are the basic

building block of a sequential circuits, they are commercially available in IC

form (D flip-flop IC 7474, J-K Flip-flop IC 7476).

Sequential Circuits

The behavior of a sequential circuit can be described by means of state

equations or state diagram or state table. It means one can build a sequential

circuit from a set of state equations or from a state table or from a state

diagram. In this experiment you will build a sequential circuit from a given

state diagram. The State diagram is a graphical representation of a sequential

circuit. In this diagram the state is represented with a circle and the transition

between states are indicated by the directed lines connecting the circles. The

binary number inside each circle identifies the state of the flip-flops. The

directed lines are labeled with two binary numbers separated by a slash. The

first one represents the input value during the present state and second one

(after the slash) represents the output during the present state with the given

input.

Equipment & Components Required

DIGITAL TRAINER

LOGIC PROBE

2 ICs of 7400 QUAD NAND GATE

1 IC of 7476 DUAL M/S F/F

1 IC of 7474 DUAL D F/F

1 IC of 7486 XOR GATE

Spring 2013-2014

60

University of Sharjah

Computer Engineering

Procedure

Part 1. Flip-flop circuits using logic gates

Design the following flip-flop circuits using NAND gates. Simulate the

operation of these flip-flop circuits using circuit maker and verify their truthtables

1. Basic R-S Flip-flop

2. Clocked R-S Flip-flops

3. D-Flip-flops

Part 2: D flip-flop IC 7474

1. Refer the datasheet and study the functions of input, output and control

pins of D Flip-flop IC (74LS74).

(The 7474 IC contains two independent positive-edge-triggered flip-flops,

each has input/ output lines as shown in figure 6.2. The information on the

D input is accepted by the flip-flops on the positive going edge of the

clock pulse (indicated with an upward arrow in the function table 6.4).

The preset (PR)and Clear (CLR) are active low control inputs (bubble on

these lines indicate active low a logic 0 on the PR or CLR inputs will set

or reset the outputs regardless of the logic levels of the other inputs)

2. Connect CLK input to a pulse switch and other inputs (D, PR and CLR) to

logic switches. Connect all output to LEDs on the trainer

3. Proceed through the conditions on the truth table 6.1 and record the

results.

Inputs

Outputs

PR CLR CLK D Q

Q

L

H

X

X

H

L

X

X

L

L

X

X

H

H

H

H

H

L

H

H

L

X

Figure 6.2

Table 6.1

Spring 2013-2014

61

University of Sharjah

Computer Engineering

Part 3: Study of J-K flip-flop IC 7476

Repeat all steps in part 2 for J-K flip flops (IC 7476) in figure 6.3 and

complete the table 6.2. The 7476 IC contains two independent positive pulse

triggered J-K flip-flops with two inputs and two outputs. A LOW logic level

on the preset (PR) or clear (CLR) inputs will set or reset the outputs

regardless of the logic levels of the other inputs.

Figure 6.3

Inputs

PR CL

R

L

H

H

L

L

L

H

H

H

H

H

H

H

H

CL

K

X

X

X

Outputs

K Q

Q

X

X

X

L

L

H

H

X

X

X

L

H

L

H

Table 6.2

Part 4: Sequential Circuits

1. Analyze the state diagram shown in figure 6.4 and complete the state

table (table 6.3). Assume that the states are represented with JK flipflops.

2. Obtain the simplified expressions for the flip-flops inputs and draw the

sequential circuits with least number of components.

3. Simulate the circuit using circuit maker and verify the state diagram or

state table.

4. Construct the circuit and experimentally verify the state table or state

diagram.

Spring 2013-2014

62

University of Sharjah

Computer Engineering

Figure 6.4

Present

State

A(t) B(t)

0 0

0 0

0 1

0 1

1 0

1 0

1 1

1 1

Input Next state

X

0

1

0

1

0

1

0

1

Output

A(t+1) B(t+1)

Flip-flop inputs

JA KA

JB KB

Table 6.3

Spring 2013-2014

63

University of Sharjah

Computer Engineering

Experiment No. 9

Registers and Counters with Design Applications

Objectives

To investigate the operation of different type of registers

To investigate the operation of asynchronous and synchronous

counters

Introduction

Registers:

The term register can be used in a variety of specific applications, but in all

cases it refers to a group of flip-flops. Each flip-flop is capable of storing 1

bit of information. Thus an n-bit register consists of a group of n flip-flops to

store n bits of binary information.

Different types of registers are available commercially. The simplest is one

that consists of only flip-flops without any gates. Figure 7.1 shows a simple

4-bit parallel register with D flip-flop. It is called a parallel register because

all bits of information are loaded simultaneously (in parallel) with a

common clock pulse.

Figure 7.1

Spring 2013-2014

64

University of Sharjah

Computer Engineering

A register capable of shifting its binary information in one or both

directions is called a shift register. Figure 7.2 shows a simple 4-bit shift

register using D flip-flops. Each clock pulse shifts the contents of the

register one bit position to the right. The serial input determines what

goes into the leftmost flip-flop during the shift.

Figure 7.2

In addition to the flip-flops, a register may have combinational gates that

perform certain data processing tasks such as shift the data right or left,

parallel in parallel out, serial in parallel out etc. Since such functions are

common in digital systems, TTL ICs capable of performing these tasks are

commercially available (Example: Universal Shift Register IC 74194).

Figure 7.3 shows the block diagram of 7494 IC. This bidirectional shift

register incorporates operations such as parallel load, right-shift, left-shift,

Clear etc. These modes of operations are controlled by the selection lines S0

and S1 as shown in the function table 8.1. The parallel loading is

accomplished by applying the four bits of data and taking both mode control

inputs, S0 and S1, logic 1. The data is loaded into the associated flip-flops

and appear at the outputs after the positive transition of the clock input.

During loading, serial data flow is inhibited. Shift right is accomplished

synchronously with the rising edge of the clock pulse when S0 is at 1 and S1

is at 0. Serial data for this mode is entered at the shift-right data input. When

Spring 2013-2014

65

University of Sharjah

Computer Engineering

S0 is 0 and S1 is 1, data shifts left and new data is entered at the shift-left

serial input. Clocking of the flip-flop is inhibited when both mode control

inputs are low.

Figure 7.3

Table 7.1

Counter

A counter is a sequential circuit which goes through a predetermined

sequence of states upon the application of input pulses. The counters may be

classified as asynchronous (ripple counter) or synchronous depending on the

way in which the clock input is applied.

In a ripple counter the clock input of flip-flops are not triggered by the

common clock pulse. The output of each flip-flop connected to the clock

input of the nest higher order flip-flop as shown in figure 7.4. Whereas in a

Spring 2013-2014

66

University of Sharjah

Computer Engineering

synchronous counter all flip-flops are triggered by a common clock pulse as

shown in figure 7.5.

Both asynchronous and synchronous counters can be constructed with flipflops. An n-bit counter (asynchronous or synchronous) needs n flip-flops.

Since the counters are important part of many digital systems these counters

are commercially available in IC form.

Equipment & Components Required

DIGITAL TRAINER

LOGIC PROBE

1 IC of 74194 UNIVERSAL SHIFT REGISTERED

2 ICs of 7474 DUAL D- F/F

2 IC of 7476 J-K FLIP-FLOP

1 IC of 7493 COUNTER

1 IC of 7408 2-INPUT AND GATE

Procedure

Part 1: 4-bit Parallel in parallel out register

Using circuit maker simulate the operation of circuit in figure 7.1 by

observing the output for each condition of CLR, PR and CLK inputs

listed in table 7.2. The data input A B C D may be set to any desired

value. If no change in the output is observed you may simply write No

change in the output column

CLR

PR

CLK

0

1

1

1

1

0

1

1

X

X

L

INPUTS

A B C D

OUTPUTS

QA QB QC QD

Table 7.2

Spring 2013-2014

67

University of Sharjah

Computer Engineering

Part 2: Shift register (Serial in parallel out)

Using circuit maker simulate the operation of the circuit in figure 7.2 by

performing the following

1. Connect the CLR input momentarily to 0 and then to 1. This will

reset the register (output becomes 0000).

2. Load a 4-bit data (any desired data, say 1011) through the serial input

one bit at a time starting from the LSB. For loading each bit you

need a clock pulse.

3. Study the operation of the circuit with different data and write your

comments.

Part 3: Universal Shift Register (74194)

1. Construct the circuit of figure 7.3. Connect all inputs except the clock to

the logic switches and outputs to LEDs on the trainer.

2. For each listed condition of the inputs observe the output (after enabling

the clock input) and complete the table 7.2. You may apply any desired

4-bit number as input (A B C D). If there is no change in output you may

simply write no change in the output column.

Inputs

Mode

Clear

S1

S0

0

1

1

1

1

1

1

1

0

0

1

0

0

1

1

0

0

0

1

1

1

0

0

0

Clock

Outputs

Serial

Left

1

1

1

1

1

0

1

1

Right

1

1

1

0

1

0

1

1

Parallel

A B C D

QA QB QC QD

Table 7.3

Spring 2013-2014

68

University of Sharjah

Computer Engineering

Part 4: 4-bit Asynchronous (ripple) counter.

1. Using Circuit Maker simulate the operation of ripple counter in figure 7.4

by performing the following.

a. Set Preset= 0 and Clear= 1 apply clock pulses and observe sequences

generated by the counter.

b. Set Preset=1 and Clear= 0 apply clock pulses and observe sequences

generated by the counter

c. Set Preset = 1 and Clear = 1 apply clock pulses and observe the

sequences generated by the counter

2. Convert the circuit in figure 7.4 to a BCD counter and simulates its

operation using circuit maker.

Figure 7.4

Part 5: Ripple counter using IC 7493

1. Refer the datasheet and study the functions of input/output lines of 7493

IC.

2. Make necessary connections to clock inputs (CP0 and CP1) and reset

inputs (R1 and R2) in the block diagram of 7493 in figure 7.5 so as to

operate it as a 4-bit binary counter. Write explanations for your

connections.

3. Construct the circuit and test it by applying clock pulses and observing

the output sequences.

Spring 2013-2014

69

University of Sharjah

Computer Engineering

Figure 7.5

Part 6: Combination between counter and universal shift register:

1. Now, keep the connection of the previous circuit and connect the output

of the counter to the inputs of the universal shift register.

2. Perform all the operations of the shift register. Make all the necessary

connections of the shift register. Put your result in table 7.4.

Inputs

Mode

Clear

S1

S0

0

1

1

1

1

1

1

1

0

0

1

0

0

1

1

0

0

0

1

1

1

0

0

0

Clock

Outputs

Serial

Left

Right

Parallel

A B C D

QA QB QC QD

Table 7.4

Spring 2013-2014

70

University of Sharjah

Computer Engineering

Part 7: Asynchronous BCD counter using 7493

1. Make necessary connections in figure 7.6 to convert the circuit in part 6

to a BCD counter. Give reasons for your connections.

Figure 7.6

2. Construct circuit and test the operation by applying clock pulses

Spring 2013-2014

71

Anda mungkin juga menyukai

- Sir Syed University of Engineering & Technology, Karachi: CS-128T Digital Logic DesignDokumen34 halamanSir Syed University of Engineering & Technology, Karachi: CS-128T Digital Logic Designسيده آمنہ رضویBelum ada peringkat

- Chapter 2 Floyd Ans - PDF (SHARED)Dokumen8 halamanChapter 2 Floyd Ans - PDF (SHARED)Mr AlphaBelum ada peringkat

- DLD LAB Sessional 2Dokumen10 halamanDLD LAB Sessional 2AitazazBelum ada peringkat

- Sir Syed University of Engineering & Technology, Karachi: CS-128T Digital Logic Design 2 Semester Computer ScienceDokumen20 halamanSir Syed University of Engineering & Technology, Karachi: CS-128T Digital Logic Design 2 Semester Computer ScienceFarrukh AbbasBelum ada peringkat

- IE LAB 8 HamzaDokumen7 halamanIE LAB 8 HamzaHamza BilgramiBelum ada peringkat

- Department of Computer Science: DLD Project: Touch Sensor and Automatic Street Light With SupplyDokumen14 halamanDepartment of Computer Science: DLD Project: Touch Sensor and Automatic Street Light With SupplyKashif RizwanBelum ada peringkat

- CS 102 Lab 1Dokumen18 halamanCS 102 Lab 1Abdulaziz Altararwah0% (1)

- Labview ReportDokumen16 halamanLabview ReportMd. Shah Kamal SaimumBelum ada peringkat

- Veilog HDL Module 3Dokumen62 halamanVeilog HDL Module 3Mallik KglBelum ada peringkat

- Labview File 5th SemDokumen20 halamanLabview File 5th Semvik9292Belum ada peringkat

- CSE Exp-1Dokumen3 halamanCSE Exp-1Piyas ChowdhuryBelum ada peringkat

- Ecad & Vlsi LabDokumen98 halamanEcad & Vlsi LabbitseceBelum ada peringkat

- EEEB161 Project PasswordCircuitDokumen4 halamanEEEB161 Project PasswordCircuitdaudBelum ada peringkat

- Digital Logic Lab ManualDokumen81 halamanDigital Logic Lab ManualArslan Majid100% (1)

- Digital Logic Design TutorialDokumen10 halamanDigital Logic Design TutorialShadab IrfanBelum ada peringkat

- Collect and Prepare Human Activity Sensor DataDokumen7 halamanCollect and Prepare Human Activity Sensor DataagamdeepBelum ada peringkat

- Chapter 13: Digital Control Systems 1Dokumen53 halamanChapter 13: Digital Control Systems 1Cesar100% (1)

- Experiment No: 02 Introduction To Labview: Aim: To Study Various Functions, Tools and Libraries of Labview (LV) SoftwareDokumen9 halamanExperiment No: 02 Introduction To Labview: Aim: To Study Various Functions, Tools and Libraries of Labview (LV) SoftwareVaibhav BacchavBelum ada peringkat

- Calculate Fibonacci Numbers in Assembly LanguageDokumen2 halamanCalculate Fibonacci Numbers in Assembly LanguageDilawarBelum ada peringkat

- D Digi Ital Elec Ctro Onic Cs La AB: L Lab M Manu UALDokumen41 halamanD Digi Ital Elec Ctro Onic Cs La AB: L Lab M Manu UALArrnaav Singh RathoreeBelum ada peringkat

- Practice Exam 3Dokumen33 halamanPractice Exam 3technovBelum ada peringkat

- Application of S-R Latch - Digital Logic & DesignDokumen13 halamanApplication of S-R Latch - Digital Logic & DesignskyviperBelum ada peringkat

- Logic Gates ExperimentDokumen5 halamanLogic Gates Experimentگيدوڙو ماڇيBelum ada peringkat

- Embedded Systems Lab ManualDokumen114 halamanEmbedded Systems Lab ManualPrasanth100% (1)

- Digital Logic Design CourseDokumen1 halamanDigital Logic Design CourseVinay PasiBelum ada peringkat

- HDL Manual 2020 5th Sem E&CE 18ECL58Dokumen74 halamanHDL Manual 2020 5th Sem E&CE 18ECL58vishvakiranaBelum ada peringkat

- Lab 12 Introduction To Simulink ObjectiveDokumen16 halamanLab 12 Introduction To Simulink Objectivesaran gulBelum ada peringkat

- Expt 5 - Wein Bridge Oscillator (2020)Dokumen3 halamanExpt 5 - Wein Bridge Oscillator (2020)samarthBelum ada peringkat

- Microprocessor - Lab 6 StudentDokumen18 halamanMicroprocessor - Lab 6 Studenttj millarBelum ada peringkat

- ICT2632 - ++oct+2017 - +information - PDF Digital LogicDokumen2 halamanICT2632 - ++oct+2017 - +information - PDF Digital LogicmmasalekBelum ada peringkat

- ModelSim Tutorial and Installation GuideDokumen10 halamanModelSim Tutorial and Installation Guidereach.tarunp9510Belum ada peringkat

- K-Map, POS & SOP Digital and Logic Design LabDokumen9 halamanK-Map, POS & SOP Digital and Logic Design LabsaadBelum ada peringkat

- Binary Arithmetic, 1's and 2's, 9's and 10's ComplementDokumen65 halamanBinary Arithmetic, 1's and 2's, 9's and 10's ComplementNayanjyot SinghBelum ada peringkat

- 2 To 4 DecoderDokumen6 halaman2 To 4 DecoderKrishna PremBelum ada peringkat

- Report On 4x1 MultiplexerDokumen17 halamanReport On 4x1 MultiplexerPRAVEEN KUMAWATBelum ada peringkat

- Sequential Logic Circuits ExplainedDokumen56 halamanSequential Logic Circuits ExplainedBonsa100% (1)

- Assignment 2021-22Dokumen2 halamanAssignment 2021-22Dan Ojwang100% (2)

- Unisa Digital Logic NotesDokumen8 halamanUnisa Digital Logic NotesmmasalekBelum ada peringkat

- Matlab Basics Tutorial: VectorsDokumen52 halamanMatlab Basics Tutorial: VectorsMohit Bathla MontyBelum ada peringkat

- DCLD LabDokumen42 halamanDCLD LabRachit ChauhanBelum ada peringkat

- How To Use Dev-C++Dokumen7 halamanHow To Use Dev-C++QaiserBelum ada peringkat

- Lab No. 04 ARM Assembly Programming Using Arithmetic InstructionsDokumen16 halamanLab No. 04 ARM Assembly Programming Using Arithmetic InstructionsAbdullah AbidBelum ada peringkat

- M.Tech ES ARM LABDokumen14 halamanM.Tech ES ARM LABdownloadscribdpdfBelum ada peringkat

- ADC (Analog-To-Digital Converter)Dokumen11 halamanADC (Analog-To-Digital Converter)Abdullah Muzammil0% (1)

- MDA8086 Kit ExperimentDokumen7 halamanMDA8086 Kit ExperimentAb A ZaferBelum ada peringkat

- Notes04 ADCDokumen9 halamanNotes04 ADCHosam BendaryBelum ada peringkat

- R2021 Python LabDokumen48 halamanR2021 Python LabT.Suganya Asst.Prof - CSE DeptBelum ada peringkat

- Hardware Lab-I: (CS-217) Instruction ManualDokumen36 halamanHardware Lab-I: (CS-217) Instruction Manualmaen2009Belum ada peringkat

- Decoders Explained: Types, Applications and Designing Logic CircuitsDokumen25 halamanDecoders Explained: Types, Applications and Designing Logic CircuitsmohitBelum ada peringkat

- Logic GatesDokumen25 halamanLogic Gatesxuanchai100% (1)

- Python AssignmentsDokumen2 halamanPython AssignmentsMaqsood AlamBelum ada peringkat

- Digital Flip-Flops Applications Registers CountersDokumen52 halamanDigital Flip-Flops Applications Registers CountersGeethanjali.pBelum ada peringkat

- Microprocessors & Interfacing Lab ManualDokumen30 halamanMicroprocessors & Interfacing Lab Manualjeravi84100% (1)

- DSA Codes - Hackerrank - AllDokumen141 halamanDSA Codes - Hackerrank - Alludaykiran penumakaBelum ada peringkat

- Ec - 501 - Microprocessor and Its ApplicationDokumen41 halamanEc - 501 - Microprocessor and Its ApplicationDr Nikita ShivhareBelum ada peringkat

- Lecture Notes: Digital Logic DesignDokumen66 halamanLecture Notes: Digital Logic DesignJyoti GroverBelum ada peringkat

- Flip-Flop Electronics) - Wikipedia, The Free EncyclopedDokumen16 halamanFlip-Flop Electronics) - Wikipedia, The Free EncyclopednatcutBelum ada peringkat

- Lab Manual ADE FinalDokumen39 halamanLab Manual ADE FinalNithiyaBelum ada peringkat

- Quartus Tutorial EECE 2317Dokumen12 halamanQuartus Tutorial EECE 2317Amir ZuhniBelum ada peringkat

- Up Down CounterDokumen20 halamanUp Down Countersumi36117Belum ada peringkat

- Spectrum Sensing Matlab SImulationsDokumen28 halamanSpectrum Sensing Matlab SImulationsNabeel ZahurBelum ada peringkat

- Answer 2) : Cellular RespirationDokumen2 halamanAnswer 2) : Cellular RespirationNabeel ZahurBelum ada peringkat

- SectB AnswersDokumen17 halamanSectB AnswersRyan MarvinBelum ada peringkat

- Response Paper Sample PDFDokumen4 halamanResponse Paper Sample PDFNabeel ZahurBelum ada peringkat

- India's Struggles with Human Rights Abuses and Corruption in 2012Dokumen5 halamanIndia's Struggles with Human Rights Abuses and Corruption in 2012Nabeel ZahurBelum ada peringkat

- Mc68hc908jl3/jk3e/jk1e Mc68hrc908jl3/jk3e/jk1e Mc68hlc908jl3/jk3e/jk1e Mc68hc903kl3e/kk3e Mc68hc08jl3e/jk3e Mc68hrc08jl3e/jk3eDokumen180 halamanMc68hc908jl3/jk3e/jk1e Mc68hrc908jl3/jk3e/jk1e Mc68hlc908jl3/jk3e/jk1e Mc68hc903kl3e/kk3e Mc68hc08jl3e/jk3e Mc68hrc08jl3e/jk3elogr1992Belum ada peringkat

- AcA Assignment VIDHI KISHORDokumen6 halamanAcA Assignment VIDHI KISHORVidhi KishorBelum ada peringkat

- VHDL - Practical Example - Designing An UartDokumen20 halamanVHDL - Practical Example - Designing An Uartvamshi mBelum ada peringkat

- Lecture 5Dokumen18 halamanLecture 5Shivani PatalbansiBelum ada peringkat

- Interview Questions For DFTDokumen3 halamanInterview Questions For DFTsumitzz4737100% (1)

- PIC Programmer Using ArduinoDokumen10 halamanPIC Programmer Using ArduinoganeshBelum ada peringkat

- ADC 0808 8-Bit Analog to Digital Converter GuideDokumen6 halamanADC 0808 8-Bit Analog to Digital Converter Guidesrc e-solutionsBelum ada peringkat

- This Specification Covers A Range of 2K Bit Serial EEPROM Products, The ST93C56, 56C Specified at 5V 10% and The ST93C57C Specified at 3V To 5.5V. in The Text, Products Are Referred To As ST93C56.Dokumen13 halamanThis Specification Covers A Range of 2K Bit Serial EEPROM Products, The ST93C56, 56C Specified at 5V 10% and The ST93C57C Specified at 3V To 5.5V. in The Text, Products Are Referred To As ST93C56.bylly122001Belum ada peringkat

- Cpu SpecificationDokumen31 halamanCpu SpecificationNikko FigueroaBelum ada peringkat

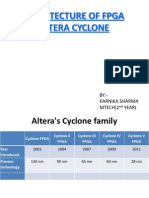

- Architecture of Fpga Altera Cyclone: BY:-Karnika Sharma Mtech (2 Year)Dokumen29 halamanArchitecture of Fpga Altera Cyclone: BY:-Karnika Sharma Mtech (2 Year)karnika143100% (1)

- Cadence OrCAD CaptureDokumen4 halamanCadence OrCAD CaptureAbdallah JamalBelum ada peringkat

- Configuration A: Unloaded BJT Transistor AmplifiersDokumen3 halamanConfiguration A: Unloaded BJT Transistor AmplifiersVincent Emmanuel SalibioBelum ada peringkat

- Logic Gates ExperimentDokumen5 halamanLogic Gates Experimentگيدوڙو ماڇيBelum ada peringkat

- VHDL - Lab SolutionDokumen33 halamanVHDL - Lab Solutionmdhuq1Belum ada peringkat

- Basic Logic Design With Verilog HDL:: Gate-Level Design On Combinational CircuitsDokumen101 halamanBasic Logic Design With Verilog HDL:: Gate-Level Design On Combinational Circuitsvenky_ladBelum ada peringkat

- Commonly Asked DFT Interview Questions (With Answers) - Indeed - Com IndiaDokumen5 halamanCommonly Asked DFT Interview Questions (With Answers) - Indeed - Com IndiaSpruha JoshiBelum ada peringkat

- Lic Project Report Vinod GroupDokumen12 halamanLic Project Report Vinod GroupPavase SumitBelum ada peringkat

- Timing DiagramDokumen15 halamanTiming DiagramKUMARASWAMY A MECBelum ada peringkat

- Current Mirror BasicsDokumen9 halamanCurrent Mirror BasicsFroilan CuevasBelum ada peringkat

- Conclusion On Boolean and DigitalDokumen1 halamanConclusion On Boolean and DigitalDweight Haward50% (2)

- VHDL Programming CourseDokumen2 halamanVHDL Programming CourseMude Kishore NaikBelum ada peringkat

- Microcode reference sheet for 16-bit machineDokumen2 halamanMicrocode reference sheet for 16-bit machineU KBelum ada peringkat

- 54LS168 Counter GuideDokumen6 halaman54LS168 Counter Guidenugroho_budiBelum ada peringkat