08r05310402 Digital Ic Applications

Diunggah oleh

andhracollegesDeskripsi Asli:

Hak Cipta

Format Tersedia

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniHak Cipta:

Format Tersedia

08r05310402 Digital Ic Applications

Diunggah oleh

andhracollegesHak Cipta:

Format Tersedia

www.andhracolleges.

com The Complete Information About Colleges in Andhra Pradesh

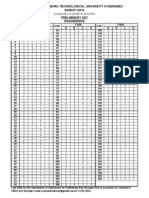

Code No: R05310402 Set No. 1

III B.Tech I Semester Supplimentary Examinations, February 2008

DIGITAL IC APPLICATIONS

( Common to Electronics & Communication Engineering and Electronics &

Instrumentation Engineering)

Time: 3 hours Max Marks: 80

Answer any FIVE Questions

All Questions carry equal marks

www.andhracolleges.com

⋆⋆⋆⋆⋆

1. (a) Explain the following terms with reference to CMOS logic.

i. Logic Levels

ii. Noise margin

iii. Power supply rails

iv. Propagation delay

(b) What is the difference between transmission time and propagation delay? Ex-

plain these two parameters with reference to CMOS logic. [8+8]

2. (a) Draw the circuit diagram of two-input 10K ECL OR gate and explain its

operation.

(b) List out different categories of characteristics in a TTL data sheet. Discuss

electrical and switching characteristics of 74LS00. [8+8]

3. (a) Discuss the steps in VHDL design flow.

(b) Explain the difference in program structure of VHDL and any other procedural

language. Give an example. [8+8]

www.andhracolleges.com

4. (a) Design a logic circuit to detect prime number of a 4-bit input? Write the

VHDL program for the same in structural style of modelling.

(b) Design the logic circuit and write a data-flow style VHDL program for the

following function? [8+8]

F (X) = ΣA,B,C,D (3, 5, 6, 7, 10, 13, 14) + d (1, 2, 4, 15)

5. Design a 3 input 5-bit multiplexer. Write the truth table and draw the logic dia-

gram. Provide the data flow VHDL program for the same. [16]

6. A simple floating-point encoder converts 16-bit fixed-point data using four high

order bits beginning with MSB. Design the logic circuit and write VHDL data-flow

program. [16]

7. (a) Design a 4-bit binary synchronous counter using 74×74. Write VHDL program

for this logic. Using data flow style.

(b) Design a modulo-60 counter using 74×163 Ics. [8+8]

8. (a) Discuss how PROM, EPROM and EEPROM technologies differ from each

other.

Seminar Topics - Scholarships - Admission/Entrance Exam Notifications

1 ofUSA-UK-Australia-Germany-France-NewZealand

2 Universities List

www.andhracolleges.com Engineering-MBA-MCA-Medical-Pharmacy-B.Ed-Law Colleges Information

www.andhracolleges.com The Complete Information About Colleges in Andhra Pradesh

Code No: R05310402 Set No. 1

(b) With the help of timing waveforms, explain read and write operations of

SRAM. [8+8]

⋆⋆⋆⋆⋆

www.andhracolleges.com

www.andhracolleges.com

Seminar Topics - Scholarships - Admission/Entrance Exam Notifications

2 ofUSA-UK-Australia-Germany-France-NewZealand

2 Universities List

www.andhracolleges.com Engineering-MBA-MCA-Medical-Pharmacy-B.Ed-Law Colleges Information

www.andhracolleges.com The Complete Information About Colleges in Andhra Pradesh

Code No: R05310402 Set No. 2

III B.Tech I Semester Supplimentary Examinations, February 2008

DIGITAL IC APPLICATIONS

( Common to Electronics & Communication Engineering and Electronics &

Instrumentation Engineering)

Time: 3 hours Max Marks: 80

Answer any FIVE Questions

All Questions carry equal marks

www.andhracolleges.com

⋆⋆⋆⋆⋆

1. (a) Explain the following terms with reference to CMOS logic.

i. Logic Levels

ii. Noise margin

iii. Power supply rails

iv. Propagation delay

(b) What is the difference between transmission time and propagation delay? Ex-

plain these two parameters with reference to CMOS logic. [8+8]

2. (a) Mention the DC noise margin levels of ECL 10K family.

(b) A single pull-up resistor to +5V is used to provide a constant-1 logic source

to 15 different 74LS00 inputs. What is the maximum value of this resistor?

How much high state DC noise margin can be provided in this case? [6+10]

3. (a) Write a VHDL Entity and Architecture for the following function?

F(x) = a ⊕ b ⊕ c

www.andhracolleges.com

Also draw the relevant logic diagram.

(b) Explain the use of Packages Give the syntax and structure of a package in

VHDL [8+8]

4. Design the logic circuit and write a data-flow style VHDL program for the following

functions?

(a) F (A) = Πp,q,r,s (1, 3, 4, 5, 6, 7, 9, 12, 13, 14)

(b) F (X) = ΣA,B,C,D (3, 5, 6, 7, 13) + d (1, 2, 4, 12, 15) [8+8]

5. (a) Design a 32 to 1 multiplexer using four 74×151 multiplexers and 74X139

decoder.

(b) Realize the following expression using 74×151 IC [8+8]

f (Y ) = AB + BC + AC

6. Write VHDL program for 8-bit comparator circuit. Using this entity write VHDL

program for 24-bit comparator. Show the additional logic used for this purpose use

structural style or modeling. [16]

Seminar Topics - Scholarships - Admission/Entrance Exam Notifications

1 ofUSA-UK-Australia-Germany-France-NewZealand

2 Universities List

www.andhracolleges.com Engineering-MBA-MCA-Medical-Pharmacy-B.Ed-Law Colleges Information

www.andhracolleges.com The Complete Information About Colleges in Andhra Pradesh

Code No: R05310402 Set No. 2

7. (a) Design a modulo-8 binary counter and decoder with glitch-free outputs. Ex-

plain the operation.

(b) Design a modulo-100 counter using two 74X163 binary counters. [8+8]

8. (a) Explain the necessity of two-dimensional decoding mechanism in memories.

Draw MOS transistor memory cell in ROM and explain the operation.

(b) Design an 8×8 diode ROM using 74×138 for the following data starting from

www.andhracolleges.com

the first location. [8+8]

11, 22, 33, F F, DD, CC, 01, 7E

⋆⋆⋆⋆⋆

www.andhracolleges.com

Seminar Topics - Scholarships - Admission/Entrance Exam Notifications

2 ofUSA-UK-Australia-Germany-France-NewZealand

2 Universities List

www.andhracolleges.com Engineering-MBA-MCA-Medical-Pharmacy-B.Ed-Law Colleges Information

www.andhracolleges.com The Complete Information About Colleges in Andhra Pradesh

Code No: R05310402 Set No. 3

III B.Tech I Semester Supplimentary Examinations, February 2008

DIGITAL IC APPLICATIONS

( Common to Electronics & Communication Engineering and Electronics &

Instrumentation Engineering)

Time: 3 hours Max Marks: 80

Answer any FIVE Questions

All Questions carry equal marks

www.andhracolleges.com

⋆⋆⋆⋆⋆

1. (a) Design CMOS transistor circuit for 2-input AND gate. Explain the circuit

with the help of function table?

(b) Draw the resistive model of a CMOS inverter circuit and explain its behavior

for LOW and HIGH outputs. [8+8]

2. (a) Design a three input NAND gate using diode logic and a transistor inverter?

Analyze the circuit with the help of transfer characteristics.

(b) Explain sinking current and sourcing current of TTL output? Which of the

parameters decide the fan-out and how? [8+8]

3. (a) Write a VHDL Entity and Architecture for the following function?

F(x) = a ⊕ b ⊕ c

Also draw the relevant logic diagram.

(b) Explain the use of Packages Give the syntax and structure of a package in

VHDL [8+8]

www.andhracolleges.com

4. (a) Explain data-flow design elements of VHDL.

(b) Write a Behavioral style VHDL program for the following functions. [8+8]

F(S) = A ⊕ B ⊕ C1

F(CO ) = AB + AC1 + BC1

5. (a) Design a 32 to 1 multiplexer using four 74×151 multiplexers and 74X139

decoder.

(b) Realize the following expression using 74×151 IC [8+8]

f (Y ) = AB + BC + AC

6. Write VHDL program for 1-bit comparator circuit with the input bits and equal,

grater than and less than inputs from the previous stage and the outputs contain

equal, greater than and less than conditions. Using this entity write VHDL program

for 16-bit comparator using data flow style. Do not use any additional logic for this

purpose. [16]

7. (a) Design a switch debouncer circuit using 74×109 IC. Explain the operation

using timing diagram.

Seminar Topics - Scholarships - Admission/Entrance Exam Notifications

1 ofUSA-UK-Australia-Germany-France-NewZealand

2 Universities List

www.andhracolleges.com Engineering-MBA-MCA-Medical-Pharmacy-B.Ed-Law Colleges Information

www.andhracolleges.com The Complete Information About Colleges in Andhra Pradesh

Code No: R05310402 Set No. 3

(b) Discuss the logic circuit of 74×377 register. Write a VHDL program for the

same in structural style. [8+8]

8. (a) Realize the logic function performed by 74×381 with ROM.

(b) How many ROM bits are required to build a 16-bit adder/subtractor with

mode control, carry input, carry output and two’s complement overflow out-

put. Show the block schematic with all inputs and outputs. [8+8]

www.andhracolleges.com ⋆⋆⋆⋆⋆

www.andhracolleges.com

Seminar Topics - Scholarships - Admission/Entrance Exam Notifications

2 ofUSA-UK-Australia-Germany-France-NewZealand

2 Universities List

www.andhracolleges.com Engineering-MBA-MCA-Medical-Pharmacy-B.Ed-Law Colleges Information

www.andhracolleges.com The Complete Information About Colleges in Andhra Pradesh

Code No: R05310402 Set No. 4

III B.Tech I Semester Supplimentary Examinations, February 2008

DIGITAL IC APPLICATIONS

( Common to Electronics & Communication Engineering and Electronics &

Instrumentation Engineering)

Time: 3 hours Max Marks: 80

Answer any FIVE Questions

All Questions carry equal marks

www.andhracolleges.com

⋆⋆⋆⋆⋆

1. (a) Explain how to estimate sinking current for low output and sourcing current

for high output of CMOS gate.

(b) Analyze the fall time of CMOS inverter output with RL = 100Ω, VL = 2.5V and CL =

10P F . Assume VL as stable state voltage. [8+8]

2. (a) Design a TTL three-state NAND gate and explain the operation with the help

of function table.

(b) Explain the following terms with reference to TTL gate.

i. Voltage levels for logic ‘1’ & logic ‘0’

ii. DC Noise margin

iii. Low-state unit load

iv. High-state fan-out [8+8]

3. (a) Write a VHDL Entity and Architecture for a 3-bit synchronous counter using

Flip-Flops.

(b) Explain the use of Packages. Give the syntax and structure of a package in

www.andhracolleges.com

VHDL. [8+8]

4. (a) Explain structural design elements of VHDL.

(b) Design the logic circuit and write a data-flow style VHDL program for the

following function. [8+8]

F (R) = ΠA,B,C,D (1, 4, 5, 7, 9, 13, 15)

5. (a) Using two 74×138 decoders design a 4 to 16 decoder?

(b) Realize the following expression using 74×151 IC? [16]

f (X) = ABC + ABC + ABC

6. (a) Design a 16-bit comparator using 74×85 ICs.

(b) Write a behavioral VHDL program to compare 16-bit signed and unsigned

integers . [16]

7. (a) Draw the logic diagram of 74×163 binary counter and explain its operation.

(b) Design a modulo-100 counter using two 74×163 binary counters? [8+8]

Seminar Topics - Scholarships - Admission/Entrance Exam Notifications

1 ofUSA-UK-Australia-Germany-France-NewZealand

2 Universities List

www.andhracolleges.com Engineering-MBA-MCA-Medical-Pharmacy-B.Ed-Law Colleges Information

www.andhracolleges.com The Complete Information About Colleges in Andhra Pradesh

Code No: R05310402 Set No. 4

8. (a) Explain the internal structure of 64K×1 DRAM. With the help of timing

waveforms discuss DRAM access.

(b) Explain the necessity of two-dimensional decoding mechanism in memories.

Draw MOS transistor memory cell in ROM and explain the operation. [8+8]

⋆⋆⋆⋆⋆

www.andhracolleges.com

www.andhracolleges.com

Seminar Topics - Scholarships - Admission/Entrance Exam Notifications

2 ofUSA-UK-Australia-Germany-France-NewZealand

2 Universities List

www.andhracolleges.com Engineering-MBA-MCA-Medical-Pharmacy-B.Ed-Law Colleges Information

Anda mungkin juga menyukai

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeDari EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifePenilaian: 4 dari 5 bintang4/5 (5794)

- The Little Book of Hygge: Danish Secrets to Happy LivingDari EverandThe Little Book of Hygge: Danish Secrets to Happy LivingPenilaian: 3.5 dari 5 bintang3.5/5 (399)

- Eamcet Agriculture Last Ranks Cutoffs Andhracolleges Eamcet 2013 CutoffsDokumen3 halamanEamcet Agriculture Last Ranks Cutoffs Andhracolleges Eamcet 2013 Cutoffsandhracolleges33% (3)

- Polycet2014 Web Counselling NotificationDokumen2 halamanPolycet2014 Web Counselling NotificationandhracollegesBelum ada peringkat

- JEE Advanced 2014 Paper I PHYSICS Paper Answer SolutionsDokumen6 halamanJEE Advanced 2014 Paper I PHYSICS Paper Answer SolutionsandhracollegesBelum ada peringkat

- Eamcet 2014 Engineering Jntu Preliminary Key AndhracollegesDokumen1 halamanEamcet 2014 Engineering Jntu Preliminary Key AndhracollegesandhracollegesBelum ada peringkat

- ICET 2014 Preliminary Key Primary Key AndhracollegesDokumen2 halamanICET 2014 Preliminary Key Primary Key AndhracollegesandhracollegesBelum ada peringkat

- Eamcet 2014 Engineering Key Solutions AndhracollegesDokumen42 halamanEamcet 2014 Engineering Key Solutions Andhracollegesandhracolleges75% (8)

- JEE Main Advanced 2014 Paper I Maths Paper Answer SolutionsDokumen4 halamanJEE Main Advanced 2014 Paper I Maths Paper Answer Solutionsandhracolleges100% (1)

- Polycet 2014 ST Certificatates Verification DatesDokumen1 halamanPolycet 2014 ST Certificatates Verification DatesandhracollegesBelum ada peringkat

- Polycet 2014 SC BC Oc Certificatates Verification DatesDokumen1 halamanPolycet 2014 SC BC Oc Certificatates Verification DatesandhracollegesBelum ada peringkat

- JEE Main Advanced Paper I Answer Key 25 May 2014Dokumen1 halamanJEE Main Advanced Paper I Answer Key 25 May 2014andhracollegesBelum ada peringkat

- EAMCET 2014 Agriculture & Medical Preliminary Answer KeysDokumen1 halamanEAMCET 2014 Agriculture & Medical Preliminary Answer KeysLohith_EnggBelum ada peringkat

- JEE Advanced 2014 Paper I Chemistry Paper Answer SolutionsDokumen4 halamanJEE Advanced 2014 Paper I Chemistry Paper Answer SolutionsandhracollegesBelum ada peringkat

- Eamcet 2014 Medical Question Paper AndhracollegesDokumen62 halamanEamcet 2014 Medical Question Paper Andhracollegesandhracolleges100% (1)

- Eamcet 2014 Medical Question Paper With Key Solutions AndhracollegesDokumen62 halamanEamcet 2014 Medical Question Paper With Key Solutions Andhracollegesandhracolleges100% (1)

- Polycet 2014 Question PaperDokumen24 halamanPolycet 2014 Question PaperandhracollegesBelum ada peringkat

- Andhracollege Eamcet 2014 Engineering Question Paper With Key SolutionsDokumen62 halamanAndhracollege Eamcet 2014 Engineering Question Paper With Key Solutionsandhracolleges50% (4)

- Eamcet 2012 Engineering Paper KeyDokumen1 halamanEamcet 2012 Engineering Paper KeyandhracollegesBelum ada peringkat

- Eamcet 2014 Engineering Key SolutionsDokumen42 halamanEamcet 2014 Engineering Key Solutionsandhracolleges100% (1)

- Eamcet 2013 Engineering PaperDokumen62 halamanEamcet 2013 Engineering Paperandhracolleges0% (1)

- Eamcet 2012 Medical Paper KeyDokumen1 halamanEamcet 2012 Medical Paper KeyandhracollegesBelum ada peringkat

- Eamcet 2011 Engineering PaperDokumen61 halamanEamcet 2011 Engineering PaperandhracollegesBelum ada peringkat

- Eamcet 2012 Medical PaperDokumen60 halamanEamcet 2012 Medical Paperandhracolleges100% (1)

- Eamcet 2009 Engineering Chemistry PaperDokumen16 halamanEamcet 2009 Engineering Chemistry PaperandhracollegesBelum ada peringkat

- Eamcet 2012 Engineering Paper KeyDokumen1 halamanEamcet 2012 Engineering Paper KeyandhracollegesBelum ada peringkat

- Eamcet 2010 Medical PaperDokumen63 halamanEamcet 2010 Medical PaperandhracollegesBelum ada peringkat

- Eamcet 2006 Engineering PaperDokumen14 halamanEamcet 2006 Engineering PaperandhracollegesBelum ada peringkat

- Eamcet 2012 Engineering PaperDokumen62 halamanEamcet 2012 Engineering Paperandhracolleges100% (1)

- Eamcet 2013 Medical PaperDokumen62 halamanEamcet 2013 Medical PaperandhracollegesBelum ada peringkat

- Eamcet 2008 Engineering PaperDokumen62 halamanEamcet 2008 Engineering PaperandhracollegesBelum ada peringkat

- Eamcet 2007 Engineering PaperDokumen13 halamanEamcet 2007 Engineering Paperandhracolleges100% (1)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryDari EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryPenilaian: 3.5 dari 5 bintang3.5/5 (231)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceDari EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RacePenilaian: 4 dari 5 bintang4/5 (894)

- The Yellow House: A Memoir (2019 National Book Award Winner)Dari EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Penilaian: 4 dari 5 bintang4/5 (98)

- Shoe Dog: A Memoir by the Creator of NikeDari EverandShoe Dog: A Memoir by the Creator of NikePenilaian: 4.5 dari 5 bintang4.5/5 (537)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureDari EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FuturePenilaian: 4.5 dari 5 bintang4.5/5 (474)

- Never Split the Difference: Negotiating As If Your Life Depended On ItDari EverandNever Split the Difference: Negotiating As If Your Life Depended On ItPenilaian: 4.5 dari 5 bintang4.5/5 (838)

- Grit: The Power of Passion and PerseveranceDari EverandGrit: The Power of Passion and PerseverancePenilaian: 4 dari 5 bintang4/5 (587)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaDari EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaPenilaian: 4.5 dari 5 bintang4.5/5 (265)

- The Emperor of All Maladies: A Biography of CancerDari EverandThe Emperor of All Maladies: A Biography of CancerPenilaian: 4.5 dari 5 bintang4.5/5 (271)

- On Fire: The (Burning) Case for a Green New DealDari EverandOn Fire: The (Burning) Case for a Green New DealPenilaian: 4 dari 5 bintang4/5 (73)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersDari EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersPenilaian: 4.5 dari 5 bintang4.5/5 (344)

- Team of Rivals: The Political Genius of Abraham LincolnDari EverandTeam of Rivals: The Political Genius of Abraham LincolnPenilaian: 4.5 dari 5 bintang4.5/5 (234)

- Rise of ISIS: A Threat We Can't IgnoreDari EverandRise of ISIS: A Threat We Can't IgnorePenilaian: 3.5 dari 5 bintang3.5/5 (137)

- The Unwinding: An Inner History of the New AmericaDari EverandThe Unwinding: An Inner History of the New AmericaPenilaian: 4 dari 5 bintang4/5 (45)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyDari EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyPenilaian: 3.5 dari 5 bintang3.5/5 (2219)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreDari EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You ArePenilaian: 4 dari 5 bintang4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Dari EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Penilaian: 4.5 dari 5 bintang4.5/5 (119)

- Her Body and Other Parties: StoriesDari EverandHer Body and Other Parties: StoriesPenilaian: 4 dari 5 bintang4/5 (821)

- SSS Format DescriptionDokumen5 halamanSSS Format Descriptionmartinos22Belum ada peringkat

- GUIDDokumen215 halamanGUIDPrakashBelum ada peringkat

- ISO 27001-2022 Transition BookDokumen20 halamanISO 27001-2022 Transition BookzghibBelum ada peringkat

- Ccna MCQ 1 PDFDokumen14 halamanCcna MCQ 1 PDFsreesree.b100% (1)

- Incentive Week 23-24Dokumen12 halamanIncentive Week 23-24Pratiksha KumariBelum ada peringkat

- Curve Weighting: Effects of High - End Non - LinearityDokumen3 halamanCurve Weighting: Effects of High - End Non - LinearityhF2hFhiddenFaceBelum ada peringkat

- LivewireDokumen186 halamanLivewireBlessing Tendai ChisuwaBelum ada peringkat

- Gen. Math - Quarter 1 Exam (11-HUMS-ALS)Dokumen3 halamanGen. Math - Quarter 1 Exam (11-HUMS-ALS)JerryBelum ada peringkat

- Alzheimers Assistant PDFDokumen34 halamanAlzheimers Assistant PDFabhirami manikandanBelum ada peringkat

- Bi Weekly Budget TrackerDokumen22 halamanBi Weekly Budget TrackeranamarieBelum ada peringkat

- EWFC 1000: "Quick-Chill and Hold" Cold ControlDokumen5 halamanEWFC 1000: "Quick-Chill and Hold" Cold ControlGede KusumaBelum ada peringkat

- Oracle Financial FaqDokumen259 halamanOracle Financial FaqAndrea NguyenBelum ada peringkat

- Fertilizer Information System For Banana PlantatioDokumen5 halamanFertilizer Information System For Banana PlantatioHazem EmadBelum ada peringkat

- Ssp393 - Audi A5 - Convenience Electronics and Driver Assist SystemsDokumen56 halamanSsp393 - Audi A5 - Convenience Electronics and Driver Assist SystemsCyberemuleBelum ada peringkat

- GTX 3X5 Transponder TSO Installation Manual: 190-01499-02 August 2020 Revision 16Dokumen248 halamanGTX 3X5 Transponder TSO Installation Manual: 190-01499-02 August 2020 Revision 16Василий ПавленкоBelum ada peringkat

- Validation Board TemplateDokumen1 halamanValidation Board Templategvs_2000Belum ada peringkat

- 3 Process Fundamentals Chapter 2 and 3Dokumen74 halaman3 Process Fundamentals Chapter 2 and 3Terry Conrad KingBelum ada peringkat

- Python - What Does Turtle - Tracer Do - Stack OverflowDokumen2 halamanPython - What Does Turtle - Tracer Do - Stack OverflowKassoum KobréBelum ada peringkat

- Chapter 2 - Operational AmplifierDokumen31 halamanChapter 2 - Operational AmplifierElie AyoubBelum ada peringkat

- GSM WorkflowDokumen1 halamanGSM WorkflowFaisal CoolBelum ada peringkat

- 9 Android List and MapsDokumen13 halaman9 Android List and MapsMarichris VenturaBelum ada peringkat

- Q4M2 Giving Technical and Operational Def.2.0Dokumen60 halamanQ4M2 Giving Technical and Operational Def.2.0Shadow Gaming YTBelum ada peringkat

- IGL 7.0.2 Installation GuideDokumen216 halamanIGL 7.0.2 Installation GuideMohammad ImranBelum ada peringkat

- PDFlib TutorialDokumen258 halamanPDFlib TutorialGasBelum ada peringkat

- 2.tekla Structures 2016i Administrator's Release NotesDokumen48 halaman2.tekla Structures 2016i Administrator's Release NotesomerumeromerBelum ada peringkat

- Maintenance Manual: MANUAL NUMBER 006-15545-0002 REVISION 2, December, 1999Dokumen181 halamanMaintenance Manual: MANUAL NUMBER 006-15545-0002 REVISION 2, December, 1999AndrewBelum ada peringkat

- Marrow E4 FMT 2Dokumen151 halamanMarrow E4 FMT 2Cherry KolaBelum ada peringkat

- Super Star Trek CompendiumDokumen256 halamanSuper Star Trek CompendiumAdiM67100% (1)

- Marantz SR 4000 User GuideDokumen30 halamanMarantz SR 4000 User Guidekeerthipinnawala6498100% (1)

- Guidline Nurse Education TodayDokumen15 halamanGuidline Nurse Education TodayaminBelum ada peringkat