Srr320405 Vlsi Design

Diunggah oleh

andhracollegesDeskripsi Asli:

Hak Cipta

Format Tersedia

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniHak Cipta:

Format Tersedia

Srr320405 Vlsi Design

Diunggah oleh

andhracollegesHak Cipta:

Format Tersedia

www.andhracolleges.

com The Complete Information About Colleges in Andhra Pradesh

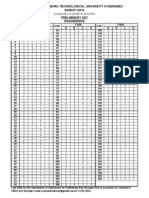

Code No: RR320405 Set No. 1

III B.Tech II Semester Supplimentary Examinations, Aug/Sep 2007

VLSI DESIGN

( Common to Electronics & Communication Engineering and Electronics &

Telematics)

Time: 3 hours Max Marks: 80

Answer any FIVE Questions

All Questions carry equal marks

www.andhracolleges.com

⋆⋆⋆⋆⋆

1. (a) Define threshold voltage of a MOS device and explain its significance.

(b) Explain the effect of threshold voltage on MOSFET current Equations. [8+8]

2. With neat sketches explain how Diodes and Resistors are fabricated in Bipolar

process. [16]

3. Design a stick diagram for n-MOS Ex-OR gate. [16]

4. Design a layout diagram for CMOS inverter. [16]

5. Derive an equation for the propagation delay from input to output of the pass

transistor chain shown in Figure 5. [16]

Figure 5

www.andhracolleges.com

6. Using PLA Implement JK Flip flop circuit.

7. With respect to synthesis process explain the following terms.

(a) Flattening

(b) Factoring.

(c) Mapping.

8. Explain about the following packaging design considerations.

[16]

[6+5+5]

(a) Electrical considerations.

(b) Mechanical design consideration. [8+8]

⋆⋆⋆⋆⋆

Seminar Topics - Scholarships - Admission/Entrance Exam Notifications

1 ofUSA-UK-Australia-Germany-France-NewZealand

1 Universities List

www.andhracolleges.com Engineering-MBA-MCA-Medical-Pharmacy-B.Ed-Law Colleges Information

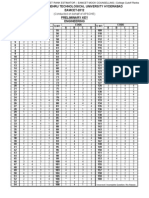

www.andhracolleges.com The Complete Information About Colleges in Andhra Pradesh

Code No: RR320405 Set No. 2

III B.Tech II Semester Supplimentary Examinations, Aug/Sep 2007

VLSI DESIGN

( Common to Electronics & Communication Engineering and Electronics &

Telematics)

Time: 3 hours Max Marks: 80

Answer any FIVE Questions

All Questions carry equal marks

www.andhracolleges.com

⋆⋆⋆⋆⋆

1. (a) With neat sketches explain the drain characteristics of an n-channel enhance-

ment MOSFET.

(b) n-MOS Transistor is operated in the Active region with the following parame-

ters VGS = 3.9V ; Vtn = 1V ; W/L = 100; µnCox = 90 µA/V 2

Find its drain current and drain source resistance. [8+8]

2. With neat sketches explain how Diodes and Resistors are fabricated in Bipolar

process. [16]

3. Design a stick diagram for the NMOS logic shown below Y = (A + B + C) [16]

4. Design a layout diagram for two input nMOS NAND gate. [16]

5. Calculate on resistance of the circuit shown in Figure 5 from VDD to GND. If n-

channel sheet resistance Rsn = 10 4 Ω per square and p-channel sheet resistance

Rsp = 2.5 × 104 Ω per square. [16]

www.andhracolleges.com Figure 5

6. (a) What are the advantages and disadvantages of the reconfiguration.

(b) Mention different advantages of Anti fuse Technology. [8+8]

7. Clearly explain each step of high level design flow of an ASIC. [16]

8. (a) Clearly explain the diffusion process in IC fabrication.

(b) Clearly explain various diffusion effects in silicon with emphasis on VLSI ap-

plication. [8+8]

Seminar Topics - Scholarships - Admission/Entrance Exam Notifications

1 ofUSA-UK-Australia-Germany-France-NewZealand

2 Universities List

www.andhracolleges.com Engineering-MBA-MCA-Medical-Pharmacy-B.Ed-Law Colleges Information

www.andhracolleges.com The Complete Information About Colleges in Andhra Pradesh

Code No: RR320405 Set No. 2

⋆⋆⋆⋆⋆

www.andhracolleges.com

www.andhracolleges.com

Seminar Topics - Scholarships - Admission/Entrance Exam Notifications

2 ofUSA-UK-Australia-Germany-France-NewZealand

2 Universities List

www.andhracolleges.com Engineering-MBA-MCA-Medical-Pharmacy-B.Ed-Law Colleges Information

www.andhracolleges.com The Complete Information About Colleges in Andhra Pradesh

Code No: RR320405 Set No. 3

III B.Tech II Semester Supplimentary Examinations, Aug/Sep 2007

VLSI DESIGN

( Common to Electronics & Communication Engineering and Electronics &

Telematics)

Time: 3 hours Max Marks: 80

Answer any FIVE Questions

All Questions carry equal marks

www.andhracolleges.com

⋆⋆⋆⋆⋆

1. (a) Derive an equation for IDS of an n-channel Enhancement MOSFET operating

in Saturation region.

(b) An nMOS transistor is operating in saturation region with the following pa-

rameters. VGS = 5V ; Vtn = 1.2V ; W/L = 110; µnCox = 110 µA/V 2 .

Find Transconductance of the device. [8+8]

2. (a) With neat sketches explain CMOS fabrication using n-well process.

(b) Explain how capacitors are fabricated in CMOS process. [10+6]

3. Design a stick diagram for the CMOS logic shown below Y = (A + B + C) [16]

4. Explain with suitable examples how design the layout of a gate to maximize per-

formance and minimize area. [16]

5. Derive an equation for the propagation delay from input to output of the pass

transistor chain shown in Figure 5. [16]

www.andhracolleges.com Figure 5

6. (a) What are the advantages and disadvantages of the reconfiguration.

(b) Mention different advantages of Anti fuse Technology.

7. Clearly explain each step of high level design flow of an ASIC.

8. With neat sketches explain the oxidation process in the IC fabrication process.

[8+8]

[16]

[16]

⋆⋆⋆⋆⋆

Seminar Topics - Scholarships - Admission/Entrance Exam Notifications

1 ofUSA-UK-Australia-Germany-France-NewZealand

1 Universities List

www.andhracolleges.com Engineering-MBA-MCA-Medical-Pharmacy-B.Ed-Law Colleges Information

www.andhracolleges.com The Complete Information About Colleges in Andhra Pradesh

Code No: RR320405 Set No. 4

III B.Tech II Semester Supplimentary Examinations, Aug/Sep 2007

VLSI DESIGN

( Common to Electronics & Communication Engineering and Electronics &

Telematics)

Time: 3 hours Max Marks: 80

Answer any FIVE Questions

All Questions carry equal marks

www.andhracolleges.com

⋆⋆⋆⋆⋆

1. (a) Define threshold voltage of a MOS device and explain its significance.

(b) Explain the effect of threshold voltage on MOSFET current Equations. [8+8]

2. (a) With neat sketches explain how resistors and capacitors are fabricated in p-

well process.

(b) With neat sketches explain how resistors and capacitors are fabricated in n-

well process. [8+8]

3. What is a stick diagram and explain about different symbols used for components

in stick diagram. [16]

4. Design a layout diagram for CMOS inverter. [16]

5. Calculate ON resistance from VDD to GND for the given inverter circuit shown in

Figure 5, If n-channel sheet resistance is 104 Ω per square. [16]

www.andhracolleges.com

Figure 5

6. (a) What are the advantages and disadvantages of the reconfiguration.

(b) Mention different advantages of Anti fuse Technology. [8+8]

7. Explain the following process in the ASIC design flow.

(a) Functional gate level verification.

(b) Static timing analysis. [8+8]

Seminar Topics - Scholarships - Admission/Entrance Exam Notifications

1 ofUSA-UK-Australia-Germany-France-NewZealand

2 Universities List

www.andhracolleges.com Engineering-MBA-MCA-Medical-Pharmacy-B.Ed-Law Colleges Information

www.andhracolleges.com The Complete Information About Colleges in Andhra Pradesh

Code No: RR320405 Set No. 4

8. (a) Mention the properties of the twin oxide.

(b) Clearly explain about ION implantation step in IC fabrication. [6+10]

⋆⋆⋆⋆⋆

www.andhracolleges.com

www.andhracolleges.com

Seminar Topics - Scholarships - Admission/Entrance Exam Notifications

2 ofUSA-UK-Australia-Germany-France-NewZealand

2 Universities List

www.andhracolleges.com Engineering-MBA-MCA-Medical-Pharmacy-B.Ed-Law Colleges Information

Anda mungkin juga menyukai

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeDari EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifePenilaian: 4 dari 5 bintang4/5 (5794)

- Eamcet Agriculture Last Ranks Cutoffs Andhracolleges Eamcet 2013 CutoffsDokumen3 halamanEamcet Agriculture Last Ranks Cutoffs Andhracolleges Eamcet 2013 Cutoffsandhracolleges33% (3)

- The Little Book of Hygge: Danish Secrets to Happy LivingDari EverandThe Little Book of Hygge: Danish Secrets to Happy LivingPenilaian: 3.5 dari 5 bintang3.5/5 (399)

- Polycet2014 Web Counselling NotificationDokumen2 halamanPolycet2014 Web Counselling NotificationandhracollegesBelum ada peringkat

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryDari EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryPenilaian: 3.5 dari 5 bintang3.5/5 (231)

- JEE Advanced 2014 Paper I PHYSICS Paper Answer SolutionsDokumen6 halamanJEE Advanced 2014 Paper I PHYSICS Paper Answer SolutionsandhracollegesBelum ada peringkat

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceDari EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RacePenilaian: 4 dari 5 bintang4/5 (894)

- Eamcet 2014 Engineering Jntu Preliminary Key AndhracollegesDokumen1 halamanEamcet 2014 Engineering Jntu Preliminary Key AndhracollegesandhracollegesBelum ada peringkat

- The Yellow House: A Memoir (2019 National Book Award Winner)Dari EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Penilaian: 4 dari 5 bintang4/5 (98)

- ICET 2014 Preliminary Key Primary Key AndhracollegesDokumen2 halamanICET 2014 Preliminary Key Primary Key AndhracollegesandhracollegesBelum ada peringkat

- Shoe Dog: A Memoir by the Creator of NikeDari EverandShoe Dog: A Memoir by the Creator of NikePenilaian: 4.5 dari 5 bintang4.5/5 (537)

- Eamcet 2014 Engineering Key Solutions AndhracollegesDokumen42 halamanEamcet 2014 Engineering Key Solutions Andhracollegesandhracolleges75% (8)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureDari EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FuturePenilaian: 4.5 dari 5 bintang4.5/5 (474)

- JEE Main Advanced 2014 Paper I Maths Paper Answer SolutionsDokumen4 halamanJEE Main Advanced 2014 Paper I Maths Paper Answer Solutionsandhracolleges100% (1)

- Never Split the Difference: Negotiating As If Your Life Depended On ItDari EverandNever Split the Difference: Negotiating As If Your Life Depended On ItPenilaian: 4.5 dari 5 bintang4.5/5 (838)

- Polycet 2014 ST Certificatates Verification DatesDokumen1 halamanPolycet 2014 ST Certificatates Verification DatesandhracollegesBelum ada peringkat

- Grit: The Power of Passion and PerseveranceDari EverandGrit: The Power of Passion and PerseverancePenilaian: 4 dari 5 bintang4/5 (587)

- Polycet 2014 SC BC Oc Certificatates Verification DatesDokumen1 halamanPolycet 2014 SC BC Oc Certificatates Verification DatesandhracollegesBelum ada peringkat

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaDari EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaPenilaian: 4.5 dari 5 bintang4.5/5 (265)

- JEE Main Advanced Paper I Answer Key 25 May 2014Dokumen1 halamanJEE Main Advanced Paper I Answer Key 25 May 2014andhracollegesBelum ada peringkat

- EAMCET 2014 Agriculture & Medical Preliminary Answer KeysDokumen1 halamanEAMCET 2014 Agriculture & Medical Preliminary Answer KeysLohith_EnggBelum ada peringkat

- JEE Advanced 2014 Paper I Chemistry Paper Answer SolutionsDokumen4 halamanJEE Advanced 2014 Paper I Chemistry Paper Answer SolutionsandhracollegesBelum ada peringkat

- The Emperor of All Maladies: A Biography of CancerDari EverandThe Emperor of All Maladies: A Biography of CancerPenilaian: 4.5 dari 5 bintang4.5/5 (271)

- Eamcet 2014 Medical Question Paper AndhracollegesDokumen62 halamanEamcet 2014 Medical Question Paper Andhracollegesandhracolleges100% (1)

- On Fire: The (Burning) Case for a Green New DealDari EverandOn Fire: The (Burning) Case for a Green New DealPenilaian: 4 dari 5 bintang4/5 (73)

- Eamcet 2014 Medical Question Paper With Key Solutions AndhracollegesDokumen62 halamanEamcet 2014 Medical Question Paper With Key Solutions Andhracollegesandhracolleges100% (1)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersDari EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersPenilaian: 4.5 dari 5 bintang4.5/5 (344)

- Polycet 2014 Question PaperDokumen24 halamanPolycet 2014 Question PaperandhracollegesBelum ada peringkat

- Team of Rivals: The Political Genius of Abraham LincolnDari EverandTeam of Rivals: The Political Genius of Abraham LincolnPenilaian: 4.5 dari 5 bintang4.5/5 (234)

- Andhracollege Eamcet 2014 Engineering Question Paper With Key SolutionsDokumen62 halamanAndhracollege Eamcet 2014 Engineering Question Paper With Key Solutionsandhracolleges50% (4)

- Eamcet 2012 Engineering Paper KeyDokumen1 halamanEamcet 2012 Engineering Paper KeyandhracollegesBelum ada peringkat

- Eamcet 2014 Engineering Key SolutionsDokumen42 halamanEamcet 2014 Engineering Key Solutionsandhracolleges100% (1)

- Rise of ISIS: A Threat We Can't IgnoreDari EverandRise of ISIS: A Threat We Can't IgnorePenilaian: 3.5 dari 5 bintang3.5/5 (137)

- Eamcet 2013 Engineering PaperDokumen62 halamanEamcet 2013 Engineering Paperandhracolleges0% (1)

- Eamcet 2012 Medical Paper KeyDokumen1 halamanEamcet 2012 Medical Paper KeyandhracollegesBelum ada peringkat

- The Unwinding: An Inner History of the New AmericaDari EverandThe Unwinding: An Inner History of the New AmericaPenilaian: 4 dari 5 bintang4/5 (45)

- Eamcet 2011 Engineering PaperDokumen61 halamanEamcet 2011 Engineering PaperandhracollegesBelum ada peringkat

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyDari EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyPenilaian: 3.5 dari 5 bintang3.5/5 (2219)

- Eamcet 2012 Medical PaperDokumen60 halamanEamcet 2012 Medical Paperandhracolleges100% (1)

- Eamcet 2009 Engineering Chemistry PaperDokumen16 halamanEamcet 2009 Engineering Chemistry PaperandhracollegesBelum ada peringkat

- Eamcet 2012 Engineering Paper KeyDokumen1 halamanEamcet 2012 Engineering Paper KeyandhracollegesBelum ada peringkat

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreDari EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You ArePenilaian: 4 dari 5 bintang4/5 (1090)

- Eamcet 2010 Medical PaperDokumen63 halamanEamcet 2010 Medical PaperandhracollegesBelum ada peringkat

- Eamcet 2006 Engineering PaperDokumen14 halamanEamcet 2006 Engineering PaperandhracollegesBelum ada peringkat

- Eamcet 2012 Engineering PaperDokumen62 halamanEamcet 2012 Engineering Paperandhracolleges100% (1)

- Eamcet 2013 Medical PaperDokumen62 halamanEamcet 2013 Medical PaperandhracollegesBelum ada peringkat

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Dari EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Penilaian: 4.5 dari 5 bintang4.5/5 (119)

- Eamcet 2008 Engineering PaperDokumen62 halamanEamcet 2008 Engineering PaperandhracollegesBelum ada peringkat

- Eamcet 2007 Engineering PaperDokumen13 halamanEamcet 2007 Engineering Paperandhracolleges100% (1)

- Lab # 8 SolvedDokumen10 halamanLab # 8 SolvedZabeehullahmiakhailBelum ada peringkat

- Ghprobe ManualDokumen99 halamanGhprobe Manualdemos70100% (1)

- Hewlett Packard 5305B Service, User ID4961Dokumen48 halamanHewlett Packard 5305B Service, User ID4961cesarmayhemBelum ada peringkat

- EE3101 Lab Manual 2013 UMNDokumen17 halamanEE3101 Lab Manual 2013 UMNNate LinxBelum ada peringkat

- AD624Dokumen17 halamanAD624سعيد ابوسريعBelum ada peringkat

- Roland/BOSS Products AC Adaptor InformationDokumen4 halamanRoland/BOSS Products AC Adaptor InformationCristian Daniel ChelariuBelum ada peringkat

- ELX303+ +Power+Electronic+Equipment+ +AC DC+Converter+Design+ +part+11+ +october+2020Dokumen51 halamanELX303+ +Power+Electronic+Equipment+ +AC DC+Converter+Design+ +part+11+ +october+2020Sohaib JavaidBelum ada peringkat

- Series and Parallel CircuitDokumen30 halamanSeries and Parallel CircuitAmirul Syazwan100% (1)

- A Typical PC (Escuela TIC Inglés I)Dokumen3 halamanA Typical PC (Escuela TIC Inglés I)Angelita Beatriz Celis AlcainoBelum ada peringkat

- ASI4517R1: Antenna SpecificationsDokumen3 halamanASI4517R1: Antenna SpecificationsyacasiestaBelum ada peringkat

- Her Body and Other Parties: StoriesDari EverandHer Body and Other Parties: StoriesPenilaian: 4 dari 5 bintang4/5 (821)

- DIGPRA2 Prac Tutorial Prac1Dokumen10 halamanDIGPRA2 Prac Tutorial Prac1SBUSISOBelum ada peringkat

- Tando 700 Brochure EnuDokumen8 halamanTando 700 Brochure Enu159753Belum ada peringkat

- Feedback Amplifiers and Oscillators PDFDokumen2 halamanFeedback Amplifiers and Oscillators PDFAmy100% (2)

- List of RF and IF components for Anthropic DSA815 spectrum analyzerDokumen2 halamanList of RF and IF components for Anthropic DSA815 spectrum analyzerInam Ur RehmanBelum ada peringkat

- WAGO 750 461 DatasheetDokumen1 halamanWAGO 750 461 DatasheetJoako ArandaBelum ada peringkat

- PDS Lab13 Counter & DisplayDokumen8 halamanPDS Lab13 Counter & DisplayPhu CuonqBelum ada peringkat

- Configure multi-function timer ranges from 0.1s to 100hDokumen3 halamanConfigure multi-function timer ranges from 0.1s to 100hMelchor FranciscoBelum ada peringkat

- Fiber Patch Cable: The Best Choice for Data CentersDokumen9 halamanFiber Patch Cable: The Best Choice for Data CentersSteven YoungBelum ada peringkat

- Circuits 2 Quiz 3Dokumen2 halamanCircuits 2 Quiz 3John Lenard SanchezBelum ada peringkat

- XD400 4v2 MANDokumen20 halamanXD400 4v2 MANDanilo GamarrosBelum ada peringkat

- ICT inventory for Belwang Elementary SchoolDokumen12 halamanICT inventory for Belwang Elementary SchoolANDY M. BAROLA100% (2)

- 308Mhz/315Mhz/418Mhz/433.92Mhz Low-Power, FSK Superheterodyne ReceiverDokumen19 halaman308Mhz/315Mhz/418Mhz/433.92Mhz Low-Power, FSK Superheterodyne ReceiverBlagoja GjakovskiBelum ada peringkat

- Iwh 090V08N0 1 - DS - 3 0 4Dokumen1 halamanIwh 090V08N0 1 - DS - 3 0 4KonstantinBelum ada peringkat

- Manuale Pj10kps-CA Rev 3.0 Eng RVR TXDokumen244 halamanManuale Pj10kps-CA Rev 3.0 Eng RVR TXkarzcom100% (1)

- All Rights Reserved, Central Computer Centre, SVNIT SuratDokumen1 halamanAll Rights Reserved, Central Computer Centre, SVNIT SuratVishwajeet S BBelum ada peringkat

- AN6105 ADokumen13 halamanAN6105 AMeshackMukakaBelum ada peringkat

- Fundamentals of Electronics, Book - 1 PDFDokumen319 halamanFundamentals of Electronics, Book - 1 PDFjramongv83% (12)

- 73 Magazine 1968 10 OctoberDokumen132 halaman73 Magazine 1968 10 Octoberrodolfo ProkopovichBelum ada peringkat

- CCDs Convert Light to Digital ImagesDokumen13 halamanCCDs Convert Light to Digital ImagesSourodeep BasuBelum ada peringkat

- 4 719208242403606532Dokumen1 halaman4 719208242403606532Yahya SaifanBelum ada peringkat