Chapter1 Basic Structure of Computers

Diunggah oleh

Ahmed SulejmanovicHak Cipta

Format Tersedia

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniHak Cipta:

Format Tersedia

Chapter1 Basic Structure of Computers

Diunggah oleh

Ahmed SulejmanovicHak Cipta:

Format Tersedia

3/8/2016

Chapter 1. Basic

Structure of Computers

Information Handled by a

Computer

Functional Units

Arithmetic

and

logic

Input

Instructions/machine instructions

Govern the transfer of information within a computer as

well as between the computer and its I/O devices

Specify the arithmetic and logic operations to be

performed

Program

Data

Used as operands by the instructions

Source program

Encoded in binary code 0 and 1

Memory

Output

Functional Units

Control

I/O

Processor

Figure 1.1. Basic functional units of a computer.

Memory Unit

Arithmetic and Logic Unit

(ALU)

Store programs and data

Two classes of storage

Primary storage

Fast

Programs must be stored in memory while they are being executed

Large number of semiconductor storage cells

Processed in words

Address

RAM and memory access time

Memory hierarchy cache, main memory

Secondary storage larger and cheaper

Most computer operations are executed in

ALU of the processor.

Load the operands into memory bring them

to the processor perform operation in ALU

store the result back to memory or retain in

the processor.

Registers

Fast control of ALU

3/8/2016

The processor : Data Path and

Control

Control Unit

All computer operations are controlled by the control

unit.

The timing signals that govern the I/O transfers are

also generated by the control unit.

Control unit is usually distributed throughout the

machine instead of standing alone.

Operations of a computer:

Accept information in the form of programs and data through an

input unit and store it in the memory

Fetch the information stored in the memory, under program control,

into an ALU, where the information is processed

Output the processed information through an output unit

Control all activities inside the machine through a control unit

Basic Operational

Concepts

Data

PC

Address

Instructions

Register #

Register

Bank

Register #

Instruction

Memory

A

L

U

Address

Data Memory

Register #

Data

Two types of functional units:

elements that operate on data values (combinational)

elements that contain state (state elements)

Review

Activity in a computer is governed by instructions.

To perform a task, an appropriate program

consisting of a list of instructions is stored in the

memory.

Individual instructions are brought from the memory

into the processor, which executes the specified

operations.

Data to be used as operands are also stored in the

memory.

Memory

MAR

MDR

Control

PC

R0

R1

Processor

IR

ALU

Rn -

Connection Between the

Processor and the Memory

n general purpose

registers

Figure 1.2. Connections between the processor and the memory.

Registers

Instruction register (IR)

Program counter (PC)

General-purpose register (R0 Rn-1)

Memory address register (MAR)

Memory data register (MDR)

3/8/2016

Typical Operating Steps

Programs reside in the memory through input

devices

PC is set to point to the first instruction

The contents of PC are transferred to MAR

A Read signal is sent to the memory

The first instruction is read out and loaded

into MDR

The contents of MDR are transferred to IR

Decode and execute the instruction

Typical Operating Steps

(Cont)

Get operands for ALU

Perform operation in ALU

Store the result back

General-purpose register

Memory (address to MAR Read MDR to ALU)

To general-purpose register

To memory (address to MAR, result to MDR Write)

During the execution, PC is

incremented to the next instruction

A Typical Instruction

Add R0, LOCA

Add the operand at memory location LOCA to the

operand in a register R0 in the processor.

Place the sum into register R0.

The original contents of LOCA are preserved.

The original contents of R0 is overwritten.

Instruction is fetched from the memory into the

processor the operand at LOCA is fetched and

added to the contents of R0 the resulting sum is

stored in register R0.

From Essentials of Computer Architecture by Douglas E. Comer. ISBN 0131491792. 2005 Pearson Education, Inc. All rights

reserved.

Separate Memory Access and

ALU Operation

Load R1, LOCA,

Add R2, R1, R0

Whose contents will be overwritten?

From Essentials of Computer Architecture by Douglas E. Comer. ISBN 0131491792. 2005 Pearson Education, Inc. All rights

reserved.

3/8/2016

From Essentials of Computer Architecture by Douglas E. Comer. ISBN 0131491792. 2005 Pearson Education, Inc. All rights

reserved.

From Essentials of Computer Architecture by Douglas E. Comer. ISBN 0131491792. 2005 Pearson Education, Inc. All rights

reserved.

From Essentials of Computer Architecture by Douglas E. Comer. ISBN 0131491792. 2005 Pearson Education, Inc. All rights

reserved.

From Essentials of Computer Architecture by Douglas E. Comer. ISBN 0131491792. 2005 Pearson Education, Inc. All rights

reserved.

Interrupt

Normal execution of programs may be preempted if

some device requires urgent servicing.

The normal execution of the current program must

be interrupted the device raises an interrupt

signal.

Interrupt-service routine

Current system information backup and restore (PC,

general-purpose registers, control information,

specific information)

From Essentials of Computer Architecture by Douglas E. Comer. ISBN 0131491792. 2005 Pearson Education, Inc. All rights

reserved.

3/8/2016

Input

Bus Structures

There are many ways to connect different

parts inside a computer together.

A group of lines that serves as a connecting

path for several devices is called a bus.

Address/data/control

Output

Memory

Processor

Bus Structure

Figure 1.3.

Single-bus structure.

Single-bus

Speed Issue

Different devices have different

transfer/operate speed.

If the speed of bus is bounded by the slowest

device connected to it, the efficiency will be

very low.

How to solve this?

A common approach use buffers.

Performance

The most important measure of a computer is

how quickly it can execute programs.

Three factors affect performance:

Hardware design

Instruction set

Compiler

Performance

Performance

Processor time to execute a program depends on the hardware

involved in the execution of individual machine instructions.

Main

memory

Cache

memory

Processor

Bus

Figure 1.5. The processor cache.

3/8/2016

Performance

Processor Clock

The processor and a relatively small cache

memory can be fabricated on a single

integrated circuit chip.

Speed

Cost

Memory management

Basic Performance Equation

T processor time required to execute a program that has been

prepared in high-level language

N number of actual machine language instructions needed to

complete the execution (note: loop)

S average number of basic steps needed to execute one

machine instruction. Each step completes in one clock cycle

R clock rate

Note: these are not independent to each other

N S

R

How to improve T?

Clock Rate

Increase clock rate

Improve the integrated-circuit (IC) technology to make

the circuits faster

Reduce the amount of processing done in one basic step

(however, this may increase the number of basic steps

needed)

Increases in R that are entirely caused by

improvements in IC technology affect all

aspects of the processors operation equally

except the time to access the main memory.

Clock, clock cycle, and clock rate

The execution of each instruction is divided

into several steps, each of which completes

in one clock cycle.

Hertz cycles per second

Pipeline and Superscalar

Operation

Instructions are not necessarily executed one after

another.

The value of S doesnt have to be the number of

clock cycles to execute one instruction.

Pipelining overlapping the execution of successive

instructions.

Add R1, R2, R3

Superscalar operation multiple instruction

pipelines are implemented in the processor.

Goal reduce S (could become <1!)

CISC and RISC

Tradeoff between N and S

A key consideration is the use of pipelining

S is close to 1 even though the number of basic steps

per instruction may be considerably larger

It is much easier to implement efficient pipelining in

processor with simple instruction sets

Reduced Instruction Set Computers (RISC)

Complex Instruction Set Computers (CISC)

3/8/2016

Compiler

A compiler translates a high-level language program

into a sequence of machine instructions.

To reduce N, we need a suitable machine instruction

set and a compiler that makes good use of it.

Goal reduce NS

A compiler may not be designed for a specific

processor; however, a high-quality compiler is

usually designed for, and with, a specific processor.

Multiprocessors and

Multicomputers

Multiprocessor computer

Execute a number of different application tasks in parallel

Execute subtasks of a single large task in parallel

All processors have access to all of the memory shared-memory

multiprocessor

Cost processors, memory units, complex interconnection networks

Multicomputers

Each computer only have access to its own memory

Exchange message via a communication network messagepassing multicomputers

Anda mungkin juga menyukai

- Introduction to Grinding Process Optimization Using Taguchi MethodsDokumen27 halamanIntroduction to Grinding Process Optimization Using Taguchi Methodsranarani2013100% (1)

- TP Job Information Sheets Aug - Jan - I PDFDokumen365 halamanTP Job Information Sheets Aug - Jan - I PDFMohan kumar G100% (1)

- Iti PDFDokumen419 halamanIti PDFhimanshu dutt100% (1)

- All in OneDokumen789 halamanAll in OneHafsa ShaukatBelum ada peringkat

- Presentation On Reforms in All India Trade Test (AITT) : Conducted Under The Aegis of NCVT On 11.10.2018Dokumen28 halamanPresentation On Reforms in All India Trade Test (AITT) : Conducted Under The Aegis of NCVT On 11.10.2018Ravi TejaBelum ada peringkat

- RefrigrantsDokumen41 halamanRefrigrantsmuthuBelum ada peringkat

- Machine Tools Hand Tools: Fitting ShopDokumen12 halamanMachine Tools Hand Tools: Fitting ShopMadara uchihaBelum ada peringkat

- Topic 1) Transistors: Marks 24: IntroductionDokumen24 halamanTopic 1) Transistors: Marks 24: IntroductionSudershan Dolli100% (1)

- Unit6 N 7Dokumen46 halamanUnit6 N 7Shanku Raajashree100% (1)

- System of Limits, Fits, Tolerance and Gauging PDFDokumen32 halamanSystem of Limits, Fits, Tolerance and Gauging PDFPraveen MohapatraBelum ada peringkat

- Hindi Notes 12th STDDokumen14 halamanHindi Notes 12th STDSiddhart ManotharaBelum ada peringkat

- Mel311 Part IIDokumen165 halamanMel311 Part IIAarsh Vir GuptaBelum ada peringkat

- MrJacksonMaths Unit 2 Higher November 2012Dokumen23 halamanMrJacksonMaths Unit 2 Higher November 2012Russell Jackson100% (1)

- Assignments Sub: Production Process IIDokumen2 halamanAssignments Sub: Production Process IIShantanu Gaikwad100% (1)

- DFBN FilterDokumen10 halamanDFBN FilterPutut SuprihartonoBelum ada peringkat

- Format - Detail Progressive Record of The StudentDokumen4 halamanFormat - Detail Progressive Record of The StudentAnita KumariBelum ada peringkat

- Demonstration 2019Dokumen14 halamanDemonstration 2019M'dth CalBelum ada peringkat

- PDF Created With Pdffactory Trial VersionDokumen17 halamanPDF Created With Pdffactory Trial VersionShanmuga LakshmikanthanBelum ada peringkat

- Progress Report CardDokumen4 halamanProgress Report CardChanna100% (1)

- A Presentation ON: Unit-IvDokumen52 halamanA Presentation ON: Unit-IvVķ MãħëšħBelum ada peringkat

- Bin CardDokumen2 halamanBin Cardershad123100% (1)

- CTS FitterDokumen14 halamanCTS FitterSahitya SaxenaBelum ada peringkat

- ADM Use of ComparativesDokumen6 halamanADM Use of ComparativesCarlos RochaBelum ada peringkat

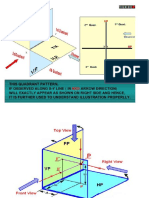

- Orthographic ProjectionDokumen36 halamanOrthographic ProjectionDEEPANGaeBelum ada peringkat

- Fitting Shop Operations Nazeef'sDokumen6 halamanFitting Shop Operations Nazeef'sFaheem Fiaz ChohanBelum ada peringkat

- Lesson 1Dokumen7 halamanLesson 1api-273340865100% (1)

- Unit 1 - Manufacturing Process - WWW - Rgpvnotes.inDokumen26 halamanUnit 1 - Manufacturing Process - WWW - Rgpvnotes.insuneel kumar rathoreBelum ada peringkat

- Average PDFDokumen13 halamanAverage PDFImtiaz AhmedBelum ada peringkat

- Bulk Deformation Processes - ExtrusionDokumen16 halamanBulk Deformation Processes - ExtrusionAnonymous 8NSojG100% (1)

- 9SurfaceRoughness Limits Fits and TolerancesDokumen25 halaman9SurfaceRoughness Limits Fits and Tolerancesharsha vardhanBelum ada peringkat

- First Angle ProjectionDokumen20 halamanFirst Angle ProjectionFaqiroh Wajed100% (1)

- Study centre lathe single point cutting tool geometryDokumen4 halamanStudy centre lathe single point cutting tool geometryTanmay Warde100% (1)

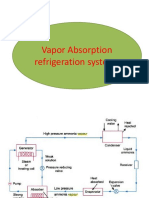

- Vapor Absorption SystemsDokumen17 halamanVapor Absorption SystemsTalibHussainBelum ada peringkat

- Assignment On ClutchDokumen8 halamanAssignment On ClutchPankaj GillBelum ada peringkat

- Job Marking RegisterDokumen2 halamanJob Marking RegisterAnurag Patel100% (1)

- Basic of GrindingDokumen19 halamanBasic of GrindingKaushik SreenivasBelum ada peringkat

- Painting Theory N IosDokumen68 halamanPainting Theory N IosMuhammad Bangi100% (1)

- Notes On Handbook of Surface Water Quality ModelingDokumen10 halamanNotes On Handbook of Surface Water Quality ModelingSalam Daeng BengoBelum ada peringkat

- Objective TestDokumen6 halamanObjective TestYussif IsshakBelum ada peringkat

- Ortographic ProjectionDokumen37 halamanOrtographic ProjectionWarren RiveraBelum ada peringkat

- First Year Theory ITIDokumen2 halamanFirst Year Theory ITImangla prasadBelum ada peringkat

- Engineering Metrology and Measurements N.V. Raghavendra L. KrishnamurthyDokumen31 halamanEngineering Metrology and Measurements N.V. Raghavendra L. KrishnamurthyRandøm TalkìêsBelum ada peringkat

- BME Unit IV Machine ToolsDokumen41 halamanBME Unit IV Machine ToolsArvind BhosaleBelum ada peringkat

- Note Chapter5 SF017Dokumen50 halamanNote Chapter5 SF017api-3699866100% (3)

- Hand ToolsDokumen29 halamanHand ToolsSsi K-din100% (2)

- Sheet Metal Practical Skills and Theory TopicsDokumen2 halamanSheet Metal Practical Skills and Theory TopicsHamza NoumanBelum ada peringkat

- Grinding Final NotesDokumen21 halamanGrinding Final NotesGaikwad Aniket100% (1)

- Unit-Ii Projection of Points & Lines Theory of Projections Projection TheoryDokumen37 halamanUnit-Ii Projection of Points & Lines Theory of Projections Projection Theorysunil kumarBelum ada peringkat

- Limits Fits TolerancesDokumen15 halamanLimits Fits TolerancespankajdharmadhikariBelum ada peringkat

- Fundamental Hindi Notes July 2018 UpdatedDokumen107 halamanFundamental Hindi Notes July 2018 Updatedsuraj786sharmaBelum ada peringkat

- Chapter 1 Hand ToolsDokumen22 halamanChapter 1 Hand ToolsMohd HapisBelum ada peringkat

- Rolling Notes @mohit Chouksey PDFDokumen11 halamanRolling Notes @mohit Chouksey PDFHimanshu GoelBelum ada peringkat

- Refrigeration Air Conditioning Lab ManualDokumen13 halamanRefrigeration Air Conditioning Lab Manualjayshah1991100% (1)

- Powerpoint Presentation: Cutting Tool and MaterialDokumen27 halamanPowerpoint Presentation: Cutting Tool and MaterialMayank RawatBelum ada peringkat

- Refrigeration and Air ConditioningDokumen22 halamanRefrigeration and Air ConditioningSiddhrajsinh ZalaBelum ada peringkat

- Aerodynamics Thermodynamics Lesson PlanDokumen3 halamanAerodynamics Thermodynamics Lesson PlanParama GuruBelum ada peringkat

- Chapter1 - Basic Structure of ComputersDokumen119 halamanChapter1 - Basic Structure of ComputersAnkit SharmaBelum ada peringkat

- Chapter1, Chap 2 PDFDokumen86 halamanChapter1, Chap 2 PDFKaram Veer SinghBelum ada peringkat

- Chapter1 - Basic Structure of ComputersDokumen119 halamanChapter1 - Basic Structure of ComputersShanmu K0% (1)

- Computer Networks Practical FileDokumen15 halamanComputer Networks Practical FilebikkerBelum ada peringkat

- Stop and Wait ProtocolDokumen10 halamanStop and Wait ProtocolananthigowrishankarBelum ada peringkat

- Z8F4822AR020SCDokumen299 halamanZ8F4822AR020SCrdc02271Belum ada peringkat

- Paket 5000 Up 531 08.25.22 25 08 2022Dokumen7 halamanPaket 5000 Up 531 08.25.22 25 08 2022pathul azizBelum ada peringkat

- NHMWriter User ManualDokumen7 halamanNHMWriter User Manualvelxerox4123Belum ada peringkat

- Guia Configuracion 9500MPR MSS4 MSS8 Orange PDFDokumen15 halamanGuia Configuracion 9500MPR MSS4 MSS8 Orange PDFalcides quijadaBelum ada peringkat

- Dialogic SS7 Call FlowDokumen176 halamanDialogic SS7 Call Flowhari423Belum ada peringkat

- ECEN 5803 Mastering Embedded Systems ArchitectureDokumen3 halamanECEN 5803 Mastering Embedded Systems ArchitectureMehul PatelBelum ada peringkat

- Blaupunkt Bahamas Mp46Dokumen204 halamanBlaupunkt Bahamas Mp46eduardskBelum ada peringkat

- Bahrain 3rd Network IP Design 20100615Dokumen161 halamanBahrain 3rd Network IP Design 20100615thakur10625Belum ada peringkat

- PIC16F887Dokumen338 halamanPIC16F887David BaronBelum ada peringkat

- Ds-2Cd2686G2-Izs 8 MP Ir Varifocal Bullet Network Camera: AcusenseDokumen6 halamanDs-2Cd2686G2-Izs 8 MP Ir Varifocal Bullet Network Camera: Acusensedariotlc100% (1)

- CALIFORNIA DEPT FORESTRY FIRE PROTECTION VOICE EVACUATION SYSTEMDokumen1 halamanCALIFORNIA DEPT FORESTRY FIRE PROTECTION VOICE EVACUATION SYSTEMmjay90Belum ada peringkat

- User Guide SimplifyDokumen1.242 halamanUser Guide SimplifyIsaac Benitez100% (1)

- Toughpower CableManagement 1200W PSU GuideDokumen12 halamanToughpower CableManagement 1200W PSU GuideIvan Carlos BolettaBelum ada peringkat

- Airo WizardDokumen3 halamanAiro WizardCuma QoBelum ada peringkat

- AutomationNetworkSelectionThirdEd Caro Chapter3Dokumen32 halamanAutomationNetworkSelectionThirdEd Caro Chapter3Camilo Ramirez ABelum ada peringkat

- 2.2.2.4 Packet Tracer - Configuring IPv4tatic and Default Routes Instructions1Dokumen4 halaman2.2.2.4 Packet Tracer - Configuring IPv4tatic and Default Routes Instructions1Rafiullah RustamBelum ada peringkat

- Deploying Instant in AirwaveDokumen36 halamanDeploying Instant in AirwaveneoaltBelum ada peringkat

- Iz Jncie SP WT v1.1Dokumen975 halamanIz Jncie SP WT v1.1Ramon PirbuxBelum ada peringkat

- High Capacity Colored Two Dimensional Codes: Antonio Grillo, Alessandro Lentini, Marco Querini and Giuseppe F. ItalianoDokumen8 halamanHigh Capacity Colored Two Dimensional Codes: Antonio Grillo, Alessandro Lentini, Marco Querini and Giuseppe F. ItalianoArihant PawariyaBelum ada peringkat

- Powervault-Tl2000 Reference Guide2 En-UsDokumen16 halamanPowervault-Tl2000 Reference Guide2 En-UsNguyen Cong ThangBelum ada peringkat

- Collaborative Whiteboard Using RMI: I I of T, KDokumen11 halamanCollaborative Whiteboard Using RMI: I I of T, Kmadhusudan chunletiaBelum ada peringkat

- Solution Brief - FortiMail For Service ProvidersDokumen31 halamanSolution Brief - FortiMail For Service ProvidersabaheabaheabaheBelum ada peringkat

- SM J700F Tshoo 7 - 2Dokumen53 halamanSM J700F Tshoo 7 - 2martapontealegreBelum ada peringkat

- Commodore 64 An Introduction To BASIC - Part 1Dokumen153 halamanCommodore 64 An Introduction To BASIC - Part 1Delfin ButlonosyBelum ada peringkat

- UM08001 JLinkARMDokumen220 halamanUM08001 JLinkARMicucutaBelum ada peringkat

- Actix DocumentDokumen13 halamanActix DocumentNgweno MzitoBelum ada peringkat

- Federation of Cloud Computing InfrastructureDokumen5 halamanFederation of Cloud Computing InfrastructureIJSTEBelum ada peringkat

- Load Balanced ProxySQL in Google CloudDokumen2 halamanLoad Balanced ProxySQL in Google Cloudtsultim bhutiaBelum ada peringkat