Arquitectura RISC Vs CISC

Diunggah oleh

Daniel Wolf0 penilaian0% menganggap dokumen ini bermanfaat (0 suara)

23 tayangan3 halamanArquitectura de ordenadores

Judul Asli

Arquitectura RISC vs CISC

Hak Cipta

© © All Rights Reserved

Format Tersedia

DOC, PDF, TXT atau baca online dari Scribd

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniArquitectura de ordenadores

Hak Cipta:

© All Rights Reserved

Format Tersedia

Unduh sebagai DOC, PDF, TXT atau baca online dari Scribd

0 penilaian0% menganggap dokumen ini bermanfaat (0 suara)

23 tayangan3 halamanArquitectura RISC Vs CISC

Diunggah oleh

Daniel WolfArquitectura de ordenadores

Hak Cipta:

© All Rights Reserved

Format Tersedia

Unduh sebagai DOC, PDF, TXT atau baca online dari Scribd

Anda di halaman 1dari 3

Arquitectura RISC vs CISC

Significado de sus siglas:

CISC (Complex instruction set computer)

Computadoras con un conjunto de instrucciones complejo

RISC (Reduced instruction set computer)

Computadoras con un conjunto de instrucciones reducido.

Con tecnologias de los semiconductores comparables e igual

frecuencia de reloj , un procesador RISC tipico tiene una capacidad de

procesamiento de 2 a 4 veces mayor que la de un CISC , pero su

estructura de hardware es tan simple , que se puede realizar en una

fraccion de la superficie ocupada por el circuito integrado de un

procesador CISC.

La meta principal es incrementar el rendimiento del procesador , ya

sea optimizando alguno existente o se desee crear uno nuevo. Para

esto se deben considerar 3 areas principales en el diseo del

procesador:

La arquitectura

La tecnologia de proceso

El encapsulado

La tecnologia de proceso , se refiere a los materiales y tecnicas

utilizadas en la fabricacin del circuito integrado.

El encapsulados se refiere a como se integra un procesador con lo

que lo rodea en un sistema funcional , que de alguna manera

determina la velocidad total del sistema .

Dependiendo de cmo el procesador almacena los operandos de las

instrucciones de la CPU, existen 3 tipos de juegos de instrucciones:

1. Juego de instrucciones para arquitecturas basadas en pilas.

2. Juego de instrucciones para arquitecturas basadas en

acumulador.

3. Juego de instrucciones para arquitecturas basadas en registros.

Las Arquitecturas RISC y CISC con ejemplos de CPU con un conjunto

de instrucciones para arquitectura basadas en registros.

Arquitecturas CISC

La microprogramacion es una caracteristica importante y esencial de

casi todas las arquitecturas CISC , como por ejemplo:

Intel 8086,8088,80286,80386,80486.

Motorola 68000,68010,68020,68030,68040.

La microprogramacin significa que cada instruccin de maquina es

interpretada por un microprograma localizado en una memoria en el

circuito integrado del procesador .

Arquitecturas RISC

Caracteristicas escenciales :

1. Toman como base el esquema moderno de Von Neumann.

2. Las instrucciones estan divididas en 3 grupos :

a) Transferencia

b) Operaciones

c) Control de Flujo

3. Reduccion del conjunto de instrucciones a

instrucciones

basicas simples.

4. Arquitectura del tipo load-store(carga y almacena)

5. Casi todas las instrucciones pueden ejecutarse dentro de un ciclo

de reloj

6. Pipeline , esta tecnica permite que una instruccin pueda

empezar a ejecutarse antes de que haya terminado el anterior.

El hecho de que la estructura simple de un procesador RISC conduzca

a una notable reduccion de la superficie del circuito integrado es

aprovechado para ubicar en el mismo funciones adicionales:

Unidad para el procesamiento aritmetico de punto flotante.

Unidad de administracin de memoria.

Funciones de control de memoria cach.

Implantacion de un conjunto de registros multiples.

Principios de Diseo de las RISC

1. Analizar las aplicaciones para encontrar las operaciones clave.

2. Disear un bus de datos que sea optimo para las operaciones clave

3. Disear instucciones que realicen las operaciones clave utilizando

el bus de datos

4. Agregar nuevas instrucciones solo si no hacen mas lenta la

maquina.

5. Repetir este proceso para otros recursos .

Capacidad de los compiladores en un sistema RISC.

Todas las operaciones complejas se trasladan al microprocesador por

medio de conexiones fijas, de esta manera el comprador asume la

funcion de un mediador inteligente entre el programa de aplicacin y

el microprocesador, se hace el esfuerzo de mantener el hardware tan

simple aun a costa de hacer el compilador mas complicado .

Entretanto los microprocesadores CISC tienden a tener el

microprograma y compilador ambos complicados.

Anda mungkin juga menyukai

- El Ladron Del Fuego - Primeras PaginasDokumen21 halamanEl Ladron Del Fuego - Primeras PaginasDaniel WolfBelum ada peringkat

- Cero Acné Como Cure Mi Acné para Siempre, Jason Wilkins - by - Juanchy13Dokumen31 halamanCero Acné Como Cure Mi Acné para Siempre, Jason Wilkins - by - Juanchy13Edu A. Salinas RojasBelum ada peringkat

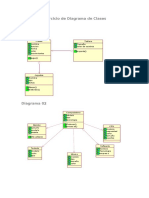

- Ejercicio de Diagrama de ClasesDokumen3 halamanEjercicio de Diagrama de ClasesDaniel WolfBelum ada peringkat

- EjerciciosSQL PDFDokumen39 halamanEjerciciosSQL PDFPaul Delgado Soto100% (1)

- El Yogurt de SoyaDokumen13 halamanEl Yogurt de SoyaDaniel WolfBelum ada peringkat

- Guia Nudos de Corbatas PDFDokumen6 halamanGuia Nudos de Corbatas PDFMalloy Ruiz100% (1)

- Detalles Tipos de TarjetasDokumen16 halamanDetalles Tipos de TarjetasDaniel WolfBelum ada peringkat

- Guía para Recuperar Una Memoria USB FlashDokumen4 halamanGuía para Recuperar Una Memoria USB Flashanon-740097100% (166)

- Guia Nudos de Corbatas PDFDokumen6 halamanGuia Nudos de Corbatas PDFMalloy Ruiz100% (1)

- En El Camino de JellicoeDokumen171 halamanEn El Camino de JellicoeDaniel WolfBelum ada peringkat

- Pensamiento Lenguaje y ComunicaciónDokumen14 halamanPensamiento Lenguaje y ComunicaciónDaniel WolfBelum ada peringkat

- Chistes Y BromasDokumen58 halamanChistes Y BromasLuis Montero0% (1)

- Fundamentación proyecto TIC escuelaDokumen60 halamanFundamentación proyecto TIC escuelaDaniel WolfBelum ada peringkat

- InformaciónDokumen4 halamanInformaciónjruizc8Belum ada peringkat

- InformaciónDokumen4 halamanInformaciónjruizc8Belum ada peringkat

- Guia Nudos de Corbatas PDFDokumen6 halamanGuia Nudos de Corbatas PDFMalloy Ruiz100% (1)

- Taller 01 - Identificación de PernosDokumen12 halamanTaller 01 - Identificación de PernosFernando JuarezBelum ada peringkat

- Integra DireccionDokumen2 halamanIntegra DireccionJose Manuel Garcia GarciaBelum ada peringkat

- ACTIVIDAD No 6 Disco DuroDokumen2 halamanACTIVIDAD No 6 Disco DuroOliver SGBelum ada peringkat

- Windows 7 Boot RepairDokumen10 halamanWindows 7 Boot RepairGuillermo Celis PradaBelum ada peringkat

- ASRock - Productos - Placas Base - G31M-VS2Dokumen2 halamanASRock - Productos - Placas Base - G31M-VS2Yamel CurielBelum ada peringkat

- Sistema AbsDokumen24 halamanSistema AbsYonner RangelBelum ada peringkat

- Dime Como Evaluas y Te Dire Que Tipo de Profesional y de Persona EresDokumen7 halamanDime Como Evaluas y Te Dire Que Tipo de Profesional y de Persona EresCinthia Flores AlarcónBelum ada peringkat

- Perfil Hidrosanitario I.E.Dokumen4 halamanPerfil Hidrosanitario I.E.Daniel RengifoBelum ada peringkat

- Preguntas NTC 2050Dokumen6 halamanPreguntas NTC 2050Gilberth Andres Charry Alvarez100% (1)

- File PDFDokumen58 halamanFile PDFDieFluxDBelum ada peringkat

- Población Por Provincias de La AmazoniaDokumen9 halamanPoblación Por Provincias de La AmazoniaAdrian ZeasBelum ada peringkat

- Autocad 2016 BasicoDokumen110 halamanAutocad 2016 Basicoawys61434100% (6)

- 284 SSP - A8 Transmision 09E Parte2 - SPDokumen52 halaman284 SSP - A8 Transmision 09E Parte2 - SPRoxana Elizabeth Valencia NavarrteBelum ada peringkat

- Autodesk Inventor Pro 2024.2 Full Español (Ultima Versión)Dokumen10 halamanAutodesk Inventor Pro 2024.2 Full Español (Ultima Versión)franjhtBelum ada peringkat

- Programacion Segun Codigo Iso Torno FagorDokumen9 halamanProgramacion Segun Codigo Iso Torno FagorxxtataxxBelum ada peringkat

- Instalaciones de enlace baja tensión guía vademécum PLC MadridDokumen108 halamanInstalaciones de enlace baja tensión guía vademécum PLC Madridrafins7667% (3)

- AssemblerDokumen56 halamanAssemblermre7852Belum ada peringkat

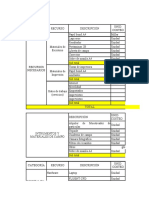

- Tesis 3 GastosDokumen11 halamanTesis 3 GastosMarco Esaú Portal ValdiviaBelum ada peringkat

- Prácticas Caja de Cambios Manual GRUPO 1Dokumen10 halamanPrácticas Caja de Cambios Manual GRUPO 1erxemilla23Belum ada peringkat

- Niveles Estructurales de Bell y NewellDokumen1 halamanNiveles Estructurales de Bell y NewellSoporte Empresas0% (1)

- Programación de microcontroladores - Implementación del aplicativo 1Dokumen7 halamanProgramación de microcontroladores - Implementación del aplicativo 1Fernando Rivera HuaytallaBelum ada peringkat

- Allen Bradley PLC Manual de ProgramacionDokumen77 halamanAllen Bradley PLC Manual de ProgramacionamiguitoBelum ada peringkat

- Arduino WikiDokumen9 halamanArduino WikiOz FugahBelum ada peringkat

- Arduino Como PLC PDFDokumen24 halamanArduino Como PLC PDFBogdan Geana50% (2)

- Memoria RamDokumen11 halamanMemoria RamCh Ana Karina100% (2)

- York VRF Gen Ii - Jtohl - HP - Publ8810esla (0118)Dokumen4 halamanYork VRF Gen Ii - Jtohl - HP - Publ8810esla (0118)Luis EstradaBelum ada peringkat

- Introducción A Los MecanismosDokumen16 halamanIntroducción A Los MecanismosDaniela Galvan ChavezBelum ada peringkat

- Análisis de VibracionesDokumen4 halamanAnálisis de VibracionesbascoperuBelum ada peringkat

- (Ex) Une-En 15629 2009Dokumen3 halaman(Ex) Une-En 15629 2009angelBelum ada peringkat

- Caja de Cambios RT 11710B PDFDokumen140 halamanCaja de Cambios RT 11710B PDFJuan José Matos ChBelum ada peringkat