Analysis of Sense Amplifier Circuit Used in High Performance & Low Power Sram

Diunggah oleh

GJESRJudul Asli

Hak Cipta

Format Tersedia

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniHak Cipta:

Format Tersedia

Analysis of Sense Amplifier Circuit Used in High Performance & Low Power Sram

Diunggah oleh

GJESRHak Cipta:

Format Tersedia

www.globaljournal.

asia

GJESR REVIEW PAPER VOL. 1 [ISSUE 4] MAY, 2014

ISSN:- 2349283X

ANALYSIS OF SENSE AMPLIFIER CIRCUIT USED IN

HIGH PERFORMANCE & LOW POWER SRAM

1*Anangaraj Singh

Dept. of Electronics and Communication

Engineering

M.M.M. University of Technology

Gorakhpur, India

Email: anangaraj107@gmail.com

2Dr.R.K.Chuhan

Dept. of Electronics and Communication

Engineering

M.M.M. University of Technology

Gorakhpur, India

Email: rkchauhan27@gmail.com

ABSTRACT: Large bit-line capacitance is one of the main bottlenecks to the performance of on-chip

caches. New sense amplifier techniques need to explicitly address this challenge. This paper describes

three sensing techniques to overcome this problem: a voltage sense amplifier (VSA), a current sense

amplifier (CSA) and a charge transfer sense amplifier (CTSA). Increased process variation and reduced

operating voltage present two of the main challenges in using sense amplifiers for small geometry bulk

CMOS process technology. The current sense amplifier senses the cell current directly and shows a speed

improvement as compared to the conventional voltage mode sense amplifier, for same energy. The other

is a charge transfer sense amplifier that takes advantage of large bit-line capacitance for its operation.

CTSA shows an improvement for read delay and consumes less energy than the voltage mode sense

amplifier. CTSA results in reduced bit-line swing and which in turn leads to lower bit-line energy than the

conventional voltage mode.

Key words: CMOS, SRAM, VSA, CSA, CTSA, BIT-LINE.

Introduction

Static Random Access Memories (SRAMs) are an

important component of microprocessors and

system-on-chips. SRAMs are used as large

caches in microprocessor cores and serve as

storage in various IPs on a system-onchip.SRAMs used in high performance

microprocessors and graphics chips have high

speed requirements. At the same time, SRAMs

used in application processors which go into

mobile, handheld and consumer devices have

very low power requirements. Since SRAMs

serve as large storage on these chips, its very

important to get maximum density out of these.

Traditionally a large number of SRAM bit cells,

up to 1024 in some cases, are connected to a

common bit-line to get the highest density and

array efficiency. This results in a large

capacitance on the bit-lines which necessitates

using differential sense amplifiers for speed

reasons. Sense amplifiers detect the data being

read by sensing a small differential voltage

swing on the bit-lines rather than waiting for a

full rail-to-rail swing.

Depending on the performance and power

requirements, its very important for the sense

amplifiers to operate fast and do so while

burning a minimum amount of power. The large

bit-line capacitance is a big performance

bottleneck.

Conventional Voltage Sense Amplifiers need a

minimum amount of differential voltage to be

developed on the bit-lines for reliable operation.

The amount of time required to develop this

differential voltage is linearly proportional to

bit-line capacitance. The dynamic power

consumed in pre-charging the bit-lines increases

with the differential voltage that needs to be

developed. Low power requirements of mobile

and embedded chips require sense amplifiers

which burn less power than the traditional

voltage sense amplifier techniques.

This work explores multiple sense amplifiers

Current Sense Amplifier (CSA), Charge Transfer

Sense Amplifier (CTSA) and compares them in

speed, area, and power to the Voltage Sense

Virtu and Foi

11

GJESR REVIEW PAPER VOL. 1 [ISSUE 4] MAY, 2014

ISSN:- 2349283X

Amplifier (VSA). A current sense amplifier

operates by sensing the bit cell current directly

rather than waiting on a differential voltage to

develop on the bit-lines. The operation of charge

transfer sense amplifier is based on charge

sharing from the high capacitance bit-lines to

the low capacitance sense amplifier node.

Figure 3: Timing Scheme for a Voltage Sense

Amplifier

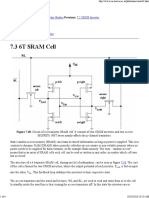

Figure 1: Basic schematic of one column for

small signal memory array using 6T cell

Voltage Sense Amplifier

A voltage sense amplifier senses the differential

voltage on the bit-lines and generates a full rail

output. The circuit is shown in Figure 2

The operation of the circuit is as follows. When

WL is enabled, a voltage differential begins to

develop on the bl/bl# pair. When enough

differential, depending on the technology and

circuit, has developed the sense amp enable

(SAEN) is activated which causes the cross

coupled inverters to go into a positive feedback

loop and translate the differential to full rail

output. The sense amplifier output node which

connects to the bit-line with a lower voltage, for

eg sa, is pulled down to 0 while the other output

sa# remains high. When sense amplifier is

enabled, NMOS devices N1 and N2 go into

saturation. The NMOS device N2 which receives

full VDD input has a higher current than N1 with

a smaller voltage as its Vgs. The one which

conducts higher current (N2) pulls its output

voltage lower reducing the Vgs on the other

NMOS device (N1), which therefore has smaller

current flowing through it.This positive

feedback loop continues until the output voltage

sa has fallen low enough to cause the NMOS

device N2 to enter linear region and turn on the

PMOS device P1 of the other inverter and cause

its output to be driven high. N1 is eventually

turned OFF, and the cross coupled inverters

store the resulting output.

Current Sense Amplifier

Figure 2: Voltage Sense Amplifier

The current sense amplifier (CSA) operates by

sensing the bit cell current directly. It is not

dependent on a differential voltage developing

Virtu and Foi

12

GJESR REVIEW PAPER VOL. 1 [ISSUE 4] MAY, 2014

ISSN:- 2349283X

across the bit-lines. This helps reduce bit-line

pre-charge power since the low going bit-line

can be clamped at a higher voltage than would

be required with a voltage sense amplifier. The

current sense amplifier consists of two parts: a

current transporting circuit with unity gain

current transfer characteristics and a sensing

circuit which senses the differential current. The

circuit diagram of the current sense amplifier is

shown in Figure 4. It is designed with a

combination of ideas from [1] and [5].

Figure 5: Current Conveyor Circuit

Figure 4: Current Sense Amplifier

The current transporting circuit or the current

conveyor consists of four equally sized PMOS

transistors (P1 through P4) with positive

feedback. These devices operate in saturation.

The current conveyor circuit, shown in Figure 5,

operates as follows. The gate-source voltage of

M1 will be equal to that of M3, since their

currents are equal, their sizes are equal, and

both transistors are in saturation. Let this

voltage be represented by V1. Similarly, the

gate-source voltages of M2 and M4 are also

equal, let this be

represented by V2. When YSEL is grounded, the

voltage on BL is given by V1+V2, so is the

voltage on BL#. Therefore, the potential of the

bit-lines will be equal independent of the

current distribution. This means that there

exists a virtual short circuit across the bit-lines.

Since the bit-line voltages are equal, the bit-line

load currents will also be equal, as well as the

bit-line capacitor currents. Since the cell draws a

current I, the right leg of the current conveyor

draws more current than the left leg. The

difference between these two currents will be

equal to the cell current. The drain current of M3

and M4 are passed to the current conveyor

output which is connected to the current

sensing circuit. The differential output current

of the current conveyor is therefore equal to the

cell current.

The current sense amplifier operates in two

phases: precharge and evaluate. During the

precharge phase, the bit-lines are precharged

through precharge devices connected to the bitlines (not shown here). The sense amplifier

output nodes SA and SA# are also precharged

high through M11 and M12 PMOS devices.

Devices M11 and M13 are ON during precharge,

equalizing the inputs and outputs of the sensing

circuit respectively. The operating current of the

sense amplifier is determined by the sizes of

devices M5-M8. At the end of the precharge

Virtu and Foi

13

GJESR REVIEW PAPER VOL. 1 [ISSUE 4] MAY, 2014

phase, precharge and equalization devices M11M14 are turned OFF. During the evaluation

phase, YSEL is pulled low and SAEN is pulled

high. The cross coupled inverters comprising of

devices M5-M8 then form a high gain positive

feedback amplifier. Due to the positive feedback,

the impedance looking into the source terminal

of either M7 or M8 is a negative resistance,

which causes M7 and M8 to begin sourcing a

portion of the difference current. The difference

current flowing through M7 and M8 flows

through the small equivalent capacitance at the

drains of M7 and M8, giving rise to a voltage

difference across the output nodes of the sense

amplifier. The initial trajectory for the

magnitude of the voltage difference between the

drains of M7 and M8 is given by

dV/dt = 2I/Cd

ISSN:- 2349283X

swing on the bit-lines. The circuit diagram of a

CTSA is shown in Figure 6.

The basic concept behind charge-transfer

amplification is to produce voltage gain by

exploiting charge conservation among capacitive

devices. For a series connection of two

capacitive elements in a system for which

charge is conserved, the product of the voltage

across the first element and its capacitance must

equal the product of the voltage across the

second element and its capacitance as shown in

the following equation.

Csmall Vsmall = Q = Clarge Vlarge

Voltage gain is therefore realized since a small

change in voltage across the larger capacitive

element will produce a larger change in voltage

across the smaller capacitive element.

where Cd is the total capacitance at the drain

node of M7 or M8. This trajectory is followed for

a short time, and then the resulting differential

voltage at the output of the sense amplifier is

rapidly amplified by the positive feedback of the

cross coupled inverters, driving one output to

zero and keeping the other one high.

The sensing delay is relatively insensitive to bitline capacitance as the operation is not

dependent on the development of a differential

voltage across the bit-lines. Unlike the voltage

sense amplifier, the output nodes are not tied to

the high capacitance bit-lines and are able to

respond very quickly. The CSA can have lower

voltage swing on bit-lines. This is because the

cross coupled PMOS pair M1 and M2 cuts off the

discharge path to ground for both bit-lines.

Suppose BL is high and BL# is going low. This

causes nodes Int and A to go high causing M2 to

be cut off. Therefore, the path from the low

going BL# to ground is cut off, reducing the

voltage swing on it.

Charge Transfer Sense Amplifier

The Charge Transfer Sense Amplifier (CTSA)

operates by making use of the charge

redistribution from high capacitance bit-lines to

the low capacitance sense amplifier output

nodes. This results in high speed operation and

lower power consumption due to low voltage

Figure 6: Charge Transfer Sense Amplifier

The operation of CTSA circuit is based on the

charge redistribution from high bit- line

capacitance to the low capacitance of sense

nodes sa and sa#. This charge redistribution

results in high speed operation and low bit-line

swing. The circuit consists of two parts. First is

the common gate cascode formed by M3, M5 and

M7 (and M4, M6 and M8), with PMOS devices

M3 and M4 biased at Vb. Second, the crosscoupled inverters formed by M9 and M13,

latches the output of the common-gate amplifier

(Sa and Sa#).In the precharge phase, the bitlines and all the intermediate nodes (ctin, ctinb,

ctout, ctoutb) are precharged high. The output of

Virtu and Foi

14

GJESR REVIEW PAPER VOL. 1 [ISSUE 4] MAY, 2014

the common gate amplifier (sa and sa#) are

predischarged low by keeping SAen high. In the

evaluation phase, SAPCH is pulled high and YSel

is grounded to select a column. CTSA is enabled

by pulling SAen low. Suppose the bit-line bl# is

going low. As the voltage of bl# goes near Vb +

Vtp, M4 goes into sub-threshold region of

operation preventing the output node sa# from

getting charged. However, the other bit-line bl

remains high and charges the output node sa to

high. Initially NMOS pair M12 and M13 helps in

rejecting the common mode noise and thereafter

helps in latching the value sensed by the

common gate amplifier. The timing scheme of

the CTSA is shown in Figure 6.

Conclusion

Current sensing is typically faster than voltage

sensing. Current sense amplifier can be enabled

faster than voltage mode, as current sensing

does not depend on differential discharging of

large bit-line capacitance. The bitline swing for

current sensing is less than the voltage mode,

but the energy saved with reduced bit-line

swing is compensated by the static power

dissipation of the current sense amplifier.

Charge transfer sense amplifier offers both

speed and power advantage. CTSA is faster than

the voltage mode sense amplifier. CTSA

consumes lower energy than voltage mode

sense amplifier. The bit-line swing for CTSA is at

least lower than voltage mode counterpart and

this gives a quadratic saving of about in the

energy. CTSA is as robust as voltage mode with

respect to Vt mismatch. CTSA offers dual

advantage of high-speed and low energy.

However, CTSA suffers from the additional

complexity in the design of bias voltage

generator. We are further studying the impact of

the secondary design issues like Vt mismatch,

bit-line capacitance mismatch etc. To determine

the robustness of these two circuits.

ISSN:- 2349283X

2. Evert Seevinck, Petrus J. van Beers and

Hans Ontrop. Current-Mode Techniques

for High-Speed VLSI Circuits with

Application to Current Sense Amplifier

for CMOS SRAMs. IEEE JSSC, Vol 26, No

4, April 1991.

3. Shoichiro Kawashima, Toshihiko Mori,

Ryuhei Sasagawa, Makoto Hamaminato,

Shigetoshi Wakayama, Kazuo Sukegawa

and Isao Fukushi. A Charge-Transfer

Amplifier

and

Encoded-Bus

Architecture for Low-Power SRAMs.

IEEE JSSC, Vol 33, No 5, May 1998.

4. Tsuguo Kobayashi, Kazutaka Nogami,

Tsukasa Shirotori, and Yukihiro

Fujimoto. A current-controlled latch

sense amplifier and a static powersaving input buffer for low-power

architecture. IEEE JSSC, Vol 28, No 4,

April 1993.

5. Sandeep Patil, Michael Wieckowski and

Martin Margala. A Self-Biased ChargeTransfer Sense Amplifier . IEEE, 2007.

6. Manoj Sinha, Steven Hsu, Atila

Alvandpour, Wayne Burleson, Ram

Krishmamurthy and Shekhar Borkar.

High-Performance and Low-Voltage

Sense Amplifier Techniques for sub90nm SRAM. IEEE, 2003.

7. Shin-Pao Cheng and Shi-Yu Huang. A

Low-Power SRAM Design Using QuietBitline Architecture. IEEE MTDT 05.

8. Tsuguo Kobayashi, Kazutaka Nogami,

Tsukasa

Shirotori

and

Yukihiro

Fujimoto. A Current-Controlled Latch

Sense Amplifier and a Static PowerSaving Input.

References

1. Travis N. Blalock and Richard C. Jaeger.

A High-Speed Clamped Bit-Line

Current-Mode Sense Amplifier. IEEE

JSSC, Vol 26, No 4, April 1991.

Virtu and Foi

15

Anda mungkin juga menyukai

- Low Power, High Performance PMOS Biased Sense AmplifierDokumen9 halamanLow Power, High Performance PMOS Biased Sense AmplifierIJRASETPublicationsBelum ada peringkat

- VLSI I - V CharacteristicsDokumen46 halamanVLSI I - V CharacteristicsMALATHI .LBelum ada peringkat

- High-Gain Differential Amplifier DesignDokumen21 halamanHigh-Gain Differential Amplifier DesignBodhayan PrasadBelum ada peringkat

- EC2 Exp2 F09Dokumen17 halamanEC2 Exp2 F09Nurul Hanim HashimBelum ada peringkat

- Design and Implementation of High Gain, High Bandwidth CMOS Folded Cascode Operational Transconductance AmplifierDokumen5 halamanDesign and Implementation of High Gain, High Bandwidth CMOS Folded Cascode Operational Transconductance AmplifierChristian Montano GalvezBelum ada peringkat

- Design of High Speed & Power Optimized Sense Amplifier Using Deep Nano CMOS VLSI TechnologyDokumen8 halamanDesign of High Speed & Power Optimized Sense Amplifier Using Deep Nano CMOS VLSI TechnologyIJRASETPublicationsBelum ada peringkat

- CMOS Process FlowDokumen35 halamanCMOS Process Flowag21937570Belum ada peringkat

- Performance Analysis of A Low-Power High-Speed Hybrid 1-Bit Full Adder Circuit Using Cmos Technologies Using CadanceDokumen8 halamanPerformance Analysis of A Low-Power High-Speed Hybrid 1-Bit Full Adder Circuit Using Cmos Technologies Using CadanceAnonymous kw8Yrp0R5r100% (1)

- CMOS Design RulesDokumen21 halamanCMOS Design Rulesrakheep123Belum ada peringkat

- Tiq ComparatorDokumen16 halamanTiq ComparatorKuldeep GuptaBelum ada peringkat

- CMOS Translinear CellsDokumen4 halamanCMOS Translinear CellsSumitChoudharyBelum ada peringkat

- Self Biased High Performance Folded Cascode Cmos OpampDokumen6 halamanSelf Biased High Performance Folded Cascode Cmos OpampArvind MishraBelum ada peringkat

- Design of 12-Bit DAC Using CMOS TechnologyDokumen5 halamanDesign of 12-Bit DAC Using CMOS TechnologysanthoshBelum ada peringkat

- MIM Cap ModelDokumen4 halamanMIM Cap ModelDuc DucBelum ada peringkat

- Two-Stage Operational Amplifier Design Using Gm/Id MethodDokumen7 halamanTwo-Stage Operational Amplifier Design Using Gm/Id Methodabhinav kumarBelum ada peringkat

- SCR-Based ESD Protection Designs For RF ICsDokumen3 halamanSCR-Based ESD Protection Designs For RF ICsjournalBelum ada peringkat

- Sense Amplifier For SRAMDokumen28 halamanSense Amplifier For SRAMPrateek AgrawalBelum ada peringkat

- Cmos Two Stage OpamppublishedDokumen5 halamanCmos Two Stage Opamppublisheddeepak pandeyBelum ada peringkat

- Preventing Latch Up - NationalDokumen2 halamanPreventing Latch Up - Nationalkvpk_vlsiBelum ada peringkat

- Chapter SixDokumen5 halamanChapter Sixyunus memonBelum ada peringkat

- Amplifier Project GradDokumen5 halamanAmplifier Project Gradمحمد قاسم نفل سميرBelum ada peringkat

- CMFB DesignDokumen4 halamanCMFB Designaminkhan83Belum ada peringkat

- A CMOS Bandgap Reference Circuit With Sub-1V OperationDokumen5 halamanA CMOS Bandgap Reference Circuit With Sub-1V Operationbooky_mookyBelum ada peringkat

- Cmos LayoutDokumen13 halamanCmos LayoutshastryBelum ada peringkat

- Design of Two-Stage Operational Amplifier: Shahin Shah (12116053), Abhinav Singhal (12116001)Dokumen2 halamanDesign of Two-Stage Operational Amplifier: Shahin Shah (12116053), Abhinav Singhal (12116001)Shahin ShahBelum ada peringkat

- Brunda V (1PE15EC039) Jigyasa N. Maheshwari (1PE15EC060) : Project Report Phase 1Dokumen43 halamanBrunda V (1PE15EC039) Jigyasa N. Maheshwari (1PE15EC060) : Project Report Phase 1Nikhil NikiBelum ada peringkat

- Low Voltage CMOS SAR ADC DesignDokumen68 halamanLow Voltage CMOS SAR ADC DesignAyush SukaniBelum ada peringkat

- Cmos Electronic PDFDokumen356 halamanCmos Electronic PDFJustin WilliamsBelum ada peringkat

- Unit # 5 Dynamic Cmos and ClockingDokumen15 halamanUnit # 5 Dynamic Cmos and ClockingKiran KumariBelum ada peringkat

- Design of Sense Amplifier For Coupling Suppression by UsingDokumen28 halamanDesign of Sense Amplifier For Coupling Suppression by UsingSai KumarBelum ada peringkat

- 4G WirelessDokumen4 halaman4G Wirelessaminkhan83Belum ada peringkat

- A 180 NM Low Power CMOS Operational Amplifier: Ketan J. Raut R. Kshirsagar A. BhagaliDokumen4 halamanA 180 NM Low Power CMOS Operational Amplifier: Ketan J. Raut R. Kshirsagar A. BhagaliAnika TahsinBelum ada peringkat

- Vlsi ch1Dokumen64 halamanVlsi ch1Nihar ranjan AditBelum ada peringkat

- Short Channel EffectsDokumen27 halamanShort Channel Effectsilg10% (1)

- Layout 02Dokumen38 halamanLayout 02Bulcea PaulBelum ada peringkat

- Understanding About CMOS Fabrication TechnologyDokumen4 halamanUnderstanding About CMOS Fabrication TechnologyJayesh RaghuwanshiBelum ada peringkat

- 7.3 6T SRAM Cell: 7.4 Ring Oscillator 7. Case Studies 7.2 CMOS InverterDokumen4 halaman7.3 6T SRAM Cell: 7.4 Ring Oscillator 7. Case Studies 7.2 CMOS InverterGowtham SpBelum ada peringkat

- Two-Stage CMOS Op-Amp Circuit Design - Jianfeng SunDokumen17 halamanTwo-Stage CMOS Op-Amp Circuit Design - Jianfeng Sunjianfeng sun100% (2)

- Sar Adc 65nm PHD PDFDokumen87 halamanSar Adc 65nm PHD PDFLex LutherBelum ada peringkat

- Question PDFDokumen12 halamanQuestion PDFjushwanth100% (1)

- Design of A Fully Differential High-Speed High-Precision AmplifierDokumen10 halamanDesign of A Fully Differential High-Speed High-Precision Amplifierkirkland1337Belum ada peringkat

- ELEC 353 Latch Up PDFDokumen20 halamanELEC 353 Latch Up PDFShwethBelum ada peringkat

- E3-327 (3) - M SOI MOSFET Oct 2013Dokumen56 halamanE3-327 (3) - M SOI MOSFET Oct 2013Tara VishinBelum ada peringkat

- PROJECT1 S 2013 v2 PDFDokumen4 halamanPROJECT1 S 2013 v2 PDFHarshal SinghBelum ada peringkat

- Rectangular Waveguide To Coax Transition DesignDokumen8 halamanRectangular Waveguide To Coax Transition DesignmmasoumianBelum ada peringkat

- Lecture 12 SRAMDokumen37 halamanLecture 12 SRAMSachin MalikBelum ada peringkat

- Lecture 3 Single Stage AmplifiersDokumen76 halamanLecture 3 Single Stage Amplifierstranhieu_hcmutBelum ada peringkat

- Lect08 GM ID Sizing MethodDokumen55 halamanLect08 GM ID Sizing MethodAmith NayakBelum ada peringkat

- Level Shifter PDFDokumen6 halamanLevel Shifter PDFKAMARUDHEEN KPBelum ada peringkat

- Common Source AmplifierDokumen4 halamanCommon Source AmplifierShoumik DeyBelum ada peringkat

- Layout TutorialDokumen17 halamanLayout TutorialAjinkya KaleBelum ada peringkat

- Ec1401 Vlsi DesignDokumen18 halamanEc1401 Vlsi DesignChaitanya PrabhuBelum ada peringkat

- SRAMDokumen55 halamanSRAMS S DhakadBelum ada peringkat

- Pass Transistor Logic PDFDokumen25 halamanPass Transistor Logic PDFTejas KumbarBelum ada peringkat

- VLSI Questions Answers r3Dokumen79 halamanVLSI Questions Answers r3Gowtham HariBelum ada peringkat

- Chapter 4Dokumen100 halamanChapter 4khgvouy hvogyflBelum ada peringkat

- Network Theory Formula Notesdoc 17Dokumen24 halamanNetwork Theory Formula Notesdoc 17Manish KushwahaBelum ada peringkat

- CMOS Bandgap Reference and Current Reference With Simplified Start-Up CircuitDokumen8 halamanCMOS Bandgap Reference and Current Reference With Simplified Start-Up CircuitSEP-PublisherBelum ada peringkat

- Ee 215 ADokumen8 halamanEe 215 AArjun Singhal100% (1)

- Studying The Behaviour of Lap Splices in RCC BEAMS 09 JulyDokumen4 halamanStudying The Behaviour of Lap Splices in RCC BEAMS 09 JulyGJESRBelum ada peringkat

- Review On Polymer Nanocomposites by Using Various Resins and Nanoclays and Their Applications 06 JuneDokumen8 halamanReview On Polymer Nanocomposites by Using Various Resins and Nanoclays and Their Applications 06 JuneGJESRBelum ada peringkat

- Soil Modification Using Shredded Scrap TiresDokumen4 halamanSoil Modification Using Shredded Scrap TiresIJBSTRBelum ada peringkat

- Utilization of Sugarcane Bagasse Ash (SCBA) As Pozzolanic Material in Concrete A Review 09 AugDokumen3 halamanUtilization of Sugarcane Bagasse Ash (SCBA) As Pozzolanic Material in Concrete A Review 09 AugGJESRBelum ada peringkat

- 02 July 2013Dokumen4 halaman02 July 2013IJBSTRBelum ada peringkat

- StabilizationSolidification and Micro-Structural Analysis of Pond Ash Using Lime 05Dokumen4 halamanStabilizationSolidification and Micro-Structural Analysis of Pond Ash Using Lime 05GJESR0% (1)

- Experimental Modeling of Shear Behavior of Reinforced Concrete Pile Caps 01 AugDokumen9 halamanExperimental Modeling of Shear Behavior of Reinforced Concrete Pile Caps 01 AugfannypramisBelum ada peringkat

- Speed Control of Doubly-Fed Induction Generator Using PI-Controller 06 AugDokumen5 halamanSpeed Control of Doubly-Fed Induction Generator Using PI-Controller 06 AugGJESRBelum ada peringkat

- Single Phase Supply Fed Three Phase Induction Motor Using SVPWM Inverter 04 JuneDokumen4 halamanSingle Phase Supply Fed Three Phase Induction Motor Using SVPWM Inverter 04 JuneGJESRBelum ada peringkat

- Stabilization of Incinerated Hospital Waste Using Different Type of Binders A Review 03 AugDokumen4 halamanStabilization of Incinerated Hospital Waste Using Different Type of Binders A Review 03 AugGJESRBelum ada peringkat

- 07 July 2013Dokumen5 halaman07 July 2013IJBSTRBelum ada peringkat

- Sewage Smells Like A Power Source For Developing 03 MayDokumen2 halamanSewage Smells Like A Power Source For Developing 03 MayGJESRBelum ada peringkat

- Parametric Optimization of Wire EDM by Using Fuzzy Logic 08 AugDokumen5 halamanParametric Optimization of Wire EDM by Using Fuzzy Logic 08 AugGJESRBelum ada peringkat

- 04 July 2013Dokumen7 halaman04 July 2013IJBSTRBelum ada peringkat

- Second Generation Feedstock Biodiesel From Jatropha 01 MayDokumen5 halamanSecond Generation Feedstock Biodiesel From Jatropha 01 MayGJESRBelum ada peringkat

- Performance Estimate of Gateway Discovery Techniques in MANET Internet Connectivity 03 JulyDokumen4 halamanPerformance Estimate of Gateway Discovery Techniques in MANET Internet Connectivity 03 JulyGJESRBelum ada peringkat

- Environmental Impact of Paper Industry 05 JuneDokumen5 halamanEnvironmental Impact of Paper Industry 05 JuneGJESRBelum ada peringkat

- Rabies Vaccine Production From Different Viral Infected Cell Line and Vaccine Production 04 FebDokumen6 halamanRabies Vaccine Production From Different Viral Infected Cell Line and Vaccine Production 04 FebGJESRBelum ada peringkat

- Improving The Behavior of Reinforced Concrete Beam With Varying Lap Splices Length 04 AugDokumen4 halamanImproving The Behavior of Reinforced Concrete Beam With Varying Lap Splices Length 04 AugGJESRBelum ada peringkat

- A Comprehensive Analysis of Space Vector Pulse Width Modulation For 3-Phase Voltage Source Inverter (VSI) 01 JuneDokumen7 halamanA Comprehensive Analysis of Space Vector Pulse Width Modulation For 3-Phase Voltage Source Inverter (VSI) 01 JuneGJESR100% (1)

- Paper Mill Sludge Utilization in Ground Improvement 15 AugDokumen4 halamanPaper Mill Sludge Utilization in Ground Improvement 15 AugGJESRBelum ada peringkat

- Noise Pollution An Overview 13 AugDokumen4 halamanNoise Pollution An Overview 13 AugGJESRBelum ada peringkat

- Design Optimization of The Formation of Boss or Ridge and Passivation of Electrolyte Flow in ECM Process Using CFD Simulation 05 JulyDokumen8 halamanDesign Optimization of The Formation of Boss or Ridge and Passivation of Electrolyte Flow in ECM Process Using CFD Simulation 05 JulyGJESRBelum ada peringkat

- 10 Aug 2013Dokumen9 halaman10 Aug 2013IJBSTRBelum ada peringkat

- Induce Pluripotent Stem Cell Methods, Development and Advancesn 02 FebDokumen11 halamanInduce Pluripotent Stem Cell Methods, Development and Advancesn 02 FebGJESRBelum ada peringkat

- Control Strategies For Water Level Control of Two Tank System 11 AugDokumen7 halamanControl Strategies For Water Level Control of Two Tank System 11 AugGJESRBelum ada peringkat

- Comparison of Traffic Noise Prediction Using FHWA and ERTC Models in Gorakhpur City 16 AugDokumen7 halamanComparison of Traffic Noise Prediction Using FHWA and ERTC Models in Gorakhpur City 16 AugGJESRBelum ada peringkat

- Comparison of Core and Cube Compressive Strength of Hardened Concrete 02 JuneDokumen6 halamanComparison of Core and Cube Compressive Strength of Hardened Concrete 02 JuneGJESRBelum ada peringkat

- Automatic Room Light ControllerDokumen36 halamanAutomatic Room Light Controllerlove2honney100% (1)

- Fisher Fieldvue DVC2000 Digital Valve ControllerDokumen8 halamanFisher Fieldvue DVC2000 Digital Valve ControllerFerio ArsyadBelum ada peringkat

- Report DoordarshanDokumen43 halamanReport Doordarshankavita4123Belum ada peringkat

- Electronics Designer's Cookbook PDFDokumen186 halamanElectronics Designer's Cookbook PDFmathurashwaniBelum ada peringkat

- TM 9 1220 239 34Dokumen130 halamanTM 9 1220 239 34Costas Moraitis100% (1)

- Paper 13-Design of An Intelligent Combat Robot For War FieldDokumen7 halamanPaper 13-Design of An Intelligent Combat Robot For War FieldDhruv DalwadiBelum ada peringkat

- Tape Op 128Dokumen75 halamanTape Op 128Cleef0% (1)

- S M00Dokumen14 halamanS M00Victoria Si Alexei DnestreanBelum ada peringkat

- Handbook of Simplified Solid State Design LENK J 1978Dokumen448 halamanHandbook of Simplified Solid State Design LENK J 1978Ionutz07iuliu100% (3)

- CMOS Three Axis Hall Sensor and Joystick Application Schott3axisJoystickDokumen4 halamanCMOS Three Axis Hall Sensor and Joystick Application Schott3axisJoystickbesttv046936Belum ada peringkat

- PFC Strategies in Light of en 61000-3-2Dokumen9 halamanPFC Strategies in Light of en 61000-3-2allex_liuBelum ada peringkat

- ECPC29 CT1 SyllabusDokumen56 halamanECPC29 CT1 SyllabusAishwarya RBelum ada peringkat

- 25 KW X-Band Transceiver DownmastDokumen132 halaman25 KW X-Band Transceiver DownmastArshad Jummani67% (3)

- ACL User Manual PDFDokumen96 halamanACL User Manual PDFChino Abad SalinasBelum ada peringkat

- NEET AIPMT 2010 Preliminary Original Solved Question PaperDokumen48 halamanNEET AIPMT 2010 Preliminary Original Solved Question PaperShaileshBelum ada peringkat

- Operational Amplifiers - DCDokumen6 halamanOperational Amplifiers - DCJoseGarciaRuizBelum ada peringkat

- 8200CD-Audiolab Service Manual v01 20101014Dokumen28 halaman8200CD-Audiolab Service Manual v01 20101014Anonymous zuM28o8IyNBelum ada peringkat

- Cassette Recording Buying Guide-1974 USADokumen114 halamanCassette Recording Buying Guide-1974 USAdanilo kassiusBelum ada peringkat

- AD5620 AnalogDevicesDokumen28 halamanAD5620 AnalogDevicesPablo AllosiaBelum ada peringkat

- Automatic Bottle Filling System FinalDokumen51 halamanAutomatic Bottle Filling System Finalsaqibusman0% (1)

- Regulation - 2010: K.S.Rangasamy College of Technology, Tiruchengode - 637 215Dokumen3 halamanRegulation - 2010: K.S.Rangasamy College of Technology, Tiruchengode - 637 215Latta SakthyyBelum ada peringkat

- Digital Signal Processing DSP 38.2Dokumen858 halamanDigital Signal Processing DSP 38.2ZaidYemenBelum ada peringkat

- Electronic Devices and Circuits - I. J. NagrathDokumen156 halamanElectronic Devices and Circuits - I. J. Nagrathprabu0% (1)

- YG602020 InnotionDokumen9 halamanYG602020 Innotiongonzalo2205Belum ada peringkat

- Kentec Catalogue11-12Dokumen112 halamanKentec Catalogue11-12Walid Aly100% (1)

- Hsu Research STF2 SubwooferDokumen8 halamanHsu Research STF2 SubwooferTomBelum ada peringkat

- Bulkhead Module (32A Module) : LocationDokumen8 halamanBulkhead Module (32A Module) : LocationInjeletro DieselBelum ada peringkat

- Planar4 System CatalogDokumen194 halamanPlanar4 System CatalogMohamed OmarBelum ada peringkat

- LM - 1875 PDFDokumen16 halamanLM - 1875 PDFDaniel Arcia JiménezBelum ada peringkat

- PPRS Training ManualDokumen145 halamanPPRS Training ManualMahesh M P NairBelum ada peringkat