Rr720204 Embedded Systems

Diunggah oleh

andhracollegesHak Cipta

Format Tersedia

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniHak Cipta:

Format Tersedia

Rr720204 Embedded Systems

Diunggah oleh

andhracollegesHak Cipta:

Format Tersedia

www.andhracolleges.

com The Complete Information About Colleges in Andhra Pradesh

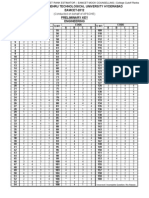

Code No: RR420204 Set No. 1

IV B.Tech II Semester Supplimentary Examinations, May 2008

EMBEDDED SYSTEMS

( Common to Electrical & Electronic Engineering and Electronics &

Communication Engineering)

Time: 3 hours Max Marks: 80

Answer any FIVE Questions

All Questions carry equal marks

www.andhracolleges.com

⋆⋆⋆⋆⋆

1. List a pair of design metrics that may compete with one another, providing an

intuitive explanation of the reason behind the competition. [16]

2. (a) What is a single-purpose processor? What are the benefits of choosing a

single-purpose processor to against a general-purpose processor?

(b) Draw the basic architecture of single-purpose processor. [8+8]

3. (a) Define instruction? Explain the instruction set format?

(b) Explain different addressing modes with an example. [8+8]

4. Explain the need of special architecture for pipelining and parallelism. [16]

5. Explain how to compute state machines in sequential programming language. [16]

6. (a) Explain rate monotonic priority scheduling algorithm with an example.

(b) Explain deadline monotonic priority assignment scheduling algorithm with an

example. [8+8]

www.andhracolleges.com

7. Explain the parallel evolution of compilation and synthesis with the co-design lad-

der. [16]

8. (a) What is hardware/software co-simulation?

(b) What is a key method for speeding up such simulation? [8+8]

⋆⋆⋆⋆⋆

Seminar Topics - Scholarships - Admission/Entrance Exam Notifications

1 ofUSA-UK-Australia-Germany-France-NewZealand

1 Universities List

www.andhracolleges.com Engineering-MBA-MCA-Medical-Pharmacy-B.Ed-Law Colleges Information

www.andhracolleges.com The Complete Information About Colleges in Andhra Pradesh

Code No: RR420204 Set No. 2

IV B.Tech II Semester Supplimentary Examinations, May 2008

EMBEDDED SYSTEMS

( Common to Electrical & Electronic Engineering and Electronics &

Communication Engineering)

Time: 3 hours Max Marks: 80

Answer any FIVE Questions

All Questions carry equal marks

www.andhracolleges.com

⋆⋆⋆⋆⋆

1. List a pair of design metrics that may compete with one another, providing an

intuitive explanation of the reason behind the competition. [16]

2. Design a 3-bit counter that counts the following sequence: 1,2,4,5,7,1,2,?.. start

from a state diagram, draw the state table, minimize the logic, and draw the final

circuit. [16]

3. (a) Explain the factors effecting selection of a microprocessor.

(b) Compare the general purpose processor, microcontroller and Digital signal

processor. [8+8]

4. Explain different data addressing modes of digital signal processor. [16]

5. Explain how to compute state machines in sequential programming language. [16]

6. (a) Explain different processes scheduler in a single general purpose processor.

(b) Explain different types of scheduling algorithms in a single processor environ-

ment. [8+8]

www.andhracolleges.com

7. Give overview of the various levels of synthesis with Gazki Y-chart. [16]

8. (a) What is hardware /software co-design?

(b) Explain temporal and spatial thinking in hardware/software co-design? [8+8]

⋆⋆⋆⋆⋆

Seminar Topics - Scholarships - Admission/Entrance Exam Notifications

1 ofUSA-UK-Australia-Germany-France-NewZealand

1 Universities List

www.andhracolleges.com Engineering-MBA-MCA-Medical-Pharmacy-B.Ed-Law Colleges Information

www.andhracolleges.com The Complete Information About Colleges in Andhra Pradesh

Code No: RR420204 Set No. 3

IV B.Tech II Semester Supplimentary Examinations, May 2008

EMBEDDED SYSTEMS

( Common to Electrical & Electronic Engineering and Electronics &

Communication Engineering)

Time: 3 hours Max Marks: 80

Answer any FIVE Questions

All Questions carry equal marks

www.andhracolleges.com

⋆⋆⋆⋆⋆

1. (a) What is an embedded system? Why is it so hard to define?

(b) List the applications of embedded systems. [8+8]

2. (a) What is a single-purpose processor? What are the benefits of choosing a

single-purpose processor to against a general-purpose processor?

(b) Draw the basic architecture of single-purpose processor. [8+8]

3. (a) Explain the factors effecting selection of a microprocessor.

(b) Compare the general purpose processor, microcontroller and Digital signal

processor. [8+8]

4. (a) Give the bus structure for digital signal processor.

(b) Explain the need for more buses in DSP architecture. [8+8]

5. Explain the state chart language with elevator controller example. [16]

6. Explain the concept of synchronization among concurrent processes by condition

www.andhracolleges.com

variables with an example. [8+8]

7. Explain the parallel evolution of compilation and synthesis with the co-design lad-

der. [16]

8. (a) Explain the three types of cores such as hard, soft and firm cores.

(b) Show the correspondence of the three types of cores with Gazki’s Y-chart.

[8+8]

⋆⋆⋆⋆⋆

Seminar Topics - Scholarships - Admission/Entrance Exam Notifications

1 ofUSA-UK-Australia-Germany-France-NewZealand

1 Universities List

www.andhracolleges.com Engineering-MBA-MCA-Medical-Pharmacy-B.Ed-Law Colleges Information

www.andhracolleges.com The Complete Information About Colleges in Andhra Pradesh

Code No: RR420204 Set No. 4

IV B.Tech II Semester Supplimentary Examinations, May 2008

EMBEDDED SYSTEMS

( Common to Electrical & Electronic Engineering and Electronics &

Communication Engineering)

Time: 3 hours Max Marks: 80

Answer any FIVE Questions

All Questions carry equal marks

www.andhracolleges.com

⋆⋆⋆⋆⋆

1. (a) What is an embedded system? Why is it so hard to define?

(b) List the applications of embedded systems. [8+8]

2. (a) Build a 2-input AND gate using a minimum number of CMOS transistors.

Explain with truth table.

(b) Build a 2-input OR gate using a minimum number of CMOS transistors.

Explain with truth table. [8+8]

3. (a) Explain the factors effecting selection of a microprocessor.

(b) Compare the general purpose processor, microcontroller and Digital signal

processor. [8+8]

4. Explain the architectural features of ADSP 21065. [16]

5. Explain in detail about Hierarchical/Concurrent state machine models. [16]

6. Explain in detail about data flow model with an example. [16]

www.andhracolleges.com

7. (a) Explain in detail about the combinational logic synthesis approach?

(b) Explain in detail about FSM synthesis. [8+8]

8. (a) What is hardware /software co-design?

(b) Explain temporal and spatial thinking in hardware/software co-design? [8+8]

⋆⋆⋆⋆⋆

Seminar Topics - Scholarships - Admission/Entrance Exam Notifications

1 ofUSA-UK-Australia-Germany-France-NewZealand

1 Universities List

www.andhracolleges.com Engineering-MBA-MCA-Medical-Pharmacy-B.Ed-Law Colleges Information

Anda mungkin juga menyukai

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryDari EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryPenilaian: 3.5 dari 5 bintang3.5/5 (231)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Dari EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Penilaian: 4.5 dari 5 bintang4.5/5 (121)

- Grit: The Power of Passion and PerseveranceDari EverandGrit: The Power of Passion and PerseverancePenilaian: 4 dari 5 bintang4/5 (588)

- Never Split the Difference: Negotiating As If Your Life Depended On ItDari EverandNever Split the Difference: Negotiating As If Your Life Depended On ItPenilaian: 4.5 dari 5 bintang4.5/5 (838)

- The Little Book of Hygge: Danish Secrets to Happy LivingDari EverandThe Little Book of Hygge: Danish Secrets to Happy LivingPenilaian: 3.5 dari 5 bintang3.5/5 (400)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaDari EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaPenilaian: 4.5 dari 5 bintang4.5/5 (266)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeDari EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifePenilaian: 4 dari 5 bintang4/5 (5794)

- Rise of ISIS: A Threat We Can't IgnoreDari EverandRise of ISIS: A Threat We Can't IgnorePenilaian: 3.5 dari 5 bintang3.5/5 (137)

- Her Body and Other Parties: StoriesDari EverandHer Body and Other Parties: StoriesPenilaian: 4 dari 5 bintang4/5 (821)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreDari EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You ArePenilaian: 4 dari 5 bintang4/5 (1090)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyDari EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyPenilaian: 3.5 dari 5 bintang3.5/5 (2259)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersDari EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersPenilaian: 4.5 dari 5 bintang4.5/5 (345)

- Shoe Dog: A Memoir by the Creator of NikeDari EverandShoe Dog: A Memoir by the Creator of NikePenilaian: 4.5 dari 5 bintang4.5/5 (537)

- The Emperor of All Maladies: A Biography of CancerDari EverandThe Emperor of All Maladies: A Biography of CancerPenilaian: 4.5 dari 5 bintang4.5/5 (271)

- Team of Rivals: The Political Genius of Abraham LincolnDari EverandTeam of Rivals: The Political Genius of Abraham LincolnPenilaian: 4.5 dari 5 bintang4.5/5 (234)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceDari EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RacePenilaian: 4 dari 5 bintang4/5 (895)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureDari EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FuturePenilaian: 4.5 dari 5 bintang4.5/5 (474)

- On Fire: The (Burning) Case for a Green New DealDari EverandOn Fire: The (Burning) Case for a Green New DealPenilaian: 4 dari 5 bintang4/5 (74)

- The Yellow House: A Memoir (2019 National Book Award Winner)Dari EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Penilaian: 4 dari 5 bintang4/5 (98)

- The Unwinding: An Inner History of the New AmericaDari EverandThe Unwinding: An Inner History of the New AmericaPenilaian: 4 dari 5 bintang4/5 (45)

- Programmable Logic Controller (PLC)Dokumen85 halamanProgrammable Logic Controller (PLC)riajdcBelum ada peringkat

- Transceiver and System Design For Digital Communications (PDFDrive)Dokumen554 halamanTransceiver and System Design For Digital Communications (PDFDrive)Elielton SilvaBelum ada peringkat

- Eamcet 2002 Engineering PaperDokumen14 halamanEamcet 2002 Engineering Paperandhracolleges0% (1)

- TAC50 20technical 20information PDFDokumen110 halamanTAC50 20technical 20information PDFLuis Bazan33% (3)

- Micom Alstom P141, P142, P143, P144 & P145: Feeder Management RelayDokumen38 halamanMicom Alstom P141, P142, P143, P144 & P145: Feeder Management RelayNur Farahatan100% (2)

- Networking AssignmentDokumen53 halamanNetworking AssignmentManish SahBelum ada peringkat

- Scan Plan Paut-Mc-02-Corregido PDFDokumen5 halamanScan Plan Paut-Mc-02-Corregido PDFCarlos TijerinaBelum ada peringkat

- EAMCET 2014 Agriculture & Medical Preliminary Answer KeysDokumen1 halamanEAMCET 2014 Agriculture & Medical Preliminary Answer KeysLohith_EnggBelum ada peringkat

- Eamcet 2014 Medical Question Paper With Key Solutions AndhracollegesDokumen62 halamanEamcet 2014 Medical Question Paper With Key Solutions Andhracollegesandhracolleges100% (1)

- Eamcet Agriculture Last Ranks Cutoffs Andhracolleges Eamcet 2013 CutoffsDokumen3 halamanEamcet Agriculture Last Ranks Cutoffs Andhracolleges Eamcet 2013 Cutoffsandhracolleges33% (3)

- Andhracollege Eamcet 2014 Engineering Question Paper With Key SolutionsDokumen62 halamanAndhracollege Eamcet 2014 Engineering Question Paper With Key Solutionsandhracolleges50% (4)

- Eamcet 2014 Engineering Key Solutions AndhracollegesDokumen42 halamanEamcet 2014 Engineering Key Solutions Andhracollegesandhracolleges75% (8)

- Eamcet 2012 Engineering Paper KeyDokumen1 halamanEamcet 2012 Engineering Paper KeyandhracollegesBelum ada peringkat

- Eamcet 2014 Engineering Key SolutionsDokumen42 halamanEamcet 2014 Engineering Key Solutionsandhracolleges100% (1)

- Eamcet 2006 Engineering PaperDokumen14 halamanEamcet 2006 Engineering PaperandhracollegesBelum ada peringkat

- Eamcet 2007 Engineering PaperDokumen13 halamanEamcet 2007 Engineering Paperandhracolleges100% (1)

- Polycet 2014 Question PaperDokumen24 halamanPolycet 2014 Question PaperandhracollegesBelum ada peringkat

- Eamcet 2010 Medical PaperDokumen63 halamanEamcet 2010 Medical PaperandhracollegesBelum ada peringkat

- Eamcet 2004 Engineering PaperDokumen12 halamanEamcet 2004 Engineering PaperandhracollegesBelum ada peringkat

- EAMCET NotificationDokumen3 halamanEAMCET NotificationKeerthiPratheek ReddyBelum ada peringkat

- Eamcet 2009 Engineering Physics PaperDokumen19 halamanEamcet 2009 Engineering Physics PaperandhracollegesBelum ada peringkat

- Eamcet 2003 Engineering PaperDokumen12 halamanEamcet 2003 Engineering Paperandhracolleges100% (1)

- Eamcet 2001 Engineering PaperDokumen14 halamanEamcet 2001 Engineering PaperandhracollegesBelum ada peringkat

- EAMCET Engineering Entrance Solved Paper 2000Dokumen13 halamanEAMCET Engineering Entrance Solved Paper 2000Giri NathBelum ada peringkat

- Icet-2014-Important Instructions BookletDokumen3 halamanIcet-2014-Important Instructions BookletandhracollegesBelum ada peringkat

- TS ICET Syllabus and Exam PatternDokumen5 halamanTS ICET Syllabus and Exam PatterngayathriBelum ada peringkat

- Eamcet Pharmacy College Fee DetailsDokumen14 halamanEamcet Pharmacy College Fee DetailsandhracollegesBelum ada peringkat

- FeeDokumen34 halamanFeeThanniru VenkateshBelum ada peringkat

- 100 Baset Crossover CableDokumen7 halaman100 Baset Crossover CableBeker BojanBelum ada peringkat

- ParameterDokumen175 halamanParameterDilip GamiBelum ada peringkat

- Chapter 9 - FMIDokumen4 halamanChapter 9 - FMIMiguel Angel ValderramaBelum ada peringkat

- TX R&S SU4200 - Operating - ManualDokumen188 halamanTX R&S SU4200 - Operating - ManualCiobanita Paul Adrian65100% (1)

- Fractional-N Frequency SynthesizerDokumen5 halamanFractional-N Frequency SynthesizerbaymanBelum ada peringkat

- Unit: Data Link Layer (Marks 5) Computer Network BSC 6 Semester Sub: Computer Science (General) Data Link LayerDokumen3 halamanUnit: Data Link Layer (Marks 5) Computer Network BSC 6 Semester Sub: Computer Science (General) Data Link LayerNur ZuraidaBelum ada peringkat

- Colossus WorksheetDokumen3 halamanColossus WorksheetKateBelum ada peringkat

- 2014-2019 RLX VSA DTC Troubleshooting - 51-12, 51-80, 52-11Dokumen4 halaman2014-2019 RLX VSA DTC Troubleshooting - 51-12, 51-80, 52-11Kevin SanchezBelum ada peringkat

- Simple 10 Bit DAC For The ArduinoDokumen5 halamanSimple 10 Bit DAC For The ArduinogacalaBelum ada peringkat

- Presented By: Subhradeep Mitra & Debanjan MukherjeeDokumen32 halamanPresented By: Subhradeep Mitra & Debanjan MukherjeeAkhilesh ChoudharyBelum ada peringkat

- Esp32 Datasheet enDokumen70 halamanEsp32 Datasheet enBianca Maria SpînuBelum ada peringkat

- Advances in Bipolar Junction Transistor ModelingDokumen4 halamanAdvances in Bipolar Junction Transistor Modelingelectroamit123Belum ada peringkat

- Smart Metering Sensor Board 2.0engDokumen46 halamanSmart Metering Sensor Board 2.0engStefan S KiralyBelum ada peringkat

- DSD TECH HM-10 DatasheetDokumen38 halamanDSD TECH HM-10 Datasheetteguh ari bowoBelum ada peringkat

- Catalog Commax 2012 2013Dokumen28 halamanCatalog Commax 2012 2013MesterulTauBelum ada peringkat

- Precision Timer: Connection DiagramDokumen5 halamanPrecision Timer: Connection DiagramValentin RaduBelum ada peringkat

- Sucoflex 104 PBDokumen13 halamanSucoflex 104 PBdspa123Belum ada peringkat

- Kick NEKXA Buds Z10 User ManualDokumen1 halamanKick NEKXA Buds Z10 User ManualllaonunBelum ada peringkat

- PHÂN TÍCH 30 NGÀNH HÀNG - Trang Tính1Dokumen12 halamanPHÂN TÍCH 30 NGÀNH HÀNG - Trang Tính1K60 Nguyễn Hữu Yên HàBelum ada peringkat

- History of ComputerDokumen8 halamanHistory of Computeramihaninternetshop aisBelum ada peringkat

- Diode: For Data Diodes, See - For Other Uses, SeeDokumen52 halamanDiode: For Data Diodes, See - For Other Uses, SeenafeesBelum ada peringkat

- Lab 2: I-V Characteristics of Diodes: Waveform DisplayDokumen6 halamanLab 2: I-V Characteristics of Diodes: Waveform DisplaywipernextBelum ada peringkat

- Error Detection and Correction Techniques in Computer Networks PDFDokumen2 halamanError Detection and Correction Techniques in Computer Networks PDFJohn100% (1)

- Pic Microcontroller Block DiagramDokumen15 halamanPic Microcontroller Block DiagramNandaKiranBelum ada peringkat