Laboratorio 5

Diunggah oleh

Anonymous kOqq2PN0 penilaian0% menganggap dokumen ini bermanfaat (0 suara)

10 tayangan5 halamanJudul Asli

laboratorio 5.docx

Hak Cipta

© © All Rights Reserved

Format Tersedia

DOCX, PDF, TXT atau baca online dari Scribd

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniHak Cipta:

© All Rights Reserved

Format Tersedia

Unduh sebagai DOCX, PDF, TXT atau baca online dari Scribd

0 penilaian0% menganggap dokumen ini bermanfaat (0 suara)

10 tayangan5 halamanLaboratorio 5

Diunggah oleh

Anonymous kOqq2PNHak Cipta:

© All Rights Reserved

Format Tersedia

Unduh sebagai DOCX, PDF, TXT atau baca online dari Scribd

Anda di halaman 1dari 5

MINITRMINO

Es una expresin algebraica booleana de n variables booleanas (ej: bits) que

solamente se evala como verdadera (1) para una nica combinacin de esas

variables, es la expresin opuesta a la maxterm

La notacin es la siguiente: \Sigma m(x_1,\,x_n)

x_1\, x_2\,

0

0

0

1

1

0

1

1

Esto es

Coincidencia

1

0

0

1

\Sigma m(0,\,3)

ya que la primera fila (0) y la ltima (3) tiene como valor 1 del minterm.

Un minterm se forma multiplicando (AND lgico) todas las variables, negando

aquellas que valen 0 en la combinacin para la cual queremos que el minterm

valga 1. Para n variables booleanas, existen 2^n minterms, uno para cada

posible combinacin de ellas.

Se emplean para obtener la forma cannica disyuntiva de una funcin lgica.

Notacin abreviada[editar]

Es habitual emplear la notacin mi para referirse al minterm i-simo en

concreto. El minterm i es aquel que vale 1 slo para la combinacin de

variables booleanas que codifican en base 2 dicho nmero i.

Por ejemplo:

- Para 3 variables {a,b,c}, el minterm m5 ser aquel que solamente vale 1 para

la combinacin abc=101(=5 en base 2), esto es, m5=a.b.c

- Para 4 variables {a,b,c,d}, el minterm m5 es m5=a.b.c.d (abcd=0101=5)

- El minterm m13 para 5 variables ser m13=a.b.c.d.e (abcde=01101=13)

Ejemplo[editar]

Basados en una funcin de 3 variables (a, b, c), y considerando la dificultad de

poner el negado de una variable como una barrita superior (aunque el

apstrofo es tambin utilizado), tenemos lo siguiente:

f(a,b,c) = (a+bc+ac)b <-Forma no normalizada

+Intentaremos expresarlo en mintrminos, por lo cual demanda una

interpretacin normalizada de Suma de Productos (Normalizada = SP)

Expresin

Comentarios

= (a+bc+ac)b

Variable "b" entre parntesis se incluye en cada producto

= (a*b)+(bc*b)+(ac*b) Eliminar signo de multiplicacin

= (ab)+(bbc)+(abc)

Eliminar trminos por ley de identidad

= (ab)+(abc)

Forma normalizada (SP)

+Intentaremos expresarlo en mintrminos, basados de la forma normalizada

"Suma de Productos"

Expresin

Comentarios

= (ab)+(abc)

Agregar variables faltantes a cada trmino

= (ab)*(c+c)+(abc)

Despejar en la forma SP

= (ab*c)+(ab*c)+(abc) Eliminar signo de multiplicacin

= (abc)+(abc)+(abc)

Forma cannica

= m7 + m6 + m3 Forma expresada en suma de mintrminos

= m(3,6,7) Forma en funcin de mintrminos

+De este modo tenemos los mintrminos, lo cual facilita (sobre todo cuando

son 3 o ms variables) encontrar la solucin de la funcin. En la tabla de

verdad, los mintrminos se representan con un 1 cuando estn presentes.

Recordemos que cada negado en cada trmino vale 0.

+He aqu la comprobacin:

a

0

0

0

0

1

1

1

1

b

0

0

1

1

0

0

1

1

c

0

1

0

1

0

1

0

1

(a+bc+ac)b min

0

0

0

0

0

0

1

1

0

0

0

0

1

1

1

1

MAXITRMINO

Es una expresin algebraica booleana de n variables booleanas (ej: bits) que

solamente se evala como falsa (0) para una nica combinacin de esas

variables.

La notacin es la siguiente: \Pi M(x_1,\,x_n)

Donde los valores x (1...n) son el nmero de las filas en que los valores que

tienen 0 en la tabla de verdad.

Por ejemplo para esta tabla de verdad para la lgica de coincidencia

x_1\, x_2\,

0

0

0

1

1

0

1

1

esto es

Coincidencia

1

0

0

1

\Pi M(1,\,2)

ya que la segunda fila (1) y la tercera (2) tiene como valor 0 del maxterm

Por ejemplo, el Maxterm a+b+c solamente vale 0 para la combinacin a=1,

b=0, c=1 ; para cualquier otra combinacin, esa expresin vale 1.

Un Maxterm se forma sumando (OR lgico) todas las variables, negando

aquellas que valen 1 en la combinacin para la cual queremos que el Maxterm

valga 0. Para n variables booleanas, existen 2^n Maxterms, uno para cada

posible combinacin de ellas.

Se emplean para obtener la forma cannica conjuntiva de una funcin lgica.

VHDL

Es el acrnimo que representa la combinacin de VHSIC y HDL, donde VHSIC

es el acrnimo de Very High Speed Integrated Circuit y HDL es a su vez el

acrnimo de Hardware Description Language.

Es un lenguaje definido por el IEEE (Institute of Electrical and Electronics

Engineers) (ANSI/IEEE 1076-1993) usado por ingenieros para describir circuitos

digitales. Otros mtodos para disear circuitos son la captura de esquemas

(con herramientas CAD) y los diagramas de bloques, pero stos no son

prcticos en diseos complejos. Otros lenguajes para el mismo propsito son

Verilog y ABEL.

Aunque puede ser usado de forma general para describir cualquier circuito se

usa principalmente para programar PLD (Programable Logic Device Dispositivo Lgico Programable), FPGA (Field Programmable Gate Array), ASIC y

similares.

FPGA

Es un dispositivo semiconductor que contiene bloques de lgica cuya

interconexin y funcionalidad puede ser configurada 'in situ' mediante un

lenguaje de descripcin especializado. La lgica programable puede reproducir

desde funciones tan sencillas como las llevadas a cabo por una puerta lgica o

un sistema combinacional hasta complejos sistemas en un chip.

Las FPGAs se utilizan en aplicaciones similares a los ASICs sin embargo son

ms lentas, tienen un mayor consumo de potencia y no pueden abarcar

sistemas tan complejos como ellos. A pesar de esto, las FPGAs tienen las

ventajas de ser reprogramables (lo que aade una enorme flexibilidad al flujo

de diseo), sus costes de desarrollo y adquisicin son mucho menores para

pequeas cantidades de dispositivos y el tiempo de desarrollo es tambin

menor.

Ciertos fabricantes cuentan con FPGAs que slo se pueden programar una vez,

por lo que sus ventajas e inconvenientes se encuentran a medio camino entre

los ASICs y las FPGAs reprogramables.

Histricamente las FPGA surgen como una evolucin de los conceptos

desarrollados en las PAL y los CPLD.

Anda mungkin juga menyukai

- Ensayo Sobre HaskellDokumen7 halamanEnsayo Sobre HaskellCarlos CruzBelum ada peringkat

- Laboratorio Taller 7okDokumen19 halamanLaboratorio Taller 7okCRKarlinhoBelum ada peringkat

- ASIO4ALL v2 - Instruction ManualDokumen20 halamanASIO4ALL v2 - Instruction ManualCiceron21Belum ada peringkat

- Guia de Implementacion y Estrategia de AzureDokumen165 halamanGuia de Implementacion y Estrategia de Azureensayandocorreo100% (3)

- Tarea Modelo MCCALLDokumen10 halamanTarea Modelo MCCALLKenyi RodriguezBelum ada peringkat

- PCBD - PCBD-212 - Formatoalumnotrabajofinal - Docx (2) TerminadoDokumen6 halamanPCBD - PCBD-212 - Formatoalumnotrabajofinal - Docx (2) Terminadojoel antonioBelum ada peringkat

- Clase #1 - BienvenidaDokumen17 halamanClase #1 - BienvenidaCarlos Mario Perez CastillaBelum ada peringkat

- A4 - Lógica & Programación EstructuradaDokumen10 halamanA4 - Lógica & Programación EstructuradaIgnacioRodriguezBelum ada peringkat

- Fanuc KukaDokumen250 halamanFanuc KukaClecio de PaulaBelum ada peringkat

- SAMSUNG UN32F5000AG Se Queman Los Leds Del BacklightDokumen7 halamanSAMSUNG UN32F5000AG Se Queman Los Leds Del BacklightLucioLopezBelum ada peringkat

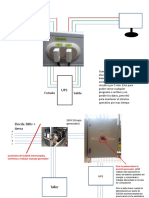

- Ups ConexionDokumen2 halamanUps ConexionPablo IbañezBelum ada peringkat

- QUINTA PARTE PROGRAMACION SHELL EN LINUX LIC. VICTOR POZO DÍAZ - UnlockedDokumen25 halamanQUINTA PARTE PROGRAMACION SHELL EN LINUX LIC. VICTOR POZO DÍAZ - UnlockedA T LBelum ada peringkat

- ISA Server 2004 como Firewall de AplicaciónDokumen75 halamanISA Server 2004 como Firewall de AplicaciónJorge MorenoBelum ada peringkat

- Los Computadores ModernosDokumen11 halamanLos Computadores ModernosBritneyBelum ada peringkat

- Lista de Precios Trascentek SAS 07 09 2020 PDFDokumen19 halamanLista de Precios Trascentek SAS 07 09 2020 PDFMAKRO SERVERBelum ada peringkat

- Informe Mapeo de Rutas BGPDokumen3 halamanInforme Mapeo de Rutas BGPThiago RaulBelum ada peringkat

- Actividad 1 2P TNSDokumen6 halamanActividad 1 2P TNSLa CerrajeriaBelum ada peringkat

- Evidencia de Aprendizaje - 2Dokumen59 halamanEvidencia de Aprendizaje - 2Arias RobertoBelum ada peringkat

- Ccna Semestre 1 Examen 10 (100%)Dokumen8 halamanCcna Semestre 1 Examen 10 (100%)rukismenBelum ada peringkat

- Redes-ComputadorasDokumen3 halamanRedes-ComputadorasDavid TorresBelum ada peringkat

- SNMP Desde PHP PDFDokumen129 halamanSNMP Desde PHP PDFAlejandro HenriquesBelum ada peringkat

- Ingeniería en Computación Inteligente 2017Dokumen4 halamanIngeniería en Computación Inteligente 2017jacer20Belum ada peringkat

- Utilerias Del SistemaDokumen24 halamanUtilerias Del SistemaJeRaHiBelum ada peringkat

- Diferencia Entre Un Traductor y Un Compilador PDFDokumen6 halamanDiferencia Entre Un Traductor y Un Compilador PDFBenjamin Viramontes JuarezBelum ada peringkat

- 02 Instala APA 6 en Word2010 o MenorDokumen3 halaman02 Instala APA 6 en Word2010 o MenorLuis Argueta MogollónBelum ada peringkat

- Temario Oracle d80343Dokumen3 halamanTemario Oracle d80343loko8585Belum ada peringkat

- SOADokumen38 halamanSOAkirstie100% (2)

- 1.0.5-Packet Tracer - Exploración de Modo Lógico y FísicoDokumen5 halaman1.0.5-Packet Tracer - Exploración de Modo Lógico y FísicoErick VargasBelum ada peringkat

- Contadores PLCDokumen10 halamanContadores PLCLuis Angel Soto EscribaBelum ada peringkat

- Introducción a compiladores: fases y tipos de traductoresDokumen35 halamanIntroducción a compiladores: fases y tipos de traductoresjdap2000-1100% (1)