IPD075N03LG

Diunggah oleh

George PietraruHak Cipta

Format Tersedia

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniHak Cipta:

Format Tersedia

IPD075N03LG

Diunggah oleh

George PietraruHak Cipta:

Format Tersedia

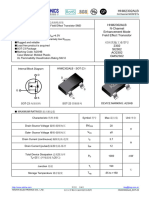

Type

OptiMOS3 Power-Transistor

IPD075N03L G

IPF075N03L G

IPS075N03L G

IPU075N03L G

Product Summary

Features

Fast switching MOSFET for SMPS

Optimized technology for DC/DC converters

V DS

30

R DS(on),max

7.5

ID

50

1)

Qualified according to JEDEC for target applications

N-channel, logic level

Excellent gate charge x R DS(on) product (FOM)

Very low on-resistance R DS(on)

Avalanche rated

Pb-free plating; RoHS compliant

Type

IPD075N03L G

IPF075N03L G

IPS075N03L G

IPU075N03L G

Package

PG-TO252-3-11

PG-TO252-3-23

PG-TO251-3-11

PG-TO251-3-21

Marking

075N03L

075N03L

075N03L

075N03L

Maximum ratings, at T j=25 C, unless otherwise specified

Parameter

Symbol Conditions

Continuous drain current

ID

Value

V GS=10 V, T C=25 C

50

V GS=10 V, T C=100 C

43

V GS=4.5 V, T C=25 C

49

V GS=4.5 V,

T C=100 C

35

Unit

A

Pulsed drain current2)

I D,pulse

T C=25 C

350

Avalanche current, single pulse 3)

I AS

T C=25 C

50

Avalanche energy, single pulse

E AS

I D=12 A, R GS=25

50

mJ

Gate source voltage

V GS

20

1)

Rev. 1.1

J-STD20 and JESD22

page 1

2009-01-14

IPD075N03L G

IPF075N03L G

IPS075N03L G

IPU075N03L G

Maximum ratings, at T j=25 C, unless otherwise specified

Parameter

Symbol Conditions

Power dissipation

P tot

Operating and storage temperature

T j, T stg

Value

T C=25 C

IEC climatic category; DIN IEC 68-1

Parameter

Unit

47

-55 ... 175

55/175/56

Values

Symbol Conditions

Unit

min.

typ.

max.

3.2

minimal footprint

75

6 cm cooling area 4)

50

Thermal characteristics

Thermal resistance, junction - case

R thJC

SMD version, device on PCB

R thJA

K/W

Electrical characteristics, at T j=25 C, unless otherwise specified

Static characteristics

Drain-source breakdown voltage

V (BR)DSS V GS=0 V, I D=1 mA

30

Gate threshold voltage

V GS(th)

V DS=V GS, I D=250 A

2.2

Zero gate voltage drain current

I DSS

V DS=30 V, V GS=0 V,

T j=25 C

0.1

V DS=30 V, V GS=0 V,

T j=125 C

10

100

I GSS

V GS=20 V, V DS=0 V

10

100

nA

R DS(on)

V GS=4.5 V, I D=30 A

9.1

11.4

V GS=10 V, I D=30 A

6.3

7.5

1.3

30

61

Gate-source leakage current

Drain-source on-state resistance

5)

Gate resistance

RG

Transconductance

g fs

2)

See figure 3 for more detailed information

3)

See figure 13 for more detailed information

|V DS|>2|I D|R DS(on)max,

I D=30 A

4)

Device on 40 mm x 40 mm x 1.5 mm epoxy PCB FR4 with 6 cm2 (one layer, 70 m thick) copper area for drain

connection. PCB is vertical in still air.

5)

Measured from drain tab to source pin

Rev. 1.1

page 2

2009-01-14

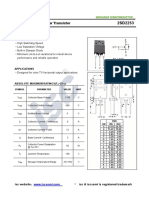

Parameter

IPD075N03L G

IPF075N03L G

IPS075N03L G

IPU075N03L G

Values

Symbol Conditions

Unit

min.

typ.

max.

1400

1900

580

770

Dynamic characteristics

Input capacitance

C iss

V GS=0 V, V DS=15 V,

f =1 MHz

Output capacitance

C oss

Reverse transfer capacitance

Crss

29

44

Turn-on delay time

t d(on)

4.3

Rise time

tr

3.6

Turn-off delay time

t d(off)

17

Fall time

tf

2.8

Gate to source charge

Q gs

4.6

Gate charge at threshold

Q g(th)

2.2

Gate to drain charge

Q gd

2.1

Switching charge

Q sw

4.4

Gate charge total

Qg

8.7

Gate plateau voltage

V plateau

3.3

Gate charge total

Qg

V DD=15 V, I D=30 A,

V GS=0 to 10 V

18

Gate charge total, sync. FET

Q g(sync)

V DS=0.1 V,

V GS=0 to 4.5 V

7.6

Output charge

Q oss

V DD=15 V, V GS=0 V

15

42

350

V DD=15 V, V GS=10 V,

I D=30 A, R G=1.6

pF

ns

Gate Charge Characteristics 6)

V DD=15 V, I D=30 A,

V GS=0 to 4.5 V

nC

nC

Reverse Diode

Diode continuous forward current

IS

Diode pulse current

I S,pulse

Diode forward voltage

V SD

V GS=0 V, I F=30 A,

T j=25 C

0.89

1.1

Reverse recovery charge

Q rr

V R=15 V, I F=I S,

di F/dt =400 A/s

10

nC

6)

Rev. 1.1

T C=25 C

See figure 16 for gate charge parameter definition

page 3

2009-01-14

IPD075N03L G

IPF075N03L G

IPS075N03L G

IPU075N03L G

1 Power dissipation

2 Drain current

P tot=f(T C)

I D=f(T C); V GS10 V

50

60

50

40

40

I D [A]

P tot [W]

30

30

20

20

10

10

0

0

50

100

150

200

50

100

T C [C]

150

3 Safe operating area

4 Max. transient thermal impedance

I D=f(V DS); T C=25 C; D =0

Z thJC=f(t p)

parameter: t p

parameter: D =t p/T

103

10

limited by on-state

resistance

1 s

102

0.5

10 s

1

0.2

Z thJC [K/W]

I D [A]

100 s

DC

101

1 ms

0.05

0.02

0.01

single pulse

10-1

10-1

100

101

102

V DS [V]

Rev. 1.1

0.1

0.1

10 ms

10

200

T C [C]

0.01

10-6

10-5

10-4

10-3

10-2

10-1

100

t p [s]

page 4

2009-01-14

IPD075N03L G

IPF075N03L G

IPS075N03L G

IPU075N03L G

5 Typ. output characteristics

6 Typ. drain-source on resistance

I D=f(V DS); T j=25 C

R DS(on)=f(I D); T j=25 C

parameter: V GS

parameter: V GS

120

20

5V

4.5 V

3.2 V

100

16

10 V

3.5 V

R DS(on) [m]

80

I D [A]

4V

60

4V

12

4.5 V

5V

8

10 V

40

3.5 V

11.5 V

3.2 V

20

3V

2.8 V

0

0

20

40

V DS [V]

60

80

100

80

100

I D [A]

7 Typ. transfer characteristics

8 Typ. forward transconductance

I D=f(V GS); |V DS|>2|I D|R DS(on)max

g fs=f(I D); T j=25 C

parameter: T j

100

80

80

60

60

I D [A]

g fs [S]

100

40

40

20

20

175 C

25 C

0

0

Rev. 1.1

20

40

60

I D [A]

V GS [V]

page 5

2009-01-14

IPD075N03L G

IPF075N03L G

IPS075N03L G

IPU075N03L G

9 Drain-source on-state resistance

10 Typ. gate threshold voltage

R DS(on)=f(T j); I D=30 A; V GS=10 V

V GS(th)=f(T j); V GS=V DS; I D=250 A

16

2.5

14

2

10

V GS(th) [V]

R DS(on) [m]

12

98 %

typ

1.5

4

0.5

2

0

-60

-20

20

60

100

140

180

-60

-20

20

60

100

140

180

T j [C]

T j [C]

11 Typ. capacitances

12 Forward characteristics of reverse diode

C =f(V DS); V GS=0 V; f =1 MHz

I F=f(V SD)

parameter: T j

104

103

25 C

103

175 C, 98%

Ciss

102

10

175 C

I F [A]

C [pF]

Coss

Crss

25 C, 98%

101

101

100

100

0

10

20

30

V DS [V]

Rev. 1.1

0.5

1.5

V SD [V]

page 6

2009-01-14

IPD075N03L G

IPF075N03L G

IPS075N03L G

IPU075N03L G

13 Avalanche characteristics

14 Typ. gate charge

I AS=f(t AV); R GS=25

V GS=f(Q gate); I D=30 A pulsed

parameter: T j(start)

parameter: V DD

100

12

15 V

6V

24 V

10

100 C

150 C

25 C

V GS [V]

I AV [A]

10

10-1

100

101

102

103

t AV [s]

12

16

20

24

Q gate [nC]

15 Drain-source breakdown voltage

16 Gate charge waveforms

V BR(DSS)=f(T j); I D=1 mA

34

V GS

Qg

32

V BR(DSS) [V]

30

28

26

V g s(th)

24

Q g(th)

22

Q sw

Q gs

20

-60

-20

20

60

100

140

Q g ate

Q gd

180

T j [C]

Rev. 1.1

page 7

2009-01-14

Package Outline

Footprint:

Rev. 1.1

IPD075N03L G

IPF075N03L G

IPS075N03L G

IPU075N03L G

PG-TO252-3-11

Packaging:

page 8

2009-01-14

Package Outline

IPD075N03L G

IPF075N03L G

IPS075N03L G

IPU075N03L G

PG-TO252-3-23

PG-TO252-3-23: Outline

Footprint:

Rev. 1.1

page 9

2009-01-14

Package Outline

IPD075N03L G

IPF075N03L G

IPS075N03L G

IPU075N03L G

PG-TO251-3-11

PG-TO251-3-11: Outline

PG-TO251-3-21: Outline

Rev. 1.1

page 10

2009-01-14

Package Outline

IPD075N03L G

IPF075N03L G

IPS075N03L G

IPU075N03L G

PG-TO251-3-21

PG-TO251-3-11: Outline

PG-TO251-3-21: Outline

Rev. 1.1

page 11

2009-01-14

IPD075N03L G

IPF075N03L G

IPS075N03L G

IPU075N03L G

Published by

Infineon Technologies AG

81726 Munich, Germany

2008 Infineon Technologies AG

All Rights Reserved.

Legal Disclaimer

The information given in this document shall in no event be regarded as a guarantee of

conditions or characteristics. With respect to any examples or hints given herein, any typical

values stated herein and/or any information regarding the application of the device,

Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind,

including without limitation, warranties of non-infringement of intellectual property rights

of any third party.

Information

For further information on technology, delivery terms and conditions and prices, please

contact the nearest Infineon Technologies Office (www.infineon.com).

Warnings

Due to technical requirements, components may contain dangerous substances. For information

on the types in question, please contact the nearest Infineon Technologies Office.

Infineon Technologies components may be used in life-support devices or systems only with

the express written approval of Infineon Technologies, if a failure of such components can

reasonably be expected to cause the failure of that life-support device or system or to affect

the safety or effectiveness of that device or system. Life support devices or systems are

intended to be implanted in the human body or to support and/or maintain and sustain

and/or protect human life. If they fail, it is reasonable to assume that the health of the user

or other persons may be endangered.

Rev. 1.1

page 12

2009-01-14

Anda mungkin juga menyukai

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeDari EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifePenilaian: 4 dari 5 bintang4/5 (5794)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreDari EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You ArePenilaian: 4 dari 5 bintang4/5 (1090)

- Never Split the Difference: Negotiating As If Your Life Depended On ItDari EverandNever Split the Difference: Negotiating As If Your Life Depended On ItPenilaian: 4.5 dari 5 bintang4.5/5 (838)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceDari EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RacePenilaian: 4 dari 5 bintang4/5 (895)

- Grit: The Power of Passion and PerseveranceDari EverandGrit: The Power of Passion and PerseverancePenilaian: 4 dari 5 bintang4/5 (588)

- Shoe Dog: A Memoir by the Creator of NikeDari EverandShoe Dog: A Memoir by the Creator of NikePenilaian: 4.5 dari 5 bintang4.5/5 (537)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersDari EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersPenilaian: 4.5 dari 5 bintang4.5/5 (344)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureDari EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FuturePenilaian: 4.5 dari 5 bintang4.5/5 (474)

- Her Body and Other Parties: StoriesDari EverandHer Body and Other Parties: StoriesPenilaian: 4 dari 5 bintang4/5 (821)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Dari EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Penilaian: 4.5 dari 5 bintang4.5/5 (121)

- The Emperor of All Maladies: A Biography of CancerDari EverandThe Emperor of All Maladies: A Biography of CancerPenilaian: 4.5 dari 5 bintang4.5/5 (271)

- The Little Book of Hygge: Danish Secrets to Happy LivingDari EverandThe Little Book of Hygge: Danish Secrets to Happy LivingPenilaian: 3.5 dari 5 bintang3.5/5 (400)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyDari EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyPenilaian: 3.5 dari 5 bintang3.5/5 (2259)

- The Yellow House: A Memoir (2019 National Book Award Winner)Dari EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Penilaian: 4 dari 5 bintang4/5 (98)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaDari EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaPenilaian: 4.5 dari 5 bintang4.5/5 (266)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryDari EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryPenilaian: 3.5 dari 5 bintang3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnDari EverandTeam of Rivals: The Political Genius of Abraham LincolnPenilaian: 4.5 dari 5 bintang4.5/5 (234)

- On Fire: The (Burning) Case for a Green New DealDari EverandOn Fire: The (Burning) Case for a Green New DealPenilaian: 4 dari 5 bintang4/5 (74)

- The Unwinding: An Inner History of the New AmericaDari EverandThe Unwinding: An Inner History of the New AmericaPenilaian: 4 dari 5 bintang4/5 (45)

- Rise of ISIS: A Threat We Can't IgnoreDari EverandRise of ISIS: A Threat We Can't IgnorePenilaian: 3.5 dari 5 bintang3.5/5 (137)

- Introductory PagesDokumen15 halamanIntroductory PagesTejeswari polaki0% (1)

- Dynamic LogicDokumen27 halamanDynamic LogicPranav DarganBelum ada peringkat

- A2shb HaohaiDokumen4 halamanA2shb HaohaiPaulo Henrique SBelum ada peringkat

- P2003BDG: N-Channel Logic Level Enhancement Mode MOSFETDokumen5 halamanP2003BDG: N-Channel Logic Level Enhancement Mode MOSFETRexer AnthonyBelum ada peringkat

- Crumar Stratus Service ManualDokumen18 halamanCrumar Stratus Service ManualdodBelum ada peringkat

- Toshiba Photocouplers and Photorelays CatalogDokumen80 halamanToshiba Photocouplers and Photorelays CatalogalanabdoBelum ada peringkat

- Mod 5 LP VLSI - Ktunotes - in PDFDokumen115 halamanMod 5 LP VLSI - Ktunotes - in PDFakhilabrahamBelum ada peringkat

- Xiner-Xns15n120t C379748Dokumen1 halamanXiner-Xns15n120t C379748roby72Belum ada peringkat

- Activity 6Dokumen10 halamanActivity 6Ultima_SarinBelum ada peringkat

- Phototransistor Switching Time Analysis: Output WaveformsDokumen8 halamanPhototransistor Switching Time Analysis: Output WaveformsklklkBelum ada peringkat

- System Plus Consulting USDokumen4 halamanSystem Plus Consulting USRaghu GowdaBelum ada peringkat

- Semiconductor Manufacturing ProcessesDokumen32 halamanSemiconductor Manufacturing ProcessesmailstonaikBelum ada peringkat

- Thyristors (SCRS) : Lecture NotesDokumen14 halamanThyristors (SCRS) : Lecture NotesBeverly PamanBelum ada peringkat

- 25 J 0007Dokumen2 halaman25 J 0007wo dotaBelum ada peringkat

- Optoelectronic DevicesDokumen13 halamanOptoelectronic DevicesJudilyn ReyesBelum ada peringkat

- IGBT Bridge ModuleDokumen3 halamanIGBT Bridge ModuleSyamnaresh GarlapatiBelum ada peringkat

- What Are TVS DiodesDokumen1 halamanWhat Are TVS Diodesrajat nimjeBelum ada peringkat

- EC2354 - Vlsi Design Iii /vi Ece - Prepared by L.M.I.Leo Joseph Asst - Prof /eceDokumen22 halamanEC2354 - Vlsi Design Iii /vi Ece - Prepared by L.M.I.Leo Joseph Asst - Prof /ecePushpalathaBelum ada peringkat

- EEE 2212 Revision QuestionsDokumen9 halamanEEE 2212 Revision QuestionsIAMMARKSBelum ada peringkat

- Transistor ApproximationsDokumen5 halamanTransistor ApproximationsGlenn D. KleinBelum ada peringkat

- Transistor Biasing: ObjectivesDokumen4 halamanTransistor Biasing: ObjectivesShannen Joyce FloresBelum ada peringkat

- Differences Between Pv-M2079-K and Pv-M2079: Comparison ChartDokumen3 halamanDifferences Between Pv-M2079-K and Pv-M2079: Comparison ChartAndre BaezBelum ada peringkat

- Subsystem Design: Architectural IssuesDokumen26 halamanSubsystem Design: Architectural IssuesSanjana M PBelum ada peringkat

- Lab Manual: 1 Dept of E&C, PACE, MangaloreDokumen78 halamanLab Manual: 1 Dept of E&C, PACE, MangaloreMr.Mohammed Zakir B ELECTRONICS & COMMUNICATIONBelum ada peringkat

- EE 503 Project 1:buck Converter: I Background: II: RequirementDokumen7 halamanEE 503 Project 1:buck Converter: I Background: II: Requirementapi-626683514Belum ada peringkat

- TransistorsDokumen14 halamanTransistorsCarolyne DaleBelum ada peringkat

- Reduction of Leakage Current in 6t SRAM CellDokumen16 halamanReduction of Leakage Current in 6t SRAM CellPraveen SaxenaBelum ada peringkat

- Vlsi DesignDokumen3 halamanVlsi DesignGokulBelum ada peringkat

- Isc 2SD2253: Silicon NPN Power TransistorDokumen2 halamanIsc 2SD2253: Silicon NPN Power TransistorFrancisco Meza BenavidezBelum ada peringkat

- Mosfet ScalingDokumen18 halamanMosfet ScalingRakeshBelum ada peringkat