(Modul 02) - (EL2102R) - (13115004)

(Modul 02) - (EL2102R) - (13115004)

Diunggah oleh

Agadi Samridho0 penilaian0% menganggap dokumen ini bermanfaat (0 suara)

14 tayangan8 halamanJudul Asli

[Modul 02]_[EL2102R]_[13115004].docx

Hak Cipta

© © All Rights Reserved

Format Tersedia

DOCX, PDF, TXT atau baca online dari Scribd

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniHak Cipta:

© All Rights Reserved

Format Tersedia

Unduh sebagai DOCX, PDF, TXT atau baca online dari Scribd

0 penilaian0% menganggap dokumen ini bermanfaat (0 suara)

14 tayangan8 halaman(Modul 02) - (EL2102R) - (13115004)

(Modul 02) - (EL2102R) - (13115004)

Diunggah oleh

Agadi SamridhoHak Cipta:

© All Rights Reserved

Format Tersedia

Unduh sebagai DOCX, PDF, TXT atau baca online dari Scribd

Anda di halaman 1dari 8

Percobaan II

Pengenalan Desain Dengan FPGA

Agadi Samridho (13115004)

Asisten : Gde KM Atmajaya (13112011)

Tanggal Percobaan : 08/11/2016

EL2102R Sistem Digital

Laboratorium Teknik Elektro

Institut Teknologi Sumatera

AbstrakFPGA (Field

Programmable

Gate

Array)

merupakan sebuah IC yang sering digunakan untuk

mengimplementasikan rangkaian digital. Pada praktikum kali

ini dilakukan bebrapa percobaan antara lain mendesain full

adder dengan pendekatan skematik dan bahasa VHDL,

mendesain 4-bit Ripple Carry Adder dengan VHDL, mendesain

4-bit adder dengan skematik, melakukan simulasi sederhana

denfan menggunakan Modelsim, membuat Testbench dan

melakukan proses tapping sinyal dari sebuah desain. Hasil yang

didapatkan dari percobaan kemudian dicocokan dengan hasil

perhitungan /truth tabel.

Field Programmable Gate Array (FPGA) merupakan sebuah

IC digital yang sering digunakan untuk

mengimplementasikan rangkaian digital. FPGA berbentuk

komponen elektronika dan semikonduktor yang terdiri dari

komponen gerbang terprogram (programmable logic) dan

sambungan terprogram (interkoneksi). Secara umum alur

perancangan rangkaian digital dengan menggunakan FPGA

dari ALTERA dapat digambarkan seperti flowchart pada

Gambar 1.2.

Kata KunciFPGA, VHDL, skematik

I.

PENDAHULUAN

PGA adalah gerbang-gerbang digital dimana

interkoneksi antar masing-masing gerbang tersebut

dapat dikonfigurasi antara satu sama lainnya, dan dapat

dirancang sesuai dengan keinginan dan kebutuhan user atau

pemakai tanpa melalui tahap burn. Hardware yang digunakan

pada FPGA berupa bahasa pemrograman VHDL dan

Modelsim. VHDL (Very High Speed Integrated Hardware

Description Language) termasuk bahasa pemodelan yang

digunakan untuk merancang atau memodelkan rangkaian

digital. Pemakaian FPGA mempunyai banyak keuntungan

dibandingkan pemakaian IC TTL dan CMOS. Selain jumlah

gerbangnya yang jauh lebih banyak, kemudahan, kecepatan

dan flexibilitas proses rancang bangun merupakan kelebihan

FPGA serta konsumsi dayanya juga jauh lebih sedikit. Pada

praktikum kali ini, akan dilakukan beberapa percobaan

sehingga diharapkan praktikan dapat memahami tujuan yang

ingin dicapai, antara lain :

1. Mempelajari teknik perancangan rangkaian digital

dengan target FPGA.

2. Dapat melakukan perancangan rangkaian digital

dengan target FPGA baik menggunakan

pendekatan skematik maupun bahasa VHDL.

Gambar 2.1 Flowchart Umum Proses Percancangan

B. Full Adder

II. LANDASAN TEORETIS

A. FPGA (Field Programmable Logic Array)

Keunggulan FULL-ADDER bila dibandingakan dengan

HALF-ADDER adalah kemampuan-nya menampung dan

menjumlahkan bit CARRY-in (Cin) yang berasal dari

CARRY-out (Cout) dari tahapan sebelumnya. Oleh

karenanya fungsi FULL-ADDER itu sendiri adalah

menjumlahkan ketiga bit input yaitu bit A, bit B dan Cin

untuk manghasilkan dua bit output yaitu S dan Cout.

Dengan menginterpresentasikan fungsi dan melihat

format operasi rangkaian FULL ADDER, table kebenaran

dapat disusun untuk setiap kemungkinan kombinasi ketiga

bit input. Diasumsikan input berasal dari sumber logika

positif dan output berupa ACTIVE HIGH.

Langkah selanjutnya adalah membuat K-Map orde 2

dari table kebenaran tersebut. K-Map ini akan membantu

merumuskan fungsi logika dari S dan Cout.

Gambar 3.1 Gelombang Sinyal Full Adder dengan

Pendekatan Skematik

Tabel 3.1 Truth Table Rangkaian Full Adder

A

B

C

Aout Bout Cout Carr

y

1

0

0

1

0

0

0

0

1

0

0

1

0

0

0

1

1

0

1

1

1

Su

m

1

1

0

Dari percobaan didapatkan bentuk sinyal seperti pada gambar

3.1. Hasil tersebut sesuai dengan truth table untuk rangakaian

rangkaian skematik full adder (tabel 3.1).

Tabel 2.1 Tabel kebenaran dan K-map dari FULL

ADDER

Gambar 2.2 Salah satu bentuk rangkaian Full Adder

III. HASIL DAN ANALISIS

A. Mendesain Full Adder dengan Skematik

Hasil implementasi pada FPGA yaitu seven segment yang

pertama untuk menampilkan Carry out dan Sum. Sedangkan

seven segment yang kedua untuk menampilkan keluaran A/A

out, B/B out, dan C/C out. Pada percobaan ini FPGA

menggunakan system Active Low, artinya seven segment akan

menyala saat diberi input logika 0 dan mati saat diberi input

logika 1.

Kaki-kaki telah terprogram seperti pada gambar diatas,

didapatkan hasil implementasi LED pada FPGA mengeluarkan

hasil yang benar sebagai berikut :

Gambar 3.2 Hasil Implementasi pada FPGA ketika Input

Bernilai 1 0 0

Dari percobaan didapatkan bentuk sinyal seperti pada Gambar

3.5. Hasil tersebut sesuai dengan truth table untuk rangakaian

rangkaian skematik full adder (Tabel 3.2).

Hasil implementasi pada FPGA yaitu hanya menggunakan

seven segment pertama untuk menampilkan Carry out dan

Sum. Pada percobaan ini FPGA menggunakan system Active

Low, artinya seven segment akan menyala saat diberi input

logika 0 dan mati saat diberi input logika 1.

Gambar 3.3 Hasil Implementasi pada FPGA ketika Input

Bernilai 0 1 0

Kaki-kaki telah terprogram seperti pada gambar diatas,

didapatkan hasil implementasi LED pada FPGA mengeluarkan

hasil yang benar sebagai berikut :

Gambar 3.4 Hasil Implementasi pada FPGA ketika Input

Bernilai 1 1 0

Ketika pin A, B, dan C masing-masing diberikan nilai logika

1, 0 dan 0 (pada switch FPGA), maka output yang dihasilkan

pada Aout, Bout, dan Cout masing-masing adalah 1, 0, 0 dan

output yang dihasilkan pada Carry dan Sum masing-masing

adalah 0 dan 1. Aout, Bout dan Cout berperan pada seven

segment kedua, sedangkan Carry dan Sum berperan pada

seven segment pertama. Karena sistem menggunakan active

low power, dimana LED akan menyala ketika nilai logika

adalah 0 dan LED akan mati ketika nilai logika adalah 1 maka

pada bagian seven segment pertama LED Sum akan mati dan

pada seven segment kedua LED Aout akan mati seperti terlihat

pada Gambar 3.2. Begitu pun dengan hasil-hasil implementasi

yang lainnya pada FPGA.

Gambar 3.6 Hasil Implementasi pada FPGA ketika Input

Bernilai 1 1 1

B. Mendesain Full Adder dengan Pendekatan

Bahasa VHDL

Gambar 3.7 Hasil Implementasi pada FPGA ketika Input

Bernilai 1 0 0

Gambar 3.5 Gelombang Sinyal Full Adder dengan

Pendekatan Bahasa VHDL

Tabel 3.2 Truth Table Rangkaian Full Adder

A

B

C

Carry

Sum

1

1

1

1

1

1

1

0

1

0

1

0

0

0

1

Gambar 3.8 Hasil Implementasi pada FPGA ketika Input

Bernilai 1 1 0

Ketika pin A, B, dan C masing-masing diberikan nilai logika

1, 1 dan 1 (pada switch FPGA), maka output yang dihasilkan

pada Carry dan Sum masing-masing adalah 1 dan 1. Karena

sistem menggunakan active low power, dimana LED akan

menyala ketika nilai logika adalah 0 dan LED akan mati

ketika nilai logika adalah 1 maka pada bagian seven segment

LED Carry akan mati dan LED Sum akan mati seperti terlihat

pada Gambar 3.6. Begitu pun dengan hasil-hasil implementasi

lainnya pada FPGA.

Gambar tampilan sinyal rangkaian full adder dengan

menggunakan pendekatan Bahasa VHDL sama dengan sinyal

rangkaian full adder dengan menggunakan pendekatan

skematik. Hal ini ditunjukkan dari kedua pendekatan tersebut

sesuai dengan truth table. Hal ini membuktikan kesamaan

sinyal gelombang yang didapatkan untuk rangkaian full adder

baik menggunakan pendekatan skematik maupun pendekatan

Bahasa VHDL. Sehingga kita dapat menggunakan pendekatan

skematik maupun Bahasa VHLD dalam implementasi dengan

FPGA.

C. Mendesain 4-Bit Ripple Carry Adder dengan

VHDL

4-Bit Ripple Carry adder yaitu menerima masukan A = 4 bit

dan B = 4 bit serta Cin = 1 bit lalu mengembalikan hasil

berupa Cout = 1 bit dan Sum = 4 bit. Percobaan ini dilakukan

dengan pendekatan Bahasa VHDL. Hasil gelombang sinyal

yang dihasilkan seperti gambar berikut :

Gambar 3.10 Pembuktikan Hasil gelombang sinyal 4-bit

Ripple Carry Adder dengan VHDL

A

B

Sum

Cout

0001

0000

0001

0

Terbukti bahwa gelombang sinyal hasil simulasi dengan

bahasa VHDL sesuai dengan perhitungan manual. Begitu pun

dengan yang lainnya.

D. Mendesain 4-Bit Adder dengan Skematik

Gambar 3.11 Hasil gelombang sinyal 4-bit Ripple Carry

Adder dengan skematik

Gambar 3.9 Hasil gelombang sinyal 4-bit Ripple Carry

Adder dengan VHDL

Gambar diatas menunjukan hasil 4 bit carry adder. Apabila

dihitung secara manual sebagai berikut :

Ambil salah satu titik/garis :

Dapat dilihat bahwa gelombang sinyal yang dihasilkan dengan

pendekatan skematik sama persis dengan gelombang yang

dihasilkan dengan pendekatan Bahasa VHDL. Hal ini

menujukan bahwa kita dapat menggunakan pendekatan

Bahasa VHDL maupun skematik dalam meranacang rangkaian

digital 4 bit Ripple Carry Adder dikarenakan kedua

pendekatan tersebut menampilkan hasil yang sama benarnya.

E. Simulasi Sederhana Menggunakan Modelsim

Gambar 3.12 Hasil simulasi sederhana meggunakan

Modelsim

A

C-in

C-out

Dapat dilihat pada gambar di garis merah, ketika A bernilai 1,

B bernilai 1, dan C bernilai 1, maka hasil Sum nya yaitu

berniali 1 dan Carry out bernilai 1. Hasil tersebut sesuai

dengan truth table. Begitu pun dengan yang lainnya. Oleh

karena itu, hal ini menunjukan bahwa untuk merancang suatu

rangkaian digital, kita juga dapat menggunakan software

Modelsim dengan hasil yang sama benarnya dengan

menggunakan Quartus.

IV. SIMPULAN

Kesimpulan yang didapatkan dari percobaan

modul II ini, yaitu

Hasil gelombang sinyal menunjukkan hasil yang sama dengan

percobaan 1 yang menggunakan Quartus. Hasil gelombang

sinyal pada percobaan ini didapatkan dengan mengatur clock

A, B, dan C dengan 50ps, 100ps dan 200ps. Kita dapat

menguji kebenaran dari gelombang sinyal tersebut dengan

mengambil 1 garis seperti berikut :

Dalam melakukan perancangan rangkaian

digital dapat menggunakan dua aplikasi

software, yaitu ALTERA Quartus II dan

Modelsim

Dalam melakukan perancangan rangkaian

digital dapat menggunakan dua pendekatan

yaitu pendekatan skematik dan pendekatan

bahasa VHDL.

Fungsi rangkaian Adder (Full Adder dan Ripple

Carry Adder) yaitu untuk menjumlahkan

bilangan biner dengan menggunakan fungsi

gerbang logika.

Keuntungan menggunakan Modelsim adalah

dapat melakukan proses testbench dan

tapping sinyal.

Keuntungan menggunakan ALTERA Quartus

adalah cara penggunaannya lebih mudah

apabila dibandingkan dengan menggunakan

Modelsim.

REFERENSI

Hutabarat, Mervin T. 2016. Praktikum Sistem

Digital. Penerbit ITB. Bandung.

Brown, Stephen and Vranesic, Zvonko. 2009.

Fundamentals of Digital Logic with VHDL Design.

McGraw-Hill. America.

Gambar 3.13 Pembuktikan Hasil Simulasi Sederhana

Menggunakan Modelsim

LAMPIRAN

Posisi Kaki yang Terhubung pada Seven Segment dan Switch Untuk DE1

Switch

Switch[0]

Switch[1]

Switch[2]

Switch[3]

Switch[4]

Switch[5]

Switch[6]

Switch[7]

Switch[8]

Switch[9]

Cyclone II Pin

PIN_L22

PIN_L21

PIN_M22

PIN_V12

PIN_W12

PIN_U12

PIN_U11

PIN_M2

PIN_M1

PIN_L2

Rangkaian Skematik Full Adder

Rangkaian Singkat Skematik Ripple Carry Adder

VCC

f ull_adder

f ull_adder

Cout

Cout

Cin

C(0)

FA0

Kode VHDL Untuk Desain Full Adder

Kode VHDL Untuk Desain 4-Bit Ripple Carry Adder

Cin

FA1

Skematik Rangkaian 4-Bit Adder

Anda mungkin juga menyukai

- Resume 6 Rangkaian Listrik 1 Teorema MilmanDokumen20 halamanResume 6 Rangkaian Listrik 1 Teorema MilmanyusrielyahyaBelum ada peringkat

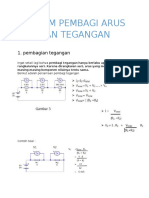

- Hukum Pembagi Arus Dan TeganganDokumen6 halamanHukum Pembagi Arus Dan TeganganAgadi SamridhoBelum ada peringkat

- Teorema SuperposisiDokumen12 halamanTeorema SuperposisiAgadi SamridhoBelum ada peringkat

- Laporan RBL Senter KocokDokumen9 halamanLaporan RBL Senter KocokAgadi Samridho100% (1)

- Laporan Praktikum Sistem Digital - Rangkaian Logika KombinasionalDokumen4 halamanLaporan Praktikum Sistem Digital - Rangkaian Logika KombinasionalAgadi SamridhoBelum ada peringkat

- Laporan Praktikum Rangkaian Elektrik Modul 01 Rangkaian Arus Searah Dan Nilai Statistik ResistansiDokumen9 halamanLaporan Praktikum Rangkaian Elektrik Modul 01 Rangkaian Arus Searah Dan Nilai Statistik ResistansiAgadi SamridhoBelum ada peringkat