Max 5304

Diunggah oleh

tabassam7801Hak Cipta

Format Tersedia

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniHak Cipta:

Format Tersedia

Max 5304

Diunggah oleh

tabassam7801Hak Cipta:

Format Tersedia

19-1562; Rev 0; 10/99

10-Bit Voltage-Output DAC

in 8-Pin MAX

Applications

Digital Offset and Gain Adjustment

Features

10-Bit DAC with Configurable Output Amplifier

+5V Single-Supply Operation

Low Supply Current

0.28mA Normal Operation

2A Shutdown Mode

Available in 8-Pin MAX

Power-On Reset Clears DAC Output to Zero

SPI/QSPI/MICROWIRE Compatible

Schmitt-Trigger Digital Inputs for Direct

Optocoupler Interface

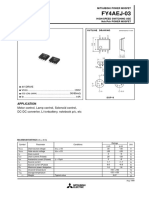

_________________Ordering Information

PART

TEMP. RANGE

PIN-PACKAGE

Industrial Process Control

MAX5304CUA

0C to +70C

8 MAX

Microprocessor-Controlled Systems

MAX5304EUA

-40C to +85C

8 MAX

Portable Test Instruments

Remote Industrial Control

Functional Diagram

VDD

GND

REF

Pin Configuration

TOP VIEW

FB

DAC

REGISTER

OUT

DAC

CONTROL

DIN

SCLK

VDD

GND

DIN 3

REF

SCLK 4

FB

CS 2

INPUT

REGISTER

CS

OUT 1

16-BIT

SHIFT

REGISTER

MAX5304

MAX5304

MAX

SPI and QSPI are trademarks of Motorola, Inc.

MICROWIRE is a trademark of National Semiconductor Corp.

________________________________________________________________ Maxim Integrated Products

For free samples & the latest literature: http://www.maxim-ic.com, or phone 1-800-998-8800.

For small orders, phone 1-800-835-8769.

MAX5304

General Description

The MAX5304 combines a low-power, voltage-output,

10-bit digital-to-analog converter (DAC) and a precision

output amplifier in an 8-pin MAX package. It operates

from a single +5V supply, drawing less than 280A of

supply current.

The output amplifiers inverting input is available to the

user, allowing specific gain configurations, remote

sensing, and high output-current capability. This makes

the MAX5304 ideal for a wide range of applications,

including industrial process control. Other features

include a software shutdown and power-on reset.

The serial interface is SPI/QSPI/MICROWIRE

compatible. The DAC has a double-buffered input,

organized as an input register followed by a DAC register. A 16-bit serial word loads data into the input register. The DAC register can be updated independently or

simultaneously with the input register. All logic inputs

are TTL/CMOS-logic compatible and buffered with

Schmitt triggers to allow direct interfacing to optocouplers.

MAX5304

10-Bit Voltage-Output DAC

in 8-Pin MAX

ABSOLUTE MAXIMUM RATINGS

VDD to GND...............................................................-0.3V to +6V

REF, OUT, FB to GND.................................-0.3V to (VDD + 0.3V)

Digital Inputs to GND................................................-0.3V to +6V

Continuous Current into Any Pin.......................................20mA

Continuous Power Dissipation (TA = +70C)

8-Pin MAX (derate 4.10mW/C above+70C) ..........330mW

Operating Temperature Ranges

MAX5304CUA ...................................................0C to +70C

MAX5304EUA ................................................-40C to +85C

Junction Temperature......................................................+150C

Storage Temperature Range.............................-65C to +150C

Lead Temperature (soldering, 10s)........................... ......+300C

Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, and functional

operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to

absolute maximum rating conditions for extended periods may affect device reliability.

ELECTRICAL CHARACTERISTICS

(Circuit of Figure 8, VDD = +5V 10%, VREF = +2.5V, RL = 5k, CL = 100pF, TA = TMIN to TMAX, unless otherwise noted. Typical values

are at TA = +25C. Output buffer connected in unity-gain configuration.)

PARAMETER

SYMBOL

CONDITIONS

MIN

TYP

MAX

UNITS

1.0

LSB

LSB

STATIC PERFORMANCEANALOG SECTION

Resolution

Differential Nonlinearity

DNL

Integral Nonlinearity

(Note 1)

INL

Offset Error

Offset-Error Tempco

Gain Error (Note 1)

10

VOS

0.3

TCVOS

GE

-0.3

Gain-Error Tempco

Power-Supply Rejection Ratio

Bits

Guaranteed monotonic

8

2

1

PSRR

mV

ppm/C

LSB

ppm/C

4.5V VDD 5.5V

800

V/V

REFERENCE INPUT

Reference Input Range

VREF

Reference Input Resistance

RREF

0

Code dependent, minimum at code 1550 hex

18

VDD - 1.4

30

MULTIPLYING-MODE PERFORMANCE

Reference -3dB Bandwidth

VREF = 0.67Vp-p

650

kHz

Reference Feedthrough

Input code = all 0s, VREF = 3.6Vp-p at 1kHz

-84

dB

VREF = 1Vp-p at 25kHz, code = full scale

77

dB

Signal-to-Noise Plus

Distortion Ratio

SINAD

DIGITAL INPUTS

Input High Voltage

VIH

Input Low Voltage

VIL

Input Leakage Current

IIN

Input Capacitance

CIN

2.4

VIN = 0 or VDD

V

0.001

8

_______________________________________________________________________________________

0.8

0.5

A

pF

10-Bit Voltage-Output DAC

in 8-Pin MAX

(Circuit of Figure 8, VDD = +5V 10%, VREF = +2.5V, RL = 5k, CL = 100pF, TA = TMIN to TMAX, unless otherwise noted. Typical values

are at TA = +25C. Output buffer connected in unity-gain configuration.)

PARAMETER

SYMBOL

CONDITIONS

MIN

TYP

MAX

UNITS

DIGITAL INPUTS

DYNAMIC

PERFORMANCE

Voltage Output Slew Rate

SR

Output Settling Time

To 1/2LSB, VSTEP = 2.5V

Output Voltage Swing

Rail-to-rail (Note 2)

0.6

V/s

10

0 to VDD

Current into FB

0.001

Start-Up Time

20

nVs

CS = VDD, DIN = 100kHz

Digital Feedthrough

0.1

POWER SUPPLIES

Supply Voltage

VDD

Supply Current

IDD

Supply Current in Shutdown

4.5

(Note 3)

5.5

0.4

mA

20

0.001

0.5

0.28

(Note 3)

Reference Current in Shutdown

TIMING CHARACTERISTICS (Figure 6)

SCLK Clock Period

tCP

100

ns

SCLK Pulse Width High

tCH

40

ns

SCLK Pulse Width Low

tCL

40

ns

CS Fall to SCLK Rise Setup Time

tCSS

40

ns

SCLK Rise to CS Rise Hold Time

tCSH

ns

tDS

40

ns

DIN Setup Time

DIN Hold Time

tDH

ns

SCLK Rise to CS Fall Delay

tCS0

40

ns

CS Rise to SCLK Rise Hold Time

tCS1

40

ns

CS Pulse Width High

tCSW

100

ns

Note 1: Guaranteed from code 3 to code 1023 in unity-gain configuration.

Note 2: Accuracy is better than 1LSB for VOUT = 8mV to (VDD - 100mV), guaranteed by a power-supply rejection test at the end

points.

Note 3: RL = , digital inputs at GND or VDD.

_______________________________________________________________________________________

MAX5304

ELECTRICAL CHARACTERISTICS (continued)

__________________________________________Typical Operating Characteristics

(VDD = +5V, RL = 5k, CL = 100pF, TA = +25C, unless otherwise noted.)

REFERENCE VOLTAGE INPUT

FREQUENCY RESPONSE

-0.025

360

SUPPLY CURRENT (A)

RELATIVE OUTPUT (dB)

RL =

380

-4

0.025

INL (LSB)

400

MAX5304-02

MAX5304-01

0.050

SUPPLY CURRENT

vs. TEMPERATURE

MAX5304-03

INTEGRAL NONLINEARITY

vs. REFERENCE VOLTAGE

-8

-12

-16

340

320

300

280

260

240

220

-20

0.4

1.2

2.0

2.8

3.6

4.4

500k

1M

REFERENCE VOLTAGE (V)

200

-60

3M

-20

60

100

140

TOTAL HARMONIC DISTORTION

PLUS NOISE vs. FREQUENCY

-50

MAX5304-05

500

MAX5304-04

20

TEMPERATURE (C)

SUPPLY CURRENT

vs. SUPPLY VOLTAGE

10

450

VREF = +2.5VDC + 1Vp-p SINE

CODE = FULL SCALE

-55

400

7

6

5

4

3

-60

350

THD + NOISE (dB)

SUPPLY CURRENT (A)

300

250

200

20

60

100

-90

4.0

140

4.4

4.8

5.2

5.6

100

10

TEMPERATURE (C)

FREQUENCY (kHz)

OUTPUT FFT PLOT

OUTPUT VOLTAGE

vs. LOAD

REFERENCE FEEDTHROUGH

AT 1kHz

-60

-80

2.49972

2.49968

2.49964

2.7

3.8

FREQUENCY (kHz)

4.9

6.0

2.49956

0.1k

-40

-60

OUTPUT FEEDTHROUGH

-80

2.49960

-100

REFERENCE INPUT SIGNAL

-20

SIGNAL AMPLITUDE (dB)

-40

MAX5304-09a/09b

2.49976

OUTPUT VOLTAGE (V)

-20

2.49980

MAX5304-08

VREF = +3.6Vp-p

CODE = FULL SCALE

fIN = 1kHz

1.6

6.0

SUPPLY VOLTAGE (V)

0.5

-75

-80

0

-20

-70

-85

50

1

0

-60

-65

150

100

MAX5304-07

POWER-DOWN SUPPLY CURRENT (A)

2.5M

FREQUENCY (Hz)

POWER-DOWN SUPPLY CURRENT

vs. TEMPERATURE

2M

1.5M

MAX5304-06

-0.050

SIGNAL AMPLITUDE (dB)

MAX5304

10-Bit Voltage-Output DAC

in 8-Pin MAX

-100

1k

10k

LOAD ()

100k

1M

0.5

1.6

2.7

3.8

FREQUENCY (kHz)

_______________________________________________________________________________________

4.9

6.0

10-Bit Voltage-Output DAC

in 8-Pin MAX

(VDD = +5V, RL = 5k, CL = 100pF, TA = +25C, unless otherwise noted.)

DIGITAL FEEDTHROUGH (fSCLK = 100kHz)

MAX5304-11a

MAX5304-10a

MAJOR-CARRY TRANSITION

CS

5V/div

SCLK

2V/div

OUT

AC-COUPLED

100mV/div

OUT

AC-COUPLED

10mV/div

CODE = 512

10s/div

2s/div

CS = 5V

MAX5304-12a

DYNAMIC RESPONSE

OUT

1V/div

GND

10s/div

GAIN = +2V/V, SWITCHING FROM CODE 0 TO 1005

_______________________________________________________________________________________

MAX5304

____________________________Typical Operating Characteristics (continued)

MAX5304

10-Bit Voltage-Output DAC

in 8-Pin MAX

_____________________Pin Description

FB

PIN

NAME

FUNCTION

OUT

CS

Chip-Select Input. Active low.

DIN

Serial-Data Input

SCLK

Serial-Clock Input

FB

REF

Reference Voltage Input

REF

GND

Ground

AGND

VDD

Positive Power Supply

DAC Output Voltage

2R

2R

2R

OUT

2R

2R

MSB

DAC Output Amplifier Feedback

SHOWN FOR ALL 1s ON DAC

Figure 1. Simplified DAC Circuit Diagram

_______________Detailed Description

The MAX5304 contains a voltage-output digital-to-analog converter (DAC) that is easily addressed using a

simple 3-wire serial interface. Each IC includes a 16-bit

shift register, and has a double-buffered input composed of an input register and a DAC register (see the

Functional Diagram). In addition to the voltage output,

the amplifiers negative input is available to the user.

The DAC is an inverted R-2R ladder network that converts a digital input (10 data bits plus 3 sub-bits) into an

equivalent analog output voltage in proportion to the

applied reference voltage. Figure 1 shows a simplified

circuit diagram of the DAC.

Reference Inputs

The reference input accepts positive DC and AC signals. The voltage at the reference input sets the fullscale output voltage for the DAC. The reference input

voltage range is 0V to (VDD - 1.4V). The output voltage

(VOUT) is represented by a digitally programmable voltage source, as expressed in the following equation:

VOUT = (VREF NB / 1024) Gain

where NB is the numeric value of the DACs binary

input code (0 to 1023), VREF is the reference voltage,

and Gain is the externally set voltage gain.

The impedance at the reference input is code dependent, ranging from a low value of 18k when the DAC

has an input code of 1550 hex, to a high value exceeding several gigohms (leakage currents) with an input

code of 0000 hex. Because the input impedance at the

reference pin is code dependent, load regulation of the

reference source is important.

6

In shutdown mode, the MAX5304s REF input enters a

high-impedance state with a typical input leakage current of 0.001A.

The reference input capacitance is also code dependent and typically ranges from 15pF (with an input

code of all 0s) to 50pF (at full scale).

The MAX873 +2.5V reference is recommended for use

with the MAX5304.

Output Amplifier

The MAX5304s DAC output is internally buffered by a

precision amplifier with a typical slew rate of 0.6V/s.

Access to the output amplifiers inverting input provides

the user greater flexibility in output gain setting/signal

conditioning (see the Applications Information section).

With a full-scale transition at the MAX5304 output, the

typical settling time to 1/2LSB is 10s when loaded

with 5k in parallel with 100pF (loads less than 2k

degrade performance).

The amplifiers output dynamic responses and settling

performances are shown in the Typical Operating

Characteristics.

Shutdown Mode

The MAX5304 features a software-programmable shutdown that reduces supply current to a typical value of

4A. Writing 111X XXXX XXXX XXXX as the input-control word puts the device in shutdown mode (Table 1).

_______________________________________________________________________________________

10-Bit Voltage-Output DAC

in 8-Pin MAX

MAX5304

SCLK

SK

DIN

SO

CS

I/O

MAX5304

In shutdown mode, the amplifiers output and the reference input enter a high-impedance state. The serial

interface remains active. Data in the input register is

retained in shutdown, allowing the MAX5304 to recall

the output state prior to entering shutdown. Exit shutdown mode by either recalling the previous configuration or updating the DAC with new data. When

powering up the device or bringing it out of shutdown,

allow 20s for the outputs to stabilize.

MICROWIRE

PORT

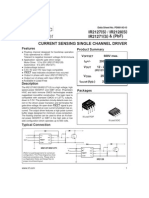

Serial-Interface Configurations

The MAX5304s 3-wire serial interface is compatible

with MICROWIRE (Figure 2) and SPI/QSPI (Figure 3).

The serial-input word consists of three control bits followed by 10+3 data bits (MSB first), as shown in Figure

4. The 3-bit control code determines the MAX5304s

response outlined in Table 1.

The MAX5304s digital inputs are double buffered.

Depending on the command issued through the serial

interface, the input register can be loaded without

affecting the DAC register, the DAC register can be

loaded directly, or the DAC register can be updated

from the input register (Table 1).

Figure 2. Connections for MICROWIRE

+5V

Serial-Interface Description

The MAX5304 requires 16 bits of serial data. Table 1

lists the serial-interface programming commands. For

certain commands, the 10+3 data bits are dont

cares. Data is sent MSB first and can be sent in two 8bit packets or one 16-bit word (CS must remain low

until 16 bits are transferred). The serial data is composed of three control bits (C2, C1, C0), followed by

the 10+3 data bits D9...D0, S2, S1, S0 (Figure 4). Set

the sub-bits (S2, S1, S0) to zero. The 3-bit control code

determines the register to be updated and the configuration when exiting shutdown.

Figure 5 shows the serial-interface timing requirements.

The chip-select pin (CS) must be low to enable the

DACs serial interface. When CS is high, the interface

control circuitry is disabled. CS must go low at least

tCSS before the rising serial-clock (SCLK) edge to properly clock in the first bit. When CS is low, data is

clocked into the internal shift register through the serialdata input pin (DIN) on SCLKs rising edge. The maximum guaranteed clock frequency is 10MHz. Data is

latched into the MAX5304 input/DAC register on CSs

rising edge.

SS

DIN

MAX5304

MOSI

SCLK

SCK

CS

SPI/QSPI

PORT

I/O

CPOL = 0, CPHA = 0

Figure 3. Connections for SPI/QSPI

MSB ..................................................................................LSB

16 Bits of Serial Data

Control

Bits

C2

C1

Data Bits

MSB............................LSB Sub-Bits

C0

D9 ...............................D0, S2, S1, S0

3 Control

Bits

10+3 Data Bits

Figure 4. Serial-Data Format

_______________________________________________________________________________________

MAX5304

10-Bit Voltage-Output DAC

in 8-Pin MAX

Table 1. Serial-Interface Programming Commands

16-BIT16-BIT

SERIAL

SERIAL

WORDWORD

C2 C1

FUNCTION

C0

D9.......................D0

MSB

LSB

S2...S0

10 bits of data

000

Load input register; DAC register immediately updated (also exit

shutdown).

10 bits of data

000

Load input register; DAC register unchanged.

XXXXXXXXXX

XXX

Update DAC register from input register (also exit shutdown; recall

previous state).

XXXXXXXXXX

XXX

Shutdown

XXXXXXXXXX

XXX

No operation (NOP)

X = Dont care

CS

COMMAND

EXECUTED

SCLK

1

DIN

8

C1

C2

C0

D9

D8

D7

D6

D5

9

D4

16

D3

D2

D1

D0

S2

S1

S0

Figure 5. Serial-Interface Timing Diagram

tCSW

CS

tCSO

tCSS

tCL

tCH

tCP

tCSH

tCS1

SCLK

tDS

tDH

DIN

Figure 6. Detailed Serial-Interface Timing Diagram

_______________________________________________________________________________________

10-Bit Voltage-Output DAC

in 8-Pin MAX

MAX5304

DIN

SCLK

CS1

CS2

TO OTHER

SERIAL DEVICES

CS3

CS

CS

CS

MAX5304

MAX5304

MAX5304

SCLK

SCLK

SCLK

DIN

DIN

DIN

Figure 7. Multiple MAX5304s Sharing Common DIN and SCLK Lines

Figure 7 shows a method of connecting several

MAX5304s. In this configuration, the clock and the data

bus are common to all devices, and separate chipselect lines are used for each IC.

Applications Information

Table 2. Unipolar Output Codes

MSB

DAC CONTENTS

LSB

11 1111 1111

(000)

1023

+VREF

1024

10 0000 0001

(000)

513

+VREF

1024

10 0000 0000

(000)

512

+ VREF

+VREF

=

2

1024

01 1111 1111

(000)

511

+VREF

1024

00 0000 0001

(000)

1

+VREF

1024

00 0000 0000

(000)

0V

Unipolar Output

For a unipolar output, the output voltage and the reference input have the same polarity. Figure 8 shows the

MAX5304 unipolar output circuit, which is also the typical operating circuit. Table 2 lists the unipolar output

codes.

Figure 9 illustrates a Rail-to-Rail output configuration.

This circuit shows the MAX5304 with the output amplifier configured for a closed-loop gain of +2V/V to provide

a 0 to 5V full-scale range when a 2.5V reference is used.

Bipolar Output

The MAX5304 output can be configured for bipolar

operation using Figure 10s circuit according to the following equation:

VOUT = VREF [(2NB / 1024) - 1]

where NB is the numeric value of the DACs binary

input code. Table 3 shows digital codes (offset binary)

and corresponding output voltages for Figure 10s circuit.

Rail-to-Rail is a registered trademark of Nippon Motorola, Ltd.

ANALOG OUTPUT

Note: ( ) are for sub-bits.

Using an AC Reference

In applications where the reference has AC signal components, the MAX5304 has multiplying capability within

the reference input range specifications. Figure 11

shows a technique for applying a sine-wave signal to

the reference input where the AC signal is offset before

being applied to REF. The reference voltage must

never be more negative than GND.

_______________________________________________________________________________________

MAX5304

10-Bit Voltage-Output DAC

in 8-Pin MAX

Table 3. Bipolar Output Codes

MSB

DAC CONTENTS

LSB

11 1111 1111

ANALOG OUTPUT

511

+VREF

512

(000)

1

+VREF

512

10 0000 0001

(000)

10 0000 0000

(000)

01 1111 1111

(000)

1

-VREF

512

00 0000 0001

(000)

511

-VREF

512

00 0000 0000

(000)

0V

The MAX5304s total harmonic distortion plus noise

(THD+N) is typically less than -77dB (full-scale code),

given a 1Vp-p signal swing and input frequencies up to

25kHz. The typical -3dB frequency is 650kHz, as

shown in the Typical Operating Characteristics graphs.

Digitally Programmable Current Source

Figure 12s circuit places an NPN transistor (2N3904 or

similar) within the op amp feedback loop to implement

a digitally programmable, unidirectional current source.

The output current is calculated with the following

equation:

IOUT = (VREF / R)(NB / 1024)

where NB is the numeric value of the DACs binary

input code, and R is the sense resistor shown in Figure

12.

512

-VREF

= - VREF

512

Note: ( ) are for sub-bits.

+5V

+5V

REF

REF

VDD

VDD

FB

MAX5304

10k

FB

MAX5304

10k

DAC

OUT

GND

Figure 8. Unipolar Output Circuit

10

DAC

OUT

GND

Figure 9. Unipolar Rail-to-Rail Output Circuit

______________________________________________________________________________________

10-Bit Voltage-Output DAC

in 8-Pin MAX

MAX5304

+5V

R1

R2

REF

+5V

26k

AC

REFERENCE

INPUT

+5V

VDD

MAX495

500mVp-p

V+

FB

10k

VDD

REF

VOUT

DAC

OUT

DAC

V-

OUT

MAX5304

GND

MAX5304

GND

R1 = R2 = 10k 0.1%

Figure 10. Bipolar Output Circuit

Figure 11. AC Reference Input Circuit

Power-Supply Considerations

+5V

REF

VDD

VL

MAX5304

IOUT

DAC

OUT

2N3904

FB

GND

Figure 12. Digitally Programmable Current Source

On power-up, the input and DAC registers are cleared

(set to zero code). For rated MAX5304 performance,

REF must be at least 1.4V below VDD. Bypass VDD with

a 4.7F capacitor in parallel with a 0.1F capacitor to

GND. Use short lead lengths, and place the bypass

capacitors as close to the supply pins as possible.

Grounding and Layout Considerations

Digital or AC transient signals on GND can create noise

at the analog output. Connect GND to the highest-quality ground available. Good PC board ground layout

minimizes crosstalk between the DAC output, reference

input, and digital input. Reduce crosstalk by keeping

analog lines away from digital lines. Wire-wrapped

boards are not recommended.

___________________Chip Information

TRANSISTOR COUNT: 3053

SUBSTRATE CONNECTED TO AGND

______________________________________________________________________________________

11

10-Bit Voltage-Output DAC

in 8-Pin MAX

8LUMAXD.EPS

MAX5304

Package Information

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are

implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

12 ____________________Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600

1999 Maxim Integrated Products

Printed USA

is a registered trademark of Maxim Integrated Products.

Anda mungkin juga menyukai

- Max 5541Dokumen9 halamanMax 5541rohitkiranbrBelum ada peringkat

- Ad 421Dokumen14 halamanAd 421Vishal Devrao JadhavBelum ada peringkat

- Potenciometro Digial Dac80Dokumen10 halamanPotenciometro Digial Dac80Katherine Marin VieiraBelum ada peringkat

- ADC128S022Dokumen20 halamanADC128S022Jorge WattesBelum ada peringkat

- Features Description: Sbas127D - September 2000 - Revised June 2006Dokumen21 halamanFeatures Description: Sbas127D - September 2000 - Revised June 2006Jesus Gerardo Esparza LopezBelum ada peringkat

- General Description Features: Bipolar/CMOS/DMOSDokumen13 halamanGeneral Description Features: Bipolar/CMOS/DMOSjavierrincon800Belum ada peringkat

- Micro: Description FeaturesDokumen20 halamanMicro: Description FeaturespopcriBelum ada peringkat

- Max038 Generador de FuncionesDokumen17 halamanMax038 Generador de FuncionesLuis Rodolfo Reyes JimenezBelum ada peringkat

- MAX31865 RTD-to-Digital Converter: General Description FeaturesDokumen25 halamanMAX31865 RTD-to-Digital Converter: General Description FeaturespaKoSTe1Belum ada peringkat

- CDP1802 DatasheetDokumen28 halamanCDP1802 DatasheetDaveBelum ada peringkat

- WM9701A Low Power AC'97 Multimedia Audio Codec: Description FeaturesDokumen0 halamanWM9701A Low Power AC'97 Multimedia Audio Codec: Description FeaturesJorBS57Belum ada peringkat

- MAX038Dokumen17 halamanMAX038Brane PetkoskiBelum ada peringkat

- Tda 8780Dokumen16 halamanTda 8780Andrey DolgovBelum ada peringkat

- Features Applications: X+ X - Y+ YDokumen35 halamanFeatures Applications: X+ X - Y+ YAlvaro ChaconBelum ada peringkat

- Low-Power, 12-Bit Voltage-Output Dacs With Serial InterfaceDokumen16 halamanLow-Power, 12-Bit Voltage-Output Dacs With Serial InterfaceMarcelo FerreiraBelum ada peringkat

- Ad8421 PDFDokumen28 halamanAd8421 PDFsoft4gsmBelum ada peringkat

- 6700 - DatasheetDokumen2 halaman6700 - DatasheetsrgroupsBelum ada peringkat

- Max9632 PDFDokumen15 halamanMax9632 PDFjorge castilloBelum ada peringkat

- Low-Cost, Triple, 8-Bit Voltage-Output Dacs With Serial InterfaceDokumen16 halamanLow-Cost, Triple, 8-Bit Voltage-Output Dacs With Serial InterfaceBboubrahim BbnnBelum ada peringkat

- TLC 7628Dokumen12 halamanTLC 7628velizarkoBelum ada peringkat

- DAC0808 DatasheetDokumen12 halamanDAC0808 DatasheetRicky CoxBelum ada peringkat

- Dac121 - 12bit DacDokumen19 halamanDac121 - 12bit DackoltearunBelum ada peringkat

- 3 V To 5 V Single Supply, 200 KSPS 8-Channel, 12-Bit Sampling ADC AD7858/AD7858LDokumen36 halaman3 V To 5 V Single Supply, 200 KSPS 8-Channel, 12-Bit Sampling ADC AD7858/AD7858Ljnax101Belum ada peringkat

- Linear - 16-Bit, Ultra Precise, Fast Settling VOUT DACDokumen16 halamanLinear - 16-Bit, Ultra Precise, Fast Settling VOUT DACAtakan OzturKBelum ada peringkat

- 3 V/5 V, 1 MW 2-/3-Channel 16-Bit, Sigma-Delta Adcs: A MaxDokumen32 halaman3 V/5 V, 1 MW 2-/3-Channel 16-Bit, Sigma-Delta Adcs: A Maxmeroka2000Belum ada peringkat

- Max 31865 DatasheetDokumen25 halamanMax 31865 Datasheetalexender2kBelum ada peringkat

- Ad7730 7730LDokumen52 halamanAd7730 7730LDa Q ShaBelum ada peringkat

- ADC0803, ADC0804: 8-Bit, Microprocessor-Compatible, A/D Converters FeaturesDokumen17 halamanADC0803, ADC0804: 8-Bit, Microprocessor-Compatible, A/D Converters FeaturesJorge Luis Castillo GuarachiBelum ada peringkat

- ADC0803, ADC0804: 8-Bit, Microprocessor-Compatible, A/D Converters FeaturesDokumen18 halamanADC0803, ADC0804: 8-Bit, Microprocessor-Compatible, A/D Converters FeaturesMarco MenezesBelum ada peringkat

- 10.709 Gbps Laser Diode Driver Chipset: A To 1200 ADokumen12 halaman10.709 Gbps Laser Diode Driver Chipset: A To 1200 ABanyugeaBelum ada peringkat

- Dual, Ultra-Low-Power, 10-Bit, Voltage-Output Dacs: General Description FeaturesDokumen23 halamanDual, Ultra-Low-Power, 10-Bit, Voltage-Output Dacs: General Description Featuresdaredev127Belum ada peringkat

- Ads 7825Dokumen21 halamanAds 7825geo888007Belum ada peringkat

- MAX5556 Stereo Audio 16b DACDokumen19 halamanMAX5556 Stereo Audio 16b DACJennifer NealBelum ada peringkat

- MAX9947ETE+ Marking Code AHFDokumen17 halamanMAX9947ETE+ Marking Code AHFZamir HussainBelum ada peringkat

- 16-Bit, Serial Input Multiplying Digital-to-Analog ConverterDokumen16 halaman16-Bit, Serial Input Multiplying Digital-to-Analog ConverternhbrBelum ada peringkat

- Ca3306 (A, C)Dokumen17 halamanCa3306 (A, C)notaden1849Belum ada peringkat

- Max7426 Max7427Dokumen12 halamanMax7426 Max7427ridzim4638100% (1)

- +3 Volt, Serial Input Complete 12-Bit DAC AD8300Dokumen8 halaman+3 Volt, Serial Input Complete 12-Bit DAC AD8300jnax101Belum ada peringkat

- A 6275 EatDokumen12 halamanA 6275 Eatn_t_162Belum ada peringkat

- sc7001q Ay 961Dokumen18 halamansc7001q Ay 961r2c1Belum ada peringkat

- Max3160 Max3162Dokumen23 halamanMax3160 Max3162jb2015831Belum ada peringkat

- OpAmp - MCP6244Dokumen38 halamanOpAmp - MCP6244Ludwig SchmidtBelum ada peringkat

- Ak 5358Dokumen18 halamanAk 5358Alver TuizaBelum ada peringkat

- Features Description: Sbas090B - September 2000 - Revised May 2002Dokumen17 halamanFeatures Description: Sbas090B - September 2000 - Revised May 2002alaska112Belum ada peringkat

- LC Mos High Speed 4-And 8-Channel 8-Bit Adcs Ad7824/Ad7828Dokumen16 halamanLC Mos High Speed 4-And 8-Channel 8-Bit Adcs Ad7824/Ad7828meroka2000Belum ada peringkat

- Integrated Circuit Systems, IncDokumen11 halamanIntegrated Circuit Systems, Incroger marqBelum ada peringkat

- High Speed, Monolithic D/A Converter With Reference FeaturesDokumen10 halamanHigh Speed, Monolithic D/A Converter With Reference FeaturessohcahtoaBelum ada peringkat

- Max 2981Dokumen13 halamanMax 2981Jamila RobinsonBelum ada peringkat

- HS-2420RH - Fast Sample and HolDokumen8 halamanHS-2420RH - Fast Sample and HolDeepa DevarajBelum ada peringkat

- Max7490 Max7491Dokumen18 halamanMax7490 Max7491xo9o6Belum ada peringkat

- DAC1020Dokumen14 halamanDAC1020micochangoBelum ada peringkat

- DS8500Dokumen7 halamanDS8500abdulmajeed_cetBelum ada peringkat

- Max1366 Max1368Dokumen36 halamanMax1366 Max1368linuxsu123Belum ada peringkat

- Max 1718Dokumen35 halamanMax 1718bmmostefaBelum ada peringkat

- Max 6954Dokumen39 halamanMax 6954danysan2525Belum ada peringkat

- Mcp3208 - AdcDokumen34 halamanMcp3208 - AdcNeneFIBelum ada peringkat

- Semiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsDari EverandSemiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsBelum ada peringkat

- Analog Circuit Design: A Tutorial Guide to Applications and SolutionsDari EverandAnalog Circuit Design: A Tutorial Guide to Applications and SolutionsPenilaian: 3.5 dari 5 bintang3.5/5 (6)

- 2SD 2017 PDFDokumen1 halaman2SD 2017 PDFtabassam7801Belum ada peringkat

- CCTV General PDFDokumen97 halamanCCTV General PDFtabassam7801Belum ada peringkat

- Ir 2112Dokumen18 halamanIr 2112Valeriu DumitracheBelum ada peringkat

- Uc 1709Dokumen15 halamanUc 1709tabassam7801Belum ada peringkat

- Mic 4120Dokumen10 halamanMic 4120tabassam7801Belum ada peringkat

- LM 2575 TDokumen5 halamanLM 2575 Ttabassam7801Belum ada peringkat

- Ach4518 471 TD01Dokumen4 halamanAch4518 471 TD01tabassam7801Belum ada peringkat

- Lithium Ion Secondary Battery Applications Portable Equipment Applications Notebook PC ApplicationsDokumen11 halamanLithium Ion Secondary Battery Applications Portable Equipment Applications Notebook PC Applicationstabassam7801Belum ada peringkat

- Hall BookDokumen126 halamanHall BookbanguyenbkBelum ada peringkat

- Turn Ratio TestDokumen8 halamanTurn Ratio TestImran Nawaz MehthalBelum ada peringkat

- Vow 3120Dokumen11 halamanVow 3120tabassam7801Belum ada peringkat

- HLC2701Dokumen4 halamanHLC2701tabassam7801Belum ada peringkat

- Fy4aej 03Dokumen9 halamanFy4aej 03tabassam7801Belum ada peringkat

- IRF7103 (Dual)Dokumen9 halamanIRF7103 (Dual)tabassam7801Belum ada peringkat

- BDV64 - 65 Darliington Silicon Power TransistorDokumen4 halamanBDV64 - 65 Darliington Silicon Power Transistortabassam7801Belum ada peringkat

- IRF7103 (Dual)Dokumen9 halamanIRF7103 (Dual)tabassam7801Belum ada peringkat

- Automotive Mosfet 2010 BRDokumen16 halamanAutomotive Mosfet 2010 BRtabassam7801Belum ada peringkat

- Auto MOSFET NamingDokumen3 halamanAuto MOSFET Namingtabassam7801Belum ada peringkat

- BLF278 Wideband RF Power MosfetDokumen23 halamanBLF278 Wideband RF Power MosfetAmador Garcia IIIBelum ada peringkat

- Ir 2127Dokumen16 halamanIr 2127kimonspBelum ada peringkat

- 193 Universal BridgeDokumen4 halaman193 Universal Bridgetabassam7801Belum ada peringkat

- 74HC4050 CNV PDFDokumen7 halaman74HC4050 CNV PDFtare890Belum ada peringkat

- Alpha, Beta & Gamma DecayDokumen7 halamanAlpha, Beta & Gamma DecayFaisal ARBelum ada peringkat

- 2SD 882Dokumen10 halaman2SD 882tabassam7801Belum ada peringkat

- Ca 3083Dokumen4 halamanCa 3083tabassam7801Belum ada peringkat

- H1061Dokumen1 halamanH1061tabassam7801Belum ada peringkat

- 2N5401Dokumen4 halaman2N5401tabassam7801Belum ada peringkat

- A1271 (To 92)Dokumen1 halamanA1271 (To 92)Josué GarciaBelum ada peringkat

- Power Transistor: SPP11N60C3 SPI11N60C3, SPA11N60C3, SPA11N60C3 E8185 Cool MOS™Dokumen16 halamanPower Transistor: SPP11N60C3 SPI11N60C3, SPA11N60C3, SPA11N60C3 E8185 Cool MOS™tabassam7801Belum ada peringkat

- AO4620Dokumen7 halamanAO4620Victor ChangBelum ada peringkat

- D LinkDokumen3 halamanD LinkSkKimondouBelum ada peringkat

- 434 SMD FuseDokumen3 halaman434 SMD Fusekhuseyin13186Belum ada peringkat

- CE Model Question Paper 2019 - 16ME72Dokumen3 halamanCE Model Question Paper 2019 - 16ME72ashitaBelum ada peringkat

- Chapter7 Input Output Organization PDFDokumen19 halamanChapter7 Input Output Organization PDFjijin kBelum ada peringkat

- Finals Cheat SheetDokumen2 halamanFinals Cheat SheetVance TanBelum ada peringkat

- Datasheet Fba3 Force Balance Accelerometer KinemetricsDokumen2 halamanDatasheet Fba3 Force Balance Accelerometer KinemetricssimonjmorBelum ada peringkat

- Littelfuse SIDACtor DO 214 Datasheet PDFDokumen5 halamanLittelfuse SIDACtor DO 214 Datasheet PDFdvalinaBelum ada peringkat

- Service Manual: IndexDokumen29 halamanService Manual: IndexAnh ĐườngBelum ada peringkat

- Exercise 1.: Single Phase Load&compensationDokumen3 halamanExercise 1.: Single Phase Load&compensationhuynhvanan24930% (1)

- Seminar ReportDokumen30 halamanSeminar Reportperky_ashish50% (4)

- Naval Antenna Products & Systems BrochureDokumen2 halamanNaval Antenna Products & Systems BrochureBALAJI037Belum ada peringkat

- Sample Problems RC TransientDokumen15 halamanSample Problems RC TransientLurking VIperBelum ada peringkat

- EV1016TURBOX: Turbo HD DVRDokumen2 halamanEV1016TURBOX: Turbo HD DVRFernando Alberto Perea MendezBelum ada peringkat

- Esab LAR 500-630 Magma ServicemanualDokumen64 halamanEsab LAR 500-630 Magma ServicemanualTommy MellemstrandBelum ada peringkat

- Funai 29a-250-450 Service ManualDokumen70 halamanFunai 29a-250-450 Service Manualgnaks58Belum ada peringkat

- Physics Project On TransformerDokumen11 halamanPhysics Project On Transformertechnical mania0% (1)

- RX Controller IP For MIPI CSI-2 v2.1Dokumen2 halamanRX Controller IP For MIPI CSI-2 v2.1prasadBelum ada peringkat

- Answer Essay 18 Capacitor 2005 PDFDokumen3 halamanAnswer Essay 18 Capacitor 2005 PDFWong Chai YenBelum ada peringkat

- Electrical Drive Unit-Ii: Vii Semester ETEE-401Dokumen100 halamanElectrical Drive Unit-Ii: Vii Semester ETEE-401Jeet DattaBelum ada peringkat

- Isolation 62109Dokumen11 halamanIsolation 62109Shahid KhanBelum ada peringkat

- 5 VregDokumen34 halaman5 VregWaddy123Belum ada peringkat

- Alia Arc900 ManualDokumen49 halamanAlia Arc900 ManualRexCrazyMind0% (1)

- Cpu IdDokumen1 halamanCpu IdJoao LuisBelum ada peringkat

- Service Manual: TA-FB930RDokumen24 halamanService Manual: TA-FB930RMaikel Borges IglesiasBelum ada peringkat

- Usb ItnDokumen6 halamanUsb ItnEU VaBelum ada peringkat

- NB To CP1E-N S1 To E5CC TEMP Controller With NBDokumen166 halamanNB To CP1E-N S1 To E5CC TEMP Controller With NBRitesh MunjalBelum ada peringkat

- VITA 48.0, 48.1, and 48.2 Recognized As American National StandardsDokumen2 halamanVITA 48.0, 48.1, and 48.2 Recognized As American National Standards1Belum ada peringkat

- SiemensDokumen23 halamanSiemensRahul JainBelum ada peringkat

- Pci DriversDokumen36 halamanPci DriversAxayacatl Alanis NarvaezBelum ada peringkat

- User Instructions: To Start Charging To Stop ChargingDokumen1 halamanUser Instructions: To Start Charging To Stop ChargingSebastin ElsinBelum ada peringkat