An Efficient Implementation of Wallace Tree Multiplier

Diunggah oleh

Editor IJRITCCHak Cipta

Format Tersedia

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniHak Cipta:

Format Tersedia

An Efficient Implementation of Wallace Tree Multiplier

Diunggah oleh

Editor IJRITCCHak Cipta:

Format Tersedia

International Journal on Recent and Innovation Trends in Computing and Communication

Volume: 4 Issue: 3

ISSN: 2321-8169

442 - 445

_______________________________________________________________________________________

An Efficient Implementation of Wallace Tree Multiplier

Anagh P. Deshpande

Mtech:Very large Scale

Integration(VLSI) design

School of Electronics

Engineering(SENSE)

VIT University, Chennai

anagh.deshpande22@gmail.com

Ameya A. Chandras

Dr. Vigneswaran T.

Mtech:Very large Scale

Integration(VLSI) design

School of Electronics

Engineering(SENSE)

VIT University, Chennai

ameyaa.chandras@gmail.com

Professor

School of Electronics

Engineering(SENSE)

VIT University, Chennai

vigneswaran.t@vit.ac.in

Abstract In Very large Scale Integration (VLSI) technology, power consumption and speed are the two important constraints for determining

the efficiency of the architecture. This paper aspires at declining this parameters of the Wallace tree multiplier with the efficient use of modified

Booth encoding and compressors.The proposed architecture is employed in Verilog HDL and it is simulated in Cadence NC Sim and synthesized

using Encounter RTL Compiler in 180nm Taiwan Semiconductor Manufacturing Company(TSMC) slow library .The proposed architecture is

found to be 42.2% faster than the conventional Wallace tree architecture and the power consumption lowered by 45% as compared to the

conventional Wallace Tree.

KeywordsWallace tree; Booth Encoder; Compressor;

__________________________________________________*****_________________________________________________

I. INTRODUCTION

II. BACKGROUND STUDY

Multipliers are extremely vital in any basic algorithmic

computation. Many researchers have done stupendous work on

the design of increasingly efficient multipliers which plays a

significant role in applications like digital signal processing

system where effective utilization of processing time with

minimum latency is most sought out. They aspire to provide

this with lesser power consumption. This makes them easier to

implement in various composite and wieldy circuits.

A . Conventional Wallace Tree

Conventional Wallace tree is an excellent approach to reduce

partial product reduction. It was first proposed by C.S Wallace

in 1964[2]. It was then used by many research scholars for

above purpose. Instead of directly adding partial products, it

suggest that once partial product array is formed, we can

arrange adjacent rows intonon-imbrication groups of ternary.

Each group is then reduced by either applying full adder or half

adders depending on input bits and then moving any single bits

to the next stage. This kind of process is carried out for each

stage until only two rows are remaining. Then finally those row

are added by Ripple arry adder. This process is demonstrated

by 8 bit by 8 bit typical Wallace tree depicted by Fig. 1 .

This section depicts the definition of the terms which

are introduced in this paper. Section 2 goes over the traditional

approaches of Wallace tree architecture. Section 3 comprises

of modified Wallace architecture for multiplier reduction.

Section 4 compares the results of modified Wallace tree

architecture with typical one.Section 5 summarizes the

conclusions.

Multipliers comprises of ternary stages viz formation

of partial products,accumulation and downsizing of partial

products and final addition of the last stage.The first stage is

simply the AND operation of each bit of the multiplier and

multiplicand. Booth encoding can be used in this stage by

which we can decrement the number of partial products. The

second stage is decrement in the number of partial products

which is utmost vital as it is more intricate and that decides

speed of whole multiplier. This stage normally conduces the

most of the latency, power and area of the multiplier. The final

stage contains various adders to generate the final output by

summing up two rows of partial products. The typical Wallace

tree multiplier employ carry save adders to cut down N-row

bit product matrix to a commensurate two row matrix [1]. The

obtained matrix, then is added up by carry look ahead adder to

yield the output.In the regard of adders in the intermediate

stage, the conventional Wallace tree uses full adders and half

adder[2].This paper is all about reduction of delay in the

computation time of multiplication with lesser power

consumption. For the above mentioned purpose, compressors

are utilized in the architecture of the multiplier.

Figure 1. Conventional Wallace Tree

III. PROPOSED ARCHITECTURE

The architecture of the proposed Wallace tree multiplier using

Booth encoder and 3:2 compressorcompromises of four blocks

of operation.In the following subsections,every component is

explained.

442

IJRITCC | March 2016, Available @ http://www.ijritcc.org

___________________________________________________________________________________________________

International Journal on Recent and Innovation Trends in Computing and Communication

Volume: 4 Issue: 3

ISSN: 2321-8169

442 - 445

_______________________________________________________________________________________

Figure 3. Grouping of 3 bits of multiplier for Booth encoding

Let

M D/2-1

M i * 2 2i

i 0

(3)

MD/2-1

2i (4)

(2 x 2i 1 x 2i x 2i 1 ) * 2

i 0

In the above equation (3), the possible values of Mi can be

2,-1,0,+1,+2}.

The product can be represented as follows:

Z A X

Figure 2. Proposed Architechure

For the multiplication of signed numbers ,it is utmost

important for complementing the multiplicand i.e. ones

complement generator. This can be achieved by generating

inverted bits(changing 1 to 0 and vice-a-versa) of the

multiplicand. Ones complement is nothing but the negative of

the original multiplicand. It is essential for the partial product

generator to easily distinguish between multiplication of both

signed as well as unsigned multiplication.

B. Booth Encoder:

Traditionally, multiplication includes calculation of partial

products by ANDing operation and then subsequently adding

all those partial products. When we multiply a N bit number

by another N bit number, the total number of partial products

generated equals to 2 .In the architecture, modified booth

encoder is used for reduction of partial produts and to speed up

the computation of the partial product array. Thus, the number

of partial products can be reduced from 2 to (N/2 -1).Booth

encoder enables the multiplication of positive as well as

negative numbers.[3]Let A and X be two N bit numbers where

A is the multiplicand and X is the multiplier.

They can be represented by equations (1) and (2) respectively.

N-2

i

a i *2

i 0

N

-2

xN 12 N 1 x 2 i (2)

i 0

(5)

where, Pi is the product bit at i-th iteration which can be

represented as

A. Ones complement generator

A aN 12 N 1

2MD-1

i

Pi * 2

i 0

{-

(1)

where aiis the i-th bit of multiplicand and xiis the i-th bit of the

multiplier[4].

In the proposed architecture, we are using radix -4 modified

Booth encoder to encode the multiplier bits. The radix-4

modified Booth encoding includes scanning the multiplier

with a window size of 3bits or simply called as scanning of

triplets. The grouping of the 3bits can be done as shown in the

Figure 2.

(MD- 2)/2

2i

(2 x 2i 1 x 2i x 2i 1 )* 2 A

i 0

(MD- 2)/2

Si

i 0

(6)

(7)

where, Si is grouping of 3bits of the multiplier starting from

LSB to MSB by overlapping the significant bit of the previous

grouping.

Considering N=8, the possible values of Mi are {-2,1,0,+1,+2}.

The modified Booth encoding values are as shown in the

following table.

TABLE I.

D2(x2i

+1

0

0

0

0

1

1

1

1

D1(x

D0(x

2i)

2i-1)

0

0

1

1

0

0

1

1

0

1

0

1

0

1

0

1

BOOTH ENCODER VALUES

Operati

on

+0

+X

+X

+2X

+2X

-X

-X

-0

Ne

g

0

0

0

0

1

1

1

1

Tw

o

0

0

0

1

1

0

0

0

On

e

0

1

1

0

0

1

1

0

Zer

o

1

0

0

0

0

0

0

1

Co

r

0

0

0

0

1

1

1

0

(-X) denotes the 2s complement of the number which can be

obtained by inverting the bits of X and adding 1 to the LSB. (2X) can be obtained by doing left shift operation on (-X) by

one bit and putting 0 at the LSB position.

(+2X) can be obtained by doing left shift operation on (X) by

one bit and putting 0 at the LSB position.

The equivalent circuit of the Booth encoder can be designed

from the values obtained in the Table 1 as shown in figure 3

443

IJRITCC | March 2016, Available @ http://www.ijritcc.org

___________________________________________________________________________________________________

International Journal on Recent and Innovation Trends in Computing and Communication

Volume: 4 Issue: 3

ISSN: 2321-8169

442 - 445

_______________________________________________________________________________________

D. Wallace tree using 3:2 Compressor

BOOTH ENCODER

neg

D2

D1

D0

two

D2

D1

The conventional Wallace tree uses half adders and

full adders as carry save adders. But this leads to increased

delay in the computation of partial products. In order to reduce

this latency, the full adders are replaced with 3:2 compressors

3:2 Compressors has XOR-XNOR and MUX as building

blocks. So delay of this device is XOR+ MUX [5] .

one

D0

D1

D0

cor

D2

D2

D1

zero

D0

Figure 4. Booth encoder circuit

The D2,D1,D0 are the 3bits of the multiplier which are fed as

the input to the Booth encoder. The neg bit will notify whether

a negative number has been multiplied to the multiplicand or

not. Zero bit tells whether it is to be considered as partial

product or not. One bit indicates the direct use of multiplicand

and two bit indicates whether left shift operation is needed or

not and the cor bit is the error correction bit which is to be

summed with the last partial product.

C. Partial Product Generator

Partial product generator is designed by the use of

multiplexers as shown in figure(5).The multiplicand and the

complement of the multiplicand are the two inputs which are

fed to the multiplexer and the neg acts as a select signal for it.

The next stage multiplexer has combination of two, one and

zero bits as the select signal. Any one of them will be high at a

time. The previous state of the input will be given as output if

two is high, the output of the multiplexer in the first stage will

be given as the input to the multiplexer in the second stage and

the output will be 0 if the zero bit is high. After one iteration,

one partial product bit will be produced. The whole logic can

be repeated for the generation of all partial product bits.

Figure 6. 3:2 Compressor

P1,P2,P3 are the three inputs of the 3:2 compressors whereas

SUM and CARRY are the ouputs of the 3: 2 compressors[6].

The structure can be represented using,

S = (P1^P2)*(P3) + (P1^P2)*(P3)

(6)

C=(P1^P2)*(P3)+(P1^P2)*(P1)(7)

IV. SIMULATION AND RESULTS

RTL schematic for Wallace tree multiplier using modified

Booth encoding and compressor was generated successfully by

the RTL compiler with the use of constraints file and output is

verified by Cadence NC Sim simulation[7].

Figure 7. Simulated output waveform of conventional Wallace

tree multiplier

Figure 5. Partial Product Generator

Figure 8. Simulated output waveform of Booth encoded

Wallace tree without compressor

444

IJRITCC | March 2016, Available @ http://www.ijritcc.org

___________________________________________________________________________________________________

International Journal on Recent and Innovation Trends in Computing and Communication

Volume: 4 Issue: 3

ISSN: 2321-8169

442 - 445

_______________________________________________________________________________________

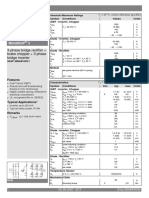

From the above table, we can infer that , in terms of area

conventional Wallace tree multiplier performs better. In the

power consumption, Wallace tree multiplier with Booth

encoding and compressor achieve less value. But Wallace tree

with Booth encoding works faster than the rest of the

architecture.

V .CONCLUSION

Figure 9.Simulated output waveform of the proposed Wallace

tree multiplier with Booth encoding and compressor

The following tabulated parameters in the Table II below

were formulated using the Cadence Encounter RTL

Compilers power,timing and area reports respectively.

The proposed architecture is better than conventional Wallace

tree by 45% in terms of power consumption. The speed of

Wallace tree multiplier with Booth encoding and compressor

is better by 42.2% than conventional Wallace tree . The delay

is reduced by the use of Booth encoding and compressor. To

further reduce power consumption and to improve the speed of

architecture ,4:2 compressor can be used[8] [9].

REFERENCES

[1]

[2]

TABLE II.

COMPARATIVE TABLE

Power(nw)

[3]

Delay(ns)

Cells

Area

Conventional

402062.22

Wallace Tree

multiplier

9.851

284

7152

Wallace tree 222072.70

multiplier with

Booth

encoding

6.103

Wallace Tree 220859.02

multiplier with

Booth

encoding and

Compressor

6.924

[4]

[5]

266

10372

[6]

322

10605

[7]

[8]

[9]

Ron walters,Earl Swartzlander,A reduced complexity Wallace

multiplier reduction, IEEE Trans.,Vol 59,no 8, 2010.

C.Wallace,The

suggestion

of

fast

multitplier,IEEE

Trans.Electron.Comp.vol.EC/13,pt.14/17,Feb 1964

J. fadavi-Ardekani,MxN Booth encoded Multiplier Generator

using optimized wallace trees, IEEE Trans.vol.1,no2, june1993.

J.Pi ng Wang,Shiann-Rong Kuang, Shish- chang Liang.High

accuracy fixed width modified Booth multipliers for lossy

application.

Shrivari Veermanchaneni, kirthi M,krishna Lingamneni Avinash

Sreekanth Reddy Puppala M.B. Srininvas.Novel Architecture

for High speed and low power 3-2,4-2 and 5-2

Compressors,20th International conference on Very large scale

integration design(VLSI),jan 2007.

J.Rao,Sanjay Dubey,A high Speed Wallace tree multiplier

using Booth algorithm for Fast Arithmetic circuits, IOSR

Journal of Electronics and Comm.Engg.(IOSRJECE) ISSN:

2278-2834,VOL 3, No. 1(sep-oct 2012),pp 07-11.

Cadence TDA Tools(RTL Compiler, NC Sim)

C.

Vinoth1,V.S.

Kanchana

Bhaaskaran2,B.Brindha,S.

Sakthikumaran,V.Kavinilavu,B.Bhaskar, M Kangasasabapathy

and B. Sharath ,A Novel low power and high speed Wallace

tree multiplier for RISC processor, @2011 IEEE

Prasad k.and Parhi K.k.,low power 4-2 and 5-2

compressors,@Proc of 35th Asilmour Confe.vol.1 ,2001,pp.

129-133.

445

IJRITCC | March 2016, Available @ http://www.ijritcc.org

___________________________________________________________________________________________________

Anda mungkin juga menyukai

- Shoe Dog: A Memoir by the Creator of NikeDari EverandShoe Dog: A Memoir by the Creator of NikePenilaian: 4.5 dari 5 bintang4.5/5 (537)

- Channel Estimation Techniques Over MIMO-OFDM SystemDokumen4 halamanChannel Estimation Techniques Over MIMO-OFDM SystemEditor IJRITCCBelum ada peringkat

- The Yellow House: A Memoir (2019 National Book Award Winner)Dari EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Penilaian: 4 dari 5 bintang4/5 (98)

- Importance of Similarity Measures in Effective Web Information RetrievalDokumen5 halamanImportance of Similarity Measures in Effective Web Information RetrievalEditor IJRITCCBelum ada peringkat

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeDari EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifePenilaian: 4 dari 5 bintang4/5 (5794)

- A Review of 2D &3D Image Steganography TechniquesDokumen5 halamanA Review of 2D &3D Image Steganography TechniquesEditor IJRITCCBelum ada peringkat

- Prediction of Crop Yield Using LS-SVMDokumen3 halamanPrediction of Crop Yield Using LS-SVMEditor IJRITCCBelum ada peringkat

- The Little Book of Hygge: Danish Secrets to Happy LivingDari EverandThe Little Book of Hygge: Danish Secrets to Happy LivingPenilaian: 3.5 dari 5 bintang3.5/5 (400)

- A Study of Focused Web Crawling TechniquesDokumen4 halamanA Study of Focused Web Crawling TechniquesEditor IJRITCCBelum ada peringkat

- Grit: The Power of Passion and PerseveranceDari EverandGrit: The Power of Passion and PerseverancePenilaian: 4 dari 5 bintang4/5 (588)

- Diagnosis and Prognosis of Breast Cancer Using Multi Classification AlgorithmDokumen5 halamanDiagnosis and Prognosis of Breast Cancer Using Multi Classification AlgorithmEditor IJRITCCBelum ada peringkat

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureDari EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FuturePenilaian: 4.5 dari 5 bintang4.5/5 (474)

- Predictive Analysis For Diabetes Using Tableau: Dhanamma Jagli Siddhanth KotianDokumen3 halamanPredictive Analysis For Diabetes Using Tableau: Dhanamma Jagli Siddhanth Kotianrahul sharmaBelum ada peringkat

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryDari EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryPenilaian: 3.5 dari 5 bintang3.5/5 (231)

- 44 1530697679 - 04-07-2018 PDFDokumen3 halaman44 1530697679 - 04-07-2018 PDFrahul sharmaBelum ada peringkat

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceDari EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RacePenilaian: 4 dari 5 bintang4/5 (895)

- 45 1530697786 - 04-07-2018 PDFDokumen5 halaman45 1530697786 - 04-07-2018 PDFrahul sharmaBelum ada peringkat

- Team of Rivals: The Political Genius of Abraham LincolnDari EverandTeam of Rivals: The Political Genius of Abraham LincolnPenilaian: 4.5 dari 5 bintang4.5/5 (234)

- Hybrid Algorithm For Enhanced Watermark Security With Robust DetectionDokumen5 halamanHybrid Algorithm For Enhanced Watermark Security With Robust Detectionrahul sharmaBelum ada peringkat

- Never Split the Difference: Negotiating As If Your Life Depended On ItDari EverandNever Split the Difference: Negotiating As If Your Life Depended On ItPenilaian: 4.5 dari 5 bintang4.5/5 (838)

- Safeguarding Data Privacy by Placing Multi-Level Access RestrictionsDokumen3 halamanSafeguarding Data Privacy by Placing Multi-Level Access Restrictionsrahul sharmaBelum ada peringkat

- The Emperor of All Maladies: A Biography of CancerDari EverandThe Emperor of All Maladies: A Biography of CancerPenilaian: 4.5 dari 5 bintang4.5/5 (271)

- Itimer: Count On Your TimeDokumen4 halamanItimer: Count On Your Timerahul sharmaBelum ada peringkat

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaDari EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaPenilaian: 4.5 dari 5 bintang4.5/5 (266)

- 41 1530347319 - 30-06-2018 PDFDokumen9 halaman41 1530347319 - 30-06-2018 PDFrahul sharmaBelum ada peringkat

- On Fire: The (Burning) Case for a Green New DealDari EverandOn Fire: The (Burning) Case for a Green New DealPenilaian: 4 dari 5 bintang4/5 (74)

- 49 1530872658 - 06-07-2018 PDFDokumen6 halaman49 1530872658 - 06-07-2018 PDFrahul sharmaBelum ada peringkat

- Paper On Design and Analysis of Wheel Set Assembly & Disassembly Hydraulic Press MachineDokumen4 halamanPaper On Design and Analysis of Wheel Set Assembly & Disassembly Hydraulic Press MachineEditor IJRITCCBelum ada peringkat

- The Unwinding: An Inner History of the New AmericaDari EverandThe Unwinding: An Inner History of the New AmericaPenilaian: 4 dari 5 bintang4/5 (45)

- BC556B, BC557A, B, C, BC558B Amplifier Transistors: PNP SiliconDokumen9 halamanBC556B, BC557A, B, C, BC558B Amplifier Transistors: PNP SiliconoridecomBelum ada peringkat

- 1-3. Introduction To Matter, Energy, and Direct CurrentDokumen46 halaman1-3. Introduction To Matter, Energy, and Direct CurrentJosephine Pinlac JunioBelum ada peringkat

- Rise of ISIS: A Threat We Can't IgnoreDari EverandRise of ISIS: A Threat We Can't IgnorePenilaian: 3.5 dari 5 bintang3.5/5 (137)

- Converter, Inverter, Brake: Skiip 35Nab126V1Dokumen4 halamanConverter, Inverter, Brake: Skiip 35Nab126V1JesusRiveroBelum ada peringkat

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersDari EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersPenilaian: 4.5 dari 5 bintang4.5/5 (345)

- Chapter 5 Mosfet - 1Dokumen31 halamanChapter 5 Mosfet - 1ahmed khairyBelum ada peringkat

- dm20 SupremaDokumen12 halamandm20 SupremaVenkateshBelum ada peringkat

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyDari EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyPenilaian: 3.5 dari 5 bintang3.5/5 (2259)

- Lattice Fpga Design GuideDokumen210 halamanLattice Fpga Design Guidelaxman_1985Belum ada peringkat

- Lab EpsaDokumen19 halamanLab Epsasemuty92Belum ada peringkat

- ACS 600 Installation ManualDokumen150 halamanACS 600 Installation Manuallalo_37Belum ada peringkat

- A1324 5 6 DatasheetDokumen12 halamanA1324 5 6 DatasheetKrisztian BoneraBelum ada peringkat

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreDari EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You ArePenilaian: 4 dari 5 bintang4/5 (1090)

- General-Purpose Switching Device Applications: Data SheetDokumen4 halamanGeneral-Purpose Switching Device Applications: Data SheetdistefanoBelum ada peringkat

- High Power Synchronous Buck Converter Delivers Up To 50ADokumen2 halamanHigh Power Synchronous Buck Converter Delivers Up To 50ABerat GündoğanBelum ada peringkat

- A Multilayer Ultra-Wideband Directional CouplerDokumen5 halamanA Multilayer Ultra-Wideband Directional Coupleragmnm1962Belum ada peringkat

- Unit-2 EMIDokumen72 halamanUnit-2 EMISujatha UthamarajBelum ada peringkat

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Dari EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Penilaian: 4.5 dari 5 bintang4.5/5 (121)

- McIntosh MC250 Service Manual 23C48+ PDFDokumen9 halamanMcIntosh MC250 Service Manual 23C48+ PDFViorel AldeaBelum ada peringkat

- Zener Diode Introduction To Zener DiodesDokumen6 halamanZener Diode Introduction To Zener DiodesSahil BhagatBelum ada peringkat

- Wayne's Tinkering: Inexpensively Program Your Arduino Via BluetoothDokumen8 halamanWayne's Tinkering: Inexpensively Program Your Arduino Via BluetoothJoey PeliasBelum ada peringkat

- 11 Thyripol Main Project FileDokumen11 halaman11 Thyripol Main Project FileKirankumar Reddy100% (1)

- Welcome To Tle Electronic Product Assembly and Servicing!: Electronics HistoryDokumen2 halamanWelcome To Tle Electronic Product Assembly and Servicing!: Electronics HistoryVerna Lois ArasainBelum ada peringkat

- LECTURE .4: Single-Phase Full-Wave Uncontrolled Rectifiers 4.1-Case of Resistive LoadDokumen6 halamanLECTURE .4: Single-Phase Full-Wave Uncontrolled Rectifiers 4.1-Case of Resistive LoadElectrifying GateBelum ada peringkat

- Project of Dcs 1Dokumen13 halamanProject of Dcs 1Pranil KambleBelum ada peringkat

- Danfoss VLT5000 Data Sheet PDFDokumen62 halamanDanfoss VLT5000 Data Sheet PDFKukuh WidodoBelum ada peringkat

- Ijiip 073059jeDokumen14 halamanIjiip 073059jestrumf381Belum ada peringkat

- An-948 Linear Power AmplifierDokumen10 halamanAn-948 Linear Power AmplifierJimmie Valverde MontalvoBelum ada peringkat

- Her Body and Other Parties: StoriesDari EverandHer Body and Other Parties: StoriesPenilaian: 4 dari 5 bintang4/5 (821)

- RCA CTC185A (3960) EfDokumen17 halamanRCA CTC185A (3960) Efapi-19523062Belum ada peringkat

- Solar Energy SystemDokumen19 halamanSolar Energy Systemanup chauhanBelum ada peringkat

- Pub QuizDokumen4 halamanPub QuizVan YangBelum ada peringkat

- Power Distribution of A Steel PlantDokumen72 halamanPower Distribution of A Steel PlantKashif Hussain Razwi100% (2)

- H Series An ManualDokumen5 halamanH Series An ManualraduldelBelum ada peringkat

- Final REVIEW Voltage FollowerDokumen17 halamanFinal REVIEW Voltage FollowerJay PadaliyaBelum ada peringkat

- SST-2000 SeriesDokumen33 halamanSST-2000 SeriesLeyverMBBelum ada peringkat