Arquitectura Básica de Computadora

Diunggah oleh

EstebanDeskripsi Asli:

Hak Cipta

Format Tersedia

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniHak Cipta:

Format Tersedia

Arquitectura Básica de Computadora

Diunggah oleh

EstebanHak Cipta:

Format Tersedia

ENTORNO DE TRABAJO PARA LA SIMULACIN HARDWARE

DE UNA COMPUTADORA SENCILLA

Fco. Javier Quiles, Manuel A. Ortiz, Carlos D. Moreno, J. Ignacio Benavides,

Vicente J. Fernndez, Nicols Martnez

rea de Conocimiento de Arquitectura y Tecnologa de Computadores

Escuela Politcnica Superior. Universidad de Crdoba

el1qulaf@uco.es

1. RESUMEN

En esta comunicacin se describe un Entorno de Trabajo, desarrollado como

Proyecto Fin de Carrera, que permite mostrar al alumno el funcionamiento de

una computadora sencilla desde el punto de vista hardware, es decir a nivel de

cronograma usando un simulador VHDL. Se define una estructura concreta,

respecto al tipo de componentes desde el punto de vista lgico (registros, alu,

memoria y unidad de control microprogramada) y buses e interconexiones

internas, y un conjunto de instrucciones por defecto. A partir de sta, el alumno

puede configurar algunos aspectos de la Arquitectura, como son el tamao de

la palabra, el nmero de palabras de la memoria (Pila, datos y programa) e

incluso definir sus propias instrucciones. El entorno ofrece todas las utilidades

necesarias para editar el fichero fuente en lenguaje ensamblador, ensamblarlo,

crear el modelo de simulacin VHDL de la computadora con el contenido

adecuado de las ROM de programa y microprograma, y finalmente realizar su

simulacin a nivel de cronograma.

2. INTRODUCCIN

En la asignatura de Arquitectura de Computadores es habitual la utilizacin de

simuladores de computadoras sencillas, cuya finalidad es mostrar al alumno el

funcionamiento interno de un computador de la forma ms fcil posible. Estos

simuladores permiten por un lado, el desarrollo de programas utilizando un

conjunto de instrucciones reducidas, y por el otro, la creacin de nuevas

instrucciones. Normalmente se define la estructura de estos computadores

definiendo los registros y las operaciones que se pueden realizar sobre llos.

Se define un controlador cableado o microprogramado y una memoria o un

sistema de memoria donde se almacenan las instrucciones y los datos.

Es habitual que estos simuladores vayan mostrando en cada ciclo la operacin

que realizan las microinstrucciones sobre los registros visualizando su

contenido. Sin embargo esta simulacin est muy lejos de la realidad del

hardware ya que no suelen mostrar las seales que generan las operaciones

sobre los registros y mucho menos el cronograma de dichas seales.

Hemos desarrollado un entorno de trabajo que pretende mostrar al alumno el

funcionamiento de una computadora sencilla desde el punto de vista hardware.

Partiendo de una estructura fija respecto a los componentes, el alumno puede

configurar el tamao de la palabra y el nmero de palabras de la memoria,

crear sus propias instrucciones, editar el fichero fuente en lenguaje

ensamblador, ensamblarlo, crear el modelo de simulacin VHDL de la

computadora con el contenido adecuado de las ROM de programa y

microprograma, y finalmente realizar su simulacin a nivel de cronograma.

A lo largo de la comunicacin se describir el entorno de trabajo, la arquitectura

de la computadora y su aplicacin a la docencia mediante un ejemplo.

3. DESCRIPCIN DE LA ARQUITECTURA DE LA COMPUTADORA

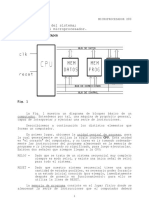

La Organizacin de la Computadora Sencilla [1] est basada en la que se

explica en las clases de teora [2]. Como se puede observar en la figura 1 se

trata de una Computadora de Arquitectura Von Neumann con memoria Pila y

Unidad de Control Microprogramada. Adems de la Unidad Aritmtico-lgica y

los registros bsicos (MAR, OPR y PC), consta de un Registro de Propsito

General (GPR), que comunica la memoria con el resto de componentes, y un

Puntero de Pila para implementar las instrucciones que trabajan con este tipo

de memoria.

Figura 1. Organizacin de la Computadora

A continuacin se analiza cada uno de los componentes. En todas las figuras

se han nombrado los terminales de orden con la microoperacin que habilitan,

de forma que se pueda deducir directamente las microperaciones que realiza

cada componente de la computadora.

3.1. Unidad Aritmtico-Lgica

Su estructura se muestra en la figura 2. Es del tipo basada en Acumulador.

Consta de un sumador, un registro Acumulador y un registro F de un solo bit.

Las microoperaciones que realiza la ALU son:

Terminal de orden

ROLF_ACC

RORF_ACC

NACC_ACC

ACC+1_ACC

0_ACC

GPR+ACC_ACC

0_F

NF_F

Microoperacin

Rotacin a la izquierda del acumulador a travs del flag F

Rotacin a la derecha del acumulador a travs del flag F

Complemento a 1 del contenido del acumulador

Incremento del contenido del acumulador

Puesta a cero del acumulador

Suma los contenidos del GPR y el acumulador y almacena el

resultado en el acumulador. El flag F almacena el acarreo

Puesta a cero del flag F

Complementa el valor del flag F

3.2. Memoria

Consta

de

una

memoria RAM, que

almacena los datos, y

otra tipo ROM, que

contiene el programa

que debe ejecutar la

computadora. La ROM

est mapeada en la

parte baja del espacio

de direccionamiento y

la RAM en la parte

superior. El nmero de

palabras de ambos

tipos es configurable

por el usuario.

Dado que se emplean

Figura 2. Estructura de la ALU

dos tipos de memoria

diferentes

que

comparten el mismo bus de datos, se ha incluido un bloque de decodificacin,

que determina la memoria a la que se accede.

En la operacin de escritura (GPR_M) se almacena el dato que contiene el

GPR en la palabra de memoria indicada por el MAR, y en la de lectura

(M_GPR) se transfiere al GPR el contenido de la palabra indicada por el MAR.

3.3. Registro GPR

Su funcin principal es la de transferir informacin con la memoria en las

operaciones de lectura o escritura, que se realicen en sta. Por tanto, al final de

los ciclos de bsqueda almacena una instruccin y durante los de ejecucin

almacenar un dato o una direccin indirecta segn el tipo de instruccin.

Segn esto, cuando almacena una instruccin se distinguen dos campos que

evidentemente vienen definidos por el formato de instruccin. stos son el de

cdigo de operacin y el de direccin. El campo de cdigo de operacin

siempre tiene un tamao fijo de 6 bits y se almacena en los 6 bits de mayor

peso. El campo de direccin tiene un tamao variable y se almacena en los bits

restantes de menor peso.

n-1 .......................... n-6 n-7 ..................................... 0

Cdigo de operacin

Direccin

Por otra parte se le puede transferir el contenido del PC (PC_GPR) o del

Acumulador (ACC_GPR). Respecto a las microoperaciones de procesamiento

solamente puede incrementar su contenido (GPR+1_GPR). Genera una seal

de estado Z a la Unidad de Control, que se pone a 1 cuando su contenido es

cero.

3.4. Registro PC

Almacena la direccin de la instruccin que se va a leer en el ciclo de

bsqueda. Por ello, las microoperaciones que debe realizar son las de

incremento (PC+1_PC) y la de transferencia del contenido del campo de

direccin del GPR (GPR_PC).

3.5. Registro OPR

Contiene el cdigo de

operacin de la instruccin

que se va a ejecutar. Por

tanto,

la

nica

microoperacin

que

realiza es la de almacenar

el contenido del campo del

cdigo de operacin del

GPR (GPR_OPR).

3.6. Pila

La computadora se puede

configurar

para

implementar en una zona

de la RAM una memoria

Pila. Esta es del tipo

expand-down. Por tanto,

se necesita un Puntero de

Pila

que

realiza

la

microoperacin

de

Figura 3. Estructura del Controlador

incremento (SP+1_SP) en

la operacin de Push y la de decremento (SP-1_SP) en la de Pop.

3.7. Registro MAR

Selecciona la posicin de memoria que se accede en los ciclos de bsqueda y

de ejecucin. Por tanto, las microoperaciones que realiza estn determinadas

por las posibles fuentes de la direccin: carga el contenido del campo de

direccin del GPR (GPR_MAR), carga el contenido del PC (PC_MAR) y carga

el contenido del Puntero de Pila (SP_MAR).

3.8. Unidad de Control

Es del tipo microprogramada [3]. En la figura 3 se muestra su estructura. A

partir del cdigo de operacin (OPR) la unidad lgica1 genera la direccin de

inicio donde comienza la secuencia de micropalabras correspondientes a la

ejecucin de cada instruccin. Esta se carga en el registro de direccin de

memoria (CMAR). La CROM contiene todas las micropalabras correspondiente

a los ciclos de bsqueda y ejecucin de cada una de las instrucciones. Tiene

una organizacin de 256 x 32. El formato de la micropalabra es el siguiente.

31............................................11

Seales de orden

10

B

9

I

8

R

Control Lgica2

7......................................0

Direccin de salto

La Unidad Lgica2 a partir de los bits B, I y R de las micropalabras y el

contenido de los flags Z y F controla las entradas B, I y R del CMAR para

determinar si incrementa su contenido (I), o salta a la direccin indicada por la

micropalabra (B) o la de comienzo de la rutina de ejecucin de la instruccin

(R).

4. DESCRIPCIN DEL ENTORNO DE TRABAJO

El objetivo principal por el que se desarroll esta herramienta fue el de disponer

de un entorno de trabajo que realizase de forma automtica la simulacin

hardware mediante un simulador VHDL del funcionamiento de una

Computadora sencilla, de forma que el alumno pudiese ver a nivel de

cronograma la secuencia de microoperaciones y la evolucin de los contenidos

de los registros, durante la ejecucin de un programa definido por l mismo.

Por ello se ha diseado con las siguientes caractersticas:

- Definicin de un conjunto bsico de instrucciones

- Editor del fichero fuente en lenguaje ensamblador

- Microemsamblador que permite la creacin de instrucciones nuevas y

determinar el contenido de la CROM

- Ensamblado automtico del fichero fuente que determina el contenido de

la ROM

- Generacin automtica de los ficheros VHDL [4][5][6] que describe el

funcionamiento de la Computadora incluyendo los contenidos de la

CROM y la ROM

- Ejecucin automtica de la herramienta Simulate de OrCAD 7.20 [7].

Ello implica que se cree previamente todos los ficheros necesarios,

como son el de proyecto de OrCAD y el de estmulos.

El entorno de trabajo tiene dos partes diferenciadas. La primera de ellas,

desarrollada en Visual Basic, permite introducir el programa utilizando las

instrucciones predefinidas o creando nuevas instrucciones definidas por el

propio usuario. Una vez editado el fichero fuente se realiza la compilacin y si

no se han producido errores se generan los ficheros VHDL y se ejecuta Orcad.

La segunda parte del entorno es el entorno de Orcad Simulate que realiza la

visualizacin del resultado de la simulacin.

4.1. Ejemplo de Simulacin con el Entorno de Trabajo

Para mostrar el funcionamiento y la utilidad del entorno de trabajo se va a

realizar la simulacin de un programa que calcule la parte entera de la raz

cuadrada de un nmero entero.

El proceso de simulacin consta de varios pasos, que corresponde a los cuatro

primeros comandos de la barra de men:

1.

Crear proyecto

2.

Especificar el conjunto de instrucciones de la Computadora

3.

Editar el fichero fuente

4.

Simular el funcionamiento mediante la utilidad Simulate de OrCAD

7.20

4.1.1. Crear proyecto

Se empieza creando un proyecto seleccionando Nuevo del men Archivo. Se

abre una ventana en la que se configura la Computadora, indicando la anchura

de la palabra y el nmero de palabras de la ROM, RAM y PILA. En nuestro

ejemplo se selecciona 16 bits de anchura de palabra, 512 palabras para la

ROM y la RAM y cero palabras para la PILA. Una vez validado los datos de

configuracin se vuelve a la ventana principal del entorno de trabajo, en la que

como se puede ver en la figura 4, se indica la arquitectura final de la

Computadora. Los mens se van habilitando conforme se avanza en el flujo de

trabajo indicado anteriormente. As, se puede comprobar como estn

habilitados los mens Archivo y Diseo, que correspondera al siguiente paso.

Figura 4. Ventana inicial del Entorno de Trabajo

4.1.2. Especificar el conjunto de instrucciones de la Computadora

En este paso se indica las instrucciones de la Computadora. El nmero mximo

de instrucciones es de 64. stas se pueden seleccionar entre la instrucciones

por defecto y los creadas por el propio usuario. La creacin del conjunto de

instrucciones se realiza mediante el comando Diseo. Antes de indicar el

proceso, se analizar el algoritmo para comprender las instrucciones que se

seleccionan y las que debe crear el alumno.

El algoritmo consiste en restar sucesivamente al nmero inicial los nmeros

impares empezando desde uno hasta obtener un resultado negativo. El nmero

de veces que se ha realizado la resta menos uno ser el resultado buscado. Se

necesitan tres variables que se almacenarn en la memoria RAM:

- Nmero. Almacena el dato inicial. Su direccin es la 512.

- Nmero_impar. Contiene los nmeros impares que se deben restar. Se

inicializa con el valor 1. Su direccin es la 513.

- Resultado. Se inicializa con el valor 0. Su direccin es la 514.

Se empieza cargando Nmero en el acumulador y se le resta Nmero_impar. A

continuacin se analiza el bit de signo. Si es positivo se incrementa Resultado y

se le suma dos a Nmero_impar, y se repite el proceso de resta y

comprobacin. Si es negativo se termina el proceso.

Figura 5. Definicin del conjunto de instrucciones

Para simplificar el programa se crearn dos instrucciones, SUB direccin, que

resta el contenido de la posicin de memoria indicada por el campo de

direccin al acumulador y almacena el resultado en ste, y INCM direccin,

que incrementa el contenido de la posicin de memoria indicada por el campo

de direccin.

La figura 5 muestra la ventana de especificacin del conjunto de instrucciones.

El men Instrucciones Predefinidas permite seleccionar las instrucciones del

conjunto declarado por defecto. Para crear las instrucciones anteriores se

selecciona Instrucciones Nuevas. Como se muestra en la figura hay que indicar

la secuencia de microoperaciones del ciclo de ejecucin. El conjunto de

instrucciones final de la Computadora estar compuesto por las indicadas en

las dos listas de la izquierda.

4.1.3. Edicin del fichero fuente

Para editar el fichero fuente se

selecciona el comando Cdigo. ste

ejecuta automticamente el Bloc de

Notas de Windows. En la figura 6 se

muestra el contenido del fichero fuente

en lenguaje ensamblador de la

Computadora.

Se empieza cargando el nmero

original almacenado en la posicin

512 en el acumulador. Esto se realiza

mediante

las

dos

primeras

instrucciones. Posteriormente se entra

en un bucle indicado por la etiqueta

del mismo nombre, que resta

sucesivamente los nmeros impares

almacenados en la posicin 513

empezando desde el valor 1. Despus

de la resta se comprueba el valor del

Figura 6. Fichero fuente

bit de signo del acumulador mediante

la instruccin SFZ.

sta salta la siguiente

instruccin (Halt) si el

flag F est a cero.

Para transferir el bit de

signo a F se ejecuta la

instruccin de rotacin

a la izquierda del

acumulador a travs

del

acumulador

(ROLF). Si F es 1

(nmero negativo) se

ejecuta la instruccin

HALT, que detiene la

ejecucin

de

la

mquina. Si F es 0

(nmero

positivo)

indica que no ha

terminado el proceso.

Figura 7. Edicin y compilacin del fichero fuente

Por

tanto

se

incrementa la posicin

514, que contiene el resultado, y se incrementa dos veces la posicin 513 para

actualizarla con el valor del siguiente nmero impar, y finalmente se salta al

inicio del bucle (JMP BUCLE:).

Despus de salvar el fichero fuente y cerrar el editor se abre la ventana de la

figura 7. Para ensamblar el fichero fuente se hace clic en el botn Aceptar. Si

no hay errores se vuelca el contenido de la memoria RAM en la lista de la

derecha. Se puede observar que el contenido de las posiciones de memoria

512, 513 y 514 coincide con el indicado en las directivas del fichero fuente.

Haciendo clic en el botn Siguiente se cierra la ventana y se crea el modelo en

VHDL de la Computadora. sta se describe como un diseo jerrquico, por lo

que constar de varios ficheros VHDL, un raz y uno para cada componente de

los indicados en la figura que describe la organizacin de la Computadora.

Evidentemente la ROM contiene el programa en lenguaje mquina obtenido al

ensamblar el fichero fuente, y la CROM las rutinas correspondientes a la

ejecucin del ciclo de bsqueda y de cada una de las instrucciones del

conjunto creado en el paso anterior.

4.1.4. Simulacin

Para realizar la simulacin del funcionamiento se hace clic en el men

Simulacin. El entorno de trabajo automticamente crea el fichero de proyecto,

que define los ficheros VHDL del diseo, y el de estmulos compatibles con

OrCAD Express 7.20, y ejecuta la utilidad Capture.

Figura 8. Cronograma de la simulacin de la raz cuadrada de 9

Seleccionando Simulate del men Tools se ejecuta el simulador de modelos

VHDL de OrCAD Express. En la figura 8 se muestra la parte final de la

simulacin. La seal instruccin indica la instruccin que ejecuta la

Computadora.

En el ejemplo se realiza la raz cuadrada de 9. Se puede observar la ejecucin

de la parte final del bucle, que incluye la resta, comprobacin del bit de signo

del acumulador y detencin de la ejecucin. En la parte izquierda del

cronograma se puede ver como al ejecutar la instruccin INCM 514 (MAR =

20216), el registro GPR contiene el valor 3, que es el resultado correcto.

5. CONCLUSIONES

La utilizacin de este entorno es vlido para las asignaturas de Estructura de

Computadores y Arquitectura de Computadores donde habitualmente se utiliza

una Computadora Sencilla para la realizacin de problemas y prcticas. A

pesar de que el entorno genera ficheros VHDL a partir de los que se obtiene la

simulacin, no es necesario que el alumno tenga conocimientos de VHDL ya

que estos se generan de forma transparente, por lo que el alumno solamente

necesita conocer la arquitectura de la computadora y OrCAD Simulate. stas

son las herramientas que utilizamos habitualmente en prcticas de simulacin

de las asignaturas de Tecnologa de Computadores y Sistemas Digitales, que

se cursan con anterioridad.

Este entorno es el complemento idneo, a otros simuladores software que se

han desarrollado tambin para esta computadora. Por tanto, el alumno puede

utilizar un simulador u otro o ambos dependiendo de cual sea el inters:

comprobar un programa y/o estudiar adems su comportamiento hardware.

Uno de los objetivos con los que se desarroll el entorno de trabajo fue el de

minimizar el nmero de pasos y facilitar el proceso de simulacin. Como se ha

demostrado mediante el ejemplo del apartado 4, stos se han cumplido ya que

solamente hay que realizar 4 pasos, y a su vez se gua al alumno durante todo

el proceso, ya que los comandos se van habilitando conforme se termina cada

fase.

6. REFERENCIAS

[1] V. J. Fernndez, N. Martnez, Entorno para la implementacin de una

computadora microprogramada bsica configurable y generacin de su

modelo de simulacin en VHDL, Proyecto Fin de Carrera, Junio de 2003.

[2] H. Taub, Circuitos digitales y microprocesadores, Ed. McGraw Hill, 1991.

[3] M. Morris Mano, Arquitectura de computadoras,3 Ed. , Prentice Hall,

1994.

[4] P. Ashenden, The Designer`s Guide to VHDL, Ed. Morgan Kaufmann, San

Francisco, 1995.

[5] IEEE Society, IEEE Standard VHDL Language Reference Manual: IEEE

Std. 1076-1987, New York, NY, 1988.

[6] IEEE Society, IEEE Standard VHDL Language Reference Manual: IEEE

Std. 1076-1993, New York, NY, 1994.

[7] E. Sez, F.J. Quiles, OrCAD Express V.7.20: Gua Rpida para la

Iniciacin al Diseo y Simulacin de Sistemas Digitales, Universidad de

Crdoba, 1999.

Anda mungkin juga menyukai

- Programación de microcontroladores paso a paso: Ejemplos prácticos desarrollados en la nubeDari EverandProgramación de microcontroladores paso a paso: Ejemplos prácticos desarrollados en la nubeBelum ada peringkat

- Arqcom - Jose Ignacio Nota - TP2 - 1K4Dokumen6 halamanArqcom - Jose Ignacio Nota - TP2 - 1K4Nacho NotaBelum ada peringkat

- UF0852 - Instalación y actualización de sistemas operativosDari EverandUF0852 - Instalación y actualización de sistemas operativosPenilaian: 5 dari 5 bintang5/5 (1)

- Apuntes de La Materia de Microcontroladores 1Dokumen10 halamanApuntes de La Materia de Microcontroladores 1Damian RocoBelum ada peringkat

- Computadores para bases de datos. IFCT0310Dari EverandComputadores para bases de datos. IFCT0310Belum ada peringkat

- MicrocontroladoresDokumen24 halamanMicrocontroladoresGeizel ToledoBelum ada peringkat

- Tutorial Xc8 IntroduccionDokumen7 halamanTutorial Xc8 IntroduccioneeindustrialBelum ada peringkat

- Ensayo Unidad 1 Arquitectura CISC y RISCDokumen15 halamanEnsayo Unidad 1 Arquitectura CISC y RISCing_jonny23Belum ada peringkat

- Mapa Conceptual Programación MicrocontroladoresDokumen6 halamanMapa Conceptual Programación MicrocontroladoresSAMANTHA LOPEZ MONTALVOBelum ada peringkat

- Unidad 2Dokumen24 halamanUnidad 2Rogelio Anguiano SantosBelum ada peringkat

- El MicroprocesadorDokumen11 halamanEl MicroprocesadorConsuelo MarinBelum ada peringkat

- Un Microprocesador de 8 Bits Z80 PDFDokumen85 halamanUn Microprocesador de 8 Bits Z80 PDFVictor Hugo Hernandez100% (1)

- 4 1-GastonDokumen11 halaman4 1-GastonLópez SantiagoBelum ada peringkat

- Unidad 4Dokumen22 halamanUnidad 4Ricardo HernandezBelum ada peringkat

- Cerradura Electronica Codificad1Dokumen8 halamanCerradura Electronica Codificad1Jhon JairoBelum ada peringkat

- Libro Sistemas Operativos Una Visión Aplicada 2 EdiciónDokumen233 halamanLibro Sistemas Operativos Una Visión Aplicada 2 EdiciónGerardo Ruiz Lopez100% (2)

- Arquitectura Del ComputadorDokumen10 halamanArquitectura Del ComputadorDavid PinoBelum ada peringkat

- Desarrollo Prueba 2018Dokumen7 halamanDesarrollo Prueba 2018Mauricio VegaBelum ada peringkat

- CPU, Registros e InstruccionesDokumen7 halamanCPU, Registros e Instruccionesjorge103Belum ada peringkat

- Diferencia Entre Microcontroladores y MicroprocesadorDokumen11 halamanDiferencia Entre Microcontroladores y MicroprocesadorCrisBelum ada peringkat

- Avance Informe Lab1 - Version 3 FinalDokumen6 halamanAvance Informe Lab1 - Version 3 FinalSergio Torres OrtizBelum ada peringkat

- Arquitectura de PCDokumen20 halamanArquitectura de PCHector Marcelo ArayaBelum ada peringkat

- Investigación U2. ADC - Alonso Mata AdanDokumen20 halamanInvestigación U2. ADC - Alonso Mata AdanADAN ALONSO MATABelum ada peringkat

- Tema 3: Componentes, Estructura y Funcionamiento de La CPUDokumen10 halamanTema 3: Componentes, Estructura y Funcionamiento de La CPUfelipeBelum ada peringkat

- Practica 01 MicrosDokumen14 halamanPractica 01 MicrosAlejandro Rodriguez100% (1)

- Asignacion Clase 1 y 2Dokumen5 halamanAsignacion Clase 1 y 2danielBelum ada peringkat

- Secuenciador de MicroprogramaDokumen15 halamanSecuenciador de MicroprogramaAngel Rodriguez RodriguezBelum ada peringkat

- EL3313 Reporte 1Dokumen4 halamanEL3313 Reporte 1Jeremy Cordoba WrightBelum ada peringkat

- 2.1 - Estructura Del Microcontrolador ATmega328PDokumen12 halaman2.1 - Estructura Del Microcontrolador ATmega328PArantxa NorzagarayBelum ada peringkat

- Laboratorio 4Dokumen7 halamanLaboratorio 4Siegnagel DormidoBelum ada peringkat

- Departamento de Ingeniería Eléctrica Y ElectrónicaDokumen37 halamanDepartamento de Ingeniería Eléctrica Y ElectrónicaRamon TorresBelum ada peringkat

- Diseño de Una Computadora Implementada en VHDLDokumen6 halamanDiseño de Una Computadora Implementada en VHDLerick Martin Rivera GarzaBelum ada peringkat

- Proyecto Final VHDLDokumen14 halamanProyecto Final VHDLFortino50% (2)

- Unidad IDokumen10 halamanUnidad IJose Manuel Godoy EscribarBelum ada peringkat

- Tarea 5Dokumen3 halamanTarea 5luisBelum ada peringkat

- Glosario de Terminos Sistemas EmbebidosDokumen7 halamanGlosario de Terminos Sistemas EmbebidoscharryperdomoBelum ada peringkat

- T3-Estructura de Un Computador PDFDokumen42 halamanT3-Estructura de Un Computador PDFManuelGalindoBelum ada peringkat

- Organización Del ProcesadorDokumen12 halamanOrganización Del ProcesadorGeovanny Quiroz MoncerradBelum ada peringkat

- TP 4Dokumen7 halamanTP 4Nacho NotaBelum ada peringkat

- UD1. Funcionamiento de Un Ordenador: Sistemas InformáticosDokumen26 halamanUD1. Funcionamiento de Un Ordenador: Sistemas InformáticosJavi PerezBelum ada peringkat

- Unidad I Y II Arquitectura Del Computador David PinoDokumen8 halamanUnidad I Y II Arquitectura Del Computador David PinoDavid PinoBelum ada peringkat

- Tema 03Dokumen5 halamanTema 03Javier Gutiérrez JiménezBelum ada peringkat

- Introduccion A Los MicroprocesadoresDokumen9 halamanIntroduccion A Los MicroprocesadoresEric Yair VenturaBelum ada peringkat

- U1, El Microprocesador (CPU)Dokumen14 halamanU1, El Microprocesador (CPU)Raúl Monforte ChulinBelum ada peringkat

- Micro Proce Sad orDokumen20 halamanMicro Proce Sad orGuada LeivaBelum ada peringkat

- Arquitectura Von Neumann y HarvardDokumen26 halamanArquitectura Von Neumann y HarvardUlivari Alexander GomezBelum ada peringkat

- Qué Es Un MicroprocesadorDokumen4 halamanQué Es Un Microprocesadorfabian PazoBelum ada peringkat

- Resumen-Sistemas de ComputacionDokumen6 halamanResumen-Sistemas de ComputacionDilan Jauregui SanchezBelum ada peringkat

- 2 Arquitectura Interna MicrocontroladorDokumen4 halaman2 Arquitectura Interna MicrocontroladorMauricio SanchezBelum ada peringkat

- Apuntes de Técnicas Digitales III - Capítulo 1Dokumen37 halamanApuntes de Técnicas Digitales III - Capítulo 1Tecnicasdigitales3 UtnBelum ada peringkat

- Un Microprocesador de 8 Bits Z80Dokumen85 halamanUn Microprocesador de 8 Bits Z80Sebastián SandovalBelum ada peringkat

- Que Son Los MicrocontroladoresDokumen5 halamanQue Son Los MicrocontroladoresPriscilla LewisBelum ada peringkat

- Unidad Central de ProcesamientoDokumen18 halamanUnidad Central de ProcesamientoJaime Hernnadez LopezBelum ada peringkat

- PIC16F877Dokumen140 halamanPIC16F877jaime2828Belum ada peringkat

- Taller Evaluativo Arquitectura Del PCDokumen6 halamanTaller Evaluativo Arquitectura Del PCDaniel MoralesBelum ada peringkat

- Arquitectura Von NeumannDokumen8 halamanArquitectura Von NeumannDaniel Medrano IzquierdoBelum ada peringkat

- 3-Arquitectura de Microcontroladores 2023Dokumen38 halaman3-Arquitectura de Microcontroladores 2023Ulises martin PellizaBelum ada peringkat

- Comparación Entre Microcontroladores y MicroprocesadoresDokumen7 halamanComparación Entre Microcontroladores y MicroprocesadorespabloBelum ada peringkat

- Modulo 7Dokumen40 halamanModulo 7gimenez adrianaBelum ada peringkat

- Presentacion No. 2Dokumen28 halamanPresentacion No. 2Einie VegaBelum ada peringkat

- Ut05 AddDokumen3 halamanUt05 AddDavid YpuntoBelum ada peringkat

- Presentación ITE-CAP11 - ResumidaDokumen26 halamanPresentación ITE-CAP11 - ResumidaYasunari RamirezBelum ada peringkat

- Examen de Salida SolucionesDokumen3 halamanExamen de Salida SolucionesArmandoVillavicencioCalcinaBelum ada peringkat

- Macumag1 Socorro 2Dokumen3 halamanMacumag1 Socorro 2kaurVRBelum ada peringkat

- Manual de Instalacion GT1Dokumen69 halamanManual de Instalacion GT1aitor100% (1)

- Practica Calificada de Iti 27-04-2023Dokumen2 halamanPractica Calificada de Iti 27-04-2023Dieter Sebastian Huiñapi DavilaBelum ada peringkat

- Sistema OperativoDokumen8 halamanSistema OperativoyeimiBelum ada peringkat

- 7.3.7 - Lab - Visualización de La Tabla de Direcciones MAC Del SwitchDokumen17 halaman7.3.7 - Lab - Visualización de La Tabla de Direcciones MAC Del SwitchCristian Rios PerezBelum ada peringkat

- Generación CeroDokumen2 halamanGeneración CeroAldo MorenoBelum ada peringkat

- Brochure Empresa BITIO SRL PDFDokumen4 halamanBrochure Empresa BITIO SRL PDFteachercarcaustoBelum ada peringkat

- IntroduccionDokumen27 halamanIntroduccionCristofer SaabBelum ada peringkat

- 840 Manual de ServicioDokumen0 halaman840 Manual de ServicioJavier Martinez Zamora100% (2)

- Investigasion ACS580 MODBUSPOLLDokumen10 halamanInvestigasion ACS580 MODBUSPOLLLuis alarcon cueylarBelum ada peringkat

- Fundamentos de ProgramaciónDokumen94 halamanFundamentos de ProgramaciónHernán Víctor Sosa DelgadoBelum ada peringkat

- Visión ArtificialDokumen10 halamanVisión ArtificialIsaiah22Belum ada peringkat

- Definicion y Ejemplos de Los Tipos de MantenimientosDokumen14 halamanDefinicion y Ejemplos de Los Tipos de MantenimientosLina Mina RodallegaBelum ada peringkat

- Desensamble y Ensamble de LaptopsDokumen59 halamanDesensamble y Ensamble de LaptopsAlonso quijano100% (2)

- Apunte AssemblerDokumen59 halamanApunte AssemblerlucasgiaquintaBelum ada peringkat

- Posicionamiento de Visión ArtificialDokumen11 halamanPosicionamiento de Visión ArtificialJordan FloresBelum ada peringkat

- Contraseña - Reporte de PracticaDokumen16 halamanContraseña - Reporte de PracticaJulie EsthefaniBelum ada peringkat

- Estudio Tecnólogico y de Mercado Acerca de Los Sistemas de Banca Electrónica en GuatemalaDokumen188 halamanEstudio Tecnólogico y de Mercado Acerca de Los Sistemas de Banca Electrónica en GuatemaladrkcatBelum ada peringkat

- Arquitectura WindowsDokumen9 halamanArquitectura WindowsxochinoxoBelum ada peringkat

- QUE ES MERCADO InformáticoDokumen3 halamanQUE ES MERCADO InformáticobatallacerotresBelum ada peringkat

- Test de Repaso y Comprueba Tú Aprendizaje Tema 4 de MyMEDokumen5 halamanTest de Repaso y Comprueba Tú Aprendizaje Tema 4 de MyMESamuel Benítez FajardoBelum ada peringkat

- Pruebin Bi0sDokumen2 halamanPruebin Bi0sCode-ModderBelum ada peringkat

- Qué Son Los Dispositivos de Entrada y SalidaDokumen2 halamanQué Son Los Dispositivos de Entrada y Salidaesrella lunaBelum ada peringkat

- Manual EnsamblajeDokumen40 halamanManual EnsamblajeShirley Viviana100% (3)

- Almacenamiento Redundante yDokumen11 halamanAlmacenamiento Redundante yAmauta WankaBelum ada peringkat

- Entendimiento de Una RedDokumen20 halamanEntendimiento de Una RedAngeles OrtegaBelum ada peringkat

- Caracteristicas de Los IntegradosDokumen2 halamanCaracteristicas de Los IntegradosDaniel NavedaBelum ada peringkat