Características Principales Del USRP N210

Diunggah oleh

Bryan GordilloHak Cipta

Format Tersedia

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniHak Cipta:

Format Tersedia

Características Principales Del USRP N210

Diunggah oleh

Bryan GordilloHak Cipta:

Format Tersedia

Caractersticas principales del USRP N210

Puede usarse con GNU radio, LabView y Simulink, posee una estructura

hardware modular especificada en la figura 1, como se puede observar el

equipo cuenta con dos ADCs y dos DACs de alta velocidad, dos

Amplificadores de potencia programables PGA uno para la recepcin y el

otro en la trasmisin, tambin cuenta con FPGA (Fiel programable gate

array) perteneciente a la familia Xilinx Spartan 3A-DSP 3400 FPGA, posee un

interfaz Gigabit Ethernet y capacidad MIMO[1]. Adems cuenta con un

dispositivo GPSDO (Global Positioning System Disciplined Oscillator) que

permite una sincronizacin ms precisa de muestras en el USRP, mientras

que UHD (USRP Hardware Driver) se trata del controlador que debe ser

instalado para poder trabajar con USRP elaborado por Ettus Research [1].

Figura. 1. Diseo hardware del USRP N210 [2]

Este dispositivo en el panel frontal cuenta con[1]:

interfaz Gigabit Ethernet que sirve de interfaz entre el equipo y el

usuario

expansin MIMO en caso de ser necesario conectar varios USRP

Puertos RF1 y RF2 con conectores SMA que sirven para la colocacin

de antenas tanto para trasmitir como para recibir respectivamente

Puerto REF Clok, destinado para la colocacin de un reloj de

referencia

Puerto PPT in , sirve para la colocacin de un multivibrador con

finalidades de sincronizacin

La entrada de voltaje DC

6 leds de color verde enumerados que indican estados del dispositivo:

- Led A: el equipo esta trasmitiendo

- Led B: conexin del equipo mimo

- Led C: el equipo esta recibiendo

- Led D: Firmware ah sido cargado

- Led E: reloj de referencia

- Led F: CPLD (Complex Programmable Logic Device) est activo.

Figura 2. Diseo fsico del USRP N210 [1]

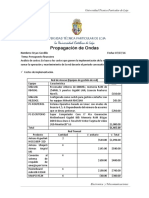

Especificaciones tcnicas

Tabla 1. Especificaciones Tcnicas de USRP N210 [2]

Especificacin Tipo Unidad

Energa

Entrada DC 6 V

Consumo de energa 1.3 A

w/ WBX placa 2.6 A

Rendimiento de la conversin y Relojes

frecuencia de 100 MSPS

muestrea ADC

Resolucin ADC 14 bits

ADC de banda ancha 88 dBc

SFDR

frecuencia de 400 MSPS

muestrea DAC

Resolucin DAC 16 bits

DAC de banda ancha 80 dBc

SFDR

Velocidad de muestreo 50/25 MSPS

hasta / desde el Host

(8b / 16b)

Precisin de frecuencia 2.5 ppm

w/ GPSDO referencia 0.01 ppm

Rendimiento RF (w / WBX)

SSB/LO superposicin 35/50 dBc

Fase de ruido (1.8 Ghz)

10 kHz -80 dBc/hz

100 kHz -100 dBc/hz

1 MHz -137 dBc/hz

Potencia se salida 15 dBm

IIP3 0 dBm

Receptor de la figura 5 dB

de ruido

Fsico

Temperatura de 0 a 55 C

operacin

Dimensiones (I x W x 22 x 16 x 5 cm

H)

Peso 1.2 kg

Describa brevemente cmo funcionan un sistema de radio definida

mediante software.

Los SDR se definen como un radio multibanda capaz de soportar mltiples

interfaces y protocolos, utilizando una mezcla apropiada de circuitos

especializados (ASICs, Application Specific Integrated Circuit), arreglos de

compuertas programadas en campo (FPGAs, Field Programmable Gate

Arrays), Procesadores Digitales de Seales (DSPs, Digital Signal Processors)

y microprocesadores de propsito general (GPPs, del ingls General Purpose

Processors.[3]

Los sistemas basados en software consisten bsicamente en subsistemas

digitales y analgico, las funciones analgicas son concretas aquellas

inmejorables digitalmente como lo son: antena, filtrado RF, combinacin RF,

preamplificacin en recepcin, transmisin de potencia de amplificacin y

generacin de frecuencia de referencia. A continuacin, se enumeran las

partes que conforman un sistema de radio basado en software:[1]

Figura 2. Arquitectura SDR

A continuacin se describen cada una de los componentes bsicos usados

por los sistemas de radio definido por software[1]:

Antenas: encargadas de trasmitir la informacin mediante ondas

electromagnticas

RF front END: en recepcin es el encargado de adecuar los niveles de

seal de entrada para que sea el adecuado en las siguientes etapas,

mientras que para la trasmisin se encarga de amplificar la seal

entregada por las etapas anteriores hasta el nivel de potencia

suficiente para su transmisin por e medio fsico.

Oscilador local: generacin de frecuencias para la conversin de

frecuencia RF en la frecuencia intermedia FI, utilizando una mezcla no

lineal, adems selecciona la frecuencia deseada mediante filtros

analgicos para su amplificacin.

Amplificadores de frecuencia intermedia: En este bloque de FI se

realiza la selectividad y ganancia del receptor, la FI siempre tiene

menor frecuencia que la RF debido a que es mas fcil y menos costos

fabricar amplificadores estables para seales de baja frecuencia

Conversor ADC y DAC: debido a que la trasmisin y la recepcin se

realisa mediante un medio analgico es imprescindible realizar una

conversin analgica/digital en el receptor y digital/analgica en el

transmisor.

Modulador / demodulador: este bloque culpe funciones complejas y

totalmente digitales. Generalmente son realizadas por Procesadores

de Propsito General GPP, pero para que las tareas de

Modulacin/Demodulacin puedan ser fcilmente programables se

utilizan procesadores como DSPs (Digital Signal Processors) o FPGAs

(Field Programmable Gate Arrays). Generalmente se usa

modulaciones de mltiples niveles denominadas en cuadratura M-

QAM, M-PSK, etc.

Referencias:

[1] Tene Castillo, Juan Pablo, Diseo e implementacin de un Sistema de

Conmutacin de

red para un sistema GSM basado en OpenBTS y Asterisk, 2013. En lnea

disponible en: https://goo.gl/5yfASu

[2] usRp n200/n210 netwoRked series, Ettus Research, 2012. Disponible

en : goo.gl/WHury1

[3] RDS (RADIO DEFINIDO POR SOFTWARE). CONSIDERACIONES PARA SU

IMPLEMENTACIN DE HARDWARE. Jos ngel Amador Fundora 1, Nstor

Alonso Torres2, 2013. Disponible en: file:///C:/Users/OSCAR/Downloads/104-

310-2-PB.pdf

Anda mungkin juga menyukai

- Características Principales Del USRP N210Dokumen4 halamanCaracterísticas Principales Del USRP N210Jandry González100% (1)

- Informe OSPF IPv6Dokumen3 halamanInforme OSPF IPv6Natalia Andrea Gonzalez GarzonBelum ada peringkat

- DslamDokumen7 halamanDslamAnonymous d0J9xGuLZoBelum ada peringkat

- Introducción a Debug MS-DOSDokumen14 halamanIntroducción a Debug MS-DOSDan LeoBelum ada peringkat

- RGN P05 Programación en C Con MikroC PRO For PICDokumen19 halamanRGN P05 Programación en C Con MikroC PRO For PICMariana Gonzales VickerBelum ada peringkat

- TV NTSC Mi PresentacionDokumen50 halamanTV NTSC Mi Presentacionkertesz25Belum ada peringkat

- Demodulación PSK y QPSKDokumen6 halamanDemodulación PSK y QPSKAshely Katt TushubiBelum ada peringkat

- Parametros en El Diseño de RadioenlacesDokumen63 halamanParametros en El Diseño de RadioenlacesSergio Granados Quezada0% (2)

- Circutos de Radio y Alta Frecuencia Lab2Dokumen17 halamanCircutos de Radio y Alta Frecuencia Lab2Johann Ivan AldahirBelum ada peringkat

- Exposicion - PCB - RFDokumen26 halamanExposicion - PCB - RFRaul Depaz NuñezBelum ada peringkat

- Conversión Digital Análoga con DAC0808Dokumen2 halamanConversión Digital Análoga con DAC0808Allan PerezBelum ada peringkat

- Propagacion SeñalesDokumen124 halamanPropagacion SeñalesMICHAEL FRANCISCO RIOS ESPINOZABelum ada peringkat

- Respuesta frecuencia amplificador BJTDokumen12 halamanRespuesta frecuencia amplificador BJTv_kathyBelum ada peringkat

- 3 - Agregar IOS de Router y Switch A GNS3 PDFDokumen11 halaman3 - Agregar IOS de Router y Switch A GNS3 PDFDanny Garzón100% (1)

- Informe 01 DHCP y NATDokumen4 halamanInforme 01 DHCP y NATalejandroBelum ada peringkat

- Historia de Automatizacion y PLCDokumen7 halamanHistoria de Automatizacion y PLCKfesito Chak Bola'ay100% (1)

- Nat PreguntasDokumen19 halamanNat Preguntasliliberh12345678Belum ada peringkat

- Trabajo Academico Telecomunicaciones Iii Ray Pillaca Dued Ayacucho 2011200464Dokumen13 halamanTrabajo Academico Telecomunicaciones Iii Ray Pillaca Dued Ayacucho 2011200464Ray PillacaBelum ada peringkat

- Mapeo SDHDokumen32 halamanMapeo SDHJorge CopaBelum ada peringkat

- Presentación HSDPA y HSUPA 1 PDFDokumen43 halamanPresentación HSDPA y HSUPA 1 PDFWillmans Sopla RojasBelum ada peringkat

- Proyecto de Radio EnlaceDokumen66 halamanProyecto de Radio EnlaceJOSE MARIA COCA PEREIRABelum ada peringkat

- Sistema GSMDokumen14 halamanSistema GSMScarllet Osuna TostadoBelum ada peringkat

- MPLS Pseudocables en GNS3 Cisco 7200Dokumen10 halamanMPLS Pseudocables en GNS3 Cisco 7200ChiseledPrawnBelum ada peringkat

- Modelo Okumura-HataDokumen29 halamanModelo Okumura-HataFabian Miño100% (2)

- Conversor Analógico Digital de SeguimientoDokumen14 halamanConversor Analógico Digital de SeguimientoBenjamin Omar Gutierrez MedellinBelum ada peringkat

- RTC DS1307 Con PBPDokumen8 halamanRTC DS1307 Con PBPalvaldez035981100% (1)

- Resumen de Capitulos Modulo 2Dokumen29 halamanResumen de Capitulos Modulo 2Maria Teresa Escobar RamirezBelum ada peringkat

- Informe 1 PotenciaDokumen3 halamanInforme 1 PotenciaDanny MantillaBelum ada peringkat

- Laboratorio Programación Switch PuTTYDokumen12 halamanLaboratorio Programación Switch PuTTYdiego armando martinez aponteBelum ada peringkat

- Redistribucion de Rutas 29087Dokumen32 halamanRedistribucion de Rutas 29087Paola Carranza DonayreBelum ada peringkat

- Ingeniería en sistemas computacionales y Com y Enrutamiento de redes de datosDokumen10 halamanIngeniería en sistemas computacionales y Com y Enrutamiento de redes de datosYARA CASIOBelum ada peringkat

- Ccna 2 v5.0 Examen FinalDokumen23 halamanCcna 2 v5.0 Examen FinalKaren Fernanda Lucas100% (1)

- Modulación y Demodulación FSK M-Aria WordDokumen5 halamanModulación y Demodulación FSK M-Aria WordAlberto GuillenBelum ada peringkat

- Diseño SDHDokumen5 halamanDiseño SDHHarold Alejo CastilloBelum ada peringkat

- Ni Multisim 12 FullDokumen1 halamanNi Multisim 12 FullGuillermo Maldonado100% (1)

- Leccion 14Dokumen28 halamanLeccion 14YeissonCandelaBelum ada peringkat

- Universidad Nacional Del Callao Examen Parcial Telematica 2021-ADokumen1 halamanUniversidad Nacional Del Callao Examen Parcial Telematica 2021-AJunior Aguilar RodriguezBelum ada peringkat

- Aguilar Rodriguez Junior Anderson Examen Parcial Telematica 2021-bDokumen2 halamanAguilar Rodriguez Junior Anderson Examen Parcial Telematica 2021-bJunior Aguilar RodriguezBelum ada peringkat

- Redes HFCDokumen34 halamanRedes HFCDavid NasaelBelum ada peringkat

- EmisoresDokumen2 halamanEmisoresAriel SanchezBelum ada peringkat

- Labo3 Tele2Dokumen8 halamanLabo3 Tele2Cesar Terrazas VillarroelBelum ada peringkat

- Informe Laboratorio 1 Manual de Laboratorio Packet TracerDokumen22 halamanInforme Laboratorio 1 Manual de Laboratorio Packet TracerErick Barrantes QuirósBelum ada peringkat

- 3.clase EWSD Curso SiemensDokumen62 halaman3.clase EWSD Curso SiemensAlvaro Rodriguez100% (1)

- Multiplexación 8Dokumen4 halamanMultiplexación 8Zzack Llanque RodrigezBelum ada peringkat

- 7.2.4.3 Uso de Wireshark para Examinar Capturas de FTP y TFTPDokumen22 halaman7.2.4.3 Uso de Wireshark para Examinar Capturas de FTP y TFTPHenry FloresBelum ada peringkat

- Adsl PaperDokumen16 halamanAdsl PaperPabloMuñozAlbitesBelum ada peringkat

- Protocolo de Enrutamiento RIP GNS3Dokumen6 halamanProtocolo de Enrutamiento RIP GNS3Juan IngaBelum ada peringkat

- Diseño de red de radiocomunicaciones de larga distancia en BoliviaDokumen46 halamanDiseño de red de radiocomunicaciones de larga distancia en BoliviapabloBelum ada peringkat

- Control de Potencia en AC Con Triac y Microcontrolador PIC 16F628ADokumen8 halamanControl de Potencia en AC Con Triac y Microcontrolador PIC 16F628ALuis Alejandro Ramos RojasBelum ada peringkat

- Filtro Pasa BajosDokumen4 halamanFiltro Pasa BajosDennys SantiagoBelum ada peringkat

- Modulacion PPMDokumen4 halamanModulacion PPMAnthony Reynaldo Flores GomezBelum ada peringkat

- CNv6 instructorPPT Chapter2Dokumen52 halamanCNv6 instructorPPT Chapter2Miguel Angel Ruiz JaimesBelum ada peringkat

- Tarjeta Desarrollo DsPICDokumen34 halamanTarjeta Desarrollo DsPICRoyer Porta CapchaBelum ada peringkat

- Informe Laboratorio No 4Dokumen5 halamanInforme Laboratorio No 4John QuinteroBelum ada peringkat

- Control Del TLC5940Dokumen4 halamanControl Del TLC5940bernejorgeBelum ada peringkat

- Estimación de canal MIMO en ondas milimétricas mediante motores de juegos y aceleración por HardwareDari EverandEstimación de canal MIMO en ondas milimétricas mediante motores de juegos y aceleración por HardwareBelum ada peringkat

- Servicio de Mensajes Cortos (SMS) el Mercado Telefónico de EspañaDari EverandServicio de Mensajes Cortos (SMS) el Mercado Telefónico de EspañaBelum ada peringkat

- Ridolfi SDR PDFDokumen3 halamanRidolfi SDR PDFdani385arBelum ada peringkat

- Curso Catv 2003Dokumen46 halamanCurso Catv 2003Manuel Alejandro Villacorta GarciaBelum ada peringkat

- ProyectoER 2Dokumen13 halamanProyectoER 2Bryan GordilloBelum ada peringkat

- Fracciones Parciales PDFDokumen5 halamanFracciones Parciales PDFLuis SegoviaBelum ada peringkat

- Covoluccion DiscretaDokumen10 halamanCovoluccion DiscretaBryan GordilloBelum ada peringkat

- Tarea 6 - INFORMEDokumen4 halamanTarea 6 - INFORMEBryan GordilloBelum ada peringkat

- PO PI Bryan GordilloDokumen6 halamanPO PI Bryan GordilloBryan GordilloBelum ada peringkat

- Covoluccion DiscretaDokumen10 halamanCovoluccion DiscretaBryan GordilloBelum ada peringkat

- Informe FinalDokumen19 halamanInforme FinalBryan GordilloBelum ada peringkat

- Deber 6Dokumen6 halamanDeber 6Bryan GordilloBelum ada peringkat

- Informe FinalDokumen19 halamanInforme FinalBryan GordilloBelum ada peringkat

- ProyectoER 2Dokumen13 halamanProyectoER 2Bryan GordilloBelum ada peringkat

- Sistema Inalámbrico de Seguridad y Ubicación para Vehículos PropuestaDokumen1 halamanSistema Inalámbrico de Seguridad y Ubicación para Vehículos PropuestaBryan GordilloBelum ada peringkat

- Tarea 6 - INFORMEDokumen4 halamanTarea 6 - INFORMEBryan GordilloBelum ada peringkat

- Impacto Socio Económico Del Turismo de EventosDokumen2 halamanImpacto Socio Económico Del Turismo de EventosBryan GordilloBelum ada peringkat

- Mochila de Carga Suspendida: January 2014Dokumen6 halamanMochila de Carga Suspendida: January 2014Bryan GordilloBelum ada peringkat

- PO CE Bryan GordilloDokumen6 halamanPO CE Bryan GordilloBryan GordilloBelum ada peringkat

- Metodo Burbuja EjercicioDokumen4 halamanMetodo Burbuja EjercicioBryan GordilloBelum ada peringkat

- PO PF Bryan GordilloDokumen6 halamanPO PF Bryan GordilloBryan GordilloBelum ada peringkat

- Análisis de EmprendimientoDokumen1 halamanAnálisis de EmprendimientoBryan GordilloBelum ada peringkat

- Parametros S - Roger Alvarado - Ronald PinedaDokumen11 halamanParametros S - Roger Alvarado - Ronald PinedaBryan GordilloBelum ada peringkat

- Impacto Socio Económico Del Turismo de EventosDokumen2 halamanImpacto Socio Económico Del Turismo de EventosBryan GordilloBelum ada peringkat

- Proyecto SIDokumen2 halamanProyecto SIBryan GordilloBelum ada peringkat

- Tecnologías InalámbricasDokumen12 halamanTecnologías InalámbricasBryan GordilloBelum ada peringkat

- Filtro HairpinDokumen9 halamanFiltro HairpinBryan GordilloBelum ada peringkat

- AtenuadorDokumen6 halamanAtenuadorBryan GordilloBelum ada peringkat

- Divisor WilkinsonDokumen9 halamanDivisor WilkinsonBryan GordilloBelum ada peringkat

- Mochila generadora de energía al caminarDokumen3 halamanMochila generadora de energía al caminarBryan GordilloBelum ada peringkat

- Proyecto SIDokumen5 halamanProyecto SIBryan GordilloBelum ada peringkat

- Comparativa Entre Normas APA y IEEEDokumen3 halamanComparativa Entre Normas APA y IEEEBryan GordilloBelum ada peringkat

- Mochila de Carga SuspendidaDokumen5 halamanMochila de Carga SuspendidaBryan GordilloBelum ada peringkat

- Orden de TrabajoDokumen1 halamanOrden de Trabajoxabiddc44830% (1)

- Cuestionario 1 y 2 Admon Ing Segu ParcialDokumen2 halamanCuestionario 1 y 2 Admon Ing Segu ParcialIvancho MedinaBelum ada peringkat

- Actividad Módulo 4Dokumen2 halamanActividad Módulo 4Andrew RosesBelum ada peringkat

- Diseño sistema inscripciones ingeniería UNAMDokumen5 halamanDiseño sistema inscripciones ingeniería UNAMBrigadefuhrer Ramses SaldivarBelum ada peringkat

- Diseno-Arquitectura Pendiente 08-08-2021Dokumen25 halamanDiseno-Arquitectura Pendiente 08-08-2021jhon rodriguezBelum ada peringkat

- Conecta Tus Proyectos Al Puerto USBDokumen13 halamanConecta Tus Proyectos Al Puerto USBEsteticoBelum ada peringkat

- 5 - Opciones de IDokumen26 halaman5 - Opciones de IYenifer Chacón RodríguezBelum ada peringkat

- Aplicaciones Parecidas A Power PointDokumen14 halamanAplicaciones Parecidas A Power PointKeviin HernándezBelum ada peringkat

- Ene2023-1Dokumen7 halamanEne2023-1Grandón Cartes Víctor AlejandroBelum ada peringkat

- Manual de Configuracion de CognexDokumen14 halamanManual de Configuracion de Cognexalejandro garciaBelum ada peringkat

- Evolución de la investigación de mercados y las nuevas tecnologías de 1950 a 2020Dokumen1 halamanEvolución de la investigación de mercados y las nuevas tecnologías de 1950 a 2020Jorge Andrés Apache AyalaBelum ada peringkat

- Cotizacion Alitas ColombianasDokumen2 halamanCotizacion Alitas ColombianasDaniel Felipe CasadiegoBelum ada peringkat

- Pos G - DB SoftDokumen4 halamanPos G - DB SoftFernando Bringas ChBelum ada peringkat

- Configuración histórico RAID 5Dokumen9 halamanConfiguración histórico RAID 5Oskr ArroyoBelum ada peringkat

- Silabo Historia D El Pensamiento EconómicoDokumen7 halamanSilabo Historia D El Pensamiento EconómicoBYRON CRAFT100% (1)

- TARE - 1 - CCNA - 2 - Grupo - 2150507 - 27Dokumen200 halamanTARE - 1 - CCNA - 2 - Grupo - 2150507 - 27alexis pedrozaBelum ada peringkat

- Tutorial Hackear Wpa2Dokumen10 halamanTutorial Hackear Wpa2Jesus Daniel DoriaBelum ada peringkat

- Sistema Operativo Linux Ubuntu - Ventajas y DesventajasDokumen3 halamanSistema Operativo Linux Ubuntu - Ventajas y DesventajasALEXANDER TACOBelum ada peringkat

- Nuevo Manual de Usuario WebDokumen33 halamanNuevo Manual de Usuario WebTavo RivièreBelum ada peringkat

- EF - 5 Reporte Auxiliar Comprobantes Dentro de Polizas v1 Rev LTDokumen27 halamanEF - 5 Reporte Auxiliar Comprobantes Dentro de Polizas v1 Rev LTaalanis53Belum ada peringkat

- Metodología RUP guía desarrollo softwareDokumen5 halamanMetodología RUP guía desarrollo softwareDiego L.Belum ada peringkat

- Modalidades de OperacionDokumen5 halamanModalidades de OperacionEdgar Dante AllighieriBelum ada peringkat

- Curriculum AnibalDokumen4 halamanCurriculum AnibalAníbal Giovanni Jara MartínezBelum ada peringkat

- Implementación WMS ProfranceDokumen23 halamanImplementación WMS ProfranceHenry Viasu ValeroBelum ada peringkat

- Guía completa para elegir tu próxima laptopDokumen7 halamanGuía completa para elegir tu próxima laptopMauro Quisbert HuariBelum ada peringkat

- Actividad 1Dokumen2 halamanActividad 1Isaac Aponte Villegas100% (1)

- Informe de Limites PostgresDokumen4 halamanInforme de Limites Postgresrichardtk_1Belum ada peringkat

- Responsabilidad y Gobierno ElectrónicoDokumen45 halamanResponsabilidad y Gobierno ElectrónicoAdrián RodriguezBelum ada peringkat

- Asignación Final - PROPUESTA DE FORMACIÓNDokumen6 halamanAsignación Final - PROPUESTA DE FORMACIÓNmariany sanchez100% (1)

- Instructivo Molycop ToolsDokumen10 halamanInstructivo Molycop ToolsAnonymous 7IoqThyc0% (1)