Arquitetura e Organizacao de Computadores 5 Ed William Stallings Cap 8

Diunggah oleh

itamar150%(1)0% menganggap dokumen ini bermanfaat (1 suara)

135 tayangan43 halamanAritmética para computadores com inteiros e ponto flutuante.

- Principais Pontos, Representação de Inteiros, Representação em Sinal-Magnitude e com complemento de dois;

-Aritmética com Inteiros e Sistema de Precisão Simples;

-Sistema de Precisão Dupla, Ponto flutuante, Norma IEEE-754

Hak Cipta

© © All Rights Reserved

Format Tersedia

PDF atau baca online dari Scribd

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniAritmética para computadores com inteiros e ponto flutuante.

- Principais Pontos, Representação de Inteiros, Representação em Sinal-Magnitude e com complemento de dois;

-Aritmética com Inteiros e Sistema de Precisão Simples;

-Sistema de Precisão Dupla, Ponto flutuante, Norma IEEE-754

Hak Cipta:

© All Rights Reserved

Format Tersedia

Unduh sebagai PDF atau baca online dari Scribd

0%(1)0% menganggap dokumen ini bermanfaat (1 suara)

135 tayangan43 halamanArquitetura e Organizacao de Computadores 5 Ed William Stallings Cap 8

Diunggah oleh

itamar15Aritmética para computadores com inteiros e ponto flutuante.

- Principais Pontos, Representação de Inteiros, Representação em Sinal-Magnitude e com complemento de dois;

-Aritmética com Inteiros e Sistema de Precisão Simples;

-Sistema de Precisão Dupla, Ponto flutuante, Norma IEEE-754

Hak Cipta:

© All Rights Reserved

Format Tersedia

Unduh sebagai PDF atau baca online dari Scribd

Anda di halaman 1dari 43

8.2

8.3

8.4

8.5

8.6

8.7

ARITMETICA

COMPUTACIONAL

A unidade légica e aritmética

Representacao de numeros inteiros

Representagao sinal-magnitude

Representagao em complemento de dois

Conversao entre representagdes com numeros de bits diferentes

Representacao de ponto fixo

Aritmética de numeros inteiros

Negagao

Adig&o @ subtragéo

Multiplicagao.

Divisao

Representacao de ntimeros de ponto flutuante

Princi

Padrao IEEE para representacao de nimeros binarios de ponto flutuante

Aritmética de niimeros de ponto flutuante

Adigao e subtragao

Multiplicagao e diviséo

Consideragées de preciso

Padrao IEEE para aritmética de nimeros binarios de ponto flutuante

Leitura e site Web recomendados

Exercicios

Apéndice 8A Sistemas de numeracao

O sistema decimal

O sistema binario

Conversdo entre ntimeros binarios e decimais

Notagao hexadecimal

290 — ARQUITETURA £ ORGANIZACAO DE COMPUTADORES — Cap. 8

[Nameros inteitos reprosentivois

——— Reta de nimeros

Tam 0 21

{2} Nimeros interos em complemento de dois

Undertow em Undertow em

nimeroe negates nimeron postivos

sete tl esr \ pea hee

woe rorormel a Teprerentnvas” —_ nimeres posaivos

gy ee ST TV ee ae

iii, | Vb | hen

= 2%) x 2 5x2 0 sez 1-202 iogmaal

(b) Nimeros de ponto flutuante

5 ; ——

1 Os dois aspectos mais importantes da aritmética computacional so o modo como

‘os mimeros so representados (0 formato binério) ¢ os algoritmos usados para as |

operagdes aritméticas basicas (adigao, subtracao, multiplicagio e divisio). Isso se

aplica tanto para a aritmética de ntimeros inteiros quanto para a de ntimeros de

ponto flutuante.

1 Niimeros de ponto flutuante so expressos na forma de um mimero (mantissa)

multiplicado por uma constante (base) elevada a uma poténcia inteira (expoente). Eles

podem ser usados para representar niimeros muito grandes e muito pequenos.

MA maioria dos processadores implementa padrao IEEE 754 para representacio

aritmética de ntimeros de ponto flutuante. Esse padrao define um formato de 32

bits e de 64 bits.

ARITMETICA COMPUTACIONAL 291

mética (ULA — arithmetic and logic unit). Em seguida, enfocamos 0 aspecto mais com-

exo da ULA: a aritmética computacional. As fungdes Iégicas que fazem parte da

ULA sao descritas no Capitulo 9 e a implementagio de fungbes légicas e aritméticas simples

por meio de circuitos digitais é discutida no Apéndice A.

A aritmética computacional geralmente opera com dois tipos de mimeros muito dife-

rentes: ntimeros inteiros e ntimeros de ponto flutuante. Em ambos 0s casos, a escolha da re-

presentagio é uma questio crucial de projeto, sendo, por isso, tratada primeiro. As operages

aritméticas serdo discutidas em seguida.

Uma revisio sobre sistemas de numeragao € incluida no apéndice deste capitulo.

N= estudo sobre o processador comega com uma visio geral da unidade légica e arit-

8.1 A UNIDADE LOGICA E ARITMETICA

AULA éa parte do computador que de fato executa as operagSes aritméticas e Iégicas

sobre os dados. Todos os outros elementos do computador — unidade de controle, registra-

dores, meméria, E/S — servem, principalmente, para trazer os dados a serem processados

pela ULA e receber os resultados das operagées efetuadas. De certo modo, a ULA constitui o

niicleo ou a esséncia de um computador.

Assim como todos os demais componentes eletrénicos de um computador, a ULA é ba-

seada em dispositivos légicos digitais simples, capazes de armazenar digitos binrios e efe-

tuar operages simples de légica booleana. O leitor interessado na implementagdo de légica

digital pode consultar 0 apéndice deste livro.

| A Figura 8.1 indica, em termos gerais, como a ULA € conectada com o restante do pro-

cessador. Os dados sao fornecidos 4 ULA em registradores e os resultados de uma operagao

sio armazenados em registradores. Esses registradores sio éreas de armazenamento tempo-

rério dentro do processador, conectadas 4 ULA por meio de caminhos de sinal (veja, por

exemplo, a Figura 2.3). A ULA pode também ativar bits especiais (flags) para indicar 0 resul-

tado de uma operacao. Por exemplo, caso o resultado de uma operacao exceda a capacidade

de armazenamento de um registrador, isso é indicado atribuindo 0 valor 1 ao bit de overflow.

Esses bits especiais sio também armazenados em registradores internos do processador. A

unidade de controle fornece sinais para controlar a operagéo da ULA e a transferéncia de da-

dos entre a ULA e 08 registradores.

Unidade de controle Bits especiais

Registradores Rogistradores

Figura 8.1 Entradas e saidas da ULA.

292 ARQUITETURA F ORGANIZACAO DE COMPUTADORES Cap. 8

8.2 REPRESENTACAO DE NUMEROS INTEIROS

No sistema de ntimeros bindrios (veja 0 Apéndice 8A), é possivel representa nuimeros

arbitrarios usando os digitos zero e um, o sinal de subtracdo ("~", para ntimeros negativos) e

a virgula decimal (que separa a parte inteira e a parte fraciondria do numero). Por exemplo:

-1101,0101y = -13,3125,y

Entretanto, para armazenar e processar esses mimeros no computador, nao é posstvel

usar os sinais de menos e virgula. Apenas digitos bindrios (0 e 1) podem ser usados para a

representagao de ntimeros. Isso ndo constitui um problema se quisermos apenas representar

ntimeros inteiros nao negativos. Por exemplo, uma palavra de 8 bits pode ser usada para re-

presentar ntimeros de 0 a 255.

00000000 0

09000001 1

00101001 = 41

10000000 = 128

1111111 = 255

De modo geral, se uma seqiiéncia de n digitos binarios a, , a, >... @,4 for interpretada

como um niimero inteiro sem sinal 4, seu valor sera dado por:

nl

A= 2a;

°

Representacao sinal-magnitude

Diversas convengées alternativas so usadas para representar ntimeros inteiros positi-

vos € negativos; todas elas tratam o bit mais significative da palavra (bit mais esquerda)

como um bit de sinal: se 0 bit mais & esquerda for 0, 0 ntimero seré positivo; se for 1, 0 nti-

mero seré negativo.

A forma mais simples de representagao que emprega um bit de sinal é a representagio

sinal-magnitude. Em uma palavra de 1 bits, os 1" ~ 1 bits mais a direita representam a magni-

tude do mimero inteiro. Por exemplo:

+18 = 00010010

=18 = 10010010 (sinal-magnitude)

O caso geral pode ser expresso como a seguir:

2

Dai se ana-o

i A iz0

Sinal-magnitude: A=) ‘1, (8.1)

~Y 2a; se an.

i=0

A representagao sinal-magnitude apresenta diversas desvantagens. Uma delas € que,

para efetuar operagoes de adicao e subtracao, é preciso considerar tanto a magnitude quanto

ARITMETICA COMPUTACIONAL 293

osinal dos dois operandos. Isso ficaré mais claro na discussdo apresentada na Seco 8.3. Outra

desvantagem 6 que existem duas representagdes para 0:

00000000

10000000 (sinal-magnitude)

Isso 6 inconveniente, pois é mais dificil testar se um valor é igual a 0 (operagéo que é

executada fregiientemente) do que no caso em que existe uma tinica representacao para 0.

Em virtude dessas desvantagens, a representagao sinal-magnitude ¢ raramente usada na

implementagio da parte inteira de uma ULA. O esquema mais comum é a representacdo em

complemento de dois.

Representacao em complemento de dois

Assim como a representacao sinal-magnitude, a representago em complemento de dois

usa o bit mais significativo como bit de sinal, 0 que torna fécil testar se um ntimero inteiro é

positivo ou negativo, Entretanto, 0s demais bits séo interpretados de maneira diferente. A Ta-

bela 8.1 relaciona as caracteristicas-chave da representagao e da aritmética em complemento

de dois, abordadas nesta e na préxima segao.

A maioria das abordagens da representagao em complemento de dois define apenas as

regras para representar os ntimeros negativos, nao incluindo qualquer prova formal de que

esse esquema ‘funciona’, A abordagem adotada nesta segao e na Seco 8.3, a0 contrério, é ba-

seada em Dattatreya (1993), que sugere que essa representagao serd bem compreendida se for

definida em termos de uma soma ponderada de bits, como foi feito anteriormente para 0 caso

das representacdes sem sinal e de sinal-magnitude. A vantagem desse tratamento é nao deixar

diividas de que as regras definidas para as operagdes aritméticas na notacao em complemento

de dois funcionam em todos os casos.

Tabela 8.1. Caracteristicas da representacao e aritmética em complemento de dois

Falxa de valores representavels amt 1

‘Numero de representagdes para zero | 1 a

Negacio Pegue o complemento booleano de cada bit do

numero positive correspondente e entio some 1 ao

padrao de bits resultante, tratado como um ntimero

| inteiro sem sinal

Expansao do ntimero de bits | ‘Acrescente posigoes de bit & esquerda e preencha

esses bits com o valor do bit de sinal original.

l Regra de overflow Se dois nimeros com mesmo sinal (ambos positivos

ou ambos negativos) forem somados, ocorrerd

overflow apenas se o resultado tiver sinal oposto.

Regra de subtragio Para subtrair B de A, pegue o complemento de dois

de Be some-o com A.

294 ARQUITETURA E ORGANIZAGAO DE COMPUTADORES Cap. 8

Considere um ntimero inteiro A de n bits na representago em complemento de dois. Se

A for positivo, entao o bit de sinal, a, 1, sera igual a zero. Os bits restantes representam a mag-

nitude do ntimero, assim como na representagao sinal-magnitude:

2

A=) 2a; para A20

3

O mimero zero é tratado como um ntimero positivo, isto 6, tem o bit de sinal igual a0

¢ todos os demais bits (magnitude) iguais a 0. E facil ver que a faixa de ntimeros inteiros po-

sitivos que podem ser representados é de 0 (todos os bits de magnitude sio iguais a 0) a2"! -1

(todos os bits de magnitude so iguais a 1), Para representar um ntimero maior seriam neces-

sérios mais bits.

Se A é um ntimero negativo (A <0), o bit de sinal, a, 1, € 1. Os n -1 bits restantes podem

representar até 2"! valores. Portanto, a faixa de mimeros inteiros negatives que podem ser

representados é de -1 a -2""1, E desejével associar padrées de bits a ntimeros inteiros negati-

vos, de maneira que as operagGes aritméticas possam ser efetuadas diretamente, de modo se-

melhante & aritmética de ntimeros inteiros sem sinal. Na representagao de nimeros inteiros

sem sinal, para calcular o valor de um ntimero inteiro a partir da sua representagao, o bit mais.

significativo é multiplicado por +2"-!. Em uma representagio que usa um bit de sinal, as pro-

priedades aritméticas desejadas sao obtidas, como veremos na Secao 8.3, se o valor do ntimero

6 calculado a partir da sua representago multiplicando o bit mais significativo por -2", Essa

€ a convengao adotada na representago em complemento de dois, 0 que fornece a seguinte

expresso para mimeros negativos:

2

lana + > Zar (8.2)

i=0

Complemento de dois = A=

Para ntimeros inteiros positives, a,, ; = 0. Portanto, a Equacao 8.2 define o valor da re-

presentacao em complemento de dois, tanto para mimeros positives quanto para negativos.

A representacao em complemento de dois pode ser visualizada por meio da represen-

tagao geométrica mostrada na Figura 8.2, extraida de Benham (1992). O circulo na metade su-

perior de cada parte da figura & formado selecionando 0 segmento adequado da reta de

ntimeros e juntando as duas extremidades. Comegando a partir de qualquer ntimero do cf

culo, podemos somar um valor k positivo (ou subtrair um valor k negativo) a esse ntimero,

movendo k posigées no sentido hordrio, ou subtrair um valor k positivo (ou somar um valor

k negativo), movendo k posigdes no sentido anti-horério. Caso essa operagao cruze o ponto

em que as duas extremidades se juntam, a resposta obtida é incorreta

‘A Tabela 8.2 compara as representacées sinal-magnitude e em complemento de dois

para ntimeros inteiros de 4 bits. Embora a representacao em complemento de dois possa pa-

recer pouco natural, do ponto de vista humano, veremos que ela torna mais facil a implemen-

tagdo das operagGes aritméticas mais importantes — a adigao e a subtragao. Por isso, ela é

usada quase universalmente para representar ntimeros inteiros no processador.

295

ARITMETICA COMPUTACIONAL

stop ap ojawordwoy wo soxjaquy sorunu sop eo_pWoaR opSeyuasaday 7°g BINGE

819 Yop sov0wpy (4) suq b ap sosounn (0)

68L9SHEZL OlzEersole6-

ep odipy

‘ep opbenqns,

296 — ARQUITETURA F ORGANIZACAO DE COMPUTADORES — Cap. 8

Uma ilustracao util da natureza da representagao em complemento de dois é dada por

uma seqiiéncia de valores, em que o valor na extremidade direita € 1 (2°) e o valor de cada

Posigao seguinte, a esquerda, é 0 dobro do valor da posigao anterior, até chegar na posigéo

mais a esquerda, cujo valor é negado. Como é mostrado na Figura 8.3a, 0 ntimero mais nega-

tivo que pode ser representado em complemento de dois é -2"-! (onde m é 0 niimero de bits

da representagio); se qualquer dos bits que nao seja o bit de sinal tiver valor 1, ele adicionard

um valor positivo a esse ntimero. E claro que o bit de sinal (mais 4 esquerda) tem valor 1 no

caso de um ntimero negativo e valor 0 no caso de um mimero positivo. Dessa maneira, a re-

presentagio do maior ntimero positivo tem valor 0 seguido dos demais bits iguais a 1, cujo

valor é igual a 2-1-1

O restante da Figura 8.3 mostra o uso dessa seqiiéncia de valores para converter um

ntimero na representacdo em complemento de dois em um ntimero decimal e vice-versa.

Tabela 8.2 _RepresentagGes alternativas para ntimeros inteiros de 4 bits

Representacao Representacao Representacao em Representacao

decimal sinal-magnitude complemento de dois _polarizada

+8 a = aa

+7 ou om nn

+6 oo o10 110

45 o1o1 o101 1101

4 o100 o100 1100

+3. oo oo 1011

+2 0010 010 1010

+1 0001 001 1001

+40 0000 0000 1000

0 1000 = oa

eT 1001 un o110

2 1010 a0 o101

3 1011 1101 0100

4 1100 1100 oon

3 1101 1011 oo10

+ 10 1010 0001

a un 1001 0000

-8 = 1000 =

ARITMETICA COMPUTACIONAL — 297

=128 [| 64 | 32 | 16 | 8 are 1

|

(a) Seqidncia de oto valores em complemento de dois

=e | 64 | 2] | 8 aries

Evel et Di Fad (ics al, a

~128 420041 = 715

=e] | 2] el] 8 fut

1{/o0]ofof1]o]o]fo

120 = -128 +8

(€ Conversbo do valor decimal 120 pre eu valor bind

Figura 8.3 Conversio entre ntimeros bindrios em complemento de dois e ntimeros decimais.

Conversao entre representacdes com nimeros de bits diferentes

Algumas vezes é desej4vel converter a representagao de um ntimero inteiro com 1 bits

para sua representagio com m bits, onde m > n. Na notagdo sinal-magnitude, isso pode ser

feito facilmente: basta mover o bit de sinal para a posigao mais a esquerda e preencher as de-

mais posig&es novas com zeros. Por exemplo:

+18 = 00010010 (sinal-magnitude, 8 bits)

+18 = 0000000000010010 _(sinal-magnitude, 16 bits)

-18 = 10010010 —_(sinal-magnitude, 8 bits)

-18 = 1000000000010010 —_(sinal-magnitude, 16 bits)

Esse procedimento nao funciona no caso de mimeros inteiros negatives representados

em complemento de dois. Usando mesmo exemplo,

+18 = 00010010 (complemento de dois, 8 bits)

+18 = 0000000000010010 —_ (complemento de dois, 16 bits)

-18 = 11101110 (complemento de dois, 8 bits)

~32,658= 1000000001101110 — (complemento de dois, 16 bits)

O penuiltimo ntimero acima pode ser verificado pela seqiiéncia de valores da Figura 8.3.

O titimo mimero pode ser verificado usando a Equacao 8.2.

A regra para converter uma representagdo em complemento de dois em outra com

maior ntimero de bits consiste em mover o bit de sinal para a posigao mais a esquerda e preen-

cher as novas posigdes de bit com valor igual ao do bit de sinal. Para mimeros positivos, isso

significa preencher com zeros e, para ntimeros negativos, preencher com uns. Isso é chamado

extensio de sinal. Desa maneira, temos:

-18= 11101110 (complemento de dois, 8 bits)

-18= 1111111111101110 —_(complemento de dois, 16 bits)

298 ARQUITETURA E ORGANIZAAO DE COMPUTADORES — Cap. 8

Para mostrar que essa regra funciona, considere uma seqiiéncia de 1 bits de digitos bi-

narios a, ,8,-2 ~» aya, interpretada como um numero inteiro A, em complemento de dois, de

modo que seu valor seja:

m2

Maga + 2a;

Se A for um ntimero positivo, a regra claramente funcionard, Se A for negativo e quiser-

mos obter sua representacdo com m bits, onde m > 1, entao,

Esses dois valores devem ser iguais:

m2

214 S 2a;

m2 m2 m2

142+ Daa 14 D2

aren

iso

m2 me

Y= D2

ml isnl

=> Agi = Ap

Ao passar da primeira para a segunda equagao, pede-se que os m ~ 1 bits menos signi-

ficativos permanegam inalterados de uma representacdo para outra. Obtemos, entao, a pentil-

tima equacdo, que é verdadeira somente se todos os bits da posicao n ~ 1 am ~2 so iguais a

1. Dessa maneira, a regra de extensio de sinal funciona.

Representacao de ponto fixo

Mencionamos anteriormente que as representagdes discutidas nesta segio so conheci-

das como representacdes de ponto fixo. Isso ocorre porque elas fixam a posigéo da virgula

decimal como a posigao a direita do bit menos significativo. Essas representagdes podem tam-

bém ser usadas pelo programador para fragdes bindrias, se supusermos a virgula decimal po-

sicionada implicitamente em outra posigao.

ARITMETICA COMPUTACIONAL 299.

8.3 ARITMETICA DE NUMEROS INTEIROS

Esta segdo examina a implementagao das operagies aritméticas mais comuns em ntime-

10s representados em complemento de dois.

Negacao

Na representacdo sinal-magnitude, a regra para a negacao de um numero inteiro é sim-

ples: basta inverter o valor do bit de sinal. Na notagao em complemento de dois, a negagio

de um niimero inteiro é obtida pelos seguintes passos

1. Tome 0 complemento booleano de cada bit do ntimero (incluindo o bit de sinal), isto é,

troque cada 1 por 0 e cada 0 por 1

2. Adicione 1 ao resultado, visto como um ntimero inteiro binério sem sinal.

Esses dois passos do processo fornecem a operaao de complemento de dois de um nuime-

ro inteiro. Por exemplo:

+18 = 00010010 (complemento de dois}

complemento bit a bit = 11101101

+

11101110 = -18

Como se pode esperar, o resultado da dupla negagao de um ntimero é 0 préprio ntimero:

-18 = 11101110 (complemento de dois)

complemento bit a bit = 00010001

a1

00010010 = +18

‘A validade da operago descrita acima pode ser demonstrada usando a definigio da re-

presentagdo em complemento de dois dada pela Equacao 8.2. Novamente, considere uma se-

giiéncia de n digitos bindrios a,_, a, . aa) como um ntimero inteiro A, representado em

complemento de dois, de modo que seu valor seja:

m2

Taya + 2a;

Zo

Obtenha agora o complemento bit a bit, 3,7 4,2 ~. a, €, tratando o resultado como

um ntimero inteiro sem sinal, adicione 1. Finalmente, interprete a seqiténcia de n bits de di-

gitos bindrios resultante como um ntimero inteiro B, representado em complemento de dois,

de modo que seu valor seja:

m2

‘aa + 1+ 2a;

0

300 — ARQUITETURA E ORGANIZACAO DE COMPUTADORES Cap. 8

E facil mostrar que A = -B, ou seja, A+ B= 0:

2

A+B=-(a, +872" +1+| DY 2'@j+a)

'=0

lars] S 2!

Na seqiiéncia de equagées acima, supomos, ao adicionar 1, que a seqiiéncia de bits re-

presenta um ntimero inteiro sem sinal (obtido fazendo o complemento bit a bit do nimero

original) e tratamos 0 resultado, enti, como um ntimero inteiro em complemento de dois

Dois casos especiais devem ser considerados. O primeiro ¢ se A = 0. Nesse caso, para uma

representagao de 8 bits, temos:

Q = 00000000 (complemento de dois)

complemento bit a bit = 11111111

——,

100000000 = 0

O bit ‘vai-um’ (carry-in) com valor 1 obtido na posigao mais 4 esquerda (indicado por

um digito sombreado) é ignorado. Como resultado, temos que o complemento de dois de 06

0, como deveria ser.

O segundo caso especial é mais problematico. Se negarmos o padrao de bits constitufdo

de um bit com valor 1 seguido de 1 =1 bits de valor 0, obteremos esse mesmo mimero. Por

exemplo, para uma palavra de 8 bits, temos:

-128 = 10000000 (complemento de dois)

complemento de bit a bit = 01111111

+ 1

1og00000 = -128

sa anomalia nao pode ser evitada. O ntimero de padrées de bits distintos de uma pa-

lavra de n bits € 2", que € um mimero par. Desejamos representar ntimeros inteiros positivos,

negatives e 0. Se a quantidade de ntimeros inteiros positivos e negativos que podem ser re-

presentados for a mesma (sinal-magnitude), entdo existirao duas representacdes para 0. Se

existir apenas uma representacao para 0 (complemento de dois), entao as quantidades de nii-

meros positivos e negativos que podem ser representados serdo diferentes. No caso da repre-

sentacao em complemento de dois, usando uma palavra de n-bits, haverd uma representacio

para o valor ~2", mas nao para +2”.

ARITMETICA COMPUTACIONAL 301

1001 1100

+0102 +9100

1110 = -2 10000 - 0

fa) (7) + O45) (by (74) + (44)

01a

+0100

oui = 7 Sy

(co) (43) # G4) (a a) + ¢

e101

+9190

1001 = Overflow

fe) (45) (44) (7D + (6)

Figura 8.4 Adicdo de ntimeros na representagao em complemento de dois.

Adicao e subtracao

A adicao de mimeros na representacdo em complemento de dois é apresentada na Fi-

gura 8.4, Os quatro primeiros exemplos mostram operagdes bem-sucedidas. Se o resultado da

operacao for positivo, seré obtido um mimero positivo na notagio bindria. Se for negativo,

serd obtido um mimero negative em complemento de dois. Note que, em alguns dos exem-

plos, ocorre um ‘vai-um’ para fora do bit mais significativo da palavra, que é ignorado.

O resultado de uma adig3o pode ter um niimero de bits maior do que o tamanho da

palavra usada. Essa condigao é denominada overflow. Quando ocorre overflow, a ULA deve

sinalizar esse fato, para que o resultado nao seja utilizado. A detecgio de overflow é feita de

acordo com a seguinte regra: na adigao de dois ntimeros, ambos positivos ou negatives, ocor-

rerd overflow somente se o resultado tiver sinal oposto. As Figuras 8.4e e 8.4f mostram exem-

plos de overflow. Note que pode ocorrer overflow mesmo nao havendo ‘vai-um’ para fora do

bit mais significativo.

A subtragao também é implementada facilmente, usando a seguinte regra: para subtrair

um ntimero $ (subtraendo) de um mimero M (minuendo), pegue o complemento de dois (ne-

Bacio) de S e acrescente esse valor a M. Dessa maneira, a subtragdo ¢ implementada usando

a adicao, como indicado na Figura 8.5. Os dois tiltimos exemplos mostram que pode ocorrer

overflow.

Voltando a Figura 8.2, note que, para mimeros com n bits, podemos subtrair um valor

k positivo (ou adicionar um valor k negativo) movendo 2" ~ k posigdes no sentido horério.

Note que 2" — k é 0 complemento de dois de k. Isso demonstra graficamente que a subtragéo

M ~S pode ser feita somando a M o complemento de dois de S.

302 —ARQUITETURA E ORGANIZAGAO DE COMPUTADORES Cap. 8

0020 102

+1001 +1220

1011 = -5 10011 = 3

(b) M= 5 = 0101

s = 2 = 0010

1011 (a) M= 5 = 0101

010 S=-2 = 1110

ato “8 010

111 1010

+911 +1100

1110 = Overflow O11 =

(ey Me 7 = 01 (f) M=-6 =

$= -7 = 1001 S= 42

“8 = o1a -s =

Figura 8.5 Subtracdo de ntimeros na representacdo em complemento de dois (M - 5).

A Figura 8.6 sugere os caminhos de dados e elementos de hardware necessérios para

efetuar a adicao e a subtracao. O elemento central é um somador bindrio (ou meio-somador),

que recebe dois mimeros e produz como resultado a soma desses ntimeros e uma indicagio

de overflow. O somador bindrio trata os dois operandos como ntimeros inteiros sem sinal. (Um

circuito légico que implementa o somador & mostrado no Apéndice A.) Esses dois operandos

so apresentados ao somador em dois registradores, designados, nesse caso, como registra-

dores A e B. O resultado pode ser armazenado em um desses registradores ou em um terceiro.

A ocorténcia de overflow é indicada por um bit de overflow (0 = nao ocorreu overflow; 1 = ocor-

reu overflow). Na operagio de subtracdo, o subtraendo (registrador B) é passado por um cir-

cuito que calcula seu complemento de dois, sendo esse valor, entdo, passado para o somador.

Multiplicacao

Comparada as operagées de adicdo e subtracao, a multiplicagao é uma operagao com-

plexa, seja implementada em hardware seja em software. Uma grande variedade de algorit-

mos de multiplicagao tem sido usada em diversos computadores. O propésito desta subsegao

€ dar ao leitor uma nogio do tipo de abordagem tipicamente adotada. Comeamos pelo pro-

blema mais simples de multiplicar dois ntimeros inteiros sem sinal (nao negativos), para de-

pois examinar uma das técnicas mais usadas para a multiplicagéo de mimeros em

complemento de dois.

Numeros inteiros sem sinal

A Figura 8.7 mostra a multiplicagao de ntimeros inteiros bindrios sem sinal, tal como é

feita com lépis e papel. Diversas observagbes importantes podem ser feita:

ARITMETICA COMPUTACIONAL 303

1. A multiplicagao envolve a geragao de produtos parciais, um para cada digito do multi-

plicador. Esses produtos parciais so somados para a obtengao do produto final.

2. Os produtos parciais sio determinados facilmente. Quando o bit do multiplicador € 0, 0

produto parcial é 0. Quando é 1, o produto parcial é préprio multiplicando.

3. 0 produto total é obtido somando-se os produtos parciais. Para isso, cada produto parcial

sucessivo é deslocado um digito para a esquerda, em relagio ao produto parcial anterior.

4. A multiplicagio de ntimeros inteiros binérios de 1 bits resulta em um produto com até

2n bits de comprimento.

Registrador 8 Rogistrador A.

Complemento de dois

——+) set

oo

Somador

OF = Bit de overtiow

SEL = Seletor de adigso ou subtragio

Figura 8.6 Diagrama de blocos do hardware de adicao e subtragio.

1011 Multiplicando (11)

x 1101 Multiplicador (13)

i012

0000 Produtos

1011 parcia,

your)

“10001111 Produto (143)

Figura 8.7 Multiplicagao de ntimeros inteiros bindrios sem sinal.

304 ARQUITETURA £ ORGANIZACAO DE COMPUTADORES Cap. 8

Multiplicagdes podem ser feitas de modo mais eficiente do que na forma usual, em que

sio feitas usando-se lépis e papel. Primeiro, podemos acumular imediatamente cada produto

parcial obtido, em vez de esperar o célculo de todos os produtos parciais. Isso elimina a ne-

cessidade de armazenar todos os produtos parciais; é preciso, dessa maneira, um niimero me-

nor de registradores. Segundo, podemos poupar algum tempo na geracdo de produtos

parciais. Para cada 1 no multiplicador, é necessario realizar uma operacao de soma e um des-

locamento; para cada 0, apenas um deslocamento é necessario.

A Figura 8.8 mostra uma implementag3o possivel que emprega essas idéias. O multi-

plicador e o multiplicando sao carregados em dois registradores (Q e M). Também é necessario

‘um terceiro registrador, o registrador A, que é inicializado com valor 0. Existe ainda um registra-

dor C, de 1 bit, inicializado com 0, que contém um potencial bit ‘vai-um’ resultante da adicao.

Muttipieando

Moto

jomador den Adigio | Lépie de controle de

ommmnene igloo deslocamento

locamento & diveita

+ [a

nd ‘Mutiplicedor|

{0} Diagrama de blocos

c A Q M

0 0000 1101 1011 Valores iniciais

° i011 1101 1011 Adicao Primeiro

0 0101 1110~=S101t-—sDesiocanento } ciclo

0 0010 qui 1011 Beslocanento } Segundo

Ciclo

0 1101 ait 1011 Adicao Terceiro

° 0110 1211 1011 Desiocamento } ciclo

a 0001 quai 1011 Adigao Quarto

0 1000 1111 1011 Desiocamento } ciclo

(0) Exemplo ds Figure 8.7 (Produto em A.)

Figura 8.8 Implementagio do hardware de multiplicagdo de nimeros bindrios sem sinal.

A operagéo do multiplicador se dé como a seguir. A légica de controle 1é os bits do mul-

tiplicador, um de cada vez. Se Qy for 1, 0 multiplicador seré adicionado ao registrador Ae 0

resultado, armazenado nesse registrador, sendo o bit C usado para indicar a ocorréncia de

~—

ARIIMETICA COMPUTACIONAL 305,

overflow. Entao, todos os bits dos registradores C, A e Q sao deslocados um bit para a direita,

de modo que o bit C va para A,,_:, Ag vA para Q,,; € Qy seja perdido. Se Qo é 0, entéo nenhuma

adigao 6 efetuada, sendo feito apenas o deslocamento dos bits. Esse processo € repetido para

cada bit do multiplicador original. © produto de 2n bits resultante estar contido nos regis-

tradores A e Q. Um fluxograma dessa operacao € mostrado na Figura 8.9 e um exemplo €

dado na Figura 8.8b. Note por meio desse exemplo, que, no segundo ciclo, quando o bit do

multiplicador é 0, nao é feita a adigao.

GAO

‘M « Muttiplicando

0 & Multiplicador

Contador #2

CACA+M

Deslocamento de C, A, 2

Contadore- Contador - 1

Sim Produto

Contactor = BP> Sie

3 Fim) produ

Figura 8.9 Fluxograma da multiplicagao de ntimeros binérios sem sinal.

Multiplicacdo de numeros em compiemento de dois

Vimos que é possivel fazer adicao e subtragio de ntimeros na notagao em complemento

de dois tratando-os como ntimeros inteiros sem sinal. Considere o seguinte:

1001

+0012

1100

Se esses mimeros forem considerados ntimeros inteiros sem sinal, entéo estaremos fa-

zendo a adigéo 9 (1001) mais 3 (0011) para obter 12 (1100). Como os ntimeros sio representa-

| dos em complementos de dois, estamos de fato fazendo a adigio -7 (1001) mais 3 (0011) e

obtendo ~4 (1100)

306 —ARQUITETURA E ORGANIZACAO DE COMPUTADORES — Cap. 8

Infelizmente, esse esquema simples ndo funciona para a multiplicagao. Para mostrar

isso, consideramos novamente a Figura 8.7. Multiplicando 11 (1011) por 13 (1101), obtemos

143 (10001111). Se interpretarmos esses ntimeros como mimeros em complemento de dois, te-

remos -5 (1011) vezes ~3 (1101), que € igual a -113 (10001111). Esse exemplo mostra que a

multiplicag3o direta nao funciona se o multiplicando e o multiplicador séo negativos. De fato,

ela ndo funciona nos casos em que o multiplicando ou o multiplicador é negativo. Para ver

isso, voltamos a Figura 8.7 para explicar o que esté sendo feito em termos de operagdes com

poténcias de 2. Lembre-se de que qualquer ntimero binario sem sinal pode ser expresso como

uma soma de poténcias de 2. Portanto:

0 deeg axa re ledge Obi 2a iexe ae

2242242

1011

x 1101

00001011 1011 x 1x

00000000 1011 x0 x

00101100 1011 x1 x

01011000 1011 x 1x

002111

Figura 8.10 Multiplicagdo de dois ntimeros inteiros de 4 bits sem sinal produzindo um resultado

de 8 bits.

A multiplicagao de um ntimero bindrio por 2" € feita deslocando esse ntimero » bits para

a esquerda. Com isso em mente, a Figura 8.10 reproduz o exemplo da Figura 8.7, mostrando

a geragao dos produtos parciais por multiplicagao explicita. A tinica diferenca na Figura 8.10

é reconhecer que os produtos parciais devem ser vistos como ntimeros de 2n bits, gerados a

partir de um multiplicando de n bits.

Dessa maneira, 0 multiplicando 1011 de 4 bits é armazenado como um ntimero inteiro

sem sinal em uma palavra de 8 bits, ou seja, como 00001011. Cada produto parcial (exceto 0

cotrespondente a 2") é constituido desse mimero deslocado para a esquerda, com as posigies

nao ocupadas a direita preenchidas com zeros (por exemplo, um deslocamento para a esquer-

da de duas posigdes produz 00101100).

Podemos agora mostrar que a multiplicacao direta nao funciona no caso em que 0 mul-

tiplicando é negativo. O problema 6 que cada contribuicdo do multiplicando negative como

produto parcial deve ser um ntimero negativo de 2n bits; os bits de sinal dos produtos parciais

devem ser alinhados. Isso pode ser visto na Figura 8.11, que mostra a multiplicago de 1001

por 0011. Se esses ntimeros so tratados como niimeros inteiros sem sinal, a multiplicagao

9 x3 = 27 prossegue da forma usual. No entanto, se 1001 for interpretado como o miimero em

complemento de dois que representa o valor ~7, entio cada produto parcial deverd ser um

ntimero negativo, em complemento de dois, de 2n (8) bits, como mostrado na Figura 8.11b.

Note que isso pode ser feito estendendo cada produto parcial para a esquerda, com bits de

valor 1

E facil perceber que a multiplicagao direta também nao funciona se o multiplicador é nega-

tivo. A razdo é que, nesse caso, os bits do multiplicador nao correspondem aos deslocamentos ¢

as multiplicagdes que devem ocorrer. Por exemplo, considere o ntimero decimal -3, escrito em

ARITMETICA COMPUTACIONAL 307

complemento de dois com 4 bits como 1101. Se calcularmos os produtos parciais simplesmen-

te com base no valor de cada posigao de bit, obteremos a seguinte correspondéncia:

1101 6 - (1x B41x 274021 +1% 2°) = (29 +27 + 2°)

1001 (9) 1001 (-7)

x 0011 (3) x 0011 (3)

O0001001 1001 x 2° TITT1001 = (-7) x 2? = (-7)

00010010 1001 x 2* (-7) x 2! = (-14)

Goo11011 = (27) (-21)

(a) Nuimeros inteiros sem sinal (b) Nuimeros inteiros em complemento de dois

Figura 8.11 Comparagio entre multiplicagao de nimeros inteiros sem sinal e em complemento

de dois.

De fato, o que se deseja obter é ~(2' + 2°), Portanto, o multiplicador nao pode ser usado

diretamente da maneira como descrevemos.

Existem diversas solugdes possiveis para esse dilema. Uma delas seria converter o mul-

tiplicador e o multiplicando para ntimeros positives, efetuar a multiplicagio e, entdo, caso 0

sinal dos dois ntimeros originais seja diferente, tomar 0 complemento de dois do resultado.

Os projetistas tém preferido usar técnicas que ndo requeiram esse passo final de transforma-

gio. Um dos algoritmos mais usados é 0 algoritmo de Booth. Esse algoritmo tem também a

vantagem de efetuar a multiplicagdo de maneira mais répida do que em uma abordagem mais

direta.

O algoritmo de Booth ¢ representado na Figura 8.12 e pode ser descrito como a seguir.

Como antes, multiplicador e multiplicando so armazenados nos registradores Q e M, respec-

tivamente. Existe também um registrador de 1 bit, posicionado logicamente A direita do bit

menos significativo (Q,) do registrador Q e designado como Q , cujo uso é explicado a seguir.

resultado da multiplicago é dado nos registradores Ae Q. Ae Q, sao izados com

valor 0. Como antes, a Idgica de controle examina os bits do multiplicador, um de cada vez.

Quando cada bit é examinado, também é examinado o bit & sua direita. Se esses dois bits fo-

tem iguais (1-1 ou 0-0), ent&o todos os bits dos registradores 4, Qe Q_; serao deslocados 1

bit para a direita. Se eles forem diferentes, 0 multiplicando seré somado ou subtraido do re-

| gistrador A, dependendo se os dois bits so 0-1 ou 1-0, respectivamente, Apés essa operacao

de adigao ou subtragao, ocorre o deslocamento de um bit para a direita, que ¢ feito de tal ma~

neira que o bit mais a esquerda de A, denominado A,_,, € deslocado para A,, 2, mas também

permanece em A,, ,. Isso é necessdrio para preservar 0 sinal do ntimero armazenado em Ae

Q. Esse deslocamento é conhecido como deslocamento aritmético, porque preserva o bit de

sinal.

A Figura 8.13 mostra a seqiiéncia de eventos do algoritmo de Booth para o caso da mul-

tiplicagao de 7 por 3. A mesma operacdo é representada de maneira mais compacta na Figura

8.14a. O restante da Figura 8.14 apresenta outros exemplos de uso do algoritmo. Como se

t pode ver, 0 algoritmo funciona com qualquer combinagao de ntimeros positivos e negativos

Note também a eficiéncia do algoritmo. Blocos de 1s ou de Os sio ignorados, sendo feita, em

média, apenas uma adigao ou subtracao por bloco.

308 — ARQUITETURA E ORGANIZACAO DE COMPUTADORES — Cap. 8

Inicio

A©0,0,¢0

‘M & Muttipticando

0 & Mutipicador

Contador «7

~ oa

AecA-M AcAtM

Deslocamento aritmético pera

aires: A, 2, 0, _

Contador = Contador — 1

Figura 8.12 Algoritmo de Booth para a multiplicagio em complementos de dois,

a °

ooo 0014

001

1001

1110 0100

0101 0100

oo10 1010,

0001 0101,

°

u

outa

ouia

oui.

011

ou

ou.

oui.

Figura 8.13 Exemplo do algoritmo de Booth

ARITMETICA COMPUTACIONAL — 309

o11a o1ar

x0011 (0) x1101 (0)

i11i1001 11111001 1-0

eo0v000 1-1 oo00111 0-1

go0111_ 0-1 11-0

00010101 (21) iiio1011 = {(-21)

(ay) (7) x GB) = (21) tb) (7) x 3) = (2D)

100: 1002,

xo (a) x (oy

op000111 1-0 0000111 1-0

ao0do00 1-4 1111001 0-1

11902 1 pool 1-0

1i10101i | ¢-21) poo1e102 (21)

fe) (7) 13) = (210) (7) 3) = (22)

Figura 8.14 Exemplos de uso do algoritmo de Booth.

Por que 0 algoritmo de Booth funciona? Considere primeiramente o caso em que o mul-

tiplicador é positivo. Em particular, suponha que o multiplicador seja constituido de um bloco

de Is cercado por 0s (por exemplo, 00011110). Como sabemos, a multiplicagao pode ser feita

somando-se cépias apropriadamente deslocadas do multiplicando:

M x (00011110) = M x (24 + 2° + 2? +2!)

Mx(16+8+4+2)

=Mx30

O mimero de operagées requeridas pode ser reduzido para dois se observarmos que:

arte Ke

nit _ oir K (63)

Portanto,

' M x (00011110) = M x (2°- 2!)

Mx @2-2)

=Mx30

Assim, 0 produto pode ser gerado efetuando-se apenas uma adigao e uma subtracao do

multiplicando. Esse esquema pode ser estendido para qualquer mimero de blocos de 1s do

multiplicador, incluindo 0 caso em que 0 bloco tem um tnico 1. Portanto,

M x (01111010) = M x (2° + 2° + 24+ 23 +24)

Mx (Q’-2+27-2')

O algoritmo de Booth opera de acordo com esse esquema, efetuando uma subtragao

quando é encontrado o primeiro 1 de um bloco (1 ~ 0) e uma adigao quando é encontrado 0

fim do bloco (0 - 1).

i Para mostrar que esse esquema também funciona se o multiplicador for negativo, ob-

serve o seguinte. Seja X um ntimero negative na notago em complemento de dois:

Representacdo de X = (1x y_2%)-3--- 1%)

Ent&

, 0 valor de X pode ser expresso como:

310 ARQUITETURA E ORGANIZACAO DE COMPUTADORES Cap. 8

|

X= F (XX 27) + yg WF) Ht (xy x 2) + (xq 2°) (8.4)

Isso pode ser verificado aplicando o algoritmo aos mimeros da Tabela 8.2.

O bit mais a esquerda de X é 1, uma vez que X € negativo. Suponha que o bit de valor

0, mais & esquerda, esteja na posicao k. Entao, X é da forma:

Representagao de X= (111... 10x, x2 ++ - XyXo} (85)

Eo valor de X é

aE DMT gO KN EL + (Kg x2") (86)

Da Equacao 8.3 obtemos que:

yoy got ee

Reordenando os termos, temos:

ot

a ee (8.7)

Substituindo a Equacdo 8.7 na Equagio 8.6, obtemos:

X= DM gy WN $+ (xy x 2) (8.8)

Por fim, retornamos ao algoritmo de Booth. Tendo em vista a representacao de X (Equa-

40 8.5), é claro que todos os bits desde xy até o bit de valor 0 mais 8 esquerda so manipula-

dos de maneira adequada, pois produzem todos os termos da Equagio 88, exceto (-2'' 1), e

assim esto na forma correta. A medida que o algoritmo examina o bit 0 mais a esquerda e

encontra 0 préximo 1 (2**1), ocorre uma transigao 1 - 0 e é realizada uma subtragao (-2' * ').

Esse é 0 termo restante da Equacao 8.8.

Como exemplo, considere a multiplicagao de um ntimero M por (-6). Na representagao

em complemento de dois, com palavras de 8 bits, (-6) é representado como 11111010. Da

Equacio 8.4, sabemos que:

6-27 424 P4242? 42)

© que vocé pode verificar facilmente. Portanto,

M x (11111010) = M x (-2" +26 + 2° + 244.2942!)

Usando a Equagio 8.7, obtemos

Mx (11111010) = M x (-2? +2!)

que vocé pode verificar que também é igual a M x (-6). Finalmente, seguindo nossa linha

de raciocinio anterior, temos:

M x (11111010) = M x (-2° + 27-2!)

Podemos perceber que o algoritmo de Booth opera de acordo com 0 esquema anterior.

Ele efetua uma subtragéo quando o primeiro 1 é encontrado (1 - 0), uma adigao quando é

encontrada uma transi¢ao (0 — 1) e, finalmente, outra subtragio quando o primeiro 1 do pré-

ximo bloco de 1s é encontrado. Portanto, 0 algoritmo de Booth efetua menos adigdes e sub-

tragdes do que um algoritmo mais direto.

TT

Divisao

A divisio 6 de certa maneira, mais complexa que a multiplicagao, embora seja baseada

nos mesmos principios gerais. Como antes, a base para o algoritmo é a abordagem usada a0

efetuar a operagao com lépis e papel, e a operacdo envolve repetidas execugdes de adigio,

subtragao e deslocamento.

ARITMETICA COMPUTACIONAL 311

oooo1i101 + Quociente

Divisor » 1011 40010011 + Dividendo

toii

| Restos parciais, = ____, 9001110

oii]

psromomiateia

aoe

TOO + Resto

Figura 8.15 Divi

10 de ntimeros inteiros bindrios sem sinal. j

A Figura 8.15 mostra um exemplo de diviso de ntimeros inteiros binarios sem sinal.

instrutivo descrever o processo em detalhes. Primeiramente, os bits do dividendo so exami-

nados, da esquerda para a direita, até que se obtenha um conjunto de bits que represente um

ntimero maior ou igual ao divisor. Quando esse miimero ¢ encontrado, diz-se que o divisor

divide © ntimero. Enquanto isso nao ocorre, sao introduzidos 0s no quociente, da esquerda

para a direita. Quando esse evento ocorre, é colocado um 1 no quociente e o divisor € subtrai-

do do dividendo parcial. O resultado é conhecido como resto parcial. Desse ponto em diante,

' a divisdo segue um padrao ciclico. A cada ciclo, bits adicionais do dividendo séo anexados

ao resto parcial, até que o resultado seja maior ou igual ao divisor. Como antes, 0 divisor é

subtraido desse mimero, para produzir um novo resto parcial. © processo continua até que

todos os bits do dividendo tenham sido examinados.

i A Figura 8.16 mostra um algoritmo de maquina para 0 longo processo de divisio. O

divisor colocado no registrador M e o dividendo, no registrador Q. A cada paso, os regis-

tradores A e Q, juntos, sio deslocados um bit para a esquerda, M é subtraido de A, para de-

terminar se A divide o resto parcial!. Se dividir, entao o valor do bit Qy sera 1. Caso contrario,

' 0 valor de Qy seré 0 e 0 de M seré somado a A, para restaurar seu valor anterior. O contador

entdo é decrementado e proceso € repetido por 1 passos. Ao final, 0 quociente estard no

registrador Q e 0 resto, no registrador A.

Esse processo pode, com alguma dificuldade, ser estendido para ntimeros negativos.

Uma possivel abordagem para niimeros em complemento de dois é apresentada a seguir. Di-

versos exemplos dessa abordagem sao mostrados na Figura 8.17. O algoritmo pode ser des

crito como a seguir:

Carregar 0 divisor no registrador M e o dividendo nos registradores A e Q. O dividendo

deve ser expresso como um ntimero em complemento de dois com 21 bits. Por exemplo,

© ntimero O111 de 4 bits seria representado como 00000111 € o mimero 1001, como

11111001.

2. Deslocar o contetido dos registradores A e Q, juntos, um bit para a esquerda,

Essa é uma subtracio de ntimeros inteiros sem sinal. Se for requeride empréstimo de uma unidade para

‘obit mais significativo (bit ‘empresta-um’), o resultado sera negativo.

312 ARQUITETURA & ORGANIZACAO DE COMPUTADORES Cap. 8

3. Se Me A témo mesmo sinal, fazer A A—M; caso contrério, A A+ M.

4. A operacdo anterior ser bem-sucedida se o sinal de A for 0 mesmo, antes ¢ depois da operagio,

a. Se a operacao for bem-sucedida ou se (A = 0 € Q = 0), entdo faga Qo 1

b. Se a operagio ndo for bem-sucedida e se (A # 0 ou Q# 0), entio faga Qo Oe res-

taure o antigo valor de A (somando M a A).

5. Repita os passos 2 a4 enquanto houver bits a examinar em Q.

6. Ao final, o resto estaré em A. Se 0 divisor e o dividendo tiverem 0 mesmo sinal, 0 quo-

ciente estard em Q; caso contrario, 0 quociente correto é 0 complemento de dois do ni

mero armazenado em Q.

Iwicio

Nao. oa sim

an Qoe0

AeAtM

‘Quociente em

Resto em A.

| Figura 8.16 Fluxograma da divisdo de nimeros bindrios sem sinal.

Voce deve notar, a partir da Figura 8.17, que (-7) + @) e (7) + (-3) produzem restos di-

ferentes. Isso porque 0 resto € definido por:

ARITMETICA COMPUTACIONAL 313

' D=QxV+R

onde:

D = dividendo

Os resultados mostrados na Figura 8.17 séo coerentes com essa formula.

A Q M-=o011 A Q M-=1101

0000 ou Valor inicial 0000 o1it Valor inicial

0000 1110 Deslocar 0000 1110 Deslocar

01 Subtrair 1101 Adicionar

0000 1110 Restaurar 0000 110 Restaurar

0001 1100 Deslocar 0001 1100 Deslocar

1110 Subtrair 1110 Adicionar

0001 1100 Restaurar 0001 1100 Restaurar

0011 1000 Deslocar 0011 1000 Deslocar

0000 Subtrair 0000 Adicionar

0000 1001 Fazer Qo=1 0000 1001 Fazer Qo= 1

0001 0010 Deslocar 0001 0010 Deslocar

110 Subtrair 1110 Adicionar

' 0001 0010 Restaurar 0001 0010 Restaurar

(a) (7) +) (&) (7) + (-3)

A Q M=o011 A Q M-=1101

aa 1001 Valor inicial mi 1001 Valor inicial

un 010 Deslocar mi 0010 Deslocar

0010 Adicionar 0010 Subtrair

ait 0010 Restaurar mt 0010 Restaurar

110 0100 Deslocar 1110 0100 Deslocar

0001 Adicionar 0001 Subtrair

m0 0100 Restaurar 1110 0100 Restaurar

1100 1000 Deslocar 1100 1000 Deslocar

a1 Adicionar 111 Subtrair

win 1001 Fazer Qo 1 1001 Fazer Qo=1

wn 0010 Deslocar ait 0010 Deslocar

0010 Adicionar 0010 Subtrair

a 0010 Restaurar sues 010 Restaurar

(©) (-7) +3) (d) (-7) + (3)

Figura 8.17 _ Exemplos de divisio em complemento de dois.

314 ARQUITETURA £ ORGANIZACAO DE COMPUTADORES Cap. 8

8.4 REPRESENTACAO DE NUMEROS DE PONTO FLUTUANTE

Principios

Usando uma notacao de ponto fixo (por exemplo, complemento de dois), € possivel re-

presentar certa faixa de ntimeros inteiros positivos e negativos, centrada em 0. Esse formato

permite também a representagdo de ntimeros com parte fracionéria, bastando fixar uma po-

sigdo adequada para a virgula que separa a parte inteira e a parte fracionaria

Essa abordagem tem, entretanto, algumas limitagdes. Ela nao possibilita representar ntime-

ros muito grandes nem fragdes muito pequenas. Além disso, em uma divisdo de dois nimeros

muito grandes, a parte fracionéria do quociente pode ser perdida.

Para niimeros decimais, essa limitagao é superada com o uso da notagao cientifica. Por

‘exemplo, 976.000.000.000.000 pode ser representado como 9,76 x 10" e 0,0000000000000976,

como 9,76 x 10", A virgula 6 deslizada dinamicamente para uma posicao conveniente e é

usado um expoente de 10 adequado, para representar 0 mesmo valor original. Isso possibilita

expressar mimeros muito grandes e muito pequenos com poucos digitos.

‘A mesma abordagem pode ser usada para ntimeros binarios. Um ntimero pode ser re-

presentado na forma:

4M x BYE

Esse ntimero pode ser armazenado em uma palavra bindria, com trés campos:

‘+ Sinal: mais ou menos

* Mantissa M

* Expoente E

A base B é implicita e nao precisa ser armazenada porque € a mesma para todos os nti-

meros.

Os princfpios usados na representacao de ntimeros bindrios de ponto flutuante podem

set bem explicados por meio de um exemplo. A Figura 8.18a mostra um formato tipico de

niimeros de ponto flutuante de 32 bits. © bit mais & esquerda armazena o sinal do mimero (0

= positivo; 1 = negativo). O valor do expoente é armazenado nos 8 bits seguintes. A represen-

tagdo usada é conhecida como representacao polarizada. Um valor fixo, chamado de polari-

zacao, é subtraido ao valor desse campo para se obter o verdadeiro valor do expoente

Tipicamente, a polarizacao é igual a (2! -1), onde k é 0 mimero de bits do expoente bindrio.

Nesse caso, 0 campo de 8 bits pode conter mimeros de 0 a 255. Com uma polarizacao igual a

127, os verdadeiros valores dos expoentes esto compreendidos na faixa de ~127 a +128. Nesse

exemplo, considera-se que a base ¢ 2

A Tabela 8.2 mostra a representagao polarizada para ntimeros inteiros de 4 bits. Note

que, se 0s bits de uma representacdo polarizada forem tratados como mimeros inteiros sem

sinal, a magnitude relativa dos ntimeros ndo mudard. Por exemplo, nas duas representacdes,

tanto polarizada quanto sem sinal, o maior ntimero é 1111 e o menor mimero, 0000. Isso ndo

& verdadeiro para as representacGes sinal-magnitude, em complemento de dois e em comple-

mento de um. Uma vantagem da representagio polarizada é que, para fins de comparacao,

nuimeros de ponto flutuante nao negatives podem ser tratados como ntimeros inteiros.

ARITMETICA COMPUTACIONAL 315,

1001 00010000000000000000

10010011 101000100000000000000:

01101011 101000100000000000000

01101011 10100010000000000000000

x xX x

(b) Exemplos

Figura 8.18 Formato tipico da representago de ntimeros de ponto flutuante de 32 bits.

A parte final da palavra (23 bits nesse caso) é a mantissa. Note que um mesmo niimero

de ponto flutuante pode ser expresso de muitas maneiras. Por exemplo, as seguintes repre-

sentagies sdo equivalentes, em que a mantissa é expressa na forma bindria:

0,110 x2°

110 x2?

0,010 x 2°

Para simplificar as operacdes sobre mimeros de ponto flutuante, tipicamente é requeri-

do que esses ntimeros estejam normalizados. No nosso exemplo, um ntimero normalizado di-

ferente de zero tem a forma:

40,1 bbb... bx 2

onde b é um digito bindrio (0 ou 1). Isso implica que o bit mais & esquerda da mantissa € sem-

pre 1. Por isso, nao é necessério armazenar esse bit, pois ele é implicito. Portanto, o campo de

23 bits é usado para armazenar uma mantissa de 24 bits com valor entre 0,5 ¢ 1,0.

A Figura 8.18 mostra alguns exemplos de nimeros armazenados nesse formato. Note

as seguintes caracteristicas:

* Osinal é armazenado no primeiro bit da palavra.

* O primeiro bit da mantissa verdadeira é sempre 1 e ndo precisa ser armazenado no

‘campo de mantissa.

* Ovalor 127 6 adicionado ao expoente verdadeiro para ser armazenado no campo de

expoente.

+ Abase 62.

A Figura 8.19 indica a faixa de mimeros que podem ser representados em uma palavra

de 32 bits, usando essa representagio. Na notacio em complemento de dois, podem ser re-

presentados todos os ntimeros inteiros de -2°! a 25-1, ou seja, um total de 2°? ntimeros dis-

tintos. No formato de ponto flutuante da Figura 8.18, ntimeros nas seguintes faixas podem

ser representados:

* Ntimeros negativos entre ~(1 - 2%) x 2128 e-0,5 x 217

+ Ntimeros positivos entre 0,5 x 217 e (1 - 2%) x 2128

3116 —ARQUITETURA E ORGANIZAGAO DE COMPUTADORES Cap. 8

yeuix0y Ua sranquasaudas soxaWNN 6L°8 BINH

Sq Ze ap O94

equeniny oiuod op sou0wnny (4)

SaieLDD sei * eZ mEX90 0 yy b*S0- eas * (ve 2 — W-

op Bey R 5 A J

\ y

Uy yr —+y~ A$ Ay

songisod sosownu slonpquoso.dos sjengiuasesdes sonneBou

wa moyZeAQ SoAN|s0d SOx0WIDN, J x sonneBeu sooUNN SOsOWIDU We Mo1/12A0

songjsod sosewunu ——_sonneBeu sosouunu

we moyepun wie moyepuny

sjop ep ojuaWwejduwos we soxjeru! SOLAN,

rie 0 ie

‘sosownu op e104 ~ ~

UH

slongiuasasda Sos}@qU! SOsOWUNN

ARITMETICA COMPUTACIONAL 317

Cinco regides na reta de mimeros nio estdo incluidas nessas faixas:

‘+ Ntimeros negativos menores que —(1 - 2) x 278, correspondendo a overflow em

nuimeros negativos

* Niimeros negativos maiores que -0,5 x 2-1”, correspondendo a underflow em ntime-

ros negativos

* Zero

* Ntimeros positivos menores que 0,5 x 2-1”, correspondendo a underflow em nime-

10s positivos

+ Niimeros positivos maiores que (1 ~ 2%) x 2!28, correspondendo a overflow em nui-

, meros positivos

Essa representacdo, tal como apresentada, ndo acomoda o valor 0. Entretanto, como

veremos, representages de ponto flutuante na verdade incluem um padrao de bits espe-

cial para designar zero. Em uma operagdo aritmética, ocorre overflow quando a magnitude

do resultado é maior do que o maior valor que pode ser expresso com expoente igual a

128 (por exemplo, 217° x 2'00 = 2229), Ocorre underflow quando a magnitude é muito peque-

na (por exemplo, 2-1" x 2-1 = 2-29). A ocorréncia de underflow € um problema menos

sério, pois 0 resultado geralmente pode ser aproximado satisfatoriamente por 0.

E importante observar que a notagao de ponto flutuante nao possibilita representar um

ntimero maior de valores distintos. © mimero maximo de valores distintos que podem ser

representados com 32 bits continua sendo 2. Entretanto, esses mimeros so divididos em

duas faixas, uma positiva e uma negativa.

Veja também que os ntimeros representados na notacao de ponto flutuante nao esto

igualmente distribufdos ao longo da reta de ntimeros, como ¢ 0 caso de ntimeros de ponto

fixo. Existe uma quantidade maior de valores representaveis prdximo a origem, e essa quan-

tidade diminui com a distancia origem, como é mostrado na Figura 8.20. Esse é um dos pro-

blemas da aritmética de ponto flutuante: muitos célculos produzem resultados nao exatos,

que tém de ser arredondados para o valor mais préximo que a notacio possibilita representar.

No tipo de formato mostrado na Figura 8.18, existe um conflito entre a faixa de valores

€ a preciso dos ntimeros representaveis. © exemplo mostra que s4o reservados 8 bits para o

expoente e 23 bits para a mantissa. Se aumentarmos o ntimero de bits do expoente, expandi-

mos a faixa de valores representdveis, Entretanto, como apenas um ntimero fixo de valores

distintos pode ser expresso, reduzimos a densidade desses niimeros, o que diminui a preci-

so. A tinica maneira de aumentar tanto 0 alcance quanto a preciso é usar um maior ntimero

de bits. Por isso, a maioria dos computadores oferece, pelo menos, ntimeros de preciso sim-

ples e ntimeros de precisdo dupla. Por exemplo, um formato de precisao simples pode ter 32

bits e um formato de preciso dupla, 64 bits.

WATE

HTT

° a nx2 nea

Figura 8.20 Densidade de ntimeros de ponto flutuante.

318 ARQUITETURA E ORGANIZAGAO DE COMPUTADORES Cap. &

Portanto, existe um conilito entre o ntimero de bits reservados para o expoente e para a

mantissa. Essa questao é, porém, ainda mais complicada. A base subentendida para o expoen-

te nao precisa, necessariamente, ser 2. Na arquitetura IBM $/390, por exempllo, € usada a base

16, O formato é composto de um expoente de 7 bits e uma mantissa de 24 bits, Assim, por

exemplo, temos:

0,11010001 x 21°! = 0,11010001 x 16"

nta 5, em vez de 20.

A vantagem de usar um expoente maior é que se pode representar uma faixa maior de

mimeros, utilizando o mesmo nimero de bits para o expoente. Lembre-se, entretanto, de que

© mtimero de valores distintos que podem ser representados permanece o mesmo. Portanto,

para um formato de tamanho fixo, uma base de expoente maior permite um maior alcance

(faixa de valores) ao custo de uma menor precisio.

onde o expoente armazenado repr.

Padrao IEEE para representacao de numeros binarios de ponto flutuante

A mais importante representago de ponto flutuante é definida no padrao IEEE 754

(IEEE, 1985). Esse padrao foi desenvolvido para facilitar a portabilidade de programas entre

processadores, além de encorajar 0 desenvolvimento de programas de processamento numé-

rico sofisticados. Ele tem sido largamente adotado, sendo usado em quase todos os processa-

dores e co-processadores aritméticos modernos.

© padrao IEEE define um formato simples de 32 bits e um formato duplo de 64 bits

(Figura 8.21), com expoentes de 8 e 11 bits, respectivamente. A base implicita é 2. Na adiga

0 padrao define dois formatos estendidos, simples e duplo, cujo formato exato é dependente

de implementagao. Os formatos estendidos incluem bits adicionais no expoente (alcance es-

tendido) e na mantissa (precisdo estendida). Eles so usados para célculos intermediérios. O

uso desses formatos diminui a chance de o resultado final ser contaminado por excessivo erro

de arredondamento, uma vez que fornecem maior precis4o. Além disso, como permite

maior alcance, também diminui a chance de overflow em operagées intermediarias, 0 que po-

deria abortar uma computagao cujo resultado final seria representavel no formato

Uma motivagao adicional para 0 formato estendido simples é que ele possui alguns dos be-

neficios do formato duplo, sem incorrer na penalidade de tempo normalmente associada a

uma precisdo mais alta. A Tabela 8.3 resume as caracterfsticas dos quatro formatos.

Bit de

Eee abit 2a bits

Expoente

E Fragdo

(0) Formato simples

Bie ‘bits 52bits

Ng Expoente

polarizado Fragso

(&) Formato duplo

Fgura 8.21 Formatos do padrao IEI

ARITMETICA COMPUTACIONAL 319.

Nem todos os padrées de bits do formato IEEE sao interpretados da maneira usual; al-

guns so usados para representar valores especiais. A Tabela 8.4 indica os valores atribuidos

a virios padrées de bits. Os casos em que o expoente ¢ totalmente preenchido com zeros (0)

ou com uns (255 no formato simples e 2047 no formato duplo) definem valores especiais. As

seguintes classes de ntimeros sdo representadas:

* Seo intervalo de valores do expoente é de 1 a 254 no formato simples ou de 1a

2.046 no formato duplo, sao representados ntimeros de ponto flutuante normaliza-

dos, diferentes de zero. O expoente é polarizado, de modo que a faixa de valores de

expoente seja ~126 a +127 no formato simples e 1022 a +1023 no formato duplo. Um

ntimero normalizado tem o bit 1 A esquerda da virgula fracionéria igual a 1; esse bit

6 implicit, o que dé uma mantissa (chamada fragio na descricao do padro IEEE)

efetiva de 24 bits no formato simples ou de 53 bits no formato duplo.

* Um expoente igual a zero junto com uma fragao igual a zero representa zero, posi-

tivo ou negativo, dependendo do bit de sinal. Como mencionamos anteriormente, €

litil ter uma representagao para o valor exato de 0.

* Um expoente totalmente preenchido com uns junto com uma fracao igual a zero re-

presenta infinito, positivo ou negativo, dependendo do bit de sinal. E também muito

itil ter uma representacdo para infinito. Isso possibilita ao usudrio decidir entre tra-

tar overflow como uma condigao de erro ou propagar esse valor (dando prossegui-

mento a execugdo do programa).

+ Um expoente de valor zero junto com uma fracdo diferente de zero representa um

ntimero nao-normalizado. Nesse caso, o bit a esquerda da virgula fracionaria é zero

e 0 expoente verdadeiro é -126 no formato simples ou —1022 no formato duplo. O

ntimero € positivo ou negativo conforme o bit de sinal.

+ Um expoente totalmente preenchido com uns junto com uma fragdo diferente de

zero representa o valor NaN (Not a Number), que significa Nao é um miimero, e 6 usado

; para sinalizar diversas condigdes de excecao,

Tabela 8.3 Parametros do formato IEEE 754

Formato

Parametro ‘Simples _ Simples estendido Duplo Duplo estendido

Tamanho da palavra (bils) 32 = oa =

‘Tamanho do expoente (bits) 8 21 u 215

Polarizagio do expoente 17 Nao especificado 1023 Nao especificado

Expoente maximo 17 21023 1023 216383,

Expoente minimo 126 s-1022 =1022 16382

Faixa de ntimeros (base 10) 10°, 10° Naoespecificado. 10%, 10°** Nao especificado

Tamanho da mantissa (bits)” 23 231 52 263

Neimero de expoentes 254 Nao especificado 2046 Nao especificado

Nuimero de fragdes a Nao especificado 2 Nao especificado

Neimero de valores 1982" Naoespecificado 1,992" _ Nilo especificado

Nao inclu o bit impli

O significado de ntimeros nao-normalizados e de NaNs é discutido na Secao 8.5.

Anda mungkin juga menyukai

- Bases Fisiológicas Do Comportamento e Da CogniçãoDokumen12 halamanBases Fisiológicas Do Comportamento e Da Cogniçãoitamar1571% (7)

- Contos de Fadas Na ContemporaneidadeDokumen244 halamanContos de Fadas Na Contemporaneidadeitamar1550% (2)

- Toxicomania PDFDokumen12 halamanToxicomania PDFitamar15Belum ada peringkat

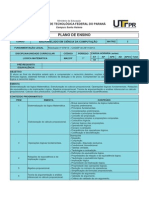

- Planos de Ensino Lógica MatemáticaDokumen4 halamanPlanos de Ensino Lógica Matemáticaitamar15Belum ada peringkat

- A Medicaliza Ão Da VidaDokumen114 halamanA Medicaliza Ão Da Vidaitamar15Belum ada peringkat

- Modelo TCLE Maior OKDokumen2 halamanModelo TCLE Maior OKitamar15Belum ada peringkat