Alu

Diunggah oleh

Kristavilla OlavianoHak Cipta

Format Tersedia

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniHak Cipta:

Format Tersedia

Alu

Diunggah oleh

Kristavilla OlavianoHak Cipta:

Format Tersedia

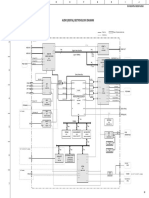

Tele 2060

A Simple Processor Architecture

Register 1

Register 2

Input

Register 7

Decoder B Select Multiplexer Multiplexer A Select

B Bus A Bus

Destination

Select ALU

Function

S Z V C Select

Shifter Shift

Select

Output

Martin B.H. Weiss

Arithmetic-Logic Unit and Processor Design - 1 University of Pittsburgh

Tele 2060

ALU

Performs Arithmentic Functions

Performs Logic Functions

Function is Selected by Control

Status Bits

C - Carry

V - Overflow

Z = 1 If Resultant Contains All Zeros

S - Sign Bit of the Result

Decoder Selects Destination for the Resultant

Martin B.H. Weiss

Arithmetic-Logic Unit and Processor Design - 2 University of Pittsburgh

Tele 2060

ALU

Inputs

Operands

Input Carry

Operation Select

Add

Subtract

AND

OR

XOR

Mode (Arithmetic or Logic) Select

Outputs

Resultant

Output Carry

Martin B.H. Weiss

Arithmetic-Logic Unit and Processor Design - 3 University of Pittsburgh

Tele 2060

ALU Function Table

Operation Select

S2 S1 S0 Cin Operation Function

0 0 0 0 F=A Transfer A

0 0 0 1 F=A+1 Increment A

0 0 1 0 F=A+B Add A and B

0 0 1 1 F=A+B+1 Add A and B With Carry

0 1 0 0 F=A+B Add A and Ones Compement of B

0 1 0 1 F=A+B+1 Subtract B From A

0 1 1 0 F=A-1 Decrement A

0 1 1 1 F=A Transfer A

1 0 0 0 F=AB AND

1 0 1 0 F=A+B OR

1 1 0 0 F=A XOR B Exclusive OR

1 1 1 0 F=A Complement

Martin B.H. Weiss

Arithmetic-Logic Unit and Processor Design - 4 University of Pittsburgh

Tele 2060

ALU Components

Arithmetic

Parallel Add

One Full Adder per Bit

Selection Logic

Logic

Gates

Multiplexer

Martin B.H. Weiss

Arithmetic-Logic Unit and Processor Design - 5 University of Pittsburgh

Tele 2060

Circuit for Arithmetic Component

Cin

S0

S1

A1 X1 C1

Full F1

B1 Adder

Y1

A2 X2 C2

Full F2

B2 Adder

Y2

Martin B.H. Weiss

Arithmetic-Logic Unit and Processor Design - 6 University of Pittsburgh

Tele 2060

Circuit for Logic Component

S0

S1

An

MUX Fn

Bn

Martin B.H. Weiss

Arithmetic-Logic Unit and Processor Design - 7 University of Pittsburgh

Tele 2060

Internal Structure of ALU

Cn-1

An

Bn Arithmetic

Stage

Multiplexer Fn

Logic

Stage

S0

S1

S2

Martin B.H. Weiss

Arithmetic-Logic Unit and Processor Design - 8 University of Pittsburgh

Tele 2060

Shifter

General

Extension of Shift Register Circuit is Possible

This Requires Several Clock Pulses

This is Time Consuming

Alternate Approach (Figure 7-18, p. 246 of Mano)

Use Multiplexers

Wire to Cause Shift Effect

Control Determines Nature of Shift

Thus, a Single Clock Cycle is Used

Martin B.H. Weiss

Arithmetic-Logic Unit and Processor Design - 9 University of Pittsburgh

Tele 2060

Control Unit Requirements

MUX A Selector

MUX B Selector

ALU Operation Selector

Shift Selector

Destination Selector

Martin B.H. Weiss

Arithmetic-Logic Unit and Processor Design - 10 University of Pittsburgh

Tele 2060

Control Word

Number and Organization of Bits Required to Control ALU

Bit Requirements

A: A Bus Select (Seven Registers Plus Input): 3 bits

B: B Bus Select (Seven Registers Plus Input): 3 bits

D: Destination Select (Seven Registers): 3 bits

F: ALU Control (Four bits)

H: Shift Control (Three bits)

TOTAL = 16 bits

Thus, 16 Bits Can Be Used to Perform All Microoperations

A B D F H

Martin B.H. Weiss

Arithmetic-Logic Unit and Processor Design - 11 University of Pittsburgh

Tele 2060

Control Word Encoding

Operation (F)

Code Cin = 0 Cin = 1 A B D H

0 0 0 F=A F=A+1 Input Input None No Shift

0 0 1 F=A+B F=A+B+1 R1 R1 R1 SHL

0 1 0 F=A+B F=A+B+1 R2 R2 R2 SHR

0 1 1 F=A-1 F=A R3 R3 R3 Bus=0

1 0 0 F=AB R4 R4 R4

1 0 1 F=A+B R5 R5 R5 ROL

1 1 0 F=A XOR B R6 R6 R6 ROR

1 1 1 F=A R7 R7 R7

Martin B.H. Weiss

Arithmetic-Logic Unit and Processor Design - 12 University of Pittsburgh

Tele 2060

Microoperations and Microprograms

Example Microoperation

R1 R2 - R3

Symbolically: R2,R3,R1,F=A-B,No Shift

Control Word = 010 011 001 0101 000 = 4CA8 (H)

Clearly, Many Microoperations Are Possible

Control Memory

Location of Available Microoperations

Width of Control Memory = Control Word

Microprograms Can be Written Using a Sequence of

Microoperations

Martin B.H. Weiss

Arithmetic-Logic Unit and Processor Design - 13 University of Pittsburgh

Anda mungkin juga menyukai

- Norton Report 2013Dokumen28 halamanNorton Report 2013Kristavilla OlavianoBelum ada peringkat

- 3.11 Evaluation of Job Related Hazards and Development of Safety ProceduresDokumen16 halaman3.11 Evaluation of Job Related Hazards and Development of Safety ProceduresKristavilla OlavianoBelum ada peringkat

- Vertical and Horizontal Motion ProblemsDokumen41 halamanVertical and Horizontal Motion ProblemsKristavilla OlavianoBelum ada peringkat

- Victims of Cybercrime Attacks Cybercrime Victims More Likely To BeDokumen2 halamanVictims of Cybercrime Attacks Cybercrime Victims More Likely To BeKristavilla OlavianoBelum ada peringkat

- 2012 Math Challenge-Individual Finals (GR I - VI)Dokumen12 halaman2012 Math Challenge-Individual Finals (GR I - VI)Kristavilla OlavianoBelum ada peringkat

- VanityDokumen3 halamanVanityPeter El RojoBelum ada peringkat

- Writing Your First Visual Basic ProgramDokumen23 halamanWriting Your First Visual Basic ProgramKristavilla OlavianoBelum ada peringkat

- Components of Culture ReportedDokumen13 halamanComponents of Culture ReportedKristavilla OlavianoBelum ada peringkat

- Safety PrecautionDokumen1 halamanSafety PrecautionKristavilla OlavianoBelum ada peringkat

- Boolean AlgebraDokumen4 halamanBoolean AlgebraS MohiuddinBelum ada peringkat

- Assignment 231 Engg EconomyDokumen1 halamanAssignment 231 Engg EconomyKristavilla OlavianoBelum ada peringkat

- 4-bit ALU Design and ImplementationDokumen1 halaman4-bit ALU Design and ImplementationKristavilla OlavianoBelum ada peringkat

- The Instruction Set SummaryDokumen6 halamanThe Instruction Set SummaryRidwan Sukma PribadiBelum ada peringkat

- Summer Reading List 2016Dokumen3 halamanSummer Reading List 2016Kristavilla OlavianoBelum ada peringkat

- PNPACAT 2015 QUALIFIED EXAMINEESDokumen427 halamanPNPACAT 2015 QUALIFIED EXAMINEESKristavilla OlavianoBelum ada peringkat

- PNPACAT 2015 QUALIFIED EXAMINEESDokumen427 halamanPNPACAT 2015 QUALIFIED EXAMINEESKristavilla OlavianoBelum ada peringkat

- Pu1473410272 PDFDokumen1 halamanPu1473410272 PDFKristavilla OlavianoBelum ada peringkat

- TocDokumen6 halamanTocKristavilla OlavianoBelum ada peringkat

- Debug TutorialDokumen20 halamanDebug TutorialHsm SsmBelum ada peringkat

- 8086 - Instruction SetDokumen1 halaman8086 - Instruction Setveera100% (2)

- Avt 2015 029Dokumen11 halamanAvt 2015 029Kristavilla OlavianoBelum ada peringkat

- Periodic TableDokumen1 halamanPeriodic TablejohnfitzsmithBelum ada peringkat

- Operating System Structures Course OutlineDokumen24 halamanOperating System Structures Course OutlineKristavilla OlavianoBelum ada peringkat

- 74181Dokumen7 halaman74181Avneesh KarBelum ada peringkat

- 372 5Dokumen5 halaman372 5Phillip TaylorBelum ada peringkat

- TocDokumen6 halamanTocKristavilla OlavianoBelum ada peringkat

- Pricelist LettersizeDokumen3 halamanPricelist LettersizeKristavilla OlavianoBelum ada peringkat

- Debug TutorialDokumen20 halamanDebug TutorialHsm SsmBelum ada peringkat

- 372 5Dokumen5 halaman372 5Phillip TaylorBelum ada peringkat

- Shoe Dog: A Memoir by the Creator of NikeDari EverandShoe Dog: A Memoir by the Creator of NikePenilaian: 4.5 dari 5 bintang4.5/5 (537)

- Grit: The Power of Passion and PerseveranceDari EverandGrit: The Power of Passion and PerseverancePenilaian: 4 dari 5 bintang4/5 (587)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceDari EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RacePenilaian: 4 dari 5 bintang4/5 (890)

- The Yellow House: A Memoir (2019 National Book Award Winner)Dari EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Penilaian: 4 dari 5 bintang4/5 (98)

- The Little Book of Hygge: Danish Secrets to Happy LivingDari EverandThe Little Book of Hygge: Danish Secrets to Happy LivingPenilaian: 3.5 dari 5 bintang3.5/5 (399)

- On Fire: The (Burning) Case for a Green New DealDari EverandOn Fire: The (Burning) Case for a Green New DealPenilaian: 4 dari 5 bintang4/5 (73)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeDari EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifePenilaian: 4 dari 5 bintang4/5 (5794)

- Never Split the Difference: Negotiating As If Your Life Depended On ItDari EverandNever Split the Difference: Negotiating As If Your Life Depended On ItPenilaian: 4.5 dari 5 bintang4.5/5 (838)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureDari EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FuturePenilaian: 4.5 dari 5 bintang4.5/5 (474)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryDari EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryPenilaian: 3.5 dari 5 bintang3.5/5 (231)

- The Emperor of All Maladies: A Biography of CancerDari EverandThe Emperor of All Maladies: A Biography of CancerPenilaian: 4.5 dari 5 bintang4.5/5 (271)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreDari EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You ArePenilaian: 4 dari 5 bintang4/5 (1090)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyDari EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyPenilaian: 3.5 dari 5 bintang3.5/5 (2219)

- Team of Rivals: The Political Genius of Abraham LincolnDari EverandTeam of Rivals: The Political Genius of Abraham LincolnPenilaian: 4.5 dari 5 bintang4.5/5 (234)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersDari EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersPenilaian: 4.5 dari 5 bintang4.5/5 (344)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaDari EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaPenilaian: 4.5 dari 5 bintang4.5/5 (265)

- Rise of ISIS: A Threat We Can't IgnoreDari EverandRise of ISIS: A Threat We Can't IgnorePenilaian: 3.5 dari 5 bintang3.5/5 (137)

- The Unwinding: An Inner History of the New AmericaDari EverandThe Unwinding: An Inner History of the New AmericaPenilaian: 4 dari 5 bintang4/5 (45)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Dari EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Penilaian: 4.5 dari 5 bintang4.5/5 (119)

- Her Body and Other Parties: StoriesDari EverandHer Body and Other Parties: StoriesPenilaian: 4 dari 5 bintang4/5 (821)

- VITRA Ophthalmic Photodisruptor Service ManualDokumen71 halamanVITRA Ophthalmic Photodisruptor Service ManualMatteo MassiBelum ada peringkat

- Series 72 Modutrol IV™ Motors: FeaturesDokumen12 halamanSeries 72 Modutrol IV™ Motors: FeaturesEzequias RoquimBelum ada peringkat

- MSendur II UPS Standby Power AppsDokumen4 halamanMSendur II UPS Standby Power AppsFirdaus PratamaBelum ada peringkat

- B - 4178972 - Eye Wash Shower SolutionDokumen1 halamanB - 4178972 - Eye Wash Shower SolutionkarehmanBelum ada peringkat

- Makalah KomputerDokumen16 halamanMakalah KomputerAbubakar AdeniBelum ada peringkat

- Tensan 4109A one-component epoxy adhesive technical data sheetDokumen1 halamanTensan 4109A one-component epoxy adhesive technical data sheetthe hoangBelum ada peringkat

- CMOS Inverter LayoutDokumen2 halamanCMOS Inverter LayoutRen ValerosoBelum ada peringkat

- Flashing Alarm Annunciator Units With Signal Storage FSB 24/16-24 - P USBDokumen4 halamanFlashing Alarm Annunciator Units With Signal Storage FSB 24/16-24 - P USBm khBelum ada peringkat

- CMOS Interview QuestionsDokumen3 halamanCMOS Interview QuestionsAjay G BellamBelum ada peringkat

- MCQ On Led and LCD TVDokumen3 halamanMCQ On Led and LCD TVBhavishya Sharma09Belum ada peringkat

- MT6768 LPDDR4x Internal ProjectDokumen31 halamanMT6768 LPDDR4x Internal Projectpc partnerBelum ada peringkat

- Integral PaperDokumen7 halamanIntegral PaperASHISHBelum ada peringkat

- Standards Specifications For Instrument CablesDokumen10 halamanStandards Specifications For Instrument CablesAmmar AltamimyBelum ada peringkat

- Comparison of Outer Rotor Radial Flux and Axial Flux PM Motors For CMG ApplicationDokumen6 halamanComparison of Outer Rotor Radial Flux and Axial Flux PM Motors For CMG ApplicationsosiBelum ada peringkat

- DC Motors: - Construction Very Similar To A DC GeneratorDokumen35 halamanDC Motors: - Construction Very Similar To A DC GeneratorDeepak Ganachari100% (1)

- Arjuna Chua Reflection For Webinars Plant VisitDokumen9 halamanArjuna Chua Reflection For Webinars Plant VisitArjuna ChuaBelum ada peringkat

- 22F-A2P5N113 Technical DataDokumen10 halaman22F-A2P5N113 Technical DataSpartan WarriorBelum ada peringkat

- CET Power - MEDIA 230vac Datasheet - V1.2Dokumen2 halamanCET Power - MEDIA 230vac Datasheet - V1.2YANdalfBelum ada peringkat

- Lab 1: Study of Gates & Flip-Flops: - Digital IC Trainer KitDokumen81 halamanLab 1: Study of Gates & Flip-Flops: - Digital IC Trainer KitforghanBelum ada peringkat

- CT - IMB - 36 To 300 KVDokumen12 halamanCT - IMB - 36 To 300 KVRaharjo YakinBelum ada peringkat

- RP 08 - Measuring EMF of An Electrochemical CellDokumen4 halamanRP 08 - Measuring EMF of An Electrochemical CellASLAM HANIEFBelum ada peringkat

- Block Diagrams: Audio (Digital) Section Block DiagramDokumen19 halamanBlock Diagrams: Audio (Digital) Section Block DiagramAran Jed HostelleroBelum ada peringkat

- 1 Product Category SpecialDokumen16 halaman1 Product Category SpecialOmar SaeedBelum ada peringkat

- Seisgram2K PQL Datawiewer Winscp Teraterm: Monitoring The EarthDokumen2 halamanSeisgram2K PQL Datawiewer Winscp Teraterm: Monitoring The EarthLuna FitrianaBelum ada peringkat

- Sample Form Inspection ChecklistDokumen5 halamanSample Form Inspection Checklistadolf001Belum ada peringkat

- Design and Implementation of Digital Code Lock Using VHDLDokumen24 halamanDesign and Implementation of Digital Code Lock Using VHDLNichanametla Sukumar83% (6)

- Simulink® Control Design™Dokumen76 halamanSimulink® Control Design™Prabhakar SinghBelum ada peringkat

- 6ES72141AG400XB0 Datasheet enDokumen9 halaman6ES72141AG400XB0 Datasheet enguevbaBelum ada peringkat

- Digital to Analog Conversion ExplainedDokumen37 halamanDigital to Analog Conversion ExplainedECEHOD SECBelum ada peringkat

- TRSS Overview Presentation - SCHNEIDERDokumen99 halamanTRSS Overview Presentation - SCHNEIDERDante FalconBelum ada peringkat