Ec 412

Diunggah oleh

Gautami SumanJudul Asli

Hak Cipta

Format Tersedia

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniHak Cipta:

Format Tersedia

Ec 412

Diunggah oleh

Gautami SumanHak Cipta:

Format Tersedia

EC 412 LOW POWER VLSI DESIGN L T P C

3 0 0 3

UNIT-I POWER DISSIPATION IN CMOS 9

Sources of power DissipationPhysics of power dissipation in MOSFET devices, Power dissipation in CMOS, Low power

VLSI design limits.

UNIT-II LOW POWER ADDERS AND MULTIPLIERS 9

Standard adder cells, CMOS adder architectures, BiCMOS adder, overview and types of Multipliers- Braun Multiplier, Baugh

Wooley Multiplier, Wallace Tree Multiplier, Booth Multiplier.

UNIT-III SYNTHESIS FOR LOW POWER 9

Behavioural level transforms-Algorithm using First Order, second, Mth Order Differences-Parallel Implementation Pipelined

Implementation- Logic level optimization Technology dependent and Independent -Circuit level- Static, Dynamic, PTL,

DCVSL, PPL.

UNIT-IV LOW POWER STATIC RAM ARCHITECTURES 9

Organization of a static RAM, MOS static RAM memory cell, Banked organization of SRAMs, Reducing voltage swings on

bit lines, Reducing power in the write diver circuits, Reducing power in sense amplifier circuits.

UNIT-V LOW ENERGY COMPUTING USING ENERGY RECOVERY 9

TECHNIQUES

Energy dissipation in transistor channel using an RC model, Energy recovery circuit design, Designs with partially reversible

logic, Supply clock generation.

L:45 T:0 T:45 PERIODS

TEXT BOOKS

1. K.Roy and S.C. Prasad, Low Power CMOS VLSI Circuit Design, Wiley, 2000.

2. K.S. Yeo and K.Roy, Low-Voltage, Low-Power VLSI Subsystems, Tata McGraw-Hill, 2004.

REFERENCES

1. DimitriosSoudris, ChirstianPignet and Costas Goutis, Designing CMOS Circuits for Low Power, Kluwer, 2009

[Unit II-IV]

2. James B. Kuo and Shin - Chia Lin, Low voltage SOI CMOS VLSI Devices and Circuits, John Wiley and Sons,

2001 [Unit III,IV]

3. J.B Kuo and J.H Lou, Low voltage CMOS VLSI Circuits, Wiley, 1999

[ Unit II]

COURSE OUTCOMES

At the end of the course the student will be able to

Evaluate the power dissipation in the CMOS circuits.

Design the of low power arithmetic circuits.

Synthesize the low power circuits in various levels of transformations.

Describe the organization of low power Static RAM architectures.

Analyze the energy recovery techniques for computing low power in circuit design.

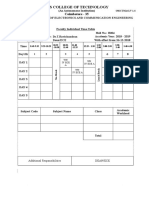

COURSE OUTCOMES MAPPING WITH PROGRAMME OUTCOMES

PO-a PO-b PO-c PO-d PO-e PO-f PO-g PO-h PO-i PO-j PO-k PO-l PSO1 PSO2 PSO3

CO1 H M H

CO2 M M

CO3 M M

CO4 L M L

CO4 M L

ACADEMIC COORDINATOR DEAN/ECE

Anda mungkin juga menyukai

- Ge8075 Intellectual Property RightsDokumen1 halamanGe8075 Intellectual Property RightsGautami SumanBelum ada peringkat

- Datapath Logic CellsDokumen19 halamanDatapath Logic CellsGautami SumanBelum ada peringkat

- Zero Shot LearningDokumen1 halamanZero Shot LearningGautami SumanBelum ada peringkat

- Combinational Logic CellsDokumen9 halamanCombinational Logic CellsGautami SumanBelum ada peringkat

- Year Reg No Students Name: Mentor - Mentees list-Gautami.A, AP/ECE - 9952253912Dokumen9 halamanYear Reg No Students Name: Mentor - Mentees list-Gautami.A, AP/ECE - 9952253912Gautami SumanBelum ada peringkat

- 16EC454 ASIC Design SyllabusDokumen2 halaman16EC454 ASIC Design SyllabusGautami SumanBelum ada peringkat

- Addressing Mode PicDokumen7 halamanAddressing Mode PicJustin LivingstonBelum ada peringkat

- Course Coordinators New - Even 18-19Dokumen1 halamanCourse Coordinators New - Even 18-19Gautami SumanBelum ada peringkat

- 1566NLDokumen106 halaman1566NLGautami SumanBelum ada peringkat

- Research Article: Gopinath P.G ., Anitha V.R ., Aruna Mastani SDokumen5 halamanResearch Article: Gopinath P.G ., Anitha V.R ., Aruna Mastani SGautami SumanBelum ada peringkat

- Texperia Miniproject-II Ece ADokumen1 halamanTexperia Miniproject-II Ece AGautami SumanBelum ada peringkat

- 14EC046Dokumen5 halaman14EC046Gautami SumanBelum ada peringkat

- Cgpa 3rd Sem II ADokumen1 halamanCgpa 3rd Sem II AGautami SumanBelum ada peringkat

- Faculty and Placement DetailsDokumen8 halamanFaculty and Placement DetailsGautami SumanBelum ada peringkat

- Antenna SyllabusDokumen2 halamanAntenna SyllabusGautami SumanBelum ada peringkat

- Attendance Vlsi-A SectionDokumen12 halamanAttendance Vlsi-A SectionGautami SumanBelum ada peringkat

- Individual TT 2018 19 OddDokumen69 halamanIndividual TT 2018 19 OddGautami SumanBelum ada peringkat

- Teacher's Manual-Session Plan: Mapping of Learning Outcome With PODokumen22 halamanTeacher's Manual-Session Plan: Mapping of Learning Outcome With POGautami SumanBelum ada peringkat

- 373427j PDFDokumen89 halaman373427j PDFjace112Belum ada peringkat

- New Syllabus Group VII Services UpdatedDokumen5 halamanNew Syllabus Group VII Services UpdatedSaravana PandiyanBelum ada peringkat

- Iot QuizDokumen1 halamanIot QuizGautami SumanBelum ada peringkat

- EceDokumen3 halamanEceNandha KumarBelum ada peringkat

- EceDokumen20 halamanEceGautami SumanBelum ada peringkat

- New Syllabus Group VII Services UpdatedDokumen5 halamanNew Syllabus Group VII Services UpdatedSaravana PandiyanBelum ada peringkat

- WSNDokumen2 halamanWSNGautami SumanBelum ada peringkat

- List of National Institutes of Technology in IndiaDokumen2 halamanList of National Institutes of Technology in IndiaGautami SumanBelum ada peringkat

- Students ObservationDokumen94 halamanStudents ObservationGautami SumanBelum ada peringkat

- Ec II Lab Manual (2013 2014)Dokumen85 halamanEc II Lab Manual (2013 2014)surendhar1987Belum ada peringkat

- Ec6401 Ec II Part b2Dokumen5 halamanEc6401 Ec II Part b2Gautami SumanBelum ada peringkat

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeDari EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifePenilaian: 4 dari 5 bintang4/5 (5794)

- Shoe Dog: A Memoir by the Creator of NikeDari EverandShoe Dog: A Memoir by the Creator of NikePenilaian: 4.5 dari 5 bintang4.5/5 (537)

- The Yellow House: A Memoir (2019 National Book Award Winner)Dari EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Penilaian: 4 dari 5 bintang4/5 (98)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceDari EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RacePenilaian: 4 dari 5 bintang4/5 (895)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersDari EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersPenilaian: 4.5 dari 5 bintang4.5/5 (344)

- The Little Book of Hygge: Danish Secrets to Happy LivingDari EverandThe Little Book of Hygge: Danish Secrets to Happy LivingPenilaian: 3.5 dari 5 bintang3.5/5 (399)

- Grit: The Power of Passion and PerseveranceDari EverandGrit: The Power of Passion and PerseverancePenilaian: 4 dari 5 bintang4/5 (588)

- The Emperor of All Maladies: A Biography of CancerDari EverandThe Emperor of All Maladies: A Biography of CancerPenilaian: 4.5 dari 5 bintang4.5/5 (271)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaDari EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaPenilaian: 4.5 dari 5 bintang4.5/5 (266)

- Never Split the Difference: Negotiating As If Your Life Depended On ItDari EverandNever Split the Difference: Negotiating As If Your Life Depended On ItPenilaian: 4.5 dari 5 bintang4.5/5 (838)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryDari EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryPenilaian: 3.5 dari 5 bintang3.5/5 (231)

- On Fire: The (Burning) Case for a Green New DealDari EverandOn Fire: The (Burning) Case for a Green New DealPenilaian: 4 dari 5 bintang4/5 (73)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureDari EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FuturePenilaian: 4.5 dari 5 bintang4.5/5 (474)

- Team of Rivals: The Political Genius of Abraham LincolnDari EverandTeam of Rivals: The Political Genius of Abraham LincolnPenilaian: 4.5 dari 5 bintang4.5/5 (234)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyDari EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyPenilaian: 3.5 dari 5 bintang3.5/5 (2259)

- Rise of ISIS: A Threat We Can't IgnoreDari EverandRise of ISIS: A Threat We Can't IgnorePenilaian: 3.5 dari 5 bintang3.5/5 (137)

- The Unwinding: An Inner History of the New AmericaDari EverandThe Unwinding: An Inner History of the New AmericaPenilaian: 4 dari 5 bintang4/5 (45)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreDari EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You ArePenilaian: 4 dari 5 bintang4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Dari EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Penilaian: 4.5 dari 5 bintang4.5/5 (120)

- Her Body and Other Parties: StoriesDari EverandHer Body and Other Parties: StoriesPenilaian: 4 dari 5 bintang4/5 (821)

- English 7 Module 2Dokumen26 halamanEnglish 7 Module 2Meach Callejo100% (1)

- Casio CTK-750 Service ManualDokumen30 halamanCasio CTK-750 Service ManualFelix Vega100% (1)

- SmartFlash HelpDokumen9 halamanSmartFlash HelpRoger Danilo FiglieBelum ada peringkat

- KUDU PCP Manager: Well Optimization UnitDokumen2 halamanKUDU PCP Manager: Well Optimization UnitFan Jack100% (1)

- Single or Multi Electronic Notice Board With Operating Distance 1000 Meters Using RS 485 ProtocolDokumen104 halamanSingle or Multi Electronic Notice Board With Operating Distance 1000 Meters Using RS 485 Protocolaravishankar23Belum ada peringkat

- Self-Instructional Manual (SIM) For Self-Directed Learning (SDL)Dokumen30 halamanSelf-Instructional Manual (SIM) For Self-Directed Learning (SDL)Geoffrey Beenie P. Orpia100% (1)

- Computer Architecture CHAPTER 1Dokumen47 halamanComputer Architecture CHAPTER 1ShaarvinBelum ada peringkat

- Cad Cam - Module 1Dokumen85 halamanCad Cam - Module 1sibaprasad.behera2020Belum ada peringkat

- Kisssoft 0315 Product Description en PDFDokumen112 halamanKisssoft 0315 Product Description en PDFhrrypnBelum ada peringkat

- MSI Z270 SLI PLUS (MS-7A59) Performance Results - UserBenchmarkDokumen3 halamanMSI Z270 SLI PLUS (MS-7A59) Performance Results - UserBenchmarkPetar SlapnicarBelum ada peringkat

- Computer Skills: CIS-100 CH1Dokumen68 halamanComputer Skills: CIS-100 CH1Khaled AbdulazizBelum ada peringkat

- Computer Programming Book Final-Version-2Dokumen199 halamanComputer Programming Book Final-Version-2Vishal VBelum ada peringkat

- RTO Management SystemDokumen4 halamanRTO Management SystemKeerthi Vasan L100% (1)

- RCS-985A Generator Protection Instruction Manual SupplementDokumen87 halamanRCS-985A Generator Protection Instruction Manual SupplementDipak Kumar PatelBelum ada peringkat

- Online Resume Builder: FeaturesDokumen3 halamanOnline Resume Builder: FeaturesGishnu GovindBelum ada peringkat

- Blue Prism Data Sheet - Provisioning A Blue Prism Database ServerDokumen5 halamanBlue Prism Data Sheet - Provisioning A Blue Prism Database Serverreddy_vemula_praveenBelum ada peringkat

- Havens Ottawa ProposalDokumen15 halamanHavens Ottawa ProposalAnonymous BjaA0IiYBelum ada peringkat

- KORG Pa300 & Havian 30: Update 2.0 - Part 1. (ENGLISH)Dokumen7 halamanKORG Pa300 & Havian 30: Update 2.0 - Part 1. (ENGLISH)Import Music USABelum ada peringkat

- HCNA-Access Lab Guide V2.0Dokumen177 halamanHCNA-Access Lab Guide V2.0ArturNascimentoBelum ada peringkat

- 1478175959468-CSE&IT StreamDokumen55 halaman1478175959468-CSE&IT StreamsaiprashantBelum ada peringkat

- Bahasa Inggris - 20024007Dokumen6 halamanBahasa Inggris - 20024007Joshua KeintjemBelum ada peringkat

- EEPROM 28C16 DatasheetDokumen18 halamanEEPROM 28C16 DatasheetCesarBelum ada peringkat

- Tutorial 5 On Memory Organization: A. RAM Chips 2k Bytes/256 Bytes 8, ROM 4k Bytes/1024 Bytes 4. BDokumen3 halamanTutorial 5 On Memory Organization: A. RAM Chips 2k Bytes/256 Bytes 8, ROM 4k Bytes/1024 Bytes 4. BAgrim DewanBelum ada peringkat

- Memory Management in Operating SystemDokumen5 halamanMemory Management in Operating Systemgyan prakashBelum ada peringkat

- XilinxDokumen107 halamanXilinxmarkostankoBelum ada peringkat

- Neogeo Programmer GuideDokumen220 halamanNeogeo Programmer GuidesudoBelum ada peringkat

- IT Assignments 1-13Dokumen34 halamanIT Assignments 1-13ASHISHBelum ada peringkat

- Critikon Dinamap SPO2 Modul - Service ManualDokumen27 halamanCritikon Dinamap SPO2 Modul - Service ManualJulio Benancio ZuluagaBelum ada peringkat

- Module 1 - Knowing ComputerDokumen23 halamanModule 1 - Knowing ComputerShiela Jane CrismundoBelum ada peringkat

- DatasheetDokumen68 halamanDatasheetjaime l cruz sBelum ada peringkat