GSM / GPRS Wireless Module: Design Guide Rev. 0.1 December. 2003

Diunggah oleh

livslxJudul Asli

Hak Cipta

Format Tersedia

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniHak Cipta:

Format Tersedia

GSM / GPRS Wireless Module: Design Guide Rev. 0.1 December. 2003

Diunggah oleh

livslxHak Cipta:

Format Tersedia

M23

GSM / GPRS Wireless Module

Design Guide

Rev. 0.1

December. 2003

COPYRIGHT BENQ Corporation

This document contains proprietary technical information which is the property of BenQ Corporation

and is issued in strict confidential and shall not be disclosed to others parties in whole or in parts

without written permission of BenQ Corporation

The documents contain information on a product, which is under development and is issued for cus-

tomer evaluation purposes only.

BENQ may make changes to product specifications at any time, without notice.

BenQ Corporation

Networking & Communications BG

18 JiHu Road, Nei-Hu, Taipei 114, Taiwan, R.O.C.

Tel: +886-2-2799-8800

Fax: +886-2-2656-6399

http://www.benq.com

©2003 BenQ Corporation 1 Confidential Property

M23 Design Guide Version: 0.1 - 2003/12/12

1. OVERVIEW ............................................................................................................................................................................................. 3

2. DESIGN GUIDE ORGANIZATION ..................................................................................................................................................... 4

3. PIN ASSIGNMENT OF M23 MODULE............................................................................................................................................... 5

3.1. M23 MODULE PLACEMENT ..................................................................................................................................................... 5

3.2. GROUND PIN.................................................................................................................................................................................. 5

3.3. VBATRF PIN (PIN 41~43) / VBATBB PIN (PIN 1) ......................................................................................................... 5

3.4. POWER ON SEQUENCE ................................................................................................................................................................ 6

3.5. INTERRUPT ..................................................................................................................................................................................... 6

3.7 THE HANDSHAKING MECHANISM BETWEEN SYSTEM (HOST) AND MODULE (CLIENT) ....................................... 10

3.8 POWER ON/OFF SEQUENCE BETWEEN SYSTEM (HOST) AND MODULE (CLIENT) ................................................ 12

4 PERIPHERALS ..................................................................................................................................................................................... 14

4.1 SIM ................................................................................................................................................................................................. 14

4.2 AUDIO ............................................................................................................................................................................................ 14

4.3 PAGING INDICATOR ............................................................................................................................................................................ 16

4.4 ACOUSTIC TEST (DAI INTERFACE) ............................................................................................................................................... 17

5 IO MAPPING ......................................................................................................................................................................................... 18

6 UART INTERFACE .............................................................................................................................................................................. 19

7 RS232 (HW FLOW CONTROL) ......................................................................................................................................................... 20

8 POWER ON/OFF CONCERNS........................................................................................................................................................... 22

©2003 BenQ Corporation 2 Confidential Property

M23 Design Guide Version: 0.1 - 2003/12/12

1. Overview

This design guide is based mainly on the M23 evaluation board (EVB). The M23 EVB enables you to

evaluate the M23 module and peripheral design. In addition, it provides sampling firmware that you

can use as a starting point to develop code. To give the user a system concept of the interconnections

between the host and M23 module, we first give a block diagram as

The reference schematics for M23 peripherals will be given in details in this design guide. Since the

interconnections between the host and M23 vary by application, we tend to give only reference de-

signs of general functions, such as, interrupts,

re-download mechanisms, flow control of RS232, etc.

©2003 BenQ Corporation 3 Confidential Property

M23 Design Guide Version: 0.1 - 2003/12/12

2. Design Guide Organization

The rest of the manual is organized as follows:

Section 3 Pin out definition of M23 module is given along with the RF antenna placement and trace

guidelines. In addition, the recommended power on; and handshaking sequences are

shown.

Section 4 Suggested peripheral schematics, i.e., SIM, audio, and paging indicator is given.

Section 5 The IO mapping of the M23 module is explained in details.

Section 6 The UART interface pin description is given.

Section 7 The re-download procedure is shown.

Section 8 Hardware flow control of the RS232 is illustrated in details.

Section 9 Some related power on/off concerns are given.

©2003 BenQ Corporation 4 Confidential Property

M23 Design Guide Version: 0.1 - 2003/12/12

3. Pin Assignment of M23 module

The following is the pin out definition of the M23 module

VBATBB 1 44 GND

GND 2 43 VBATRF

GND 3 42 VBATRF

GND 4 41 VBATRF

GND 5 40 GND

LEDA 6 39 IO10

ROW4 7 38 PWON

TXD2 8 37 RXD2

IO12/DCD 9 36 BU

GND 10 35 GND

SIM_CLK 11 34 TXD

SIM_IO 12 33 RXD

SIM_RST 13 32 RTS

NC 14 31 CTS

MICBIAS 15 30 DSR

MICIP 16 29 IO8

MICIN 17 28 IO13

AUXI 18 27 IO11

GND 19 26 GND

EARP 20 25 IO6

EARN 21 24 IO1/RI

AUXOP 22 23 VRSIM

3.1. M23 Module Placement

In our module, we have one 50ohm antenna port (interfaced by MMCX female connector) for signal

transfer, and the Antenna port can be directly connected to antenna though RF coaxial cable. In addi-

tion, the RF signal will be impacted by high data rate. We strongly suggest the audio trace and SIM

signal trace to be short as possible and as far away as possible from the RF trace and power line to

prevent cross coupling.

3.2. Ground Pin

There are 10 ground pins in M23 module, they should be connected together and routed to the

common connection of the PCB ground plane (The ground plane in PCB should be as large as

possible).

3.3. VBATRF Pin (Pin 41~43) / VBATBB Pin (Pin 1)

The “Power amplifier” is supplied by the VBATRF pins. During transmitting mode, high output power

will draw a large amount of current. The width of this power trace that is connected to the VBATRF

pins could not be less than 80mils. In addition, it is better to shunt a 100uF (low ESR) bypass ca-

pacitor on VBATRF pins to prevent voltage drop and to reduce ripple. Furthermore, another chips in

©2003 BenQ Corporation 5 Confidential Property

M23 Design Guide Version: 0.1 - 2003/12/12

the module are supplied by the VBATBB pin. The width of this trace that connected to this pin

should also be wider.

3.4. Power on sequence

The pin POWON is dedicated to powering on the M23 module. The pin is initially HIGH when

power is applied to the M23 module. Once the pin is pulled low for more than 120 ms, M23 will

power on.

120 ms

3.5. Interrupt

There are two pins dedicated to work as an acknowledge function between the system (Host) and

module (Client):

The pin IO10 is used for the M23 module (Client) to interrupt the system (Host), whereas the pin

Row4 is used for the system (Host) to interrupt the M23 module (Client).

Pin Name Function

39 IO10 (active high) Module (Client) informs system (Host)

7 Row 4 (active low) System (Host) informs module (Client)

©2003 BenQ Corporation 6 Confidential Property

M23 Design Guide Version: 0.1 - 2003/12/12

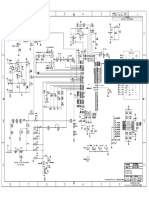

Figure 1 Application Connection Diagram

Note: Vcc comes from system.

Note: The scenario in Figure 1 is to be used when the Module is required to control the switches

connecting the UARTs and GPIOs of the host and module. This is done when the module power off.

The AND gate in the above diagram can be implemented by the following schematics.

©2003 BenQ Corporation 7 Confidential Property

M23 Design Guide Version: 0.1 - 2003/12/12

AND GATE OUTPUT, PWON, ROW4, IO11 Sequence

VCC

U5

6 1

VCC A ROW4

5 2 VCC R1

NC B

4 3 220K

Y GND

NC7SZ08 BGND

R2

BGND

100K

3

BQ1 R4

1

IO11

2K

BC817-40W R3

2

22K

BGND

BGND

©2003 BenQ Corporation 8 Confidential Property

M23 Design Guide Version: 0.1 - 2003/12/12

VCC=4V; M23 VBAT=4V

IO11: reset status is input

ROW4/wakeup:input pin pull high after trigger

Note: The mechanism shows that after the PWON pin is pulled low, ROW4 becomes HIGH after 63ms.

At the same time interval IO11 remains input status, since the resistor R3 pulls IO11 to low within the

reset period, therefore BQ1 is kept open and pin 3 of BQ1 is kept high. Meanwhile Row4 is high, so the

output of the AND gate (U5) is high and the switch is closed. If the switch needs to be opened, the

IO11 can be controlled to be high and BQ1 will close. This in turn will make pin 2 of U5 Low. The output

of the AND gate will therefore be low and the switch will be opened. During power off of the module,

the pull Low resistor R1 will keep the pin 1 of U5 to low and therefore the output of the AND gate will be

Low also. Thus opening the switch in Figure 1.

©2003 BenQ Corporation 9 Confidential Property

M23 Design Guide Version: 0.1 - 2003/12/12

3.7 The handshaking mechanism between System (Host) and Module (Client)

Note: The UART function of the handshaking mechanism is defined to be hardware flow control type.

Module (Client) needs to inform system (Host) of tasks

M odule (Client)

No Module (Client) kept at

Is there incom ing task? original status

Yes

Module pulls high IO10 40~50m s to inform

system , Module is going to do som ething

and sets IO11 Low (default)

4 0~50 m s

Module (Client) via UART

IO 1 0

sends com m and to system

The above block diagram shows how the module informs the host system that a task requiring inter-

action will be carried out. When the tasking is coming, the module pulls HIGH IO10 for at least 40~50

ms to inform host that a task will be carried out.

Note: Based on Figure 1, assume the interrupt pin in system (Host) is low active, therefore if module

needs to inform system via IO10, the module have to pull high IO10 a time interval to achieve this

requirement,

©2003 BenQ Corporation 10 Confidential Property

M23 Design Guide Version: 0.1 - 2003/12/12

System (Host) informs Module (Client) of tasks

System (Host) Side

No Module kept at original

Inform Module?

status

Yes

Check if module Yes

Send AT command

sleep mode is off

No

System(Host) pull low Row4

50ms to inform Module, and

immediately sends "don't Host need to keep module Yes

deep sleep" command to out of sleep mode?

disable module deep sleep

mode (or any other AT

command)

No

Send AT command to

activate sleep mode

The above block diagram shows how the host system informs the module that a task requiring inter-

action will be carried out.

Note: The above procedure is exclusively used in hardware flow control configuration.

©2003 BenQ Corporation 11 Confidential Property

M23 Design Guide Version: 0.1 - 2003/12/12

3.8 Power on/off sequence between System (Host) and Module (Client)

Power on sequence

System (Host) side

No

Module kept

Power on Module?

power off

Yes

PWON

Pull Low PWON for 120 ms

120 ms

M22 is Powered On

Success

40~50ms

Module sets IO10 High 40 ~ 50 ms

to inform system power on

IO10

System (Host) sends "AT" to

Module, and Module returns "OK" to

Host

The above block diagram shows the power on sequence. First the host powers on and pulls Low

PWON of the module for at least 120 ms. When the module is powered on, it sets IO10 will High 40 ~

50 ms .

©2003 BenQ Corporation 12 Confidential Property

M23 Design Guide Version: 0.1 - 2003/12/12

Power off sequence

System (Host) side

Power off Module? Module kept on

No

Yes

System sends AT command

'at$poweroff' to set Module into

power off

Fail

Module receives AT command

Success (returns ACK to host)

Module prepares to power off

The above block diagram shows the power off sequence. The host sends an AT command

‘at$poweroff’ to set module into power off. Module powers off once AT command is received. Please

note that if the host system is left powered on, switches are suggested to protect from current leakage.

Note : User can not try to power on module within 2000 ms after sending at$poweroff command

to module

©2003 BenQ Corporation 13 Confidential Property

M23 Design Guide Version: 0.1 - 2003/12/12

4 Peripherals

4.1 SIM

The SIM Card digital interface in the M23 ensures the translation of logic levels between M23 and

the SIM Card, for the transmission of 3 different signals: SIM_CLK; a reset signal from M23 to the

SIM Card (SIM_RST); and serial data from M23 to the SIM Card (SIM_IO). The SIM card interface

can be programmed to drive a 3V SIM Card.

(1) Type I ( 8 Pin SIM Socket )

(2) Type II ( 6 Pin SIM Socket )

4.2 Audio

There are 2 embedded audio drivers built in the BenQ M23 module. The 2 drivers can drive different

kinds of audio load (such as receiver, microphone, or hands free).

¾ Microphone

©2003 BenQ Corporation 14 Confidential Property

M23 Design Guide Version: 0.1 - 2003/12/12

¾ Auxiliary Input/output

AUXOP

R51

MICBIAS

2K

C13 R53 C17

R57 0.1UF 1K 4.7UF

J6

5.6K

BGND BGND 2 1

R54 C15 SW GND

3

AUXI SPK

3

BQ5

2K 1UF 1 4

MIC

BC817-40W Audio Jack

2

BGND

1

C17

R58 T2 T3

. .

. .

4.7UF TVS TVS

12K

2

R60

3.3K

BGND BGND

BGND

Voltage Gain = 2 with R60=3.3K

¾ Ear output

Audio Path Selection AT Commands

The M23 module provides the switching of audio paths using AT commands (In connection status):

Default value: case (2)

(1) at$aupath=3,0 (EARN, EARP, MICIN, MICIP, MICBIAS path OFF)

(2) at$aupath=3,1 (EARN, EARP, MICIN, MICIP, MICBIAS path ON)

(3) at$aupath=2,0 (AUXI,AUXOP,MICBIAS path OFF)

(4) at$aupath=2,1 (AUXI,AUXOP,MICBIAS path ON)

©2003 BenQ Corporation 15 Confidential Property

M23 Design Guide Version: 0.1 - 2003/12/12

4.3 Paging Indicator

LEDA is dedicated for paging indication. The application circuit is shows as below. The diagram

below illustrates the application schematic for LED driver inputs LEDA. In each case the current

limiter resistor R has to be selected in order to be compliant with maximum current drive capability

of each input.

Pin Name Max drive current High level voltage Low level voltage supply Function

6 LEDA 10mA VBATBB 0.4 VBATBB paging indicator

VBAT

Module

LEDA

<Value>

LEDA is controlled through software program using a dedicated bit, which is built in the M23

module already.

The LEDA pin status :

a. When there is no voltage input, the LEDA is in high status. It means that the LED won’t be

illuminated.

b. When the module is powered on and not making phone calls, LEDA will pull low 500 ms and

pull high 500 ms, alternately.

c. When incoming phone call, the LEDA will pull low 125 ms and return to high status 125ms

after hanging up the phone

©2003 BenQ Corporation 16 Confidential Property

M23 Design Guide Version: 0.1 - 2003/12/12

4.4 Acoustic test (DAI interface)

Pin Name Pin Out Pull Reset Config Description

MCSI_TXD/IO 9 28* 0 0 Transmit serial data

MCSI_RXD/IO10 4 Input Input Receive serial data

MCSI_CLK/IO 11 30 Input Input Bit synchronization clock

MCSI_FSYNCH/IO 12 10 Input Input Frame synchronization clock or SS reset

*Pin 28 is multipurpose function pin (switch by config JP5). In normal operation mode, it pin is function

as GPIO1 (JP5 is setting as Case 1). In acoustic test mode, it pin is function as DAI interface (JP5

should be setting as Case 2)

IO9

Case1 Case2

JP5 JP5

©2003 BenQ Corporation 17 Confidential Property

M23 Design Guide Version: 0.1 - 2003/12/12

5 IO mapping

There have 6 IO pins available for M23 module. The function for these IO pins is List below.

No. Pin Description I/O PU Reset Config

39 IO 10 M23 (Client) wake up System (Host) O Input Output / 0

28 IO 13 GPIO13 I Output/1 Input

25 IO 6 Re-download Data path and audio path switch O Input Output/1

Power off mode switch control signal to open or

link the connection between system (Host) and

module (client).

27 IO 11 O Input Output / 0

Low :; Connect

High: Disconnect

Default = Connect ( Low )

9 IO 12/DCD IO12/Data Carrier Detect O Input Output / 0

24 IO 1/RI IO1/Ring Indicator O Input Output / 0

©2003 BenQ Corporation 18 Confidential Property

M23 Design Guide Version: 0.1 - 2003/12/12

6 UART Interface

UART/RS232

The UART includes the following additional features

- Hardware flow control (DSR, RTS/CTS)

- Auto-bauding rate with the possibility of baud-rates ranging from 1200 to 115.2K bits.

Pin Name Pin Out Pull Reset Config Description

TXD 34 1 Output/1 Transmit Data

RXD 33 PU Input Input Receive Data

RTS 32 1 Output/1 Request to Send

CTS 31 PD Input Input Clear to Send

DSR 30 Input Input Data Set Ready

IO 8/DTR 29 1 Output/0 Data Terminal Ready

Note: The difference between Reset and Config in the pin definition table

UART 2

Used for software debug.

Pin Name Pin Out Pull Reset Config Description

TXD2 8 1 Output/1 Transmit Data

RXD2 37 PU Input Input Receive Data

©2003 BenQ Corporation 19 Confidential Property

M23 Design Guide Version: 0.1 - 2003/12/12

7 RS232 (HW flow control)

There are two types of UART connection able to implement the communication between the sys-

tem (Host side) and module (Client side).

HW flow control

When the hardware flow control type is recommended for communication between the Host and client,

IO13 of the module must be pulled high to 3V to setup module into this condition. Regarding the

hardware flow control mechanism between the system (host side) and module (client side), there are

two connections possible and are illustrated as follows:

Option 1:

HOST

M23

Device

TX TX

RX RX

DTR DTR

DSR DSR

RTS RTS

CTS CTS

GND GND

Option :2

External

HOST

Device M23

TX TX

RX RX

RTS RTS

CTS CTS

DSR

DTR

GND GND

Note: Since the DSR in M23 is PU 10K.

©2003 BenQ Corporation 20 Confidential Property

M23 Design Guide Version: 0.1 - 2003/12/12

Autobaud Rate Mechanism

The M23 module UART is set at autobaud rate. This means when the M23 is powered on, it auto-

matically detects the baud rate after the first AT command sent by the host. The baud rate is locked at

the initially detected rate unless the following conditions:

For Option 1 autobaud rate detect process is reinitialized:

a) If the module is powered off then powered on;

Or

b) If the DSR pin of the UART is disabled and then enabled

For Option 2 autobaud rate detect process is reinitialized:

If the module is powered off then powered on.

©2003 BenQ Corporation 21 Confidential Property

M23 Design Guide Version: 0.1 - 2003/12/12

8 Power On/Off Concerns

The designer should be careful when there are different status between System (Host) and M23

module. In other words, if the System (Host) is powered on and the M23 module is powered off or

vice versa, problems of current leakage will arise. Therefore, we make the following recommenda-

tion to avoid the problem owing to the different status described as the following conditions between

system (Host) and module (client).

©2003 BenQ Corporation 22 Confidential Property

M23 Design Guide Version: 0.1 - 2003/12/12

M23 Power on condition

Condition 1: System (Host) is powered on but M23 do not need to be powered on

Since we don’t need to power on the module, it is better to open the UART and IO connec-

tion between the system (Host) and module (Client). A buffer should be added to the PWON ,

ROW4 and IO10 pins.

M23 Power off condition

Condition 1: System (Host) is active and M23 needs to be turned off:

Switches should be added to the GPIOs which connects the System (Host) and M23 module.

A buffer should be added to the PWON , ROW4 and IO10 pins.

The System (Host) should give an AT command to the M23 module and when M23 receives

power off command, M23 return ACK via UART to inform system (Host) that M23 is going to

enter power-off status. When M23 is powered off , the switch between the System (Host) and

M23 will be open to avoid the current leakage to be happened.

Condition 2: System (Host) needs to be turned off:

The M23 module should be turned off with the System (Host) and follow Conditions 1.

©2003 BenQ Corporation 23 Confidential Property

M23 Design Guide Version: 0.1 - 2003/12/12

Anda mungkin juga menyukai

- JASON Version 0.99: Just Another Ship-Owner Name:-)Dokumen7 halamanJASON Version 0.99: Just Another Ship-Owner Name:-)Apollos_80Belum ada peringkat

- Attiny2313 ESR SchematicDokumen1 halamanAttiny2313 ESR SchematiclivslxBelum ada peringkat

- 11 Normal Vs AbnormalCombustionDokumen4 halaman11 Normal Vs AbnormalCombustionDhananjay BaviskarBelum ada peringkat

- Power Supply Repair PDFDokumen4 halamanPower Supply Repair PDFAbdul Basit AminBelum ada peringkat

- Fluke 17b Multimeter SchematicsDokumen1 halamanFluke 17b Multimeter Schematicslivslx100% (1)

- Poor Man 1GHzDokumen3 halamanPoor Man 1GHzmuddogBelum ada peringkat

- 6th Central Pay Commission Salary CalculatorDokumen15 halaman6th Central Pay Commission Salary Calculatorrakhonde100% (436)

- Fluke 17b Multimeter Schematics PDFDokumen1 halamanFluke 17b Multimeter Schematics PDFlivslxBelum ada peringkat

- MIC-10K1 Insulation TesterDokumen68 halamanMIC-10K1 Insulation TesterlivslxBelum ada peringkat

- Interfacing 555 TimersDokumen4 halamanInterfacing 555 TimerslivslxBelum ada peringkat

- Designing Oscillators OpAmpDokumen5 halamanDesigning Oscillators OpAmplivslxBelum ada peringkat

- Simple Overload Circuit Protects DC PSUDokumen1 halamanSimple Overload Circuit Protects DC PSUlivslxBelum ada peringkat

- LKZ 1500Dokumen48 halamanLKZ 1500livslxBelum ada peringkat

- Troubleshooting OPAMPs and OtherDokumen11 halamanTroubleshooting OPAMPs and OtherlivslxBelum ada peringkat

- Single Supply Op Amp DesignDokumen2 halamanSingle Supply Op Amp DesignlivslxBelum ada peringkat

- MMR-650 MilliohmeterDokumen72 halamanMMR-650 MilliohmeterlivslxBelum ada peringkat

- Survey and Examination of Ships' Lifting AppliancesDokumen24 halamanSurvey and Examination of Ships' Lifting Applianceshpss77100% (1)

- Radio Electronics November 1991 PDFDokumen188 halamanRadio Electronics November 1991 PDFlivslx100% (1)

- Mpi Mru Guide For The En62305 En60364-6 StandardsDokumen48 halamanMpi Mru Guide For The En62305 En60364-6 StandardsChristine BuchananBelum ada peringkat

- Operating Manual for the MZC-304 Fault Loop Impedance MeterDokumen44 halamanOperating Manual for the MZC-304 Fault Loop Impedance MeterlivslxBelum ada peringkat

- Rules of the Road guide for safe navigationDokumen5 halamanRules of the Road guide for safe navigationlivslxBelum ada peringkat

- Dissassembling and Patching Hardware - (Malestrom)Dokumen90 halamanDissassembling and Patching Hardware - (Malestrom)diwankumaniBelum ada peringkat

- Archivi Audiofilofine Crowhurst Cooper 1956 High Fidelity Circuit DesignDokumen304 halamanArchivi Audiofilofine Crowhurst Cooper 1956 High Fidelity Circuit DesignGastrolio ErmeteBelum ada peringkat

- Low-Resistance Meter ManualDokumen40 halamanLow-Resistance Meter ManuallivslxBelum ada peringkat

- Panamax Cargo Hold Cleaning Manual Rev01Dokumen22 halamanPanamax Cargo Hold Cleaning Manual Rev01livslx100% (2)

- Wire Ropes and Their UsesDokumen12 halamanWire Ropes and Their UseslivslxBelum ada peringkat

- Ordering Safety SignsDokumen14 halamanOrdering Safety SignslivslxBelum ada peringkat

- Garbage RegulationDokumen1 halamanGarbage RegulationlivslxBelum ada peringkat

- Shipping in Arctic Waters, A Comparison of The Northeast, Northwest and Trans Polar PassagesDokumen435 halamanShipping in Arctic Waters, A Comparison of The Northeast, Northwest and Trans Polar Passageslivslx100% (1)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeDari EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifePenilaian: 4 dari 5 bintang4/5 (5784)

- The Little Book of Hygge: Danish Secrets to Happy LivingDari EverandThe Little Book of Hygge: Danish Secrets to Happy LivingPenilaian: 3.5 dari 5 bintang3.5/5 (399)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceDari EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RacePenilaian: 4 dari 5 bintang4/5 (890)

- Shoe Dog: A Memoir by the Creator of NikeDari EverandShoe Dog: A Memoir by the Creator of NikePenilaian: 4.5 dari 5 bintang4.5/5 (537)

- Grit: The Power of Passion and PerseveranceDari EverandGrit: The Power of Passion and PerseverancePenilaian: 4 dari 5 bintang4/5 (587)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureDari EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FuturePenilaian: 4.5 dari 5 bintang4.5/5 (474)

- The Yellow House: A Memoir (2019 National Book Award Winner)Dari EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Penilaian: 4 dari 5 bintang4/5 (98)

- Team of Rivals: The Political Genius of Abraham LincolnDari EverandTeam of Rivals: The Political Genius of Abraham LincolnPenilaian: 4.5 dari 5 bintang4.5/5 (234)

- Never Split the Difference: Negotiating As If Your Life Depended On ItDari EverandNever Split the Difference: Negotiating As If Your Life Depended On ItPenilaian: 4.5 dari 5 bintang4.5/5 (838)

- The Emperor of All Maladies: A Biography of CancerDari EverandThe Emperor of All Maladies: A Biography of CancerPenilaian: 4.5 dari 5 bintang4.5/5 (271)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryDari EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryPenilaian: 3.5 dari 5 bintang3.5/5 (231)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaDari EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaPenilaian: 4.5 dari 5 bintang4.5/5 (265)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersDari EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersPenilaian: 4.5 dari 5 bintang4.5/5 (344)

- On Fire: The (Burning) Case for a Green New DealDari EverandOn Fire: The (Burning) Case for a Green New DealPenilaian: 4 dari 5 bintang4/5 (72)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyDari EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyPenilaian: 3.5 dari 5 bintang3.5/5 (2219)

- Rise of ISIS: A Threat We Can't IgnoreDari EverandRise of ISIS: A Threat We Can't IgnorePenilaian: 3.5 dari 5 bintang3.5/5 (137)

- The Unwinding: An Inner History of the New AmericaDari EverandThe Unwinding: An Inner History of the New AmericaPenilaian: 4 dari 5 bintang4/5 (45)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreDari EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You ArePenilaian: 4 dari 5 bintang4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Dari EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Penilaian: 4.5 dari 5 bintang4.5/5 (119)

- Her Body and Other Parties: StoriesDari EverandHer Body and Other Parties: StoriesPenilaian: 4 dari 5 bintang4/5 (821)

- Ecole Polytechnique Federale de LausanneDokumen44 halamanEcole Polytechnique Federale de LausanneSyed Yahya HussainBelum ada peringkat

- Distinguish Between Tax and FeeDokumen2 halamanDistinguish Between Tax and FeeRishi Agarwal100% (1)

- Key formulas for introductory statisticsDokumen8 halamanKey formulas for introductory statisticsimam awaluddinBelum ada peringkat

- Exor EPF-1032 DatasheetDokumen2 halamanExor EPF-1032 DatasheetElectromateBelum ada peringkat

- Living Nonliving DeadDokumen11 halamanLiving Nonliving DeadArun AcharyaBelum ada peringkat

- Programming Manual Magic 308/616-CLI Quick ReferenceDokumen16 halamanProgramming Manual Magic 308/616-CLI Quick ReferencekrishnamarajublrBelum ada peringkat

- Quiz-Travel - Beginner (A1)Dokumen4 halamanQuiz-Travel - Beginner (A1)Carlos Alberto Rodriguez LazoBelum ada peringkat

- Module - No. 3 CGP G12. - Subong - BalucaDokumen21 halamanModule - No. 3 CGP G12. - Subong - BalucaVoome Lurche100% (2)

- Bandung Colonial City Revisited Diversity in Housing NeighborhoodDokumen6 halamanBandung Colonial City Revisited Diversity in Housing NeighborhoodJimmy IllustratorBelum ada peringkat

- Reservoir Rock TypingDokumen56 halamanReservoir Rock TypingAffan HasanBelum ada peringkat

- Self Team Assessment Form - Revised 5-2-20Dokumen6 halamanSelf Team Assessment Form - Revised 5-2-20api-630312626Belum ada peringkat

- Optimization of The Spray-Drying Process For Developing Guava Powder Using Response Surface MethodologyDokumen7 halamanOptimization of The Spray-Drying Process For Developing Guava Powder Using Response Surface MethodologyDr-Paras PorwalBelum ada peringkat

- Doe v. Myspace, Inc. Et Al - Document No. 37Dokumen2 halamanDoe v. Myspace, Inc. Et Al - Document No. 37Justia.comBelum ada peringkat

- Clogging in Permeable (A Review)Dokumen13 halamanClogging in Permeable (A Review)Chong Ting ShengBelum ada peringkat

- Ana White - PLANS - A Murphy Bed YOU Can Build, and Afford To Build - 2011-03-03Dokumen20 halamanAna White - PLANS - A Murphy Bed YOU Can Build, and Afford To Build - 2011-03-03Ahmad KamilBelum ada peringkat

- Childrens Ideas Science0Dokumen7 halamanChildrens Ideas Science0Kurtis HarperBelum ada peringkat

- Guidelines Tax Related DeclarationsDokumen16 halamanGuidelines Tax Related DeclarationsRaghul MuthuBelum ada peringkat

- Victron MultiPlus 48 1200-13-16 Datasheet enDokumen1 halamanVictron MultiPlus 48 1200-13-16 Datasheet enBAHJARI AMINEBelum ada peringkat

- Trading Course DetailsDokumen9 halamanTrading Course DetailsAnonymous O6q0dCOW6Belum ada peringkat

- Weekly Choice - Section B - February 16, 2012Dokumen10 halamanWeekly Choice - Section B - February 16, 2012Baragrey DaveBelum ada peringkat

- DSE61xx Configuration Suite Software Manual PDFDokumen60 halamanDSE61xx Configuration Suite Software Manual PDFluisBelum ada peringkat

- Individual Assignment ScribdDokumen4 halamanIndividual Assignment ScribdDharna KachrooBelum ada peringkat

- WassiDokumen12 halamanWassiwaseem0808Belum ada peringkat

- Postnatal Assessment: Name Date: Age: D.O.A: Sex: Hospital: Marital Status: IP .NoDokumen11 halamanPostnatal Assessment: Name Date: Age: D.O.A: Sex: Hospital: Marital Status: IP .NoRadha SriBelum ada peringkat

- The Singular Mind of Terry Tao - The New York TimesDokumen13 halamanThe Singular Mind of Terry Tao - The New York TimesX FlaneurBelum ada peringkat

- PA Inspection Guidelines For Single Site Acceptance: 1 © Nokia Siemens NetworksDokumen18 halamanPA Inspection Guidelines For Single Site Acceptance: 1 © Nokia Siemens NetworksDenny WijayaBelum ada peringkat

- PW CDokumen4 halamanPW CAnonymous DduElf20OBelum ada peringkat

- Lesson 2 Mathematics Curriculum in The Intermediate GradesDokumen15 halamanLesson 2 Mathematics Curriculum in The Intermediate GradesRose Angel Manaog100% (1)

- Chapter 2Dokumen22 halamanChapter 2Okorie Chinedu PBelum ada peringkat

- MORTGAGE Short NotesDokumen11 halamanMORTGAGE Short Noteshamzatariq015Belum ada peringkat