Actividad 3 - Practica de Laboratorio (Punta Logica TTL-CMOS)

Diunggah oleh

Carlos SuruyHak Cipta

Format Tersedia

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniHak Cipta:

Format Tersedia

Actividad 3 - Practica de Laboratorio (Punta Logica TTL-CMOS)

Diunggah oleh

Carlos SuruyHak Cipta:

Format Tersedia

UNIVERSIDAD MARIANO GALVEZ DE GUATEMALA

FACULTAD DE INGENIERIA EN SISTEMAS DE INFORMACION

INGENIERIA EN SISTEMAS DE INFORMACION

JORNADA DIARIA VESPERTINA

Curso: Electrónica Digital Código: 2014 - 030

Actividad #3 Práctica de Laboratorio

PUNTA LÓGICA TTL / CMOS

OBJETIVOS

1. Construir una Punta Lógica

2. Armar un circuito digital en placa PCB o Placa perforada

MATERIALES

1 compuerta CD4049B

4 diodos 1N4148

1 Resistencia de 100KΩ 1/8w

1 Resistencia de 10MΩ 1/8w

1 Resistencia de 6.8kΩ 1/8w

1 Resistencia de 56Kk 1/8w

1 Transistor NTE159

1 Led rojo pequeño

1 Led verde pequeño

1 Lagarto pequeño color negro

1 Lagarto pequeño color rojo

1 Punta para prueba

Protoboard y cables para protoboard

Fuente o batería de 5 voltios

Y todos los materiales necesarios para su montaje en placa pcb y presentación final.

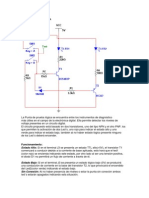

PUNTA LÓGICA

En un laboratorio electrónico necesitamos ciertos instrumentos de medición, por tal motivo construiremos una

punta lógica muy útil para analizar un circuito digital.

Una punta lógica es un instrumento que sirve para detectar niveles ALTOS o BAJOS (respuestas lógicas

digitales de unos y ceros) o señales de pulso en cualquier parte de un circuito digital. Para este caso la punta

lógica servirá para circuitos de la familia TTL y CMOS.

La punta lógica se alimenta de la misma fuente de tensión del circuito a analizar, conectando la terminal (-) o

sea el lagarto negro a la tierra y la terminal (+) o el lagarto rojo a los + 5 voltios del circuito para la familia TTL o

a más de 5 voltios para la familia CMOS (máximo de 15 voltios).

Su funcionamiento es muy básico, ya que se basa en un transistor PNP que trabajará con un interruptor, junto

con dos compuertas inversoras pudiendo mostrar en el LED indicador 2 estados posibles los cuales son:

1. Estado bajo (0) = LED verde

2. Estado alto (1) = LED rojo

Ing. Carlos Suruy

En el circuito que se presenta en la figura, trata de un circuito más elaborado y cercano a los nivelas CMOS,

aunque los niveles que presenta para TTL no son del todo rigurosos pero se pueden aceptar como buenos.

En dicho esquema, se aprecia una fuente de corriente constante de unos 15mA, formada por los componentes

pasivos: Q1, R3, R4, D3 y D4, la cual se encarga de alimentar el LED correspondiente, según el nivel lógico

detectado.

Los diodos D1 y D2, sirven de protección para la sonda, contra tensiones fortuitas de hasta 100V. Si a la

conexión "terminal libre" de R1 de 100k, se aplica una tensión elevada respecto a masa, la compuerta inversora

U1A del circuito integrado CMOS, invertirá este nivel y el cátodo de LED2 (Rojo) se pondrá a masa, por

consiguiente se iluminará, indicando un nivel lógico alto H.

Mientras tanto el nivel del cátodo de LED1 (Verde), permanecerá alto gracias a la nueva inversión producida

por U1B, y por consiguiente, dicho diodo no se iluminará. Sólo se iluminará cuando al extremo libre de R1 se le

aplique una pequeña tensión, respecto a masa inferior a 1/3 de la tensión de alimentación, en cuyo caso el nivel

bajo 0, se transmitirá hasta el cátodo de LED1 y éste se iluminará indicando un nivel lógico L, lo que conlleva

que el diodo LED2 se desactive permaneciendo ambos diodos en ese estado hasta que se produzca un cambio

en la entrada.

La resistencia R2 tiene encomendadas las funciones de limitar la carga que presentará la punta al circuito bajo

prueba por una parte y pone a masa al primer inversor U1A cuando no se aplica tensión alguna a la entrada,

evitando así que las puertas U1A y U1B entren en auto-oscilación por la gran sensibilidad que estas presentan

por tratarse de CMOS.

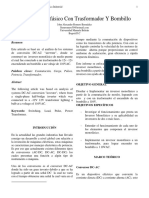

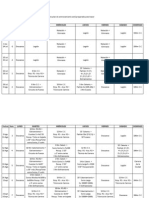

Pin Out del circuito integrado 4049B (compuerta NOT)

Ing. Carlos Suruy

Configuración del transistor NTE159 pnp

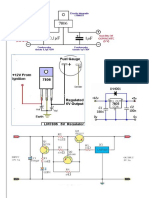

Diagrama esquemático

Ing. Carlos Suruy

Condiciones de la Entrega:

Individual.

Armar el circuito en el protoboard y comprobar su funcionamiento.

El circuito deberá ser armado en placa PCB o en placa perforada.

El circuito deberá ser debidamente montado en alguna caja o en algo que sirva para su presentación,

mientras más pequeño sea el circuito y el montaje; será mejor ponderado.

Se calificará el día del 1er. Examen Parcial

Si desea cambiar el circuito propuesto debe de presentar el diagrama esquemático y explicar su

funcionamiento el día de la entrega.

Ing. Carlos Suruy

Anda mungkin juga menyukai

- Punta Lógica TTL de Tres EstadosDokumen8 halamanPunta Lógica TTL de Tres EstadosMiguel Lop100% (1)

- Generador de PulsosDokumen8 halamanGenerador de PulsosRocio RicardezBelum ada peringkat

- Punta Logica de Prueba InformeDokumen17 halamanPunta Logica de Prueba InformeAngel OrtizBelum ada peringkat

- W3230 Interruptor Controlador de Temperatura On OFFDokumen2 halamanW3230 Interruptor Controlador de Temperatura On OFFJoaquin SilveraBelum ada peringkat

- Rectificador monofásico controlado PWM 150WDokumen7 halamanRectificador monofásico controlado PWM 150WAlveiro Alfonso GerenaBelum ada peringkat

- PUENTE RECTIFICADOR SEMICONTROLADO MONOFÁSICODokumen8 halamanPUENTE RECTIFICADOR SEMICONTROLADO MONOFÁSICOCarmen Rosa Amau QuispeBelum ada peringkat

- El 555 (Configuraciones)Dokumen8 halamanEl 555 (Configuraciones)enriquecourtadepBelum ada peringkat

- Circuito para Activación de Luz Nocturna AutomáticaDokumen2 halamanCircuito para Activación de Luz Nocturna Automáticahenry vergaraBelum ada peringkat

- Generación de Señal de Frecuencia Variable PWMDokumen6 halamanGeneración de Señal de Frecuencia Variable PWMAdriana KomykBelum ada peringkat

- Encoder Hall sensores simplificadoDokumen12 halamanEncoder Hall sensores simplificadoMartin Daza GarciaBelum ada peringkat

- Diseno de Un Oscilador en Un Puente Wien A 20KhzDokumen4 halamanDiseno de Un Oscilador en Un Puente Wien A 20KhzMartín Esteban Camargo100% (1)

- MultivibradoresDokumen20 halamanMultivibradoresDenny Herrera MarínBelum ada peringkat

- Rectificadores y FiltrosDokumen4 halamanRectificadores y FiltrosAaronE.TelloRuizBelum ada peringkat

- Control Temperatura para Cautin 112Dokumen5 halamanControl Temperatura para Cautin 112Fabian Barrios Torres100% (1)

- Simulador TpsDokumen4 halamanSimulador TpsRene CaMeBelum ada peringkat

- Amplificador LM386Dokumen22 halamanAmplificador LM386Jess1805Belum ada peringkat

- PIC 16F877A y Lenguaje CDokumen23 halamanPIC 16F877A y Lenguaje CBraulio Parizaca PBelum ada peringkat

- Prueba de Mosfet PDFDokumen1 halamanPrueba de Mosfet PDFGiraldoCarpioRamosBelum ada peringkat

- 2 TL 494 5Dokumen20 halaman2 TL 494 5KevinEstebanVillaneraBelum ada peringkat

- Tipos de Puente HDokumen5 halamanTipos de Puente HCharles HolesBelum ada peringkat

- Clase Practica - Unidad IiDokumen3 halamanClase Practica - Unidad IiAder Hariel Treminio MontoyaBelum ada peringkat

- EcualizadorDokumen5 halamanEcualizadorJuan KarlosBelum ada peringkat

- Como Hacer Un Provador o Punta LogicaDokumen20 halamanComo Hacer Un Provador o Punta LogicaCamilo Andres Penagos S.Belum ada peringkat

- Diseño de Punta LogicaDokumen2 halamanDiseño de Punta LogicaEdwin Marquez100% (1)

- Man Sistemas Digitales 2022-1 UnlockedDokumen52 halamanMan Sistemas Digitales 2022-1 UnlockedPaola YGBelum ada peringkat

- Doblador de tensión de media onda: funcionamiento y aplicacionesDokumen9 halamanDoblador de tensión de media onda: funcionamiento y aplicacionesJavier Terreros GalarzaBelum ada peringkat

- Memoria SpeeduinoDokumen2 halamanMemoria Speeduinodavid rodriguezBelum ada peringkat

- SpiDokumen10 halamanSpiJuan Carlos ValdiviezoBelum ada peringkat

- Manual Probador de MariposaDokumen12 halamanManual Probador de MariposaarielfoxtoolsBelum ada peringkat

- Proyectos de Circuitos ElectricosDokumen2 halamanProyectos de Circuitos ElectricosMarco MasBelum ada peringkat

- Inversor MonofasicoDokumen7 halamanInversor MonofasicojohnBelum ada peringkat

- Reparacion CentralitaDokumen7 halamanReparacion CentralitaPatrick LopezBelum ada peringkat

- Cómo Elegir Un Reemplazo para El Transistor BipolarDokumen2 halamanCómo Elegir Un Reemplazo para El Transistor BipolarMiguel ViscarraBelum ada peringkat

- Gol Power 1.6Dokumen2 halamanGol Power 1.6Maxi LandivisnayBelum ada peringkat

- Diagnóstico paso a paso del sensor MAPDokumen3 halamanDiagnóstico paso a paso del sensor MAPSatooAtheiBelum ada peringkat

- Generador de PulsosDokumen45 halamanGenerador de PulsosElías Sueldo100% (1)

- Proyecto 2 PLC Bandas-TransportadorasDokumen7 halamanProyecto 2 PLC Bandas-TransportadorasRamiro Octavio Cuacua FriasBelum ada peringkat

- Capítulo 19. Módulo MSSPDokumen13 halamanCapítulo 19. Módulo MSSPAlfredo Flores VargasBelum ada peringkat

- 12V A 5VDokumen4 halaman12V A 5VoscarBelum ada peringkat

- Fuente Conmutada (Diseño)Dokumen18 halamanFuente Conmutada (Diseño)INJESBG100% (1)

- Configuración y funcionamiento del temporizador 555Dokumen16 halamanConfiguración y funcionamiento del temporizador 555oapvBelum ada peringkat

- Como Hacer Una Punta LógicaDokumen4 halamanComo Hacer Una Punta LógicaYolanda CastilloBelum ada peringkat

- 2 Contador de 0-99 7segDokumen6 halaman2 Contador de 0-99 7segJalapa Lug GuatemalaBelum ada peringkat

- Opel Corsa Chevy Posición de Los RelayDokumen1 halamanOpel Corsa Chevy Posición de Los Relayjeyson messaBelum ada peringkat

- Termostato ElectrónicoDokumen3 halamanTermostato ElectrónicoDownloadfree VeryfreeBelum ada peringkat

- Sensores y Actuadores en El AutomovilDokumen8 halamanSensores y Actuadores en El AutomovilChristopher MzxBelum ada peringkat

- Curva NTCDokumen4 halamanCurva NTCKerly Esthefanny100% (1)

- Qué Es Una Fuente de AlimentaciónDokumen4 halamanQué Es Una Fuente de AlimentaciónAugustoRosarioBelum ada peringkat

- Timer Con 555Dokumen10 halamanTimer Con 555hectcandBelum ada peringkat

- Aplicación de Circuitos Operacionales Integrales en El AutomovilDokumen16 halamanAplicación de Circuitos Operacionales Integrales en El AutomovilJose Torres Vilcapoma100% (2)

- Puntalogica 12vDokumen12 halamanPuntalogica 12vAlexander RicoBelum ada peringkat

- Practica 2:destellador de Luz Intermitente: ElectrónicaDokumen4 halamanPractica 2:destellador de Luz Intermitente: ElectrónicaLuisBelum ada peringkat

- Circuitos digitalesDokumen13 halamanCircuitos digitalesjordyBelum ada peringkat

- Circuito monoestable 555Dokumen5 halamanCircuito monoestable 555LuisBelum ada peringkat

- Practica 1.2Dokumen5 halamanPractica 1.2LuisBelum ada peringkat

- Punta Logica 2Dokumen2 halamanPunta Logica 2Jose luisBelum ada peringkat

- Manual 3 82Dokumen37 halamanManual 3 82GUSTAVO GAMESBelum ada peringkat

- Final 2Dokumen7 halamanFinal 2Mathias Chero MendozaBelum ada peringkat

- Previo 1 OficialDokumen12 halamanPrevio 1 OficialGuillermo AQxpzBelum ada peringkat

- GUÍA cd1Dokumen11 halamanGUÍA cd1kleberBelum ada peringkat

- PLANTILLA para Los ProgramasDokumen1 halamanPLANTILLA para Los ProgramasCarlos SuruyBelum ada peringkat

- Sensores Infrarrojos de Barrera y ReflexivosDokumen4 halamanSensores Infrarrojos de Barrera y ReflexivosCarlos SuruyBelum ada peringkat

- Algebra Booleana y Circuitos LógicosDokumen3 halamanAlgebra Booleana y Circuitos LógicosCarlos Suruy0% (1)

- Microcontroladores: qué son y sus principales característicasDokumen13 halamanMicrocontroladores: qué son y sus principales característicasCarlos SuruyBelum ada peringkat

- 06 - Arboles LogicosDokumen15 halaman06 - Arboles LogicosCarlos Suruy67% (3)

- Práctica Nº1: Diseño de Circuitos CombinacionalesDokumen3 halamanPráctica Nº1: Diseño de Circuitos CombinacionalesVíctor ArrietaBelum ada peringkat

- Universal Serial Bus - USB (Grupo 2)Dokumen15 halamanUniversal Serial Bus - USB (Grupo 2)Carlos SuruyBelum ada peringkat

- Microcontroladores: qué son y sus principales característicasDokumen13 halamanMicrocontroladores: qué son y sus principales característicasCarlos SuruyBelum ada peringkat

- Arquitectura de MicroprocesadoresDokumen14 halamanArquitectura de MicroprocesadoresCarlos SuruyBelum ada peringkat

- 06.1 - Lógica Del Concepto 2Dokumen11 halaman06.1 - Lógica Del Concepto 2Carlos SuruyBelum ada peringkat

- Problemas Resueltos Plano InclinadoDokumen37 halamanProblemas Resueltos Plano InclinadoAndres Hersal71% (7)

- 06 - Arboles LogicosDokumen15 halaman06 - Arboles LogicosCarlos Suruy67% (3)

- Diagrama Fuente Lm317 y Tip 3055Dokumen4 halamanDiagrama Fuente Lm317 y Tip 3055normang100% (7)

- Plan Chicago 2013Dokumen4 halamanPlan Chicago 2013Carlos SuruyBelum ada peringkat

- Unidad1 Presentacion I Parte IntroductoriaDokumen45 halamanUnidad1 Presentacion I Parte IntroductoriaCarlos SuruyBelum ada peringkat

- Movimiento Ondulatorio - LECTURADokumen6 halamanMovimiento Ondulatorio - LECTURACarlos SuruyBelum ada peringkat

- Fabricacion de Circuitos Impresos PDFDokumen12 halamanFabricacion de Circuitos Impresos PDFCarlos SuruyBelum ada peringkat

- Practicas Circuitos Serie-ParaleloDokumen8 halamanPracticas Circuitos Serie-ParaleloCarlos SuruyBelum ada peringkat

- Diagrama Fuente Lm317 y Tip 3055Dokumen4 halamanDiagrama Fuente Lm317 y Tip 3055normang100% (7)

- Comput Ad orDokumen20 halamanComput Ad orCarlos SuruyBelum ada peringkat

- Comput Ad orDokumen20 halamanComput Ad orCarlos SuruyBelum ada peringkat

- Control de Inventario 2Dokumen32 halamanControl de Inventario 2gricel gamarraBelum ada peringkat

- Modelo medición productividad total empresa BarranquillaDokumen221 halamanModelo medición productividad total empresa BarranquillaPROYECT 2017Belum ada peringkat

- Patricio Robles - Control - S - 8 LogisticaDokumen4 halamanPatricio Robles - Control - S - 8 LogisticaMANUEL SOTOMAYORBelum ada peringkat

- Plantilla de Diagrama Gantt en ExcelDokumen18 halamanPlantilla de Diagrama Gantt en ExcelBrendaBelum ada peringkat

- Ut 2 Admon Conf WsDokumen85 halamanUt 2 Admon Conf Wsdavidelnoob33Belum ada peringkat

- Cotizacion de Laptop - PC, Impresora, Proyector, RackDokumen6 halamanCotizacion de Laptop - PC, Impresora, Proyector, RackLidia De Lourdes Lopez LizanaBelum ada peringkat

- Lista de Chequeo Inicio de ObraDokumen4 halamanLista de Chequeo Inicio de ObraVictor Díaz AravenaBelum ada peringkat

- Howen Presentaciòn-Spainish 20191218Dokumen46 halamanHowen Presentaciòn-Spainish 20191218Daniel OrtizBelum ada peringkat

- (ES) EPSILON - 23 - Tendencias - 2023 - SPDokumen27 halaman(ES) EPSILON - 23 - Tendencias - 2023 - SPalx axlBelum ada peringkat

- Reglamento Especifico Pse 01116Dokumen29 halamanReglamento Especifico Pse 01116Pablo BenitezBelum ada peringkat

- Silabo de Logística X Ciclo AgroindustrialDokumen6 halamanSilabo de Logística X Ciclo AgroindustrialDianaElizabethMallquiSanchezBelum ada peringkat

- Programa psicoeducativo para padres con hijos adolescentesDokumen17 halamanPrograma psicoeducativo para padres con hijos adolescentesgeos8329Belum ada peringkat

- CV Jose JaramilloDokumen36 halamanCV Jose JaramilloJose JaramilloBelum ada peringkat

- Soluciones Intranet ExtranetDokumen12 halamanSoluciones Intranet ExtranetGrover Luis Untoja AduviriBelum ada peringkat

- Análisis de Riego (IEC 62305)Dokumen10 halamanAnálisis de Riego (IEC 62305)IVAN TURCOBelum ada peringkat

- Ejemplo de Plan de PruebasDokumen14 halamanEjemplo de Plan de PruebasNathaly GonzálezBelum ada peringkat

- Análisis Forense pasoDokumen8 halamanAnálisis Forense pasoRicardo PadillaBelum ada peringkat

- Memoria Descriptiva A.C.I.Dokumen20 halamanMemoria Descriptiva A.C.I.Jose Luis Gamarra SupoBelum ada peringkat

- 2006 Analisis Del Sistema de Transporte Público en La Ciudad de Huancayo PDFDokumen122 halaman2006 Analisis Del Sistema de Transporte Público en La Ciudad de Huancayo PDFJoel GuzmanBelum ada peringkat

- Bioingenio Ambiental ofrece servicios de asesoría ambientalDokumen2 halamanBioingenio Ambiental ofrece servicios de asesoría ambientalClaudia Camargo100% (1)

- Perfil Del Ing. AgroindustrialDokumen2 halamanPerfil Del Ing. AgroindustrialJonathan BorjasBelum ada peringkat

- Acosta, Jose Miguel y Sueiro Yolanda, Una Historia de PelículaDokumen33 halamanAcosta, Jose Miguel y Sueiro Yolanda, Una Historia de PelículaVanessa MontenegroBelum ada peringkat

- Asus M2A-MVPDokumen2 halamanAsus M2A-MVPAlexiel DuartesBelum ada peringkat

- Koshino HouseDokumen12 halamanKoshino HousecafierojaBelum ada peringkat

- 002 Hoja de Vida de Equipos de Computo A-Tic-Ft-002 v3-14nDokumen1 halaman002 Hoja de Vida de Equipos de Computo A-Tic-Ft-002 v3-14nAlbenis Robayo0% (1)

- Aporte1 PF Wilmar HernandezDokumen10 halamanAporte1 PF Wilmar HernandezALEJANDRA SALAS CBelum ada peringkat

- Unidad 7 Conectividad de Bases de DatosDokumen6 halamanUnidad 7 Conectividad de Bases de DatosAlberto DiazBelum ada peringkat

- La Educación Superior, Internacionalización e Integración Regional de América Latina y El Caribe PDFDokumen281 halamanLa Educación Superior, Internacionalización e Integración Regional de América Latina y El Caribe PDFPablo Flores JaraBelum ada peringkat

- Motor Capacitor Triple Cbb61 4.7uf 6uf 6uf VentilDokumen1 halamanMotor Capacitor Triple Cbb61 4.7uf 6uf 6uf VentilAlex CobosBelum ada peringkat

- Folleto de Auditoria ClaroDokumen2 halamanFolleto de Auditoria ClaroNataly MoralesBelum ada peringkat